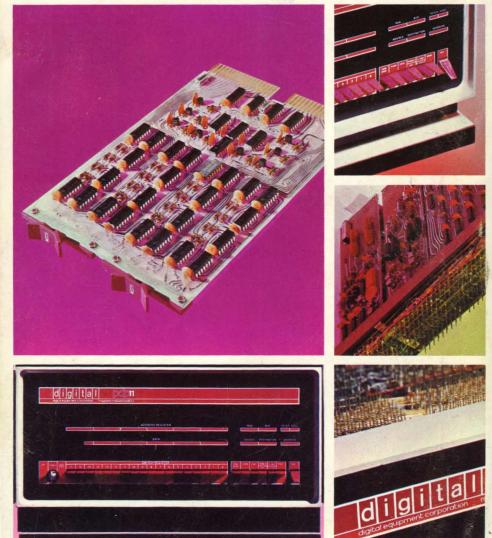

digital equipment corporation 1976

# heineloook

# digital equipment corporation

I

Copyright 1969 by Digital Equipment Corporation

PDP is a registered trademark of Digital Equipment Corporation

The material in this handbook is for information purposes only and is subject to change without notice.

# TABLE OF CONTENTS

| CHAPTER 1 INTRODUCTION              |                                 |

|-------------------------------------|---------------------------------|

| PDP-11 SYSTEMS                      | 1                               |

| UNIBUS                              | 1                               |

| KA11 PROCESSOR                      | 1                               |

| Priority Interrupts                 | 1                               |

| Reentrant Code                      | 2                               |

| General Registers                   | 2<br>2<br>2<br>2<br>2<br>2<br>2 |

| Instruction Set                     | 2                               |

| Addressing                          | 2                               |

| Asynchronous Operation              | 2                               |

| PACKAGING                           |                                 |

| SOFTWARE                            | 3                               |

|                                     |                                 |

| CHAPTER 2 SYSTEM INTRODUCTION       |                                 |

| SYSTEM DEFINITION                   | 5                               |

| SYSTEM COMPONENTS                   | 5                               |

| UNIBUS                              | 5                               |

| Single Bus                          | 5                               |

| Bidirectional Lines                 | 5                               |

| Master-Slave Relation               | 5                               |

| Interlocked Communication           | 5                               |

| Dynamic Master-Slave Relation       | 6                               |

| KA11 CENTRAL PROCESSOR              | 6                               |

| General Registers                   | 6                               |

| Central Processor Status Register   | 6                               |

| CORE MEMORY                         | 6                               |

| PERIPHERAL DEVICES                  | 7                               |

| SYSTEM INTERACTION                  | 7                               |

| TRANSFER OF BUS MASTER              | 7                               |

| PRIORITY STRUCTURE                  | 7                               |

| NPR Requests                        | 8                               |

| Interrupt Requests                  | 8                               |

| CHAPTER 3 ADDRESSING MODES          |                                 |

|                                     |                                 |

| INTRODUCTION                        | 11                              |

| SINGLE OPERAND ADDRESSING           | 11                              |

| General Register Addressing         | 11                              |

| Deferred Addressing                 | 11                              |

| Indexed Addressing                  | 12                              |

| Autoincrement Mode Addressing       | 12                              |

| Autodecrement Addressing            | 12                              |

| STACK PROCESSING                    | 13                              |

| USE OF THE PC AS A GENERAL REGISTER | 13                              |

| Immediate Addressing                | 13                              |

| Absolute Addressing                 | 13                              |

| Relative Addressing                 | 14                              |

| Deferred Relative Addressing        | 14                              |

| USE OF THE SP AS A GENERAL REGISTER | 14                              |

| DOUBLE OPERAND ADDRESSING           | 14                              |

| CHAPTER 4 INSTRUCTION SET           |                                 |

| INSTRUCTION TIMING                  | 17                              |

| NOTATION                            | 17                              |

|                                     |                                 |

| DOUBLE OPERAND INSTRUCTIONS          |     |

|--------------------------------------|-----|

| Arithmetic Operations                |     |

| Boolean Instructions                 |     |

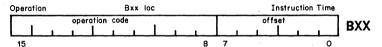

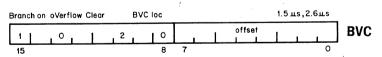

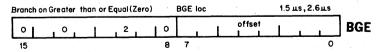

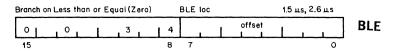

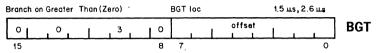

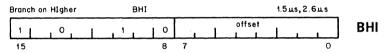

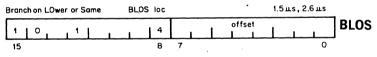

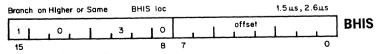

| BRANCHES                             |     |

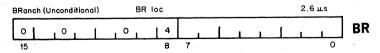

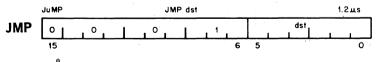

| Unconditional Branch                 |     |

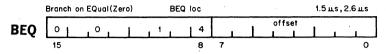

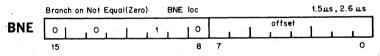

| Simple Conditional Branches          |     |

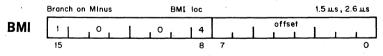

| Signed Conditional Branches          |     |

| Unsigned Conditional Branches        |     |

| JuMP                                 |     |

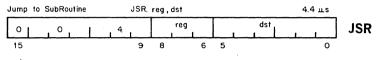

| SUBROUTINES                          |     |

| Examples                             |     |

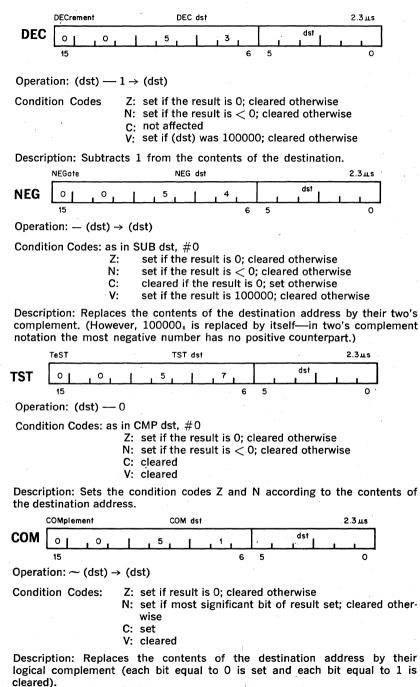

| SINGLE OPERAND INSTRUCTIONS          |     |

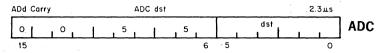

| Multiple Precision Operations        |     |

|                                      |     |

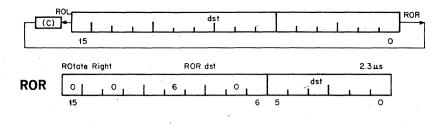

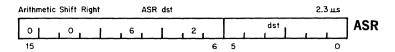

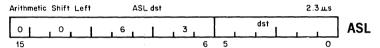

| Rotates<br>Shifts                    |     |

|                                      |     |

| Examples                             |     |

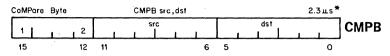

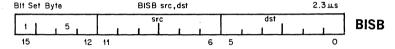

| BYTE OPERATIONS                      |     |

| Double Operand Byte Instructions     |     |

| Example                              |     |

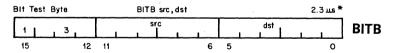

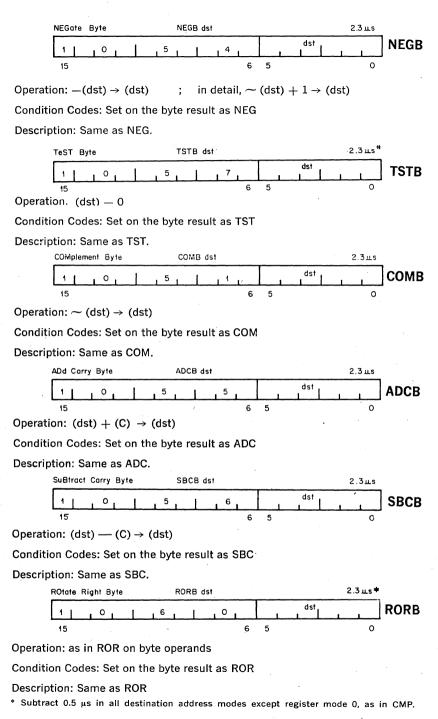

| Single Operand Instructions          |     |

| CONDITION CODE OPERATORS             |     |

| MISCELLANEOUS CONTROL INSTRUCTIONS   |     |

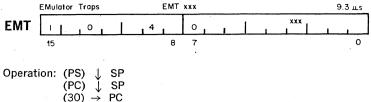

| PROCESSOR TRAPS                      |     |

| Trap Instructions                    |     |

| Stack Overflow Trap                  |     |

| Bus Error Traps                      |     |

| Trace Traps                          |     |

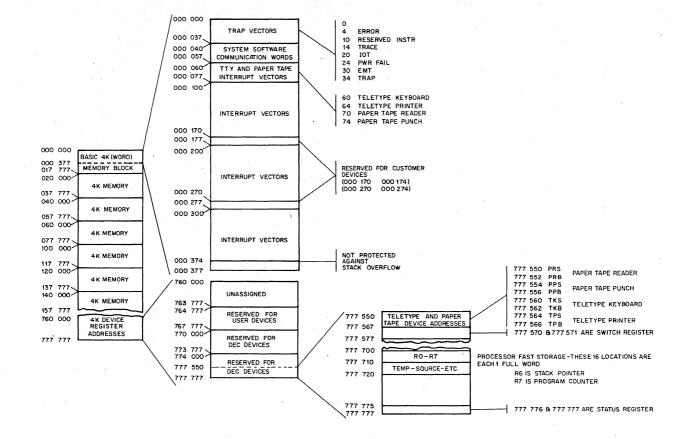

| CHAPTER 5 ADDRESS ALLOCATION         | 4 C |

| ADDRESS MAP                          | 45  |

| Interrupt and Trap Vector            |     |

| Processor Stack and General Storage  |     |

| Peripheral Registers                 |     |

| CORE MEMORY                          |     |

| Read-Write Core Memory               |     |

| Read-Only Core Memory                |     |

|                                      |     |

| Wordlet Memory                       |     |

| CHAPTER 6 PROGRAMMING OF PERIPHERALS |     |

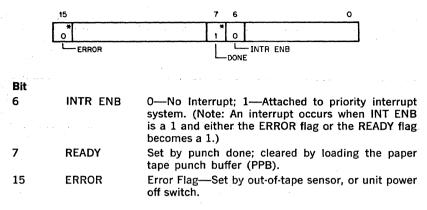

| DEVICE REGISTERS                     |     |

| CONTROL & STATUS REGISTERS           |     |

| Device Function Bits                 |     |

| Memory Extension                     |     |

| Done Enable and Interrupt Enable     |     |

| Condition Bits                       |     |

| Unit Bits                            |     |

| Error Bits                           |     |

| DATA BUFFER REGISTERS                |     |

| PROGRAMMING EXAMPLES—NON INTERRUPT   |     |

| INTERRUPT STRUCTURE                  |     |

| PROGRAMMING EXAMPLE                  | 51  |

|                                      |     |

| CHAPTER 7 PERIPHERAL BULLETINS       |     |

| TELETYPE (MODEL LT33-DC/DD)          |     |

| Size                                 |     |

| Power Requirement                    |     |

|                                      |     |

| TELETYPE CONTROL (MODEL KL11)                                                                                                                                                                                                                                       | 53                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| Teletype Control                                                                                                                                                                                                                                                    | 53                                                             |

| Keyboard/Reader Operation                                                                                                                                                                                                                                           | 53                                                             |

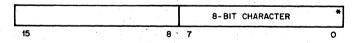

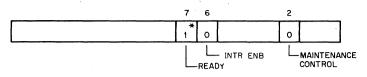

| Registers (TKS, TKB)                                                                                                                                                                                                                                                | 54                                                             |

| Teleprinter/Punch                                                                                                                                                                                                                                                   | 54                                                             |

| Registers (TPS, TPB)                                                                                                                                                                                                                                                | 55                                                             |

| Programming Example                                                                                                                                                                                                                                                 |                                                                |

| Peripheral Address Assignments                                                                                                                                                                                                                                      | 55                                                             |

| Mounting                                                                                                                                                                                                                                                            | 55                                                             |

| HIGH-SPEED PERFORATED TAPE READER (MODEL PC11)                                                                                                                                                                                                                      | 55                                                             |

| Tape Reader                                                                                                                                                                                                                                                         |                                                                |

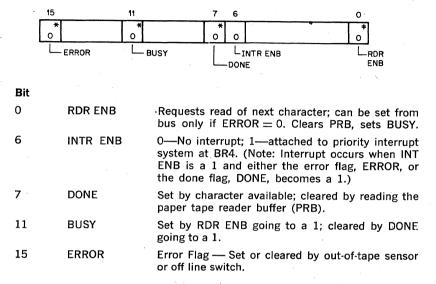

| Registers (PRS, PRB)                                                                                                                                                                                                                                                | 56                                                             |

| Programming Example                                                                                                                                                                                                                                                 | 56                                                             |

| Peripheral Address Assignments                                                                                                                                                                                                                                      |                                                                |

| Tape Punch                                                                                                                                                                                                                                                          |                                                                |

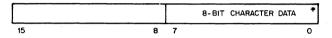

| Registers (PPS, PPB)                                                                                                                                                                                                                                                | 57                                                             |

| Programming Example                                                                                                                                                                                                                                                 | 57                                                             |

| Peripheral Address Assignments                                                                                                                                                                                                                                      | 57                                                             |

| Mounting                                                                                                                                                                                                                                                            | 57                                                             |

| Environmental                                                                                                                                                                                                                                                       |                                                                |

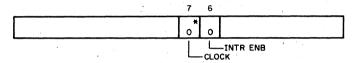

| Line Frequency Clock (Model KW11-L)                                                                                                                                                                                                                                 | 58                                                             |

| Register                                                                                                                                                                                                                                                            | 58                                                             |

| Peripheral Address Assignments                                                                                                                                                                                                                                      |                                                                |

| Mounting                                                                                                                                                                                                                                                            |                                                                |

| Vector Address                                                                                                                                                                                                                                                      | 58                                                             |

| Priority Level                                                                                                                                                                                                                                                      |                                                                |

|                                                                                                                                                                                                                                                                     |                                                                |

| CHAPTER 8 DESCRIPTION OF THE UNIBUS                                                                                                                                                                                                                                 |                                                                |

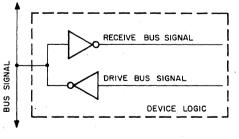

| GENERAL CONCEPTS OF THE UNIBUS                                                                                                                                                                                                                                      | 59                                                             |

| Single Bus                                                                                                                                                                                                                                                          | 59                                                             |

| Bidirectional Bus                                                                                                                                                                                                                                                   | 59                                                             |

| Master-Slave Relation                                                                                                                                                                                                                                               | 59                                                             |

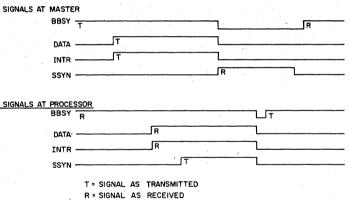

| Interlocked Communication                                                                                                                                                                                                                                           | 60                                                             |

| Dynamic Master-Slave Relation                                                                                                                                                                                                                                       | 60                                                             |

| UNIBUS SIGNALS                                                                                                                                                                                                                                                      | 60                                                             |

| NON-INTERRUPT SIGNALS                                                                                                                                                                                                                                               | 60                                                             |

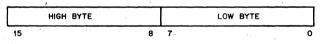

| Data Lines                                                                                                                                                                                                                                                          | 60                                                             |

| Address Lines                                                                                                                                                                                                                                                       | 60                                                             |

| Control Lines                                                                                                                                                                                                                                                       | 61                                                             |

| Master Sync & Slave Sync                                                                                                                                                                                                                                            | 61                                                             |

| Parity Available & Parity Bit                                                                                                                                                                                                                                       | 61                                                             |

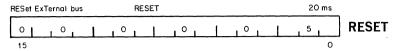

| Initialization                                                                                                                                                                                                                                                      | 61                                                             |

| Spore 1 P Spore 2                                                                                                                                                                                                                                                   | <b>U</b> 1                                                     |

|                                                                                                                                                                                                                                                                     | 61                                                             |

| Spare 1 & Spare 2<br>INTERRUPT SIGNALS                                                                                                                                                                                                                              |                                                                |

|                                                                                                                                                                                                                                                                     | 61                                                             |

| INTERRUPT SIGNALS                                                                                                                                                                                                                                                   | 61<br>61                                                       |

| INTERRUPT SIGNALS                                                                                                                                                                                                                                                   | 61<br>61<br>61                                                 |

| INTERRUPT SIGNALS<br>Bus Request Lines<br>Bus Grant Lines                                                                                                                                                                                                           | 61<br>61<br>61<br>61<br>61<br>61                               |

| INTERRUPT SIGNALS<br>Bus Request Lines<br>Bus Grant Lines<br>Non-Processor Request<br>Non-Processor Grant<br>Selection Acknowledge                                                                                                                                  | 61<br>61<br>61<br>61<br>61<br>61<br>61                         |

| INTERRUPT SIGNALS<br>Bus Request Lines<br>Bus Grant Lines<br>Non-Processor Request<br>Non-Processor Grant<br>Selection Acknowledge<br>Interrupt (and) Bus Busy                                                                                                      | 61<br>61<br>61<br>61<br>61<br>61<br>61<br>61                   |

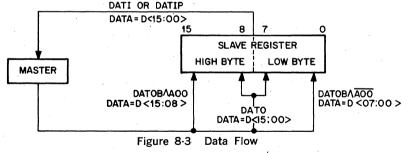

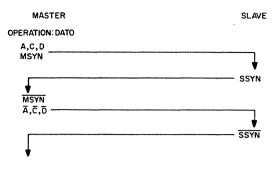

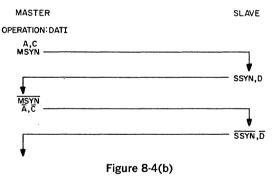

| INTERRUPT SIGNALS<br>Bus Request Lines<br>Bus Grant Lines<br>Non-Processor Request<br>Non-Processor Grant<br>Selection Acknowledge<br>Interrupt (and) Bus Busy<br>UNIBUS DATA TRANSFER OPERATIONS                                                                   | 61<br>61<br>61<br>61<br>61<br>61<br>61<br>61<br>61<br>61       |

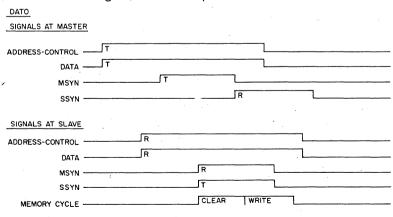

| INTERRUPT SIGNALS<br>Bus Request Lines<br>Bus Grant Lines<br>Non-Processor Request<br>Non-Processor Grant<br>Selection Acknowledge<br>Interrupt (and) Bus Busy<br>UNIBUS DATA TRANSFER OPERATIONS<br>DATO and DATOB                                                 | 61<br>61<br>61<br>61<br>61<br>61<br>61<br>61<br>61<br>61<br>62 |

| INTERRUPT SIGNALS<br>Bus Request Lines<br>Bus Grant Lines<br>Non-Processor Request<br>Non-Processor Grant<br>Selection Acknowledge<br>Interrupt (and) Bus Busy<br>UNIBUS DATA TRANSFER OPERATIONS<br>DATO and DATOB<br>DATI and DATIP                               | 61<br>61<br>61<br>61<br>61<br>61<br>61<br>61<br>61<br>62<br>62 |

| INTERRUPT SIGNALS<br>Bus Request Lines<br>Bus Grant Lines<br>Non-Processor Request<br>Non-Processor Grant<br>Selection Acknowledge<br>Interrupt (and) Bus Busy<br>UNIBUS DATA TRANSFER OPERATIONS<br>DATO and DATOB<br>DATI and DATIP<br>Examples of Data Transfers | 61<br>61<br>61<br>61<br>61<br>61<br>61<br>61<br>62<br>62<br>62 |

| INTERRUPT SIGNALS<br>Bus Request Lines<br>Bus Grant Lines<br>Non-Processor Request<br>Non-Processor Grant<br>Selection Acknowledge<br>Interrupt (and) Bus Busy<br>UNIBUS DATA TRANSFER OPERATIONS<br>DATO and DATOB<br>DATI and DATIP                               | 61<br>61<br>61<br>61<br>61<br>61<br>61<br>61<br>61<br>62<br>62 |

| INTERRUPT SIGNALS<br>Bus Request Lines<br>Bus Grant Lines<br>Non-Processor Request<br>Non-Processor Grant<br>Selection Acknowledge<br>Interrupt (and) Bus Busy<br>UNIBUS DATA TRANSFER OPERATIONS<br>DATO and DATOB<br>DATI and DATIP<br>Examples of Data Transfers | 61<br>61<br>61<br>61<br>61<br>61<br>61<br>61<br>62<br>62<br>62 |

| INTERRUPT SIGNALS<br>Bus Request Lines<br>Bus Grant Lines<br>Non-Processor Request<br>Non-Processor Grant<br>Selection Acknowledge<br>Interrupt (and) Bus Busy<br>UNIBUS DATA TRANSFER OPERATIONS<br>DATO and DATOB<br>DATI and DATIP<br>Examples of Data Transfers | 61<br>61<br>61<br>61<br>61<br>61<br>61<br>61<br>62<br>62<br>62 |

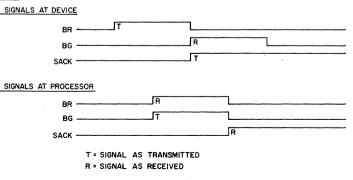

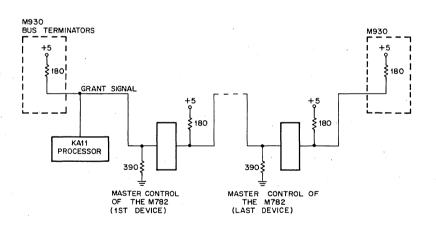

| UNIBUS CONTROL<br>Priority Arbitration<br>Selection of Next Bus Master<br>Interrupt Sequence<br>Example of Interrupt, etc.<br>Example of NPR Operation                                                                                                                                                                                                                                                                                                                                                                                | 64<br>65<br>65<br>66<br>66                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| CHAPTER 9 INTERFACING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                |

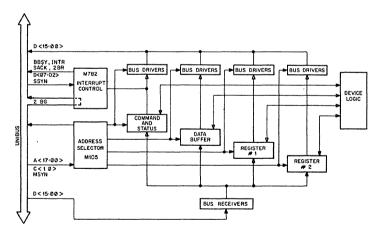

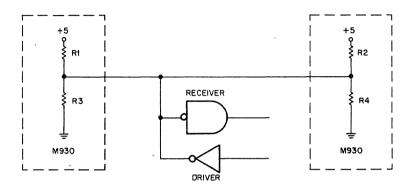

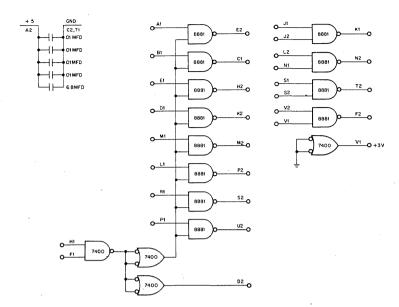

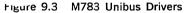

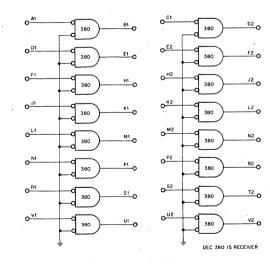

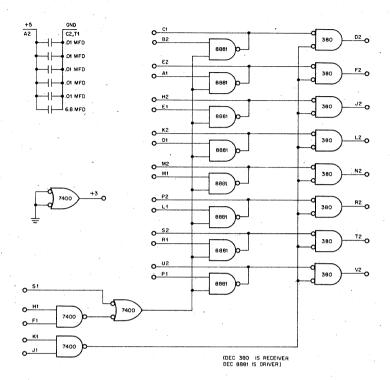

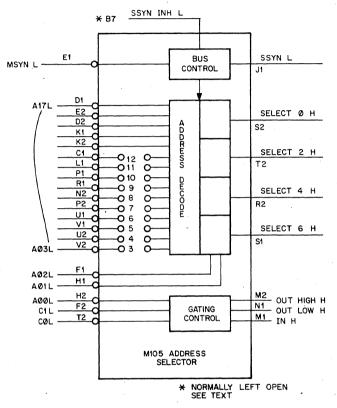

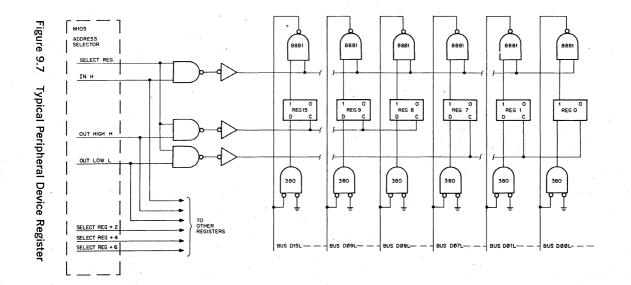

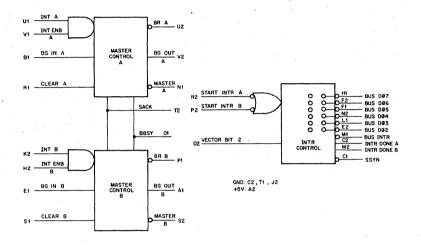

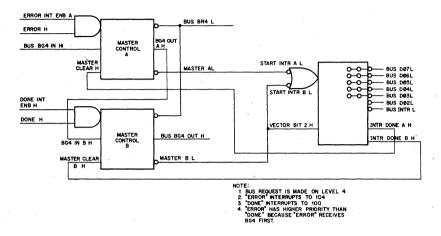

| REGISTERS<br>BUS DRIVERS AND RECEIVERS<br>ADDRESS SELECTOR<br>INTERRUPT CONTROL<br>DEVICE CONTROL LOGIC                                                                                                                                                                                                                                                                                                                                                                                                                               | 69<br>69<br>71<br>74<br>76                                                                                     |

| CHAPTER 10 CONFIGURATION AND INSTALLATION PLANNING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                |

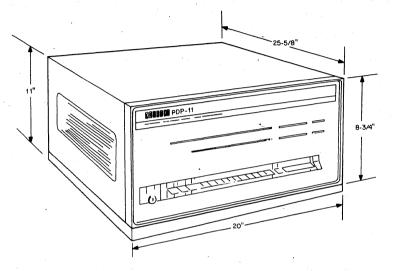

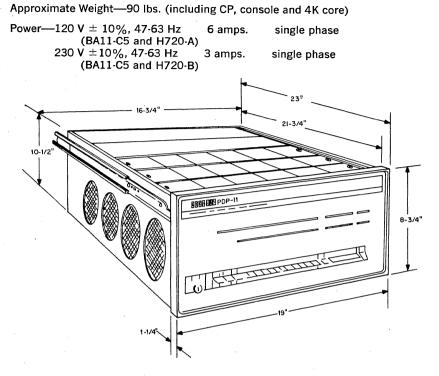

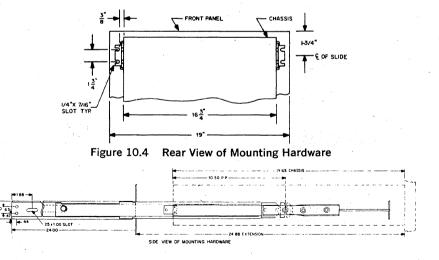

| MODULAR CONSTRUCTION<br>MOUNTING BOXES AND CABINETS<br>PDP-11 Tabletop Box for 11/20, Etc.<br>PDP-11 Basic Mounting Box<br>PDP-11 Tabletop Extension Mounting Box<br>PDP-11 Freestanding Base Cabinet<br>Freestanding Programmer's Table<br>SYSTEM UNITS AND CABLES<br>Peripheral Mounting Unit<br>Blank System Unit<br>Unibus Module<br>Unibus Cable<br>CABLE REQUIREMENTS<br>PDP-11/20 POWER REQUIREMENTS<br>TELETYPE REQUIREMENTS<br>ENVIRONMENTAL REQUIREMENTS<br>INSTALLATION PROCEDURE<br>CHAPTER 11 BARER TARE SOFTWARE SYSTEM | 77<br>77<br>78<br>80<br>81<br>81<br>81<br>81<br>82<br>82<br>82<br>82<br>82<br>82<br>82<br>82<br>82<br>82<br>83 |

| CHAPTER 11 PAPER TAPE SOFTWARE SYSTEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                |

| PTS FEATURES<br>PAL-11A Assembler<br>ED11 Editor<br>ODT On-Line Debugging<br>IOX Input/Output, etc.<br>Math Package<br>Loaders<br>Core Dump Routines                                                                                                                                                                                                                                                                                                                                                                                  | 85<br>85<br>85<br>85<br>86<br>86<br>86<br>86                                                                   |

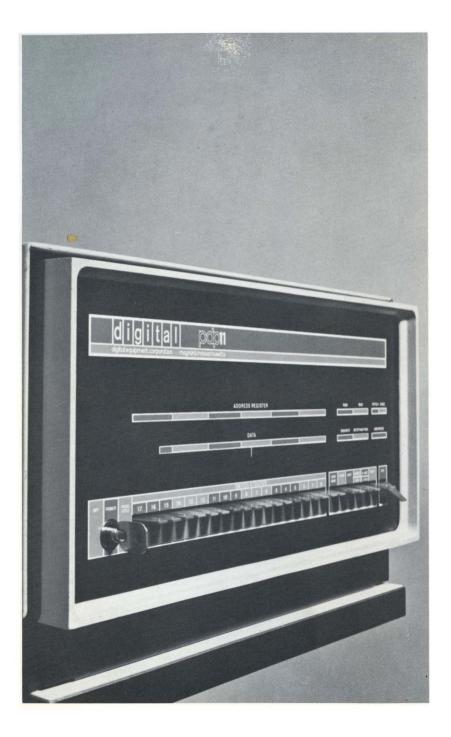

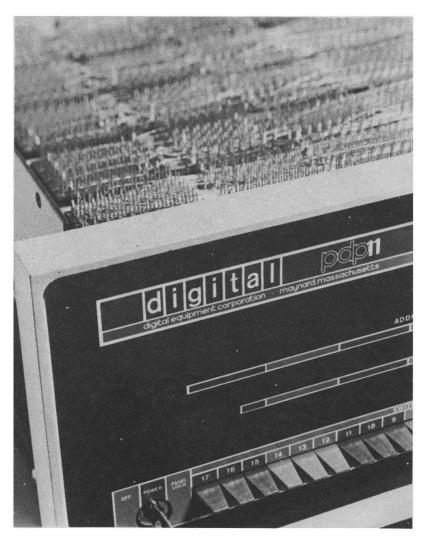

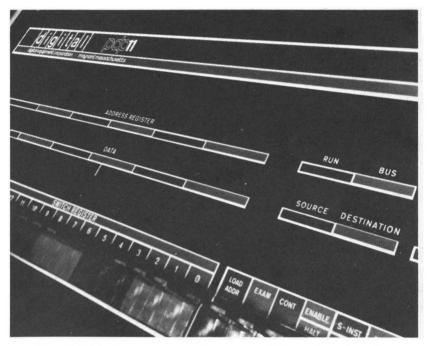

| CHAPTER 12 THE OPERATOR'S CONSOLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                |

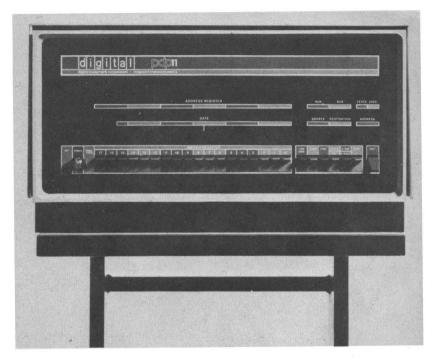

| CONSOLE ELEMENTS<br>Indicator Lights<br>Register Displays<br>Switch Register<br>Control Switches<br>CONTROL SWITCH OPERATION                                                                                                                                                                                                                                                                                                                                                                                                          | 87<br>87<br>87<br>87<br>87<br>89                                                                               |

| APPENDIX A—PDP-11 INSTRUCTION REPERTOIRE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 91                                                                                                             |

| APPENDIX B—ADDRESSING SUMMARY<br>ADDRESSING MODES<br>General Register Addressing<br>PC Register Addressing                                                                                                                                                                                                                                                                                                                                                                                                                            | 95<br>95<br>95<br>95                                                                                           |

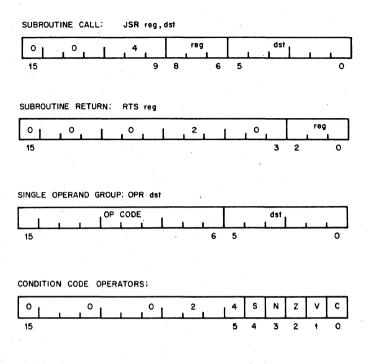

| INSTRUCT | ION FORMATS      |            |  |

|----------|------------------|------------|--|

| APPENDIX | C-ADDRESS MAP .  |            |  |

| DATA-TRA | NSFERS           | FIONS      |  |

|          |                  |            |  |

|          |                  |            |  |

|          |                  |            |  |

| GENERAL  | NOTES ON THE BUS | OPERATIONS |  |

The PDP-11 is available in two versions—PDP-11/10 and PDP-11/20. The basic PDP-11/10 contains 1,024 words of read only memory in conjunction with 128 words of read/write memory and the basic PDP-11/20 includes 4,096 words of read/write memory.

# CHAPTER 1 INTRODUCTION

This publication is a handbook for Digital Equipment Corporation's PDP-11. It provides a comprehensive overview of the system structure, the instruction repertoire, input/output programming, peripherals, general interfacing, software, and console operation.

PDP-11 is Digital's answer to the demand for a modular system for real-time data acquisition, analysis and control. PDP-11 systems can handle a wide variety of real-time control applications—each system being individually tailored from a comprehensive array of modular building blocks. Digital is unique among manufacturers of small-scale computers in its ability to provide not only fast and efficient processing units, but also a large family of its own compatible I/O devices including A/D and D/A converters, magnetic tape, disk storage, paper tape, and displays, as well as a wide range of general-purpose modules. This capability offers the user a new, more efficient approach to real-time systems.

The following paragraphs introduce the new PDP-11 by way of highlighting several of the important design features that set it apart from other machines in its class. Subsequent chapters of this manual place these features in their proper context and provide detailed descriptions of each.

#### PDP-11 SYSTEMS

The PDP-11 is available in two versions designated as PDP-11/10 and PDP-11/20. The PDP-11/10 contains a KA11 processor, 1,024 words of 16-bit read-only memory, and 256 16-bit words of read-write memory. The basic PDP-11/20 contains a KA11 processor and 4,096 words of 16-bit read-write core memory, a programmer's console, and an ASR-33 Teletype. Both versions can be similarly expanded with either read-write or read-only memory and peripheral devices.

#### UNIBUS

Unibus is the name given to the single bus structure of the PDP-11. The processor, memory and all peripheral devices share the same high-speed bus. The Unibus enables the processor to view peripheral devices as active memory locations which perform special functions. Peripherals can thus be addressed as memory. In other words, memory reference instructions can operate directly on control, status, or data registers in peripheral devices. Data transfers from input to output devices can bypass the processor completely.

#### KA11 PROCESSOR

The KA11 processor incorporates a unique combination of powerful features not previously available in 16-bit computers.

**Priority Interrupts**—A four-level automatic priority interrupt system permits the processor to respond automatically to conditions outside the system, or in the processor itself. Any number of separate devices can be attached to each level.

Each peripheral device in a PDP-11 system has a hardware pointer to its own unique pair of memory words which, in turn, point to the device's service routine. This unique identification eliminates the need for polling of devices

to identify an interrupt, since the interrupt servicing hardware selects and begins executing the appropriate service routine.

The device's interrupt priority and service routine priority are independent. This allows dynamic adjustment of system behavior in response to real-time conditions.

The interrupt system allows the processor continually to compare its own priority levels with the levels of any interrupting devices and to acknowledge the device with the highest level above the processor's priority level. Servicing an interrupt for a device can be interrupted for servicing a higher priority device. Service to the lower priority device can be resumed automatically upon completion of the higher level servicing. Such a process, called nested interrupt servicing, can be carried out to any level.

**Reentrant Code**—Both the interrupt handling hardware and the subroutine call hardware are designed to facilitate writing reentrant code for the PDP-11. This type of code allows use of a single copy of a given subroutine or program to be shared by more than one process or task. This reduces the amount of core needed for multi-task applications such as the concurrent servicing of many peripheral devices.

**General Registers**—The PDP-11 is equipped with eight general registers. All are program-accessible and can be used as accumulators, as pointers to memory locations, or as full-word index registers. Six registers are used for general-purpose access while the seventh and eighth registers are used as a stack pointer and program counter respectively.

**Instruction Set**—An important feature of the PDP-11 instruction set is the availability of double operand instructions. These instructions allow memory to-memory processing and eliminate the need to use registers for storage of intermediate results. By using double operand instructions, every memory location can be treated as an accumulator. This significantly reduces the length of programs by eliminating load and store operations associated with single operand machines.

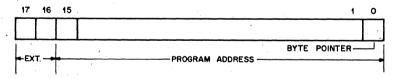

Addressing—Much of the power of the PDP-11 is derived from its wide range of addressing capabilities. PDP-11 addressing modes include list sequential addressing, full address indexing, full 16-bit word addressing, 8-bit byte addressing, stack addressing, and direct addressing to 32K words.

Variable length instruction formatting allows a minimum number of bits to be used for each addressing mode. This results in efficient use of program storage space.

Asynchronous Operation—The PDP-11's memory and processor operations are asynchronous. As a result, I/O devices transferring directly to or from memory may steal memory cycles during instruction operation.

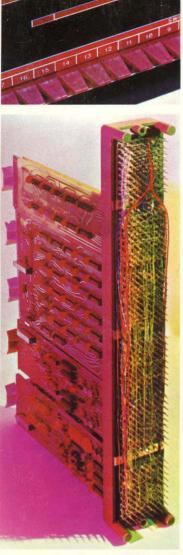

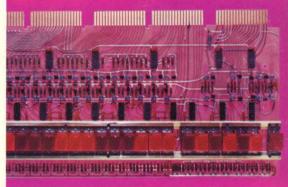

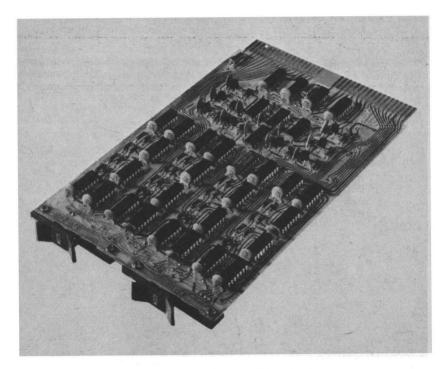

#### PACKAGING

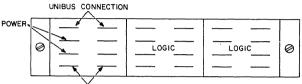

The PDP-11 has adopted a modular approach to allow custom configuring of systems, easy expansion, and easy servicing. Systems are composed of basic building blocks, called System Units, which are completely independent subsystems connected only by pluggable Unibus and power connections. There is no fixed wiring between them. An example of this type of subsystem is a 4,096-word memory module.

System Units can be mounted in many combinations within the PDP-11 hardware, since there are no fixed positions for memory or I/O device controllers. Additional units can be mounted easily and connected to the system

in the field. In case maintenance is required, defective System Units can be replaced with spares and operation resumed within a few minutes.

#### SOFTWARE

A complete package of user-oriented software includes:

- Absolute assembler providing object and source listings

- String-oriented editor

- Debugging routines capable of operating in a priority interrupt environment

- Input/output handlers for standard peripherals

- Relocatable integer and floating point math library

All PDP-11 processors, memories and peripherals are electrically and mechanically modular subsystems supported in System Units which are simply plugged together to form a computer tailored to user needs.

#### CHAPTER 2

#### SYSTEM INTRODUCTION

#### SYSTEM DEFINITION

Digital Equipment Corporation's PDP-11 is a 16-bit, general-purpose, parallellogic computer using two's complement arithmetic. The PDP-11 is a variable word length processor which directly addresses 32,768 16-bit words or 65,536 8-bit bytes. All communication between system components is done on a single high-speed bus called a Unibus. Standard features of the system include eight general-purpose registers which can be used as accumulators, index registers, or address pointers, and a multi-level automatic priority interrupt system.

#### SYSTEM COMPONENTS

**UNIBUS**—There are five concepts that are very important for understanding both the hardware and software implications of the Unibus.

**Single Bus**—The Unibus is a single, common path that connects the central processor memory, and all peripherals. Addresses, data, and control information are sent along the 56 lines of the bus.

The form of communication is the same for every device on the Unibus. The processor uses the same set of signals to communicate with memory as with peripheral devices. Peripheral devices also use this set of signals when communicating with the processor, memory, or other peripheral devices.

Peripheral device registers may be manipulated as flexibly as core memory by the central processor. All the instructions that can be applied to data in core memory can be applied equally well to data in peripheral device registers. This is an especially powerful feature, considering the special capability of PDP-11 instructions to process data in any memory location as though it were an accumulator.

**Bidirectional Lines**—Unibus lines are bidirectional, so that the same signals which are received as input can be driven as output. This means that a peripheral device register can be either read or set by the central processor or other peripheral devices; thus, the same register can be used for both input and output functions.

**Master-Slave Relation**—Communication between two devices on the bus is in the form of a master-slave relationship. At any point in time, there is one device that has control of the bus. This controlling device is termed the "bus master." The master device controls the bus when communicating with another device on the bus, termed the "slave." A typical example of this relationship is the processor, as master, fetching an instruction from memory (which is always a slave). Another example is the disk, as master, transferring data to memory, as slave.

Interlocked Communication—Communication on the Unibus is interlocked so that for each control signal issued by the master device, there must be a response from the slave in order to complete the transfer. Therefore, communication is independent of the physical bus length and the response time of the master and slave devices. The maximum transfer rate on the Unibus is one 16-bit word every 750 nanoseconds, or 1.3 million 16-bit words per second.

5

**Dynamic Master-Slave Relation**—Master-slave relationships are dynamic. The processor, for example, may pass bus control to a disk. The disk, as master, could then communicate with a slave memory bank.

Since the Unibus is used by the processor and all I/O devices, there is a priority structure to determine which device gets control of the bus. Therefore, every device on the Unibus which is capable of becoming bus master has a priority assigned to it. When two devices which are capable of becoming a bus master request use of the bus simultaneously, the device with the higher priority will receive control first. Details of what conditions must be satisfied before a device will get control of the bus are given in the section on System Interaction.

**KA11 CENTRAL PROCESSOR**—There are four major features which are of particular interest to the programmer: 1), the General Registers; 2), the Processor Status Word; (3), the Addressing Modes; and 4), the Instruction Set. The addressing modes and the instruction set of the PDP-11 processor will be discussed in detail in Chapters 3 and 4.

**General Registers**—The KA11 processor contains eight 16-bit general registers. These eight general registers (referred to as R0, R1, . . . . R7) may be used as accumulators, as index registers, or as stack pointers. One of these registers, R7, is reserved as a program counter (PC). Generally, the PC holds the address of the next instruction, but it may point to data or to an address of data. The register R6 has the special function of processor stack pointer.

**Central Processor Status Register**—The Central Processor Status Register (PS) contains information on the current priority of the processor, the result of previous operations, and an indicator for detecting the execution of an instruction to be trapped during program debugging. The priority of the central processor can be set under program control to any one of eight levels. This information is held in bits 5, 6, and 7 of the PS.

Four bits of the PS are assigned to monitoring different results of previous instructions. These bits are set as follows:

Z----if the result was zero

- N----if the result was negative

- C----if the operation resulted in a carry from the most significant bit

- V—if the operation resulted in an arithmetic overflow

The T bit is used in program debugging and can be set or cleared under program control. If this bit is set, when an instruction is fetched from memory a processor trap will be caused by the completion of the instruction's execution.

| 1 | 1 | UNUS | ED | 1 | 1 |  | P | ROCESS | OR<br>Y | т | N | z | v | ° c <sup>°</sup> . |  |

|---|---|------|----|---|---|--|---|--------|---------|---|---|---|---|--------------------|--|

|   |   |      |    |   |   |  | 7 | 6      | · 5     | 4 | 3 | 2 | 1 | 0                  |  |

#### Central Processor Status Register (PS)

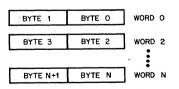

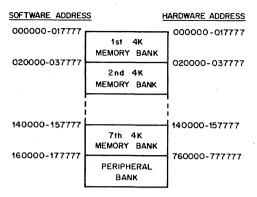

**CORE MEMORY**—The PDP-11 allows both 16-bit word and 8-bit byte addressing. The address space may be filled by core memory and peripheral device registers. The top 4,096 words generally are reserved for peripheral device registers. The remainder of address space can be used for read-write core memory or read-only core memory.

Read-write core memory is currently available in 4,096 16-bit word segments. This memory has a cycle time of <u>1.2</u> microseconds and an access time of 500 nanoseconds. It is a standard part of a PDP-11/20 system.

Read-only core memory (ROM) is available in 1,024 16 bit-word segments. The access time of the ROM is 500 nanoseconds. Memory is also available in 256 16-bit word segments with a 2.0 microsecond cycle time. 1,024 words of read-only memory as well as 256 words of read-write memory mount in a single System Unit and are a standard part of the PDP-11/10 system.

**PERIPHERAL DEVICES**—The ASR-33 Teletype with low-speed paper tape reader and punch is provided in the basic PDP-11/20 system. Options for the PDP-11 include a paper tape reader capable of reading 300 characters per second, a paper tape punch with an output capacity of 50 characters per second, and additional Teletype units. Provision is made for the addition of numerous peripheral devices. These include standard DEC peripherals as well as other devices which will be unique to the PDP-11.

#### SYSTEM INTERACTION

At any point in time only one device can be in control of the bus, or be bus master. The master communicates with another device on the bus which is called the slave. Usually, the established master will communicate with the slave in the form of data transfers.

Full 16-bit words or 8-bit bytes of information can be transferred on the bus between the master and the slave. The information can be instructions, addresses, or data. This type of operation occurs when the processor, as master, is fetching instructions, operands, and data from memory, and restoring the results into memory after execution of instructions. Direct data transfers occur between a disk control and memory.

**TRANSFER OF BUS MASTER**—When a device (other than the central processor) is capable of becoming bus master and requests use of the bus, it is generally for one of two purposes: 1) to make a non-processor transfer of data directly to or from memory, or 2) to interrupt program execution and force the processor to branch to a specific address where an interrupt service routine is located.

**PRIORITY STRUCTURE**—When a device capable of becoming bus master requests use of the bus, the handling of that request depends on the location of that device in the priority structure. These factors must be considered to determine the priority of the request:

- 1. The processor's priority can be set under program control to one of eight levels using bits 7, 6, and 5 in the processor status register. These three bits set a priority level that inhibits granting of bus requests on lower levels.

- 2. Bus requests from external devices can be made on one of five request lines. A non-processor request (NPR) has the highest priority, and its request is honored by the processor between bus cycles of an instruction execution. Bus request 7 (BR7) is the next highest priority, and BR4 is the lowest. The four lower level priority requests are honored by the processor between instructions. When the processor's priority is set to a level, for example 6, all bus requests on BR6 and below are ignored.

- 3. When more than one device is connected to the same bus request (BR) line, a device nearer the central processor has a higher priority than a device farther away. Any number of devices can be connected to a given BR or NPR line.

Once a device other than the processor has control of the bus, it may do one of two types of operations: 1) data transfers, 2) Interrupt operations.

NPR Data Transfers—NPR data transfers can be made between any two peripheral devices without the supervision of the processor. Normally, NPR transfers are between a mass storage device, such as a disk, and core memory. The structure of the bus also permits device-to-device transfers, allowing customer-designed peripheral controllers to access other devices such as disks directly.

Margan

An NPR device has very fast access to the bus and can transfer at high data rates once it has control. The processor state is not affected by the transfer; therefore the processor can relinquish control while an instruction is in progress. This can occur at the end of any bus cycle except in between a read-modify-write sequence. (See Chapter 8 for details). In the PDP-11, an NPR device can gain bus control in 3.5 microseconds or less. An NPR device in control of the bus may transfer 16-bit words from memory at memory speed or every 1.2 microseconds in the PDP-11/20 or every 1.0 microseconds in the PDP-11/10.

Interrupt Operations—Devices that request interrupts after getting bus control on the bus request lines (BR7, BR6, BR5, BR4) can take advantage of the power and flexibility of the processor. The entire instruction set is available for manipulating data and status registers. When a device servicing program must be run, the task currently under way in the central processor is interrupted and the device service routine is initiated. Once the device request has been satisfied, the processor returns to the interrupted task.

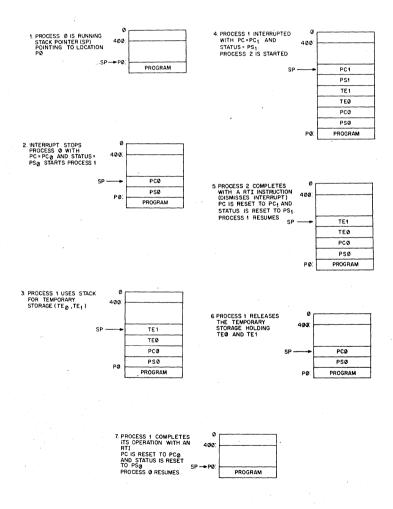

In the PDP-11, the return address for the interrupted routine and the processor status word are held in a "stack." A stack is a dynamic sequential list of data with special provision for access from one end. A stack is also called a "push down" or "LIFO" (Last-In First-Out) list. Storage and retrieval from stacks is called "pushing" and "popping" respectively. These operations are illustrated in Figure 2-1.

In the PDP-11, a stack is automatically maintained by the hardware for interrupt processing. Thus, higher level requests can interrupt the processing of lower level interrupt service, and automatically return control to the lower level interrupt service routines when the higher level servicing is completed.

Here is an example of this procedure. A peripheral requires service and requests use of the bus at one of the BR levels (BR7, BR6, BR5, BR4). The operations undertaken to "service" the device are as follows:

Fig 2-1 Illustration of Push and Pop Operations

8

- 1. Priorities permitting, the processor relinquishes the bus to the device.

- 2. When the device has control of the bus, it sends the processor interrupt command with the address of the words in memory containing the address and status of the appropriate device serv routine.

- The processor then "pushes"—first, the current central process status (PS) and then, the current program counter (PC) onto t processor stack.

- 4. The new PC and PS (the "interrupt vector") are taken from the loc tion specified by the device and the next location, and the devi

Figure 2-2 Nested Device Servicing

service routine is begun. Note that those operations all occur automatically and that no device-polling is required to determine which service routine to execute.

- 5. 7.2 microseconds is the time interval between the central processor's receiving the interrupt command and the fetching of the first instruction. This assumes there were no NPR transfers during this time.

- 6. The device service routine can resume the interrupted process by executing the RTI (Return from Interrupt) instruction which "pops" the processor stack back into the PC and PS. This requires 4.5 microseconds if there are no intervening NPR's.

- 7. A device service routine can be interrupted in turn by a sufficiently high priority bus request any time after completion of its first instruction.

- 8. If such an interrupt occurs, the PC and PS of the device service routine are automatically pushed into the stack and the new device routine initiated as above. This "nesting" of priority interrupts can go on to any level, limited only by the core available for the stack. More commonly, this process will nest only four levels deep since there are four levels of BR signals. An example of nested device servicing is shown in Figure 2-2. A rough core map is given for each step of the process. The SP points to the top word of the stack as shown.

### CHAPTER 3 ADDRESSING MODES

Most data in a program is structured in some way—in a table, in a stack, in a table of addresses, or perhaps in a small set of frequently-used variables local to a limited region of a program. The PDP-11 handles these common data structures with addressing modes specifically designed for each kind of access. In addition, addressing for unstructured data is general enough to permit direct random access to all of core.

Addressing in the PDP-11 is done through the general registers. Programs requiring several stacks can use the general registers for stack pointers. Those requiring many local variables can use general registers as accumulators. The general registers can be used interchangeably as index registers or as sequential list pointers to access tabular data. Address arithmetic may be done directly in the general registers.

#### SINGLE OPERAND ADDRESSING

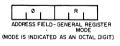

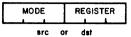

PDP-11 instruction words contain a 6-bit address field divided into two subfields selecting the general register and the mode of generating the effective address.

| _ |    | _    | OP  | FIEL | D   |       |      |   |   | ADDRESS | FIELD    |   |

|---|----|------|-----|------|-----|-------|------|---|---|---------|----------|---|

| Γ | }  | 1    | 1   | 1    | ł   | Ţ     | T    | 1 | 1 | MODE    | REGISTER |   |

| _ | IN | STRU | стю | NW   | ORD | (10 B | ITS) |   |   |         |          | - |

The register subfield specifies which of the eight general registers is to be used in the address calculation. The mode subfield indicates how this register is to be used in determining the operand. These modes will be described in the following paragraphs.

**GENERAL REGISTER ADDRESSING**—The general registers can be used as simple accumulators for operating on frequently-accessed variables. In this mode, the operand is held directly in the general register. The general registers are in fast memory, resulting in a speed improvement for operations on these variables.

PAL-11, the PDP-11 assembler, interprets instructions of the form

OPR R

as general register operations. R has been defined as a register name and OPR is used to represent a general instruction mnemonic. The address field for general register operations is

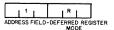

#### DEFERRED ADDRESSING

Operands that are pointed to by addresses (indirect or deferred) are denoted to the assembler by the @ symbol. Thus, instructions of the form

#### OPR @R or OPR (R)

specify deferred register addressing and have the following address field.

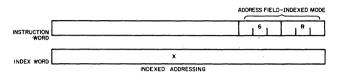

**INDEXED AND DEFERRED INDEXED ADDRESSING**—The general registers may be used as index registers to permit random access of items in tables or stacks of data. Instructions of the form

#### OPR X(R)

specify indexed mode addressing. The effective address is the sum of X and the contents of the specified general register R.

The index word containing X follows the instruction word.

Index mode addressing can be deferred to permit access of data elements through tables or stacks of their addresses. The address field for index deferred mode is

|               | R                |

|---------------|------------------|

| ADDRESS FIELD | DEFERRED INDEXED |

It is specified by instructions of the form

#### OPR @X(R)

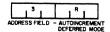

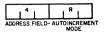

AUTOINCREMENT AND DEFERRED AUTOINCREMENT ADDRESSING—Autoincrement addressing provides for automatic stepping of a pointer through sequential elements of a table of operands. In this mode, the address of the operand is taken from the general register and then the contents of the register are stepped (incremented by one or two) to address the next word or byte depending upon whether the instruction operates on byte or word data. Instructions of the form

OPR (R)+

specify autoincrement addressing. The address field for autoincrement addressing is

ADDRESS FIELD- AUTOINCREMENT

This mode may also be deferred. Instructions of the form

OPR @(R)+

specify deferred autoincrement addressing and assemble with the following address field. In this case, the register points to a location which contains the effective address of the operand.

AUTODECREMENT AND DEFERRED AUTODECREMENT ADDRESSING— Autodecrement addressing steps the specified general register to the next (decrement by two) address and uses the new contents of the general register as the operand address. Instructions of the form

OPR - (R)

specify autodecrement addressing. The address field for autodecrement addressing is

This mode also may be deferred and specified by instructions of the form OPR @ -(R). When deferred the address field is

#### STACK PROCESSING

The combination of autoincrement addressing in which the general register is stepped forward after the operand address is determined and autodecrement addressing in which the general register is stepped backward before the operand address is determined is the basic requirement for convenient low overhead stack operations.

The PDP-11 has extensive stack processing capabilities. The stack pointer SP (R6), maintains a stack for the nested handling of interrupts and subroutine calls. All of the general registers can maintain stacks under program control. Elements in the middle of stacks may be accessed through indexed addressing. This provides for convenient access of dynamically assigned temporary storage, especially useful in nested procedures.

#### **USE OF THE PC AS A GENERAL REGISTER**

There are special implications in the use of the addressing modes already described when applied to the PC (that is, to R7). The use of the PC with the addressing modes described above generates immediate, direct, relative, and deferred relative addressing.

**IMMEDIATE ADDRESSING**—Immediate addressing provides time and space improvement for access of constant operands by including the constant in the instruction. The instruction word referencing an immediate operand specifies autoincrement addressing through the program counter. The address field would be

ADDRESS FIELD-IMMEDIATE MODE

The program counter points to the word after the instruction word following the instruction fetch. The contents of this word are therefore used as the operand and the program counter is advanced to the next word. PAL-11 recognizes address expressions of the form "#n" as immediate operands and codes them with the address field shown above followed by a word of data.

A full word is assembled for immediate operands even in byte instructions so that instruction words are always fetched from even locations.

ABSOLUTE ADDRESSING-The contents of the location following the instruc-

tion word may be taken as the address of an operand by specifying deferral in immediate mode addressing. That is, instructions of the form

OPR @#A

refer to the operand at address A. The assembler places address expressions of this form into an instruction with address field

| 3                           | 7 |  |  |  |  |  |

|-----------------------------|---|--|--|--|--|--|

| ADDRESS FIELD-ABSOLUTE MODE |   |  |  |  |  |  |

followed by a word containing the operand address.

**RELATIVE ADDRESSING**—Relative addressing specifies an operand address relating the program counter to the referenced instruction location. This is done by using the PC as a base register. The offset, which is calculated by subtracting the program counter's contents from the address of the referenced location, is <u>retained</u> in the index word of the instruction. The assembler operates on instructions of the form:

OPR A

(where A has not been assigned as a name of a general register) as an instruction word with the address field

followed by an index word of the form

A-ADDRESS OF THIS WORD-2

**DEFERRED RELATIVE ADDRESSING**—Deferral of relative addressing permits access to data through memory locations holding operand addresses. The "@" character specifies deferred addressing; i.e., OPR @A. The address field for deferred relative addressing is

#### USE OF THE SP AS A GENERAL REGISTER

The processor stack pointer will in most cases be the general register used for PDP-11 stack operations. Note that —(SP) will push data onto the stack, that (SP) + will pop data off the stack, and that X(SP) will permit random access of items on the stack. Since the SP is used by the processor for interrupt handling, it has a special attribute: autoincrements and autodecrements are always done in steps of two. Byte operations using the SP in this way will simply leave odd addresses unmodified.

#### DOUBLE OPERAND ADDRESSING

Operations which imply two operands such as add, subtract and compare are presented in the PDP-11 by instructions which specify two addresses. The instruction word for such operations is of the form

| OP FIELD | SOURCE ADDRESS FIELD | DESTINATION ADDRESS FIELD |

|----------|----------------------|---------------------------|

|          |                      |                           |

|          |                      |                           |

INSTRUCTION WORD- DOUBLE OPERAND INSTRUCTIONS

Instruction Word—Double Operand Instructions

and is followed by index words and immediate operands for the source and destination address fields as appropriate. Source address calculations are performed before destination address calculations. The addressing modes are as for single operand instructions, and are described below. Addressing modes can be mixed in the same instruction. The source address and destination address can be any combination of modes. Since each operand may be anywhere in core storage or in the general registers, each memory location is thus effectively provided with the arithmetic capabilities of an accumulator. Further, since peripheral device registers and memory location are addressed in the same way, the contents of peripheral data buffers can be stored or loaded directly to and from memory without use of any general register. This means that interrupt routines can be executed without saving and restoring any of the general registers.

#### GENERAL REGISTER ADDRESSING

OPR RX,RY

is interpreted by the assembler as a register mode, and signifies that the source address is a general register, as is the destination address.

#### DEFERRED ADDRESSING

OPR @RX, @RY

or

OPR (RX), (RY)

specifies that the source register contains the effective address of the source operand, and the destination register contains the effective address of the destination operand.

#### INDEXED AND DEFERRED INDEXED ADDRESSING

OPR A(RX), B(RY)

specifies that the effective address of the source operand is given by logically adding (in 2's complement) the value of A to register RX. The destination address is defined by the sum of the value of B and the contents of register RY.

When the instruction is of the form

OPR @A(RX), @B(RY)

then the above operations define the address of the location which in turn contains the effective address, rather than being the effective address.

#### AUTOINCREMENT AND DEFERRED AUTOINCREMENT ADDRESSING

OPR (RX) +, (RY) +

implies that the effective address of the source operand is in register RX and the effective address of the destination operand is in register RY. After the addresses have been fetched from the registers, the registers are incremented automatically by two (or by one for byte instructions).

OPR @(RX) +, @(RY) +

implies the same as above, except that the addresses in the registers are the addresses of locations which in turn contain the addresses of the operands.

#### AUTODECREMENT AND DEFERRED AUTODECREMENT ADDRESSING

uses the registers as in autoincrement mode except that the contents are decremented by two (or one for byte instructions) before the contents of the registers are used as operand addresses.

OPR @-(RX), @-(RY)

uses the registers as in autodecrement mode except that the contents of the register is a pointer to the *address* of the operand rather than to the operand itself.

#### IMMEDIATE ADDRESSING

OPR #C, DEST ADDRESS

is a special case of

OPR (RX)+, DEST ADDRESS

where RX is Register 7 (the PC). In this case, the source address is the memory location following the instruction and the constant "C" is the operand.

#### ABSOLUTE ADDRESSING

OPR @#A, DEST ADDRESS

is a special case of

#### OPR @(RX)+, DEST ADDRESS

where RX is Register 7. The memory location following the instruction contains the effective address (points to the operand).

#### RELATIVE AND DEFERRED RELATIVE ADDRESSING

OPR A, DEST ADDRESS

is a special case of

#### OPR X(RX), DEST ADDRESS

where RX is Register 7 and X is an offset which, when logically added to the PC (which does not change the contents of the PC), results in the effective address. This mode aids the generation of relocatable programs.

OPR @A, DEST ADDRESS

is the equivalent of

#### OPR @X(RX), DEST ADDRESS

which differs from relative addressing in that the offset from the PC points at a location containing the address of the operand rather than the operand itself.

Deferred register addressing may also be selected in PAL-11 by the form  $\mathsf{OPR}$  (R).

## **CHAPTER 4** INSTRUCTION SET

This chapter presents the order code for the PDP-11. Each PDP-11 instruction is described in terms of five parameters: operation, effect on condition codes, base timing, assembler mnemonics, and octal representation. Special comments are included where appropriate.

#### NOTATION

The following notations will be used in this section:

| (XXX)         | : The contents of XXX                  |

|---------------|----------------------------------------|

| src           | : The Source Address                   |

| dst           | : The Destination Address              |

| Λ .           | : Boolean "AND" Function               |

| V .           | : Boolean "OR" Function                |

| ¥             | : Boolean "Exclusive OR" Function      |

| ~             | : Boolean 'NOT'' Function (Complement) |

| $\rightarrow$ | : ''becomes''                          |

| ↑             | : "is popped from the stack"           |

| ↓ .           | : ''is pushed onto the stack''         |

#### INSTRUCTION TIMING

The PDP-11 is an asynchronous processor in which, in many cases, memory and processor operations are overlapped. The execution time for an instruction is the sum of a basic instruction time and the time to determine and fetch the source and/or destination operands. The following table shows the addressing times required for the various modes of addressing source and destination operands. The instruction time for each operation is given (throughout this chapter) for the 11/20 configuration. All times stated are subject to  $\pm 20\%$  variation.

TIMING

#### ADDRESSING FORM

| DRESSING FORM    | TIMITING  |           |  |  |

|------------------|-----------|-----------|--|--|

| (src or dst)     | src (μs)† | dst (μs)† |  |  |

| R                | 0         | 0         |  |  |

| (R) or @R        | 1.5       | 1.4*      |  |  |

| (R) +            | 1.5       | 1.4*      |  |  |

| —(R)             | 1.5       | 1.4*      |  |  |

| @(R) +           | 2.7       | 2.6*      |  |  |

| @-(R)            | 2.7       | 2.6*      |  |  |

| BASE(R)          | 2.7       | 2.6*      |  |  |

| @BASE(R) or @(R) | 3.9       | 3.8*      |  |  |

\* dst time is 0.5 us. less than listed time if instruction was a

| <br>CoMPare, CoMPare Byte |

|---------------------------|

| Bit Test, Bit Test Byte   |

| <br>TeST, or TeST Byte    |

none of which ever modify the destination word. treferencing bytes at odd addresses adds 0.6µs to src and dst times.

**DOUBLE OPERAND INSTRUCTIONS**—Double Operand Instructions are represented in assembly language as:

#### OPR src. dst

where src and dst are the addresses of the source and destination operands respectively. The execution time for these operations is comprised of the source time, the destination time, and the instruction time. The source and destination times depend on addressing modes and are described in the preceding table.

#### Arithmetic Operations-

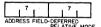

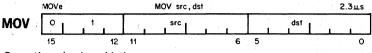

Operation: (src)  $\rightarrow$  (dst)

Condition Codes:

Z: set if (src) = 0; cleared otherwise N: set if (src) < 0; cleared otherwise C: not affected V: cleared

Description: Moves the source operand to the destination location. The previous contents of the destination are lost. The contents of the source are not affected.

The MOV instruction is a generalization of 'load," "store," "setup," 'push," "pop,' and interregister transfer operations.

General registers may be loaded with the contents of memory addresses with instructions of the form:

#### MOV src, R

Registers may be loaded with a counter, and pointer values with MOV instructions:

MOV #n, R

(which loads the number n into register R)

Operands may be pushed onto a stack by:

MOV src. -(R)

and may be popped off a stack by:

MOV (R)+, dst

Interregister transfers are simply:

MOV RA, RB

(RA and RB are general registers)

Memory-to-memory transfers may be done with the MOV instruction in the general form:

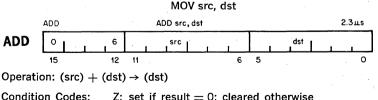

Z: set if result = 0; cleared otherwise

N: set if result < 0; cleared otherwise

- C: set if there was a carry from the most significant bit of the result; cleared otherwise

- V: set if there was arithmetic overflow as a result of the operation, that is, if both operands were of the same sign and the result was of the opposite sign; cleared otherwise

Description: Adds the source operand to the destination operand and stores the result at the destination address. The original contents of the destination are lost. The contents of the source are not affected. Two's complement addition is performed.

The ADD instruction includes as special cases the "add-to-register," "add-tomemory," and "add-register-to-register" functions:

| Add-to-Register          | ADD src, R |

|--------------------------|------------|

| Add-to-Memory            | ADD R, dst |

| Add Register-to-Register | ADD RA, RB |

Arithmetic may also be done directly in memory by the general form ADD instruction

ADD src. dst

Use of this form saves considerable loading and storing of accumulators.

Two special cases of the ADD instruction are particularly useful in compilers, interpreters, and other stack arithmetic processes:

#### ADD (R)+, (R)

#### (where R is the stack pointer)

which replaces the top two elements of the stack with their sum; and ADD src, (R), which increases the top element of the stack by the contents of the source address.

The "Add Immediate" operation is yet another special case of this generalized ADD instruction:

Immediate operations are useful in dealing with constant operands. Note that:

ADD #n, R

steps the register R (which may be an index register) through n addresses eliminating the need for a special "add-to-index- register" instruction.

All these special cases of the ADD instruction apply equally well to the other double operand instructions that follow.

| SUBtract |    |    | SUB src, dst |   |   |     | 2.3 µ.s |     |

|----------|----|----|--------------|---|---|-----|---------|-----|

| 1        | 6  |    | src          | 1 |   | dst |         | SUB |

| 15       | 12 | 11 |              | 6 | 5 |     | 0       |     |

Operation: (dst) — (src)  $\rightarrow$  (dst) [in detail, (dst) +  $\sim$  (src) + 1  $\rightarrow$  (dst)] Condition Codes:

Z: set if result = 0; cleared otherwise

N: set if result < 0; cleared otherwise

- C: cleared if there was a carry from the most significant bit of the result: set otherwise

- V: set if there was arithmetic overflow as a result of the operation, that is, if the operands were of opposite signs and the sign of source was the same as the sign of the result; cleared otherwise.

Description: Subtracts the source operand from the destination operand and leaves the result at the destination address. The original contents of the destination are lost. The contents of the source are not affected.

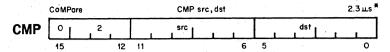

Operation: (src) — (dst) [in detail, (src) +  $\sim$  (dst) + 1] Condition Codes: Z: set if result = 0; cleared otherwise

- N: set if result < 0; cleared otherwise

- C: cleared if there was a carry from the most significant bit of the result; set otherwise

- V: set if there was arithmetic overflow; that is, operands were of opposite signs and the sign of the destination was the same as the sign of the result; cleared otherwise.

Description: Arithmetically compares the source and destination operands. Affects neither operand. The only action is to set the condition codes appropriately.

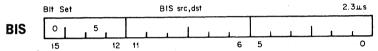

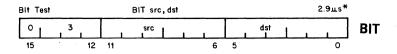

**Boolean Instructions**—These instructions have the same format as the double operand arithmetic group. They permit operations on data at the bit level.

Operation: (src) V (dst)  $\rightarrow$  (dst)

Condition Codes:

Z: set if result = 0; cleared otherwise

- N: set if high-order bit of result set; cleared otherwise

- C: not affected

- V: cleared

Description: Performs "Inclusive OR" transfer between the source and destination operands and leaves the result at the destination address; that is, corresponding bits set in the source are set in the destination. The original contents of the destination are lost. The source is not affected.

Operation:  $\sim$  (src)  $\land$  (dst)  $\rightarrow$  (dst)

Conditions Codes:

Z: set if result = 0; cleared otherwise

- N: set if high-order bit of result set; cleared otherwise C: not affected

- V: cleared