# NVAX Plus CPU Chip Functional Specification

The NVAX Plus CPU Chip is a high-performance, single-chip implementation of the VAX Architecture for use in low-end and mid-range systems.

Sevision/Update Information:

This is Revision 0.3 of this specification, the third external release

#### DIGITAL CONFIDENTIAL

This information shall not be disclosed to persons other than DIGITAL employees or generally distributed within DIGITAL. Distribution is restricted to persons authorized and designated by the originating organization. This document shall not be transmitted electronically, copied unless authorized by the originating organization, or left unattended. When not in use, this document shall be stored in a locked storage area. These restrictions are enforced until this document is reclassified by the originating organization.

Semiconductor Engineering Group Digital Equipment Corporation, Hudson, Massachusetts

#### October 1991

The drawings and specifications in this document are the property of Digital Equipment Corporation and shall not be reproduced or copied or used in whole or in part as the basis for the manufacture or sale of items without written permission.

The information in this document may be changed without notice and is not a commitment by Digital Equipment Corporation. Digital Equipment Corporation is not responsible for any errors in this document.

This specification does not describe any program or product that is currently available from Digital Equipment Corporation, nor is Digital Equipment Corporation committed to implement this specification in any program or product. Digital Equipment Corporation makes no commitment that this document accurately describes any product it might ever make.

> Copyright ©1991 by Digital Equipment Corporation All Rights Reserved Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation:

DEC DECnet DECUS MicroVAX MicroVMS PDP ULTRIX ULTRIX-32 UNIBUS VAX VAXBI VAXCluster VAXstation VMS VT

| CHAPTER 1 | INTRODUCTION                                                                                                                                                                                                                | 1–1                                                         |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--|

| 1.1       | SCOPE AND ORGANIZATION OF THIS SPECIFICATION                                                                                                                                                                                |                                                             |  |

| 1.2       | RELATED DOCUMENTS                                                                                                                                                                                                           | 1-1                                                         |  |

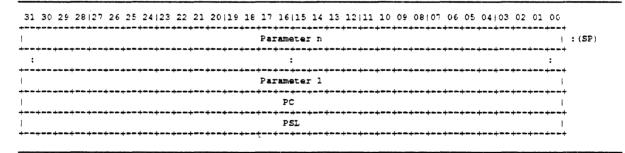

| 1.3       | TERMINOLOGY AND CONVENTIONS1.3.1Numbering1.3.2UNPREDICTABLE and UNDEFINED1.3.3Ranges and Extents1.3.4Must be Zero (MBZ)1.3.5Should be Zero (SBZ)1.3.6Register Format Notation1.3.7Timing Diagram Notation                   | 1-2<br>1-2<br>1-2<br>1-2<br>1-2<br>1-2<br>1-2<br>1-3<br>1-5 |  |

| 1.4       | REVISION HISTORY                                                                                                                                                                                                            | 1—6                                                         |  |

| CHAPTER 2 | ARCHITECTURAL SUMMARY                                                                                                                                                                                                       | 2–1                                                         |  |

| 2.1       | OVERVIEW                                                                                                                                                                                                                    |                                                             |  |

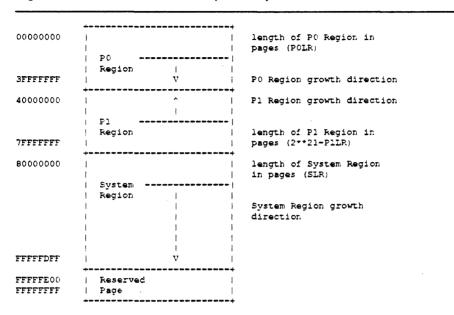

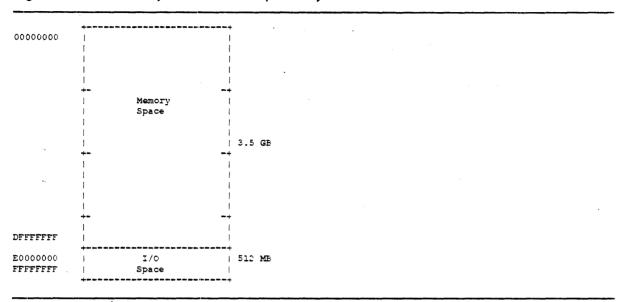

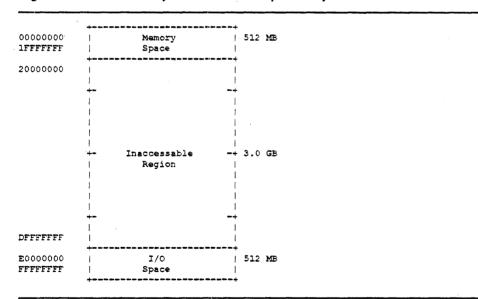

| 2.2       | VISIBLE STATE<br>2.2.1 Virtual Address Space<br>2.2.2 Physical Address Space<br>2.2.2.1 Physical Address Control Registers • 2–4<br>2.2.3 Registers                                                                         | 2–1<br>2–1<br>2–2<br>2–4                                    |  |

| 2.3       | DATA TYPES                                                                                                                                                                                                                  | 2–6                                                         |  |

| 2.4       | INSTRUCTION FORMATS AND ADDRESSING MODES<br>2.4.1 Opcode Formats<br>2.4.2 Addressing Modes<br>2.4.3 Branch Displacements                                                                                                    | 2-8<br>2-8<br>2-8<br>2-11                                   |  |

| 2.5       | INSTRUCTION SET                                                                                                                                                                                                             | 2–11                                                        |  |

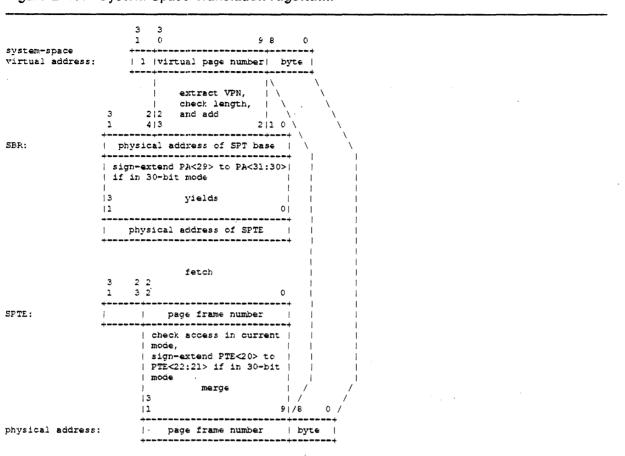

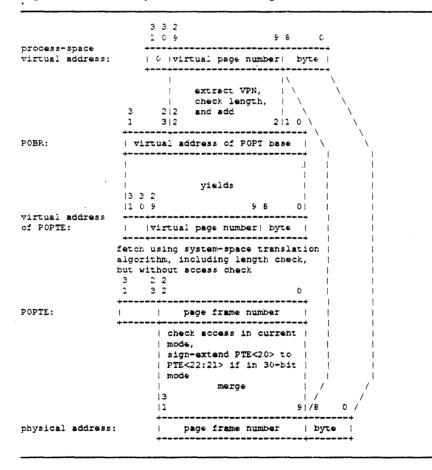

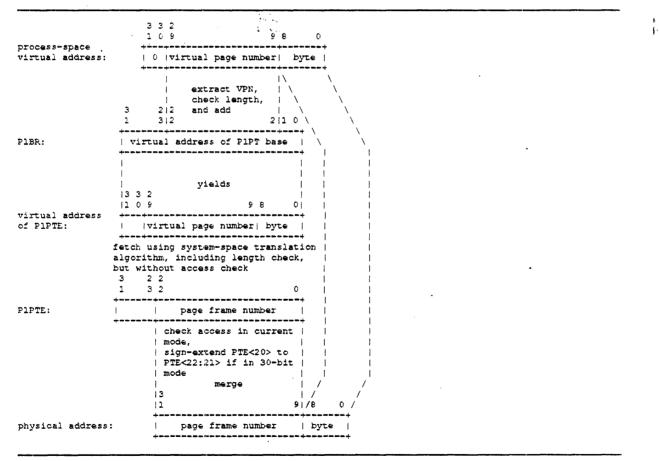

| 2.6       | MEMORY MANAGEMENT2.6.1Memory Management Control Registers2.6.2System Space Address Translation2.6.3Process Space Address Translation.2.6.3.1P0 Region Address Translation • 2–272.6.3.2P1 Region Address Translation • 2–28 | 2–25<br>2–25<br>2–26<br>2–27                                |  |

|           | 2.6.4 Page Table Entry<br>2.6.5 Translation Buffer                                                                                                                                                                          | 2–30<br>2–31                                                |  |

| 2.7       | 2.6.5       Translation Buffer         EXCEPTIONS AND INTERRUPTS         2.7.1       Interrupts         2.7.1.1       Interrupt Control Registers • 2–33                                                                    | 2–31<br>2–32<br>2–32                                        |  |

III

|           | 2.7.2                                                         | Exceptions2.7.2.1Arithmetic Exceptions • 2–352.7.2.2Memory Management Exceptions • 2–362.7.2.3Emulated Instruction Exceptions • 2–372.7.2.4Machine Check Exceptions • 2–392.7.2.5Console Halts • 2–39                                                                                                                                                                                                | 2–34                                   |

|-----------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 2.8       | SYSTEM (<br>2.8.1<br>2.8.2                                    | CONTROL BLOCK<br>System Control Block Vectors<br>System Control Block Layout                                                                                                                                                                                                                                                                                                                         | 240<br>240<br>241                      |

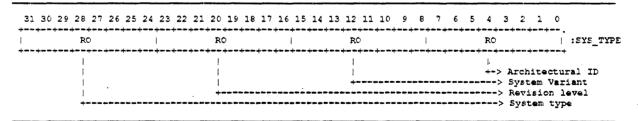

| 2.9       | CPU IDEN                                                      | TIFICATION                                                                                                                                                                                                                                                                                                                                                                                           | 2-43                                   |

| 2.10      | SYSTEM I                                                      | DENTIFICATION                                                                                                                                                                                                                                                                                                                                                                                        | 2-43                                   |

| 2.11      | PROCESS                                                       | STRUCTURE                                                                                                                                                                                                                                                                                                                                                                                            | 2-46                                   |

| 2.12      | MAILBOX<br>2.12.1                                             | STRUCTURE<br>Mailbox Operation                                                                                                                                                                                                                                                                                                                                                                       | 248<br>250                             |

| 2.13      | PROCESS                                                       | OR REGISTERS                                                                                                                                                                                                                                                                                                                                                                                         | 2–52                                   |

| 2.14      | REVISION                                                      | HISTORY                                                                                                                                                                                                                                                                                                                                                                                              | 2-63                                   |

| CHAPTER 3 | EXTERNA                                                       | L INTERFACE                                                                                                                                                                                                                                                                                                                                                                                          | 3—1                                    |

| 3.1       | OVERVIEW                                                      |                                                                                                                                                                                                                                                                                                                                                                                                      |                                        |

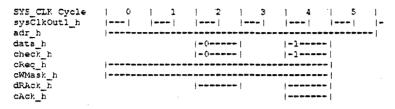

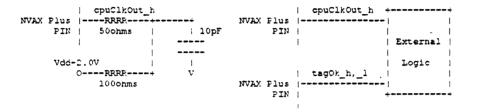

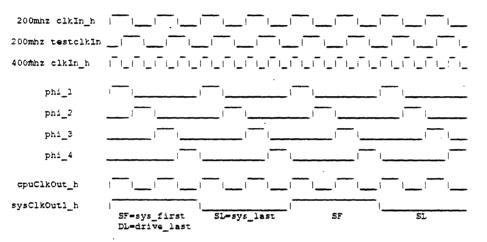

| 3.2       | SIGNALS<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6 | Clocks<br>DC_OK and Reset<br>Initialization and Diagnostic Interface<br>Address Bus<br>Data Bus<br>External Cache Control<br>3.2.6.1 The TagAdr RAM • 3-8<br>3.2.6.2 The TagCtl RAM • 3-8<br>3.2.6.3 The Data RAM • 3-9<br>3.2.6.4 Backmaps • 3-10<br>3.2.6.5 External Cache Access • 3-10<br>3.2.6.5 External Cache Access • 3-10<br>3.2.6.5.1 HoldReq and HoldAck • 3-10<br>3.2.6.5.2 TagOk • 3-11 | 3-1<br>3-4<br>3-5<br>3-6<br>3-6<br>3-7 |

|           | 3.2.7<br>3.2.8<br>3.2.9<br>3.2.10<br>3.2.11                   | External Cycle Control<br>Primary Cache Invalidate<br>Interrupts<br>Electrical Level Configuration<br>Testing                                                                                                                                                                                                                                                                                        | 3-12<br>3-15<br>3-16<br>3-16<br>3-16   |

| 3.3       | 64-BIT MC                                                     | DE                                                                                                                                                                                                                                                                                                                                                                                                   | 3–16                                   |

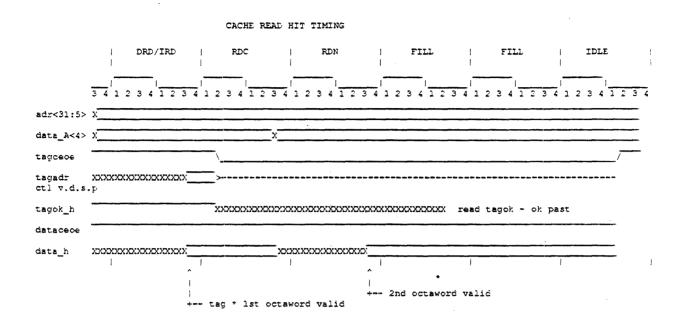

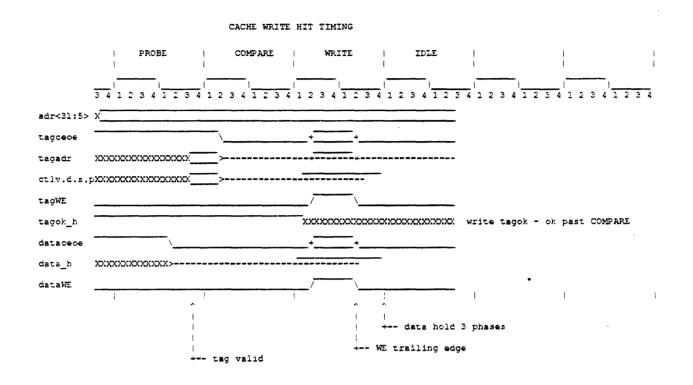

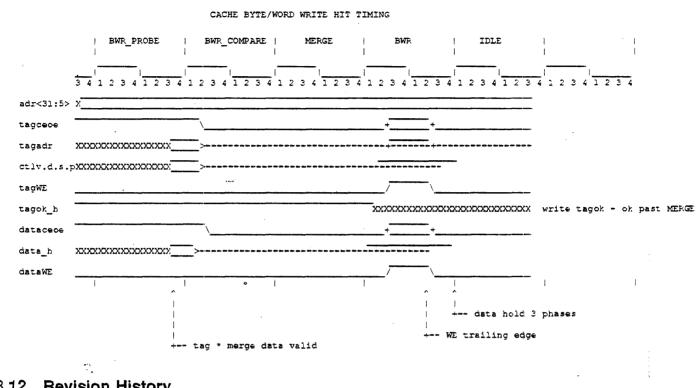

| 3.4       | TRANSAC<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5          | CTIONS<br>Reset<br>Fast External Cache Read Hit<br>Fast External Cache Write Hit<br>Fast External Cache Byte/Word Write Hit<br>Transfer to SysCik for External tranactions                                                                                                                                                                                                                           | 316<br>316<br>319<br>319<br>320<br>320 |

.

|           | 3.4.6          | READ_BLOCK Transaction                                                                                                                                                                                                                                                                                                                                                                                         | 3-21         |

|-----------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

|           | 3.4.7 \        | Nrite Block                                                                                                                                                                                                                                                                                                                                                                                                    | 3-22         |

|           | 3.4.8 1        | DxL Transaction                                                                                                                                                                                                                                                                                                                                                                                                | 3-23         |

|           | 3.4.9 5        | STxC Transaction                                                                                                                                                                                                                                                                                                                                                                                               | 3–23         |

|           | 3.4.10         | BARRIER Transaction                                                                                                                                                                                                                                                                                                                                                                                            | 3-24         |

|           | 3.4.11 F       | ETCH Transaction                                                                                                                                                                                                                                                                                                                                                                                               | 3-24         |

|           | 3.4.12         | ETCHM Transaction                                                                                                                                                                                                                                                                                                                                                                                              | 3–24         |

| 3.5       | SUMMARY        | OF NVAX PLUS OPTIONS                                                                                                                                                                                                                                                                                                                                                                                           | <b>3–2</b> 5 |

|           |                | System Clock Divisors                                                                                                                                                                                                                                                                                                                                                                                          | 3-25         |

|           | 3.5.2 0        | Cache Access                                                                                                                                                                                                                                                                                                                                                                                                   | <b>3–2</b> 5 |

|           | 3.5.3 F        | Flamingo I/O Address Mapping                                                                                                                                                                                                                                                                                                                                                                                   | 3-25         |

|           | 3.5.4 I        | Direct Mapped Pcache                                                                                                                                                                                                                                                                                                                                                                                           | 3-25         |

|           | 3.5.5 <b>s</b> | adr_h<33:32>                                                                                                                                                                                                                                                                                                                                                                                                   | 3-25         |

|           | 3.5.6 (        | 2W I/O WRITES/MTPR MAILBOX                                                                                                                                                                                                                                                                                                                                                                                     | 3-26         |

|           | 3.5.7 0        | 2W I/O READS                                                                                                                                                                                                                                                                                                                                                                                                   | 3-26         |

|           | 3.5.8          | PV mode                                                                                                                                                                                                                                                                                                                                                                                                        | 326          |

| 3.6       | REVISION H     | IISTORY                                                                                                                                                                                                                                                                                                                                                                                                        | 3-27         |

| CHAPTER 4 | CHIP OVER      | VIEW                                                                                                                                                                                                                                                                                                                                                                                                           | 4-1          |

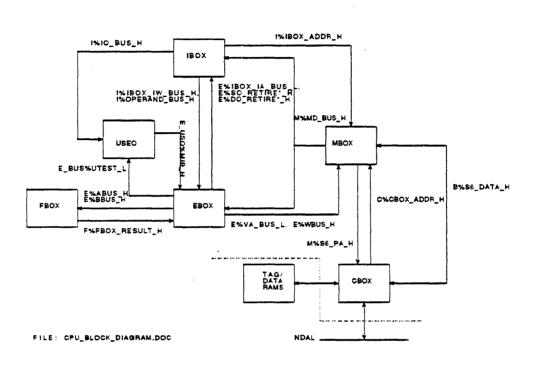

| 4.1       | NVAX PLUS      | CPU CHIP BOX AND SECTION OVERVIEW                                                                                                                                                                                                                                                                                                                                                                              | 41           |

|           | 4.1.1 1        | The Ibox                                                                                                                                                                                                                                                                                                                                                                                                       | 4-2          |

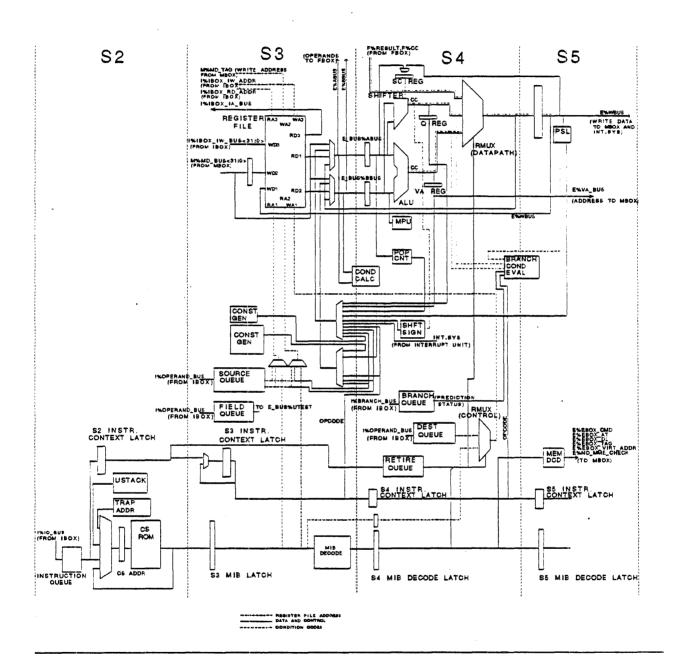

|           | 4.1.2 1        | The Ebox and Microsequencer                                                                                                                                                                                                                                                                                                                                                                                    | 43           |

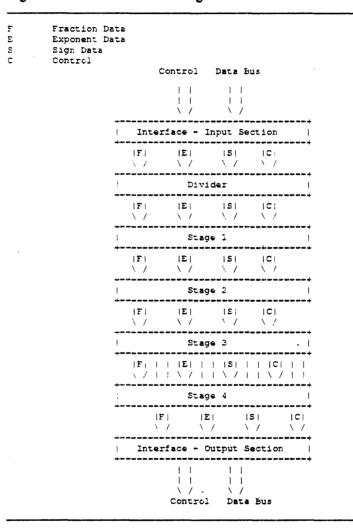

|           | 4.1.3          | The Fbox                                                                                                                                                                                                                                                                                                                                                                                                       | 4-3          |

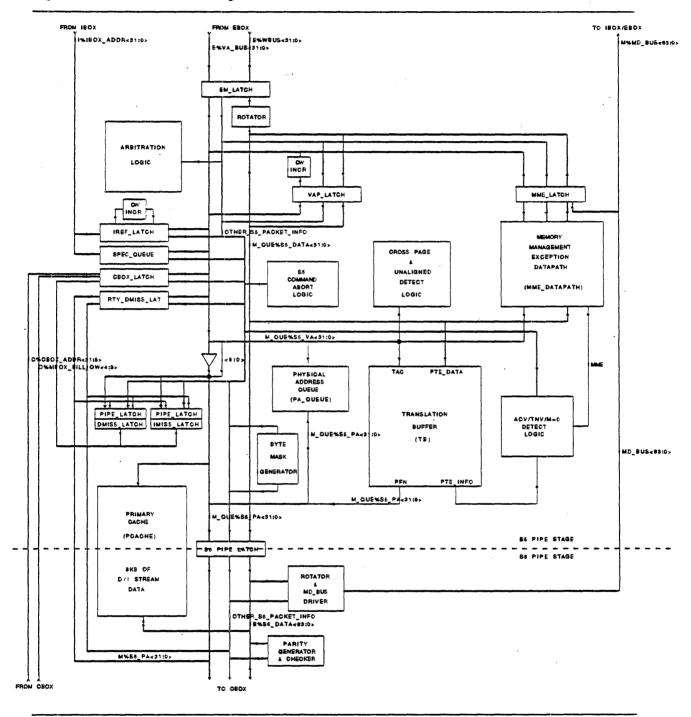

|           | 4.1.4          | Гне Мьох                                                                                                                                                                                                                                                                                                                                                                                                       | 4-4          |

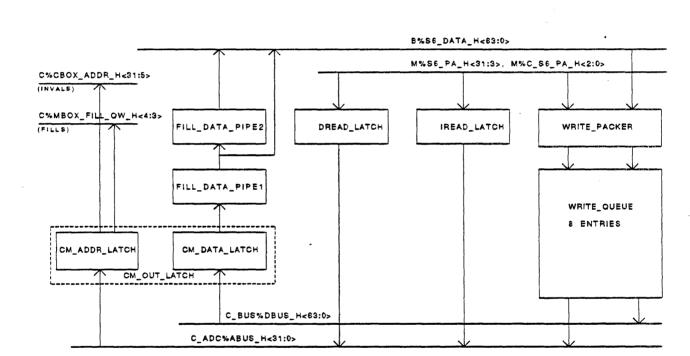

|           | 4.1.5          | The Cbox                                                                                                                                                                                                                                                                                                                                                                                                       | 4-4          |

|           | 4.1.6          | Major Internal Buses                                                                                                                                                                                                                                                                                                                                                                                           | 4-4          |

| 4.2       | REVISION H     | IISTORY                                                                                                                                                                                                                                                                                                                                                                                                        | 45           |

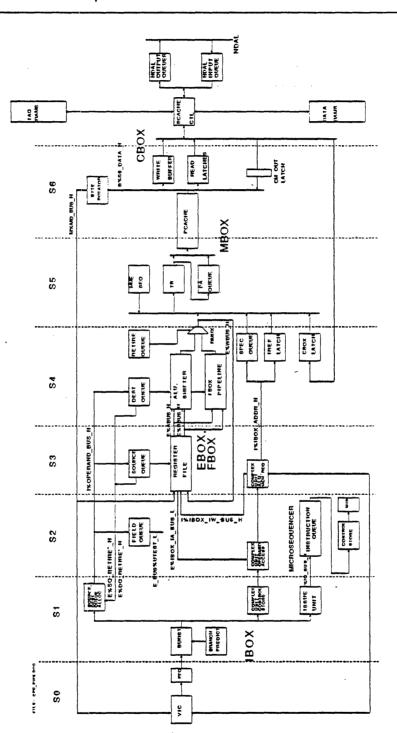

| CHAPTER 5 | MACROINS       | TRUCTION AND MICROINSTRUCTION PIPELINES                                                                                                                                                                                                                                                                                                                                                                        | 5—1          |

| 5.1       | INTRODUCT      | FION CONTRACT OF CONTRACT. | 5-1          |

| 5.2       |                | UNDAMENTALS                                                                                                                                                                                                                                                                                                                                                                                                    | 5–1          |

|           |                | The Concept of a Pipeline                                                                                                                                                                                                                                                                                                                                                                                      | 5-1          |

|           |                | Pipeline Flow                                                                                                                                                                                                                                                                                                                                                                                                  | 5-3          |

|           |                | Stalls and Exceptions in an Instruction Pipeline                                                                                                                                                                                                                                                                                                                                                               | 5-5          |

| 5.3       | NVAX PLUS      | CPU PIPELINE OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                          | 56           |

| -         | 5.3.1          | Normal Macroinstruction Execution                                                                                                                                                                                                                                                                                                                                                                              | 56           |

|           |                | 5.3.1.1 The lbox • 5-6                                                                                                                                                                                                                                                                                                                                                                                         |              |

|           | ţ              | 5.3.1.2 The Microsequencer • 5-8                                                                                                                                                                                                                                                                                                                                                                               |              |

|           | 5              | 5.3.1.3 The Ebox • 5–9                                                                                                                                                                                                                                                                                                                                                                                         |              |

|           | ŧ              | 5.3.1.4 The Fbox • 5–10                                                                                                                                                                                                                                                                                                                                                                                        |              |

# 5.3.1.5The Mbox • 5-105.3.1.6The Cbox • 5-11

# DIGITAL CONFIDENTIAL

.

v

|           | 5.3.2    | Stalls in th | e Pipeline                                                       | 5–11     |

|-----------|----------|--------------|------------------------------------------------------------------|----------|

|           |          | 5.3.2.1      | S0 Stalls · 5-12                                                 |          |

|           |          | 5.3.2.2      | S1 Stalls • 5–12                                                 |          |

|           |          | 5.3.2.3      | S2 Stalls • 5–13                                                 |          |

|           |          | 5.3.2.4      | S3 Stalls · 5-13                                                 | <i>i</i> |

|           |          | 5.3.2.5      | S4 Stalls • 5-14                                                 |          |

|           | 5.3.3    | Exception    | Handling                                                         | 5-15     |

|           |          |              | Interrupts • 5–16                                                |          |

|           |          |              | Integer Arithmetic Exceptions • 5–17                             |          |

|           |          |              | Floating Point Arithmetic Exceptions • 5–17                      |          |

|           |          |              | Memory Management Exceptions • 5-17                              |          |

|           |          |              | Translation Buffer Miss • 5–19                                   |          |

|           |          |              | Reserved Addressing Mode Faults • 5-19                           |          |

|           |          |              | Reserved Operand Faults • 5-20                                   |          |

|           |          |              | Exceptions Occurring as the Consequence of an Instruction • 5-20 |          |

|           |          |              | Trace Fault • 5-20                                               |          |

|           |          |              | Conditional Branch Mispredict • 5–20                             | c        |

|           |          |              | First Part Done Handling • 5-21                                  |          |

|           |          | 5.3.3.12     | Cache and Memory Hardware Errors • 5-21                          |          |

| 5.4       | REVISION | HISTORY      |                                                                  | 5-22     |

| CHAPTER 6 | MICROINS | TRUCTION     | FORMATS                                                          | 61       |

|           |          |              |                                                                  |          |

| 6.1       | EBOX MIC |              |                                                                  | 6-1      |

|           | 6.1.1    | Data Path (  |                                                                  | 6-1      |

|           | 6.1.2    | Microseque   | ancer Control                                                    | 63       |

| 6.2       | IBOX CSU | MICROCOD     | DE                                                               | 64       |

| 6.3       | REVISION | HISTORY      |                                                                  | 6-5      |

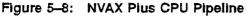

| CHAPTER 7 | THE IBOX |              |                                                                  | 7–1      |

| 7.1       | OVERVIE  | N            |                                                                  | 7-1      |

|           | 7.1.1    | introductio  | n                                                                | 7-1      |

|           | 7.1.2    | Functional   |                                                                  | 7-2      |

|           |          |              |                                                                  | ,        |

| 7.2       |          |              | RROR REGISTERS                                                   | 7-4      |

| 7.3       |          |              | MONITORING HARDWARE                                              | 7–6      |

| 7.4       | IBOX IPR | TRANSACTI    | ONS                                                              | 7-7      |

|           | 7.4.1    | IPR Reads    |                                                                  | 7-7      |

|           | 7.4.2    | IPR Writes   |                                                                  | 7_7      |

| 7.5       | BRANCH   | PREDICTION   | IPR REGISTER                                                     | 78       |

| 7.6       | TESTABIL | ITY.         |                                                                  | 7-9      |

|           | 7.6.1    | Overview     |                                                                  | 7-9      |

|           | 7.6.2    | Internal Sc  | an Register and Data Reducer                                     | 7-9      |

|           | 7.6.3    | Parallel Po  | -                                                                | 7–10     |

|           | 7.6.4    |              | ral Features                                                     | 7-10     |

|           | 7.6.5    | Metal 3 No   |                                                                  | 7-10     |

|           | 7.6.6    | Issues       |                                                                  | 7-10     |

vi

| Cont | ents |

|------|------|

|------|------|

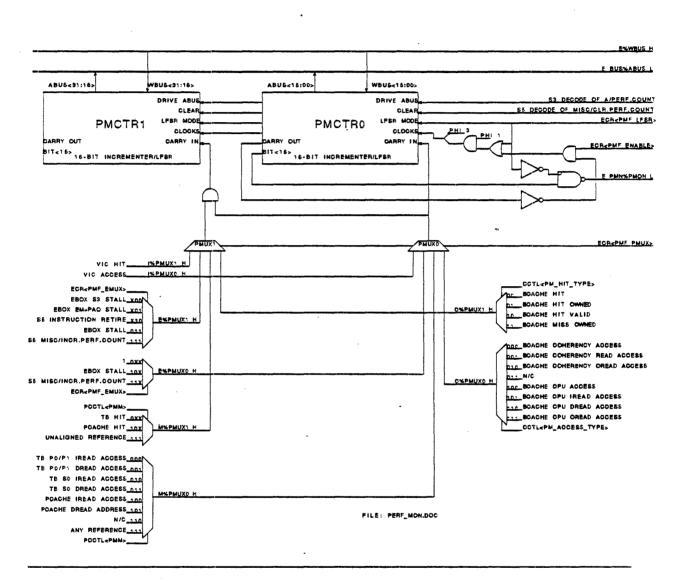

| 7.7       | PERFORM  | MANCE MON<br>Signals | ITORING HARDWARE                                                                                  | 7–10<br>7–10    |

|-----------|----------|----------------------|---------------------------------------------------------------------------------------------------|-----------------|

| 7.8       | REVISION | HISTORY              |                                                                                                   | 7–11            |

| 7.0       | REVISION | nistoni              |                                                                                                   | /=11            |

| CHAPTER 8 | THE EBO  | X                    |                                                                                                   | 8—1             |

| 8.1       | CHAPTER  | R OVERVIEW           |                                                                                                   | , <b>8—1</b>    |

| 8.2       | INTRODU  | CTION                |                                                                                                   | 8-1             |

| 8.3       | EBOX OV  | ERVIEW               |                                                                                                   | 84              |

|           | 8.3.1    | Microword            |                                                                                                   | 8-4             |

|           |          | 8.3.1.1              | Microsequencer Control Fields • 8-6                                                               | ·               |

|           | 8.3.2    | The Regist           |                                                                                                   | 86              |

|           | 8.3.3    | ALU and S            |                                                                                                   | 86              |

|           |          | 8.3.3.1              | Sources of ALU and Shifter Operands • 8-6                                                         |                 |

|           |          |                      | ALU Functions • 8-6                                                                               |                 |

|           |          | 8.3.3.3              | Shifter Functions • 8–6<br>Destinations of ALU and Shifter Results • 8–7                          |                 |

|           | 8.3.4    | 8.3.3.4<br>Ibox-Ebox |                                                                                                   | 0 7             |

|           |          |                      |                                                                                                   | 8-7             |

|           | 8.3.5    | -                    | sters and States                                                                                  | 88              |

|           | 8.3.6    |                      | ory Access                                                                                        | 8-9             |

|           | 8.3.7    |                      | ol Functions                                                                                      | 8 <b></b> 9     |

|           | 8.3.8    | Ebox Pipel           |                                                                                                   | 8-9             |

|           | 8.3.9    | Pipeline St          |                                                                                                   | 8-10            |

|           | 8.3.10   |                      | , Exceptions, and interrupts                                                                      | 8-11            |

|           | 8.3.11   | Ebox IPRs            |                                                                                                   | 8-12            |

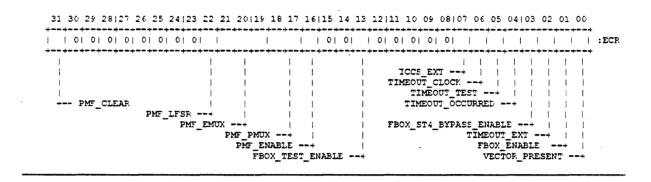

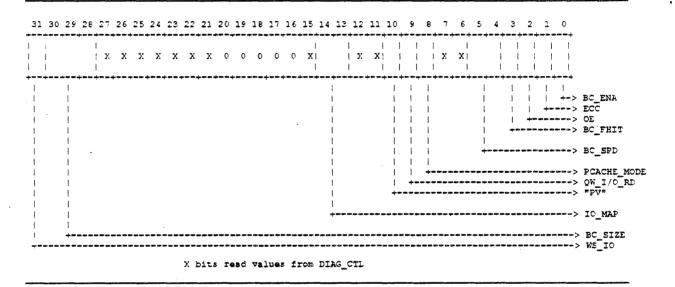

|           |          | 8.3.11.1<br>8.3.11.2 | IPR 124, Patchable Control Store Control Register • 8–12<br>IPR 125, Ebox Control Register • 8–13 |                 |

|           | 8.3.12   | Initializatio        | 'n                                                                                                | 8—16            |

|           | 8.3.13   | Testability          |                                                                                                   | 8—16            |

|           |          | 8.3.13.1             | Parallel Port Test Features • 8-16                                                                |                 |

|           |          | 8.3.13.2             | Observe Scan • 8-17                                                                               |                 |

|           |          | 8.3.13.3             | E%WBUS<31:0> LFSR • 8-17                                                                          | <b>. .</b>      |

|           | 8.3.14   | Revision H           | listory                                                                                           | 8-17            |

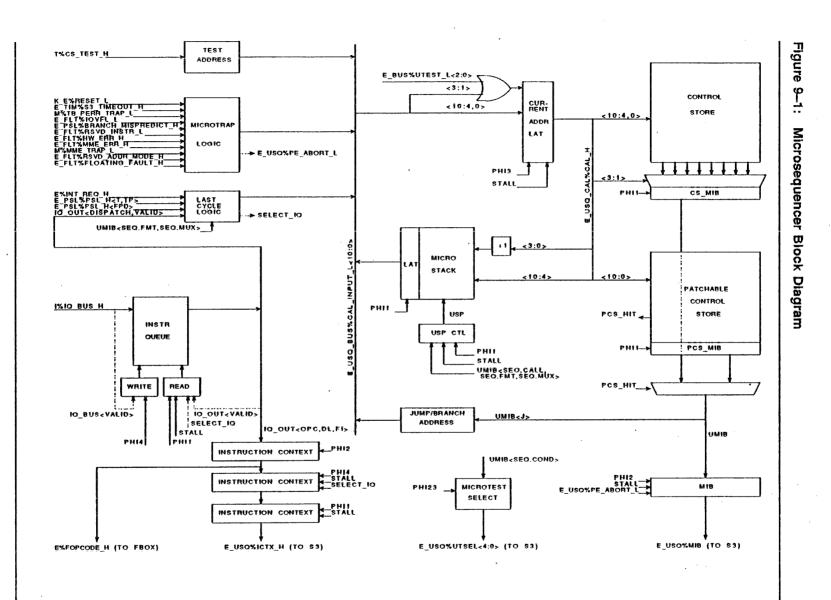

| CHAPTER 9 | THE MICF | ROSEQUEN             | CER                                                                                               | 9–1             |

| 9.1       | OVERVIE  | W                    |                                                                                                   | <del>9</del> –1 |

| 9.2       | FUNCTIO  | NAL DESCR            | IPTION                                                                                            | <del>9</del> —1 |

|           | 9,2.1    | Introductio          | n                                                                                                 | <del>9</del> –2 |

|           | 9.2.2    | Control St           | ore                                                                                               | <del>9–</del> 2 |

|           |          | 9.2.2.1              | Patchable Control Store • 9-2                                                                     |                 |

|           |          | 9.2.2.2              | Microsequencer Control Field of Microcode • 9-2                                                   |                 |

|           |          | 9.2.2.3              | MIB Latches • 9–4                                                                                 |                 |

|           | 9.2.3    | Next Addr            |                                                                                                   | <del>9</del> –5 |

|           |          | 9.2.3.1              | CAL and CAL INPUT BUS • 9-5                                                                       |                 |

|           |          | 9.2.3.1.1            | Microtest Bus • 9–5                                                                               |                 |

|           |          | 9.2.3.2              | Microtrap Logic • 9-7                                                                             |                 |

|           |          | 9.2.3.3              | Last Cycle Logic • 9–7                                                                            |                 |

|           |          | 9.2.3.4              | Microstack • 9-8                                                                                  |                 |

|           | 9.2.4    | Stall Logic          | ;<br>, , , , , , , , , , , , , , , , , , ,                                                        | 98              |

DIGITAL CONFIDENTIAL

vii

| Con | ten | ts |

|-----|-----|----|

|-----|-----|----|

|       | 9.3    | INITIALIZA                             | ATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 98                       |

|-------|--------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

|       | 9.4    | MICROCO                                | DE RESTRICTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <del>9</del> 8           |

| ·     | 9.5    | TESTABIL<br>9.5.1<br>9.5.2             | ITY<br>Test Address<br>MIB Scan Chain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 99<br>99<br>910          |

|       | 9.6    | REVISION                               | HISTORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <del>9</del> –10         |

| СНАРТ | FER 10 | THE INTE                               | ERRUPT SECTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>10</b> —1             |

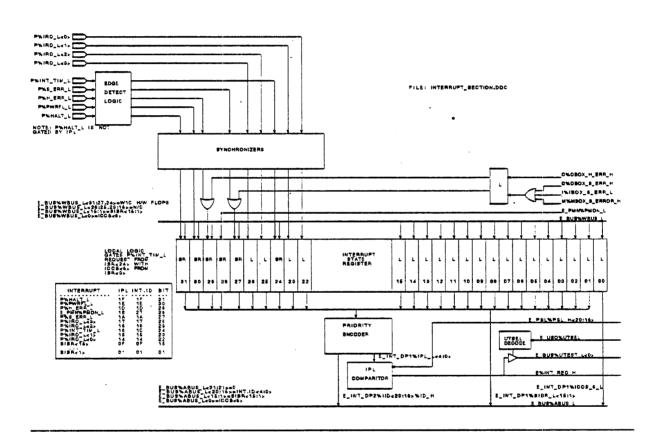

|       | 10.1   | OVERVIEW                               | N · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10-1                     |

|       | 10.2   | INTERRUF<br>10.2.1<br>10.2.2           | PT SUMMARY         External Interrupts         10.2.1.1       HALT_H Interrupt Received by Edge-Sensitive Logic • 10–2         10.2.1.2       External Interrupt Requests Received by Level-Sensitive Logic • 10–2         Internal Interrupt Requests       The second sec | 10–1<br>10–2<br>10–3     |

|       |        | 10.2.3<br>10.2.4                       | Special Considerations for Interval Timer Interrupts<br>Priority of Interrupt Requests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10-3<br>10-4             |

|       | 10.3   | INTERRUF<br>10.3.1<br>10.3.2<br>10.3.3 | PT SECTION STRUCTURE<br>Synchronization Logic<br>Interrupt State Register<br>Interrupt Generation Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 105<br>105<br>106<br>107 |

|       | 10.4   |                                        | ROCODE INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 108                      |

|       | 10.5   | PROCESS                                | OR REGISTER INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 10-10                    |

|       | 10.6   | INTERRUF<br>10.6.1                     | <b>PT SECTION INTERFACES</b><br><b>Ebox Interface</b><br>10.6.1.1 Signals From Ebox • 10–11<br>10.6.1.2 Signals To Ebox • 10–11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 10–11<br>10–11           |

|       |        | 10.6.2                                 | Microsequencer Interface<br>10.6.2.1 Signals from Microsequencer • 10–11<br>10.6.2.2 Signals To Microsequencer • 10–11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10-11                    |

|       |        | 10.6.3                                 | Cbox Interface<br>10.6.3.1 Signals From Cbox • 10-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10-11                    |

|       |        | 10.6.4                                 | <b>Ibox Interface</b><br>10.6.4.1 Signals From Ibox • 10–12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>10–1</b> 1            |

|       |        | 10.6.5                                 | Mbox Interface<br>10.6.5.1 Signals From Mbox • 10–12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10-12                    |

|       |        | 10.6.6                                 | Pin Interface<br>10.6.6.1 Input Pins • 10–12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10-12                    |