# digital

INCLUDING MEMORIES

# microcomputer processor handbook

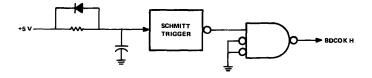

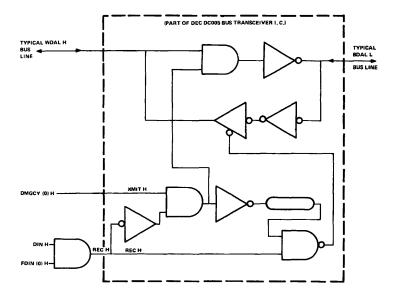

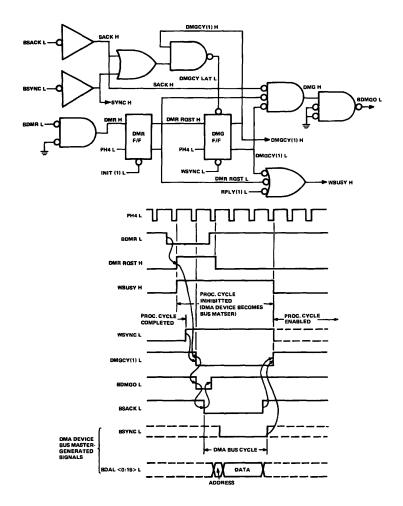

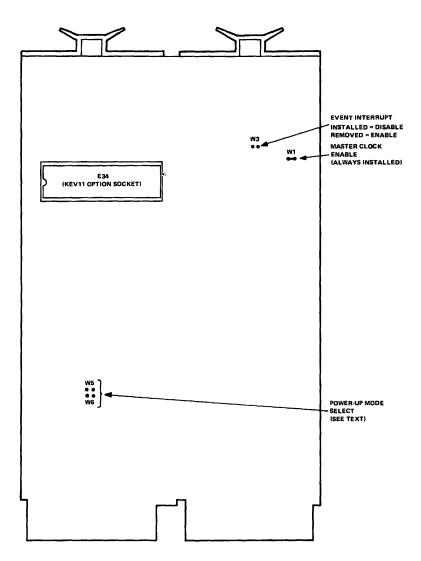

DIGITAL Facility, Kanata, Canada

## **CORPORATE PROFILE**

Digital Equipment Corporation designs, manufactures, sells and services computers and associated peripheral equipment, and related software and supplies. The Company's products are used world-wide in a wide variety of applications and programs, including scientific research, computation, communications, education, data analysis, industrial control, timesharing, commercial data processing, word processing, health care, instrumentation, engineering and simulation.

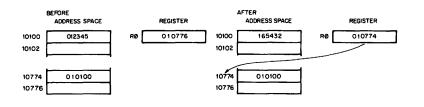

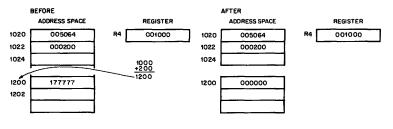

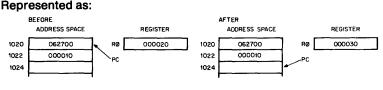

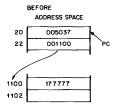

# microcomputer processor handbook

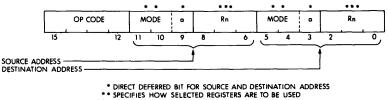

COPYRIGHT © 1979 BY DIGITAL EQUIPMENT CORPORATION

.

1

# CONTENTS

| CHAPTER 1 INTRODUCTION    | .1 |

|---------------------------|----|

| SYSTEM ARCHITECTURE       | .3 |

| THE LSI-11 MICROCOMPUTER  | .4 |

| LSI-11 MEMORY ORGANIZATON | 10 |

| THE LSI-11 BUS            | 10 |

| PERIPHERALS               | 12 |

| DOCUMENTATION             | 12 |

|                           | 13 |

| EDUCATIONAL SERVICES      | 13 |

| LSI-11 RELATED COURSES    |    |

| DECUS                     | 14 |

| MAINTENANCE               | 15 |

| ON-SITE SERVICE           | 15 |

|                           |    |

| CHAPTER 2 SYSTEMS AND SOFTWARE2   | 1 |

|-----------------------------------|---|

| PDP-11/23 SYSTEM DESIGNATIONS2    | 1 |

| BA11-N MOUNTING BOX               | 2 |

| Specifications                    | 2 |

| SOFTWARE                          | 3 |

| PDP-11/03-S AND PDP-11/03-L BOXES | 6 |

| PDP-11/03-S (Small Boxes)         | 7 |

| BA11-M MOUNTING BOX               | 7 |

| Specifications                    | 7 |

| PDP-11/03-L Box                   | 7 |

| PDP-11V03-L PACKAGED SYSTEMS      | 0 |

| PDP-11T03-L SYSTEMS               | 0 |

| PDP-11/03 SYSTEM SOFTWARE         | 1 |

ł

ł

1

ł

| CHAPTER 3              | LSI-11/23  | PROCESSO | R | <br>.33  |

|------------------------|------------|----------|---|----------|

| GENERAL                |            |          |   | <br>. 33 |

| FEATURES               |            |          |   | <br>.33  |

| SPECIFICATION          | S          |          |   | <br>.35  |

| DESCRIPTION.           |            |          |   | <br>.36  |

| <b>General Process</b> | or Hardwar | е        |   | <br>.36  |

| Instruction Set .      |            |          |   | <br>.41  |

| Floating Point Op      | otion      |          |   | <br>.42  |

| Data Address Lir       | nes (DAL)  |          |   | <br>.43  |

| Microinstruction Bus (MIB)4                         | 43 |

|-----------------------------------------------------|----|

| Direct Memory Access (DMA)                          |    |

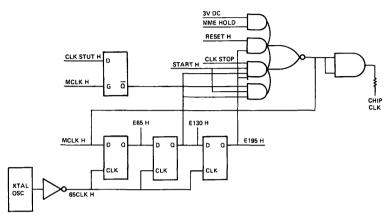

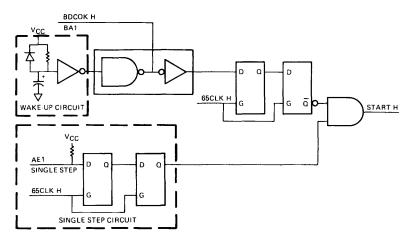

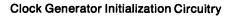

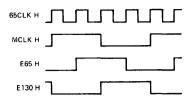

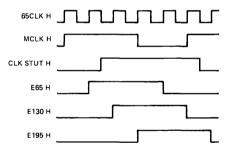

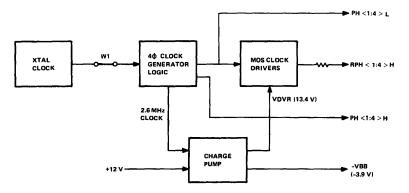

| Clock Generator Circuitry                           |    |

| Clock Generator Cycles                              | 54 |

| CONFIGURATION                                       | 58 |

| Jumper Configurations                               | 58 |

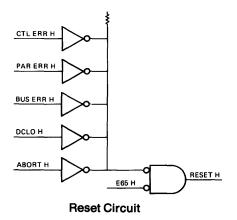

| Module Contact Finger Identification                | 32 |

| Backplane Pin Assignments and LSI-11/23 Utilization | 33 |

| Hardware Options                                    | 34 |

| System Differences                                  | 70 |

| Module Installation Procedure                       | 71 |

| Console Odt                                         | 78 |

| Console Odt Command Set                             | 79 |

| Address Specification                               | 36 |

| Entering Octal Digits                               | 37 |

| Odt Timeout                                         | 37 |

| Invalid Characters                                  | 37 |

| CHAPTER 4           | LSI-11/2 | PROCES | SSOR | <br>                          | 89  |

|---------------------|----------|--------|------|-------------------------------|-----|

| GENERAL             |          |        |      | <br>                          | 89  |

| FEATURES            |          |        |      | <br>                          | 89  |

| SPECIFICATION       | s        |        |      | <br>                          | 90  |

| <b>DESCRIPTION</b>  |          |        |      | <br>                          | 91  |

| Chip Set            |          |        |      |                               |     |

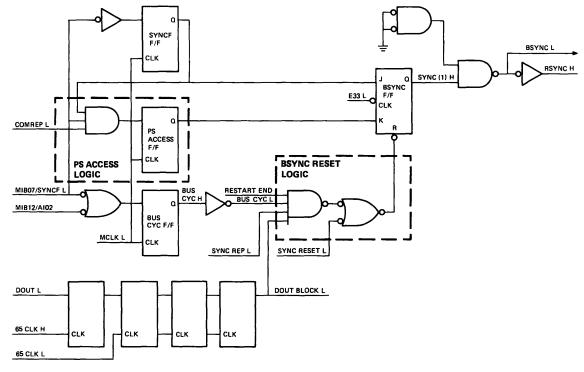

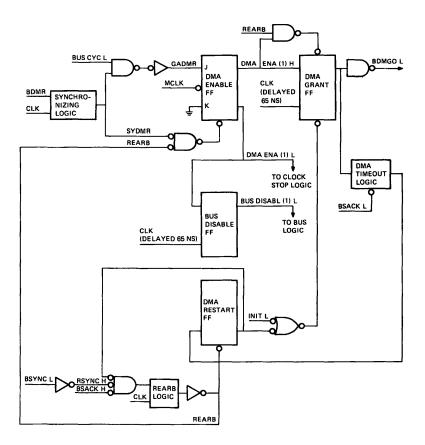

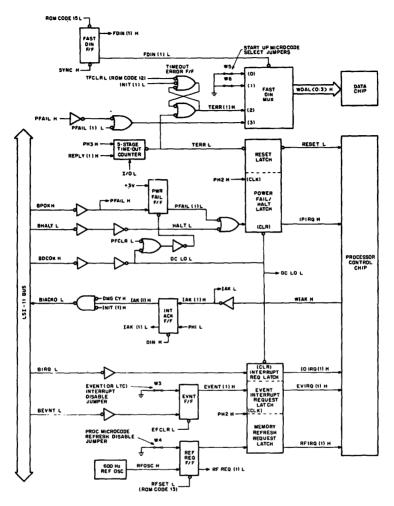

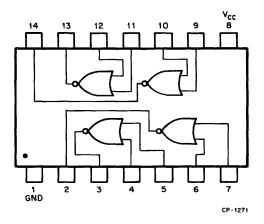

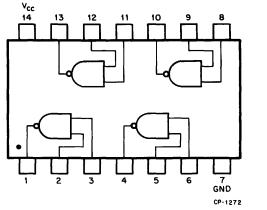

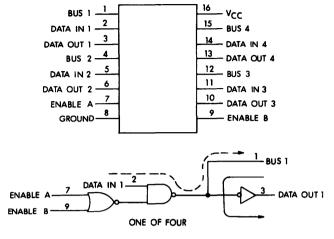

| LSI-11/2 Logic Fi   | unctions |        |      | <br>• • • • • • • • • • • • • | 105 |

| CONFIGURATIO        |          |        |      |                               |     |

| Processor Opera     |          |        |      |                               |     |

| <b>ODT Commands</b> |          |        |      | <br>                          | 117 |

| CHAPTER   | 5     | LSI-11 | PRO   | CESS | OR | <br> | <br>129 |

|-----------|-------|--------|-------|------|----|------|---------|

| GENERAL   |       |        |       |      |    | <br> | <br>129 |

| FEATURES  |       |        |       |      |    | <br> | <br>129 |

| SPECIFICA | TIONS | S      |       |      |    | <br> | <br>129 |

| DESCRIPTI | ON.   |        |       |      |    | <br> | <br>131 |

| CONFIGUR  | ATIO  | N      |       |      |    | <br> | <br>151 |

| WRITABLE  | CONT  | ROL S  | STORE |      |    | <br> | <br>158 |

| WCS FEAT  | URES  |        |       |      |    | <br> | <br>159 |

| WCS SPEC  | IFICA | TIONS  |       |      |    | <br> | <br>159 |

| CHAPTER 6 ADDRESSING MODES                    | 1 |

|-----------------------------------------------|---|

| REGISTER MODE                                 | 4 |

| REGISTER DEFERRED MODE165                     | 5 |

| AUTOINCREMENT MODE165                         | 5 |

| AUTOINCREMENT DEFERRED MODE160                | 5 |

| AUTODECREMENT MODE167                         | 7 |

| AUTODECREMENT DEFERRED MODE162                | 7 |

| INDEX MODE                                    | 3 |

| INDEX DEFERRED MODE169                        | Э |

| USE OF THE PC AS A GENERAL REGISTER170        | 0 |

| PC IMMEDIATE MODE                             | 0 |

| PC ABSOLUTE MODE                              | 1 |

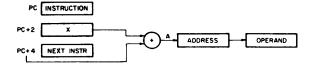

| PC RELATIVE MODE                              | 1 |

| PC RELATIVE DEFERRED MODE                     | 2 |

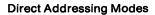

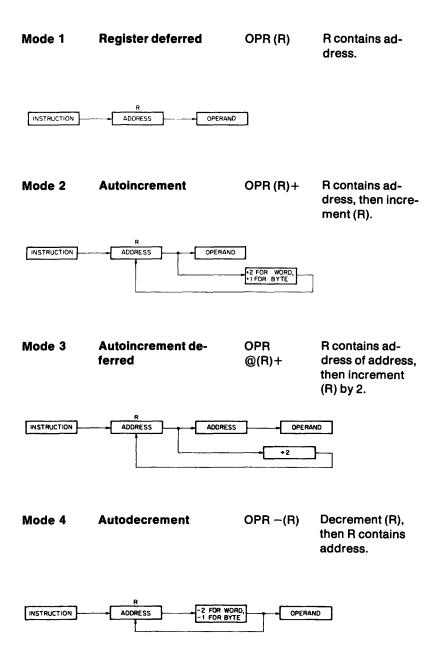

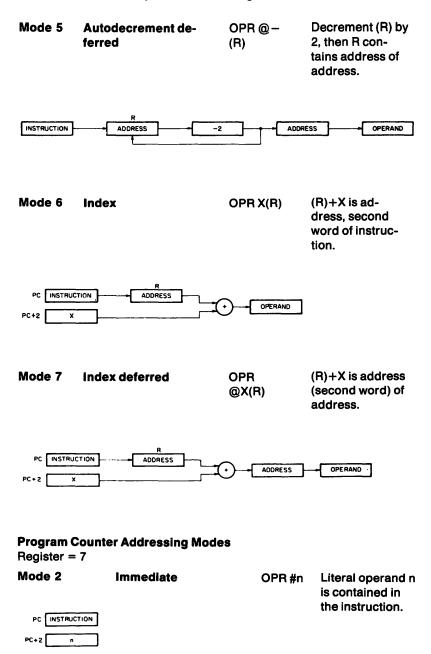

| GRAPHIC SUMMARY OF PDP-11 ADDRESSING MODES175 | 5 |

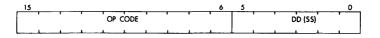

| CHAPTER 7 INSTRUCTION SET        |   |

|----------------------------------|---|

| SINGLE OPERAND INSTRUCTIONS      |   |

| DOUBLE OPERAND INSTRUCTIONS      |   |

| PROGRAM CONTROL INSTRUCTIONS     | 1 |

| JUMP AND SUBROUTINE INSTRUCTIONS | ŀ |

| INTERRUPTS AND TRAPS185          | , |

| MISCELLANEOUS INSTRUCTIONS       | j |

| CONDITION CODE OPERATION         | 6 |

| EXAMPLES                         | 6 |

| SPECIAL SYMBOLS191               |   |

| INSTRUCTION SET                  |   |

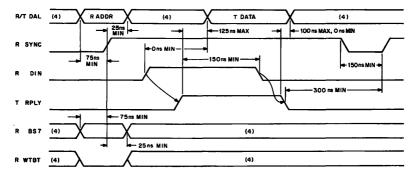

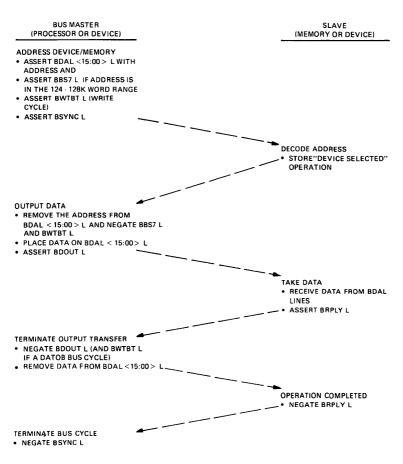

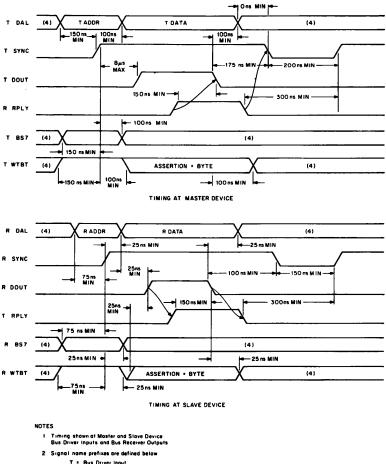

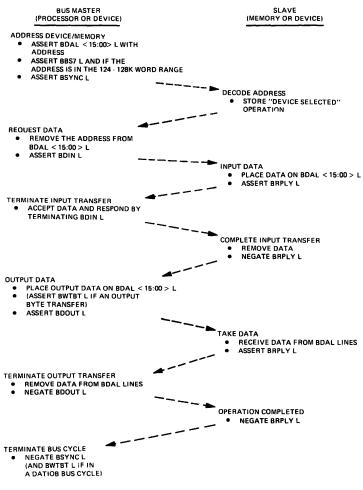

| CHAPTER 8             | LSI-11 BUS        | 223 |

|-----------------------|-------------------|-----|

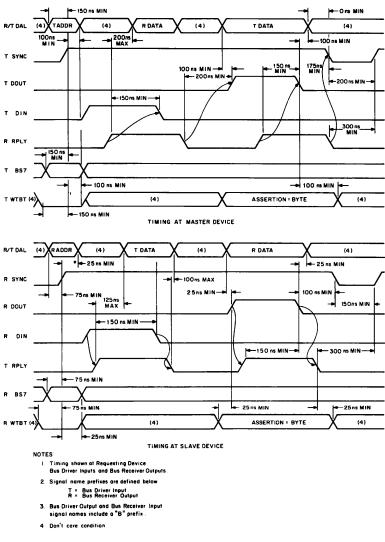

| DATA TRANSFER         | R BUS CYCLES      | 225 |

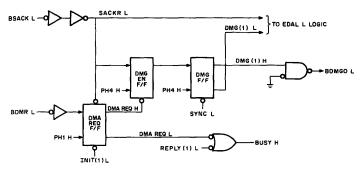

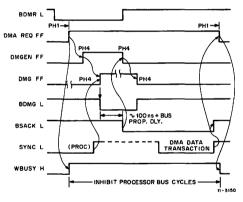

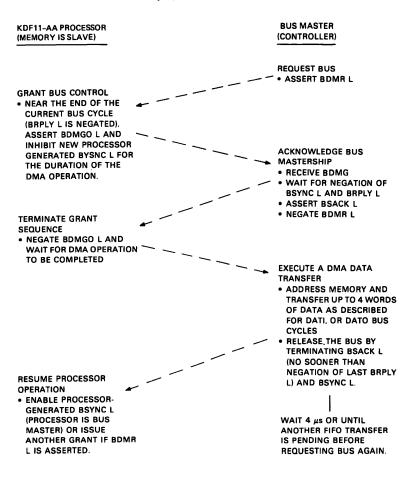

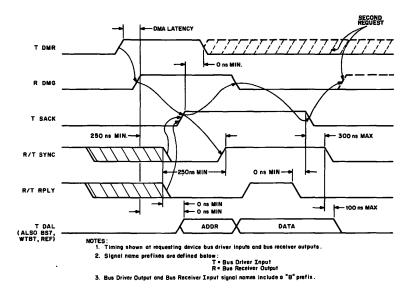

| DIRECT MEMOR          | ACCESS            | 234 |

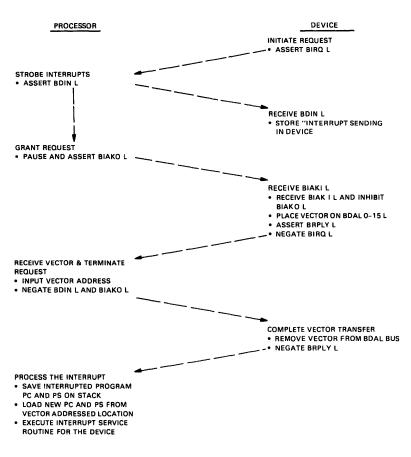

| INTERRUPTS            |                   | 237 |

| <b>CONTROL FUNC</b>   |                   | 243 |

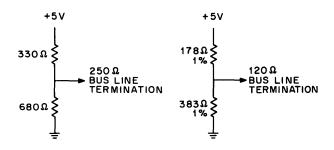

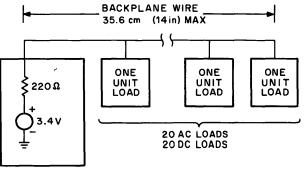

| <b>BUS ELECTRICA</b>  | L CHARACTERISTICS | 245 |

| SYSTEM CONFIG         | GURATIONS         | 249 |

| <b>BUS PIN DESCRI</b> | IPTION TABLE      | 253 |

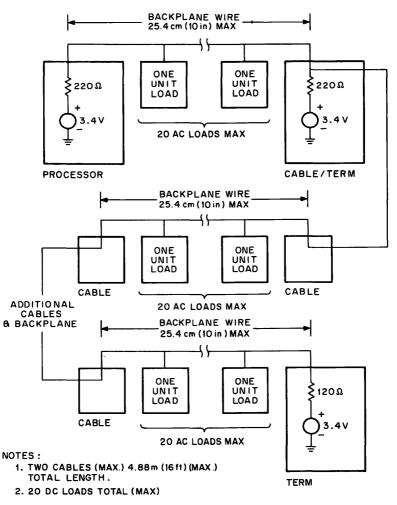

| CHAPTER 9 MEMORY MANAGEMENT                     | 271 |

|-------------------------------------------------|-----|

| MEMORY RELOCATION                               | 273 |

| PROTECTION                                      |     |

| PAGE ADDRESS REGISTER (PAR)                     | 283 |

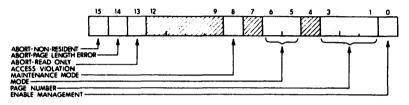

| PAGE DESCRIPTOR REGISTER (PDR)                  |     |

| VIRTUAL AND PHYSICAL ADDRESSES                  | 287 |

| STATUS REGISTERS                                | 289 |

| MEMORY MANAGEMENT INSTRUCTIONS                  | 292 |

|                                                 |     |

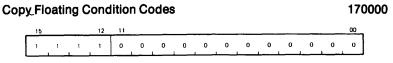

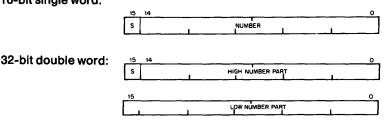

| CHAPTER 10 FLOATING POINT                       | 293 |

| INTRODUCTION                                    | 293 |

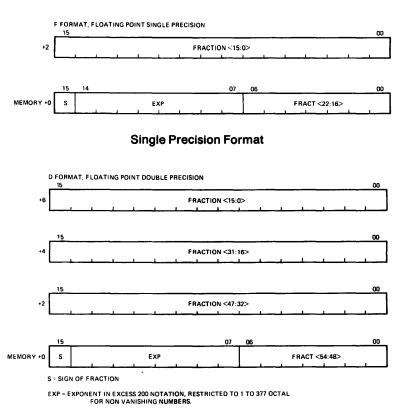

| FLOATING POINT DATA FORMATS                     |     |

| FLOATING POINT STATUS REGISTER (FPS)            | 295 |

| FLOATING EXCEPTION CODE AND ADDRESS REGISTERS   | 300 |

| FLOATING POINT PROCESSOR INSTRUCTION ADDRESSING |     |

| ACCURACY                                        |     |

| FLOATING POINT INSTRUCTIONS                     |     |

| EXTENDED ARITHMETIC OPTION                      |     |

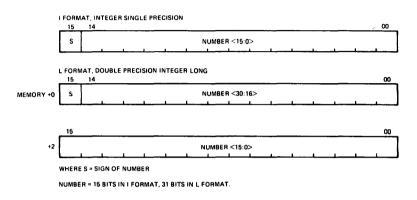

| FIXED POINT ARITHMETIC (EIS)                    | 325 |

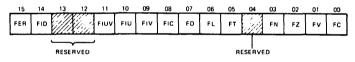

| FLOATING POINT ARITHMETIC (FIS)                 | 329 |

| CHAPTER 11 PROGRAMMING TECHNIQUES | .335  |

|-----------------------------------|-------|

| POSITION-INDEPENDENT CODE         | .335  |

| EXAMPLES                          | . 337 |

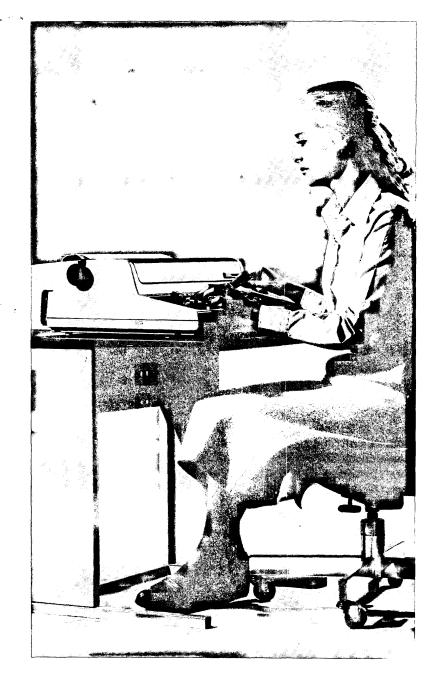

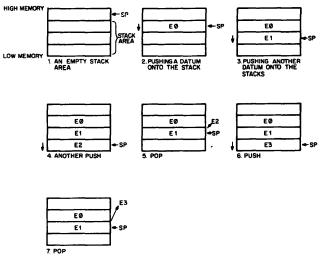

| STACKS                            | . 339 |

| DELETING ITEMS FROM A STACK       | . 344 |

| SUBROUTINE LINKAGE                | .345  |

| INTERRUPTS                        | . 346 |

| RE-ENTRANCY                       |       |

| COROUTINES                        | .352  |

| RECURSION                         |       |

| PROCESSOR TRAPS                   |       |

| TRAP INSTRUCTIONS                 |       |

| CONVERSION ROUTINES               |       |

| ASCII CONVERSIONS                 |       |

|                                   | .004  |

| CHAPTER 12     | MEMORIES                  | 367        |

|----------------|---------------------------|------------|

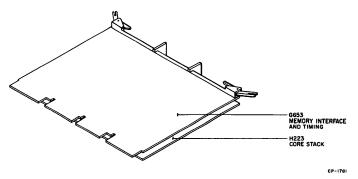

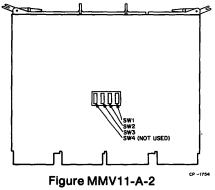

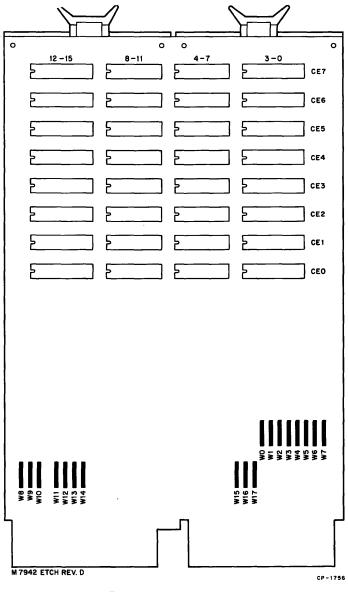

| MMV11-A 4K BY  | 16-BIT CORE MEMORY        | 367        |

| MRV11-AA 4K BY | ( 16-BIT READ-ONLY MEMORY | 85         |

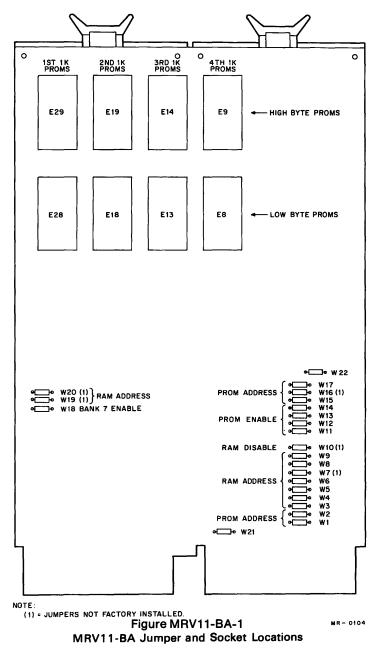

| MRV11-BA LSI-1 | 1 UV PROM/RAM             | 396        |

| MRV11-C ROM N  | 10DULE                    | <b>112</b> |

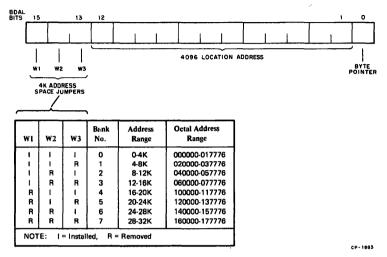

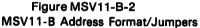

| MSV11-B 4K BY 16-BIT MOS READ/WRITE MEMORY   | 445 |

|----------------------------------------------|-----|

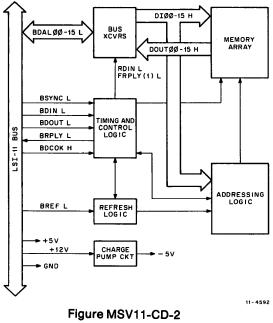

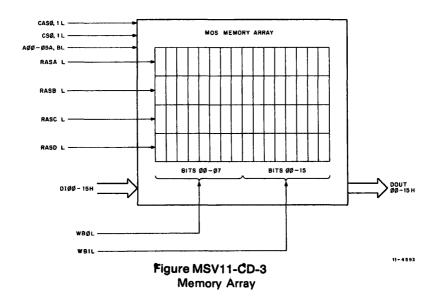

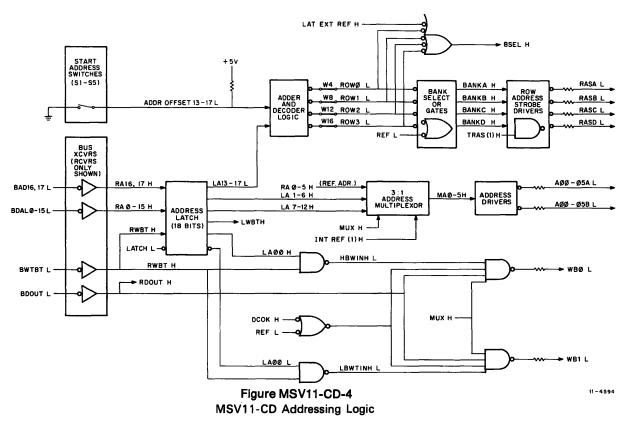

| MSV11-CD 16K BY 16-BIT MOS READ/WRITE MEMORY | 451 |

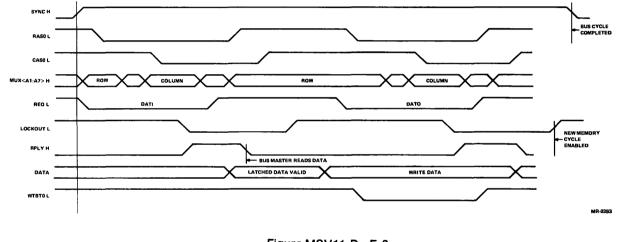

| MSV11-D, -E MEMORY                           | 474 |

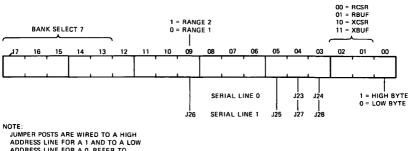

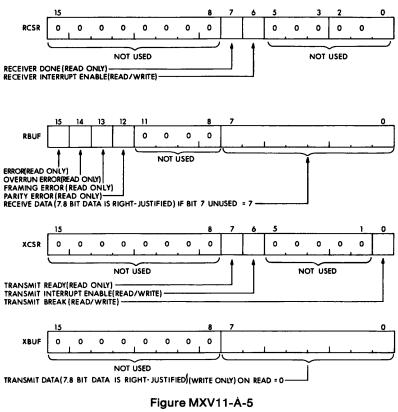

| MXV11-A MEMORY AND ASYNCHRONOUS SERIAL       |     |

|                                              | 494 |

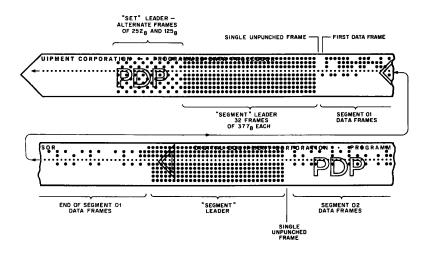

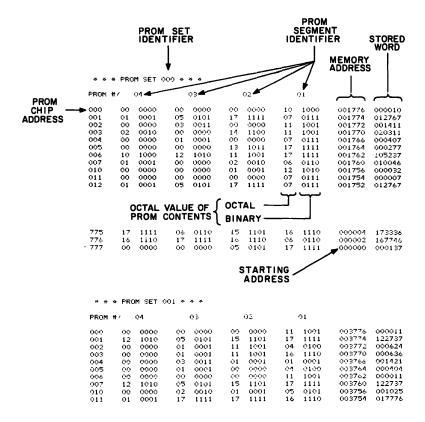

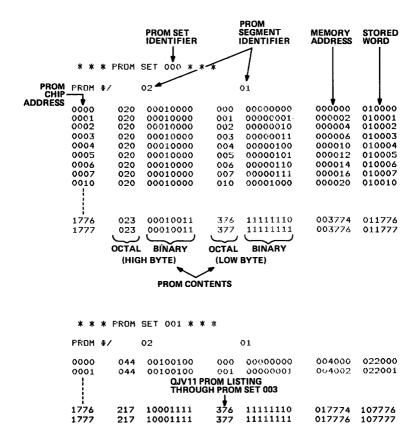

| CHAPTER 13 PROMS                  |  |

|-----------------------------------|--|

| PROGRAMMING NOTES                 |  |

| LOADING AND INSTALLING PROMS      |  |

| MRV11-C PROCEDURES                |  |

| PB11 UNIVERSAL PROM PROGRAMMER    |  |

| THE QJV11 PROM FORMATTING PROGRAM |  |

| APPENDIX A | TIMING INFORMATION       |

|------------|--------------------------|

| APPENDIX B | DIFFERENCES              |

| APPENDIX C | INTEGRATED CIRCUITS      |

| APPENDIX D | OCTAL-DECIMAL CONVERSION |

F B F

ł

## CHAPTER 1 INTRODUCTION

DIGITAL's development of microcomputers began in 1975, with the introduction of the LSI-11. Large Scale Integration technological advances in semiconductor chip design have led to rapid progress in the reduction of cost and escalation of functionality.

Ł

This handbook discusses three members of DIGITAL's LSI-11 processor family—the LSI-11 (KD11-F), LSI-11/2 (KD11-HA) and the newest member, the LSI-11/23 (KDF11-AA).

The original **LSI-11** is packaged on a *quad-height* board,  $10'' \times 8.9''$  (25.4 cm  $\times$  22.8 cm). In 1977, DIGITAL introduced the **LSI-11/2**, a smaller, *double height* version of the LSI-11. The LSI-11/2 employs the same chip set as the original LSI-11, but lacks the 8K bytes of memory contained on the quad height board. The smaller physical size of the LSI-11/2 made it convenient for incorporation into instrumentation devices.

With the introduction of the LSI-11/2, DIGITAL announced new memory and communications peripheral boards in the double height form factor.

The newest member of the LSI-11 family, the LSI-11/23 was announced in 1979. Software- and hardware-compatible with LSI-11 processors, it's improved functionality provides minicomputer power with the price and size benefits of a microcomputer.

The most fundamental LSI-11/23 design decision was to remain with the LSI-11 bus architecture. This architecture assures the continued hardware and software commonality of LSI-11 family. Expansion potential was incorporated into the original design of the LSI-11 bus. The original design specified 18 memory address lines, the upper two reserved for later use. These high order address lines are now utilized by the LSI-11/23 to permit increased memory addressing capability.

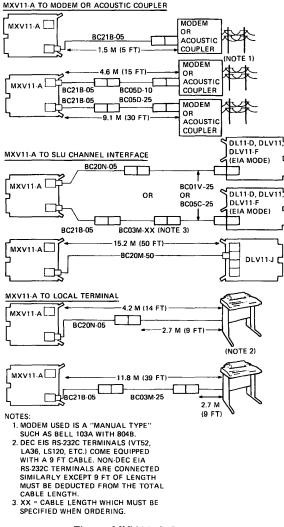

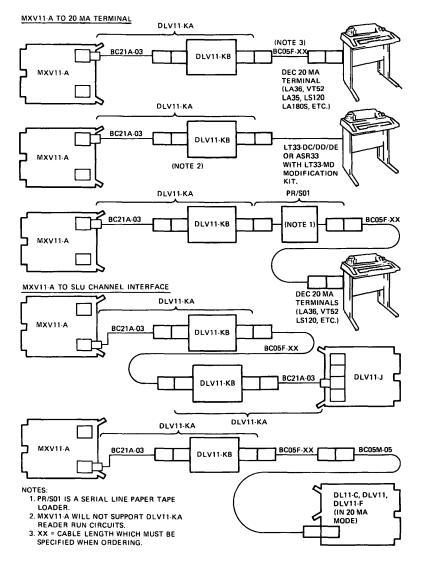

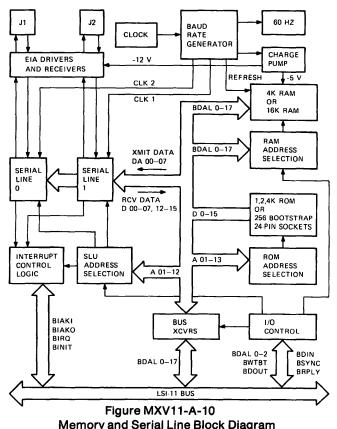

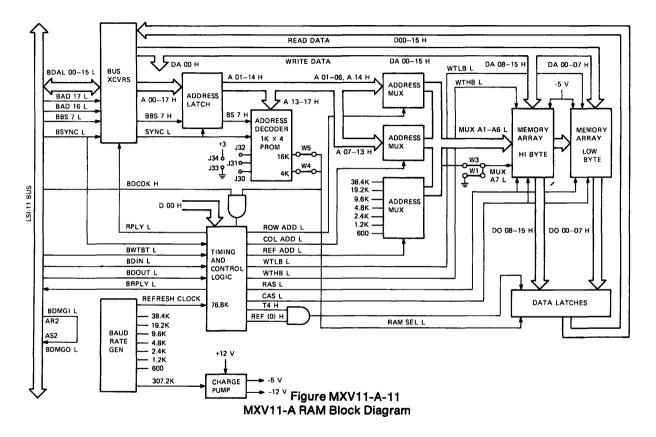

The size and hardware compatibility of the LSI-11/23 and the other LSI-11 family members permits substitution of the newer module into existing applications requiring greater functionality and performance. It continues this improvement by permitting development of products that can be used with all LSI-11 processors. One such device is the MXV11 multifunction board, a double height board containing either 8K or 32K bytes of RAM, sufficient ROM/PROM for bootstrap or program functions, a crystal clock, and two serial input/output ports. When used together, the LSI-11/23 processor board and the multifunction board contain all the functions needed to implement a complete small system.

1

j.

ł

1

í.

1

When an LSI processor board is packaged with a backplane, power supply and rack mountable box, DIGITAL considers it a member of the outstanding PDP-11 family. An LSI-11 or LSI-11/2 boxed with backplane, memory, and power supply, becomes PDP-11/03 or PDP-11/03-Ls and the LSI-11/23 boxed with backplane, memory, and power supply, becomes a PDP-11/23. These *low end* members of the PDP-11 family have, with a very few exceptions, all the features and benefits of the other family members.

#### • Extensive Computer Power and Small Processor Size

The processor modules are built around a set of N-channel metal oxide semiconductor (MOS) chips, which include control and data elements as well as microcoded read-only memory (microms). The memory is microprogrammed to emulate the powerful PDP-11 instruction set, and also contains routines for on-line debugging techniques (ODT) that function as a console emulator. The processor also contains a 16-bit buffered parallel input/output (I/O) bus, a real-time clock input, priority interrupt control logic, bus arbitration logic, power-fail/auto restarts and other features to provide stand-alone operation. LSI-11 processors are contained on three basic module types to suit a variety of applications.

#### Modularity

The processor, memory, device interfaces, backplane, and interconnecting hardware are all modular in design. Module selection, such as the type and size of memory and device interfaces, enables custom tailoring to meet specific applications requirements.

- 16-Bit Word (Two 8-Bit Bytes)

- Word or Byte Processing Efficient handling of 8-bit characters without the need to rotate, swap, or mask.

- Asynchronous Operation

LSI-11 processor and system components (memory and peripherals) run at their highest possible speed.

#### Stack Processing

Hardware sequential memory manipulation makes it easy to handle structured data, subroutines, and interrupts.

- Direct Memory Access (DMA) Direct memory access for multiple devices is inherent in the architecture.

- Eight General-Purpose Registers For accumulators or address generation.

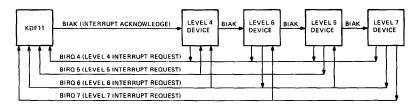

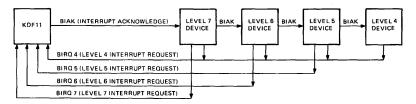

- **Priority-Structured I/O System** Daisy-chained grant signals provide a priority-structured I/O system.

## Vectored Interrupts

Fast interrupt response without device polling.

• Single and Double Operand Instructions Powerful and efficient set of programming instructions.

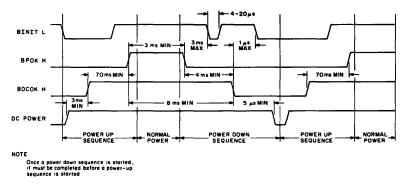

## Power-Fail/Auto Restart

Whenever dc power sequencing signals indicate an impending ac power loss, a microcoded power-fail sequence is initiated. When power is restored, the processor can automatically return to the run state (when nonvolatile memory is contained in the system).

## • A Wide Variety of Options

Options include memory (read/write and read-only); serial line, parallel line, and DMA interfaces; mass storage devices (hard disk and floppy disk systems); analog interfaces (D/A and A/D converters); bus expansion, power supply, and hardware options (backplanes, boxes, etc.).

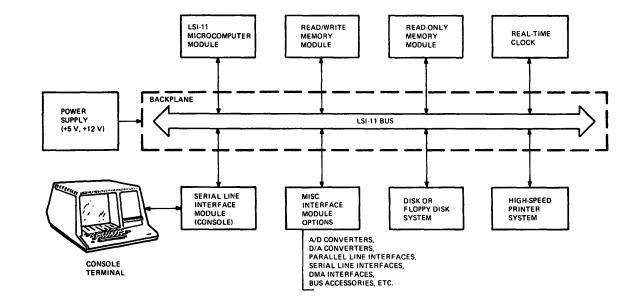

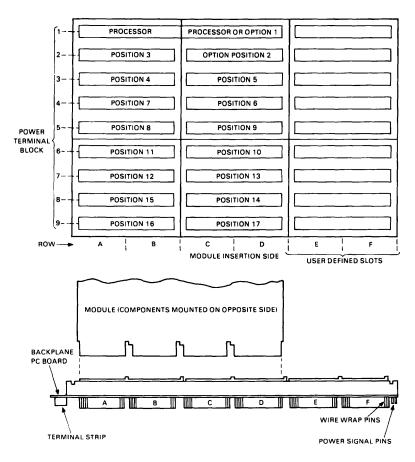

## SYSTEM ARCHITECTURE

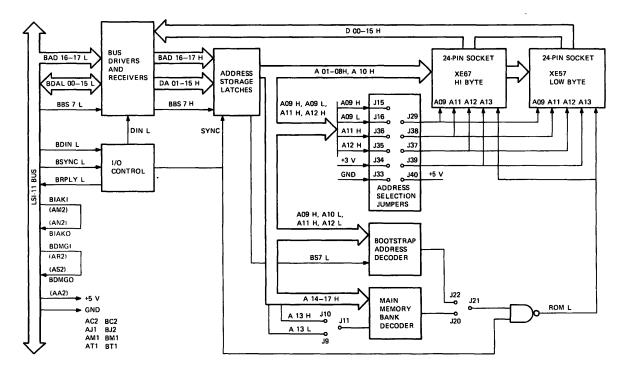

A complete and powerful microcómputer system can be configured using an LSI-11 microcomputer, appropriate memory, I/O devices, and interconnection hardware. The LSI-11 Bus provides communication between system components. A typical system configuration is shown in the accompanying figure.

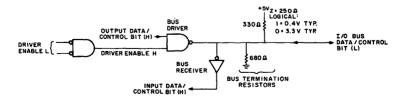

All modules connected to this common LSI-11 Bus structure receive the same interface signals. LSI-11 Bus control and data lines are open-collector lines which are asserted when low. All data and most control lines are bidirectional. All transactions on the bus are asynchronous. The LSI-11 processors use the following LSI-11 Bus signals: 16 multiplexed data/address lines, 2 multiplexed address/parity lines, 6 data transfer control lines, 6 system control lines, and 8 interrupt and direct memory access (DMA) control lines.

Interrupt and DMA are implemented with two daisy-chained grant signals which provide a priority-structured I/O system. The highest priority device is the module located electrically closest to the microcomputer module. A device passes grant signals to lower priority devices only when it is not requesting service.

The LSI-11 bus provides a vectored interrupt interface for any device. Device polling is not required in processing interrupt requests. When an interrupting device receives a grant, the device passes an interrupt vector to the processor, which points to a new processor status word and the starting address of an interrupt service routine for the device.

LSI-11 backplane options contain all LSI-11 bus wiring plus power distribution wiring to all device locations.

## THE LSI-11 MICROCOMPUTER

The microcomputer connected to the LSI-11 bus controls the time allocation of the LSI-11 Bus for peripherals and performs arithmetic and logic operations and instruction decoding. It contains multiple high-speed, general-purpose registers which can be used as accumulators, address pointers, index registers, and for other specialized functions. The processor does both single and double operand instruction and handles both 16-bit word and 8-bit byte data. The bus permits DMA data transfers directly between I/O devices and memory without disturbing the processor registers.

S

Typical LSI-11 System Configuration

## **General Registers**

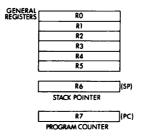

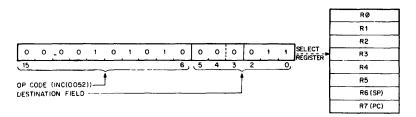

The LSI-11 central processor module contains eight 16-bit generalpurpose registers that can perform a variety of functions. These registers can serve as accumulators, index registers, autoincrement registers, autodecrement registers, or as stack pointers for temporary storage of data. Arithmetic operations can be from one general register to another, from one memory location or device register to another, or between memory locations or a device register and a general register. The eight 16-bit general registers (R0 through R7) are identified in the following figure.

**General Register Identification**

Registers R6 and R7 in the LSI-11 are dedicated. R6 serves as the Stack Pointer (SP) and contains the location (address) of the last entry in the stack. Register R7 serves as the processor Program Counter (PC) and contains the address of the next instruction to be executed. It is normally used for addressing purposes only and not as an accumulator. Register operations are internal to the processor and do not require bus cycles (except for instruction fetch); all memory and peripheral device data transfers do require bus cycles and longer execution time. Thus, general registers used for processor operations result in faster execution times. The bus cycles required for memory and device references are described below.

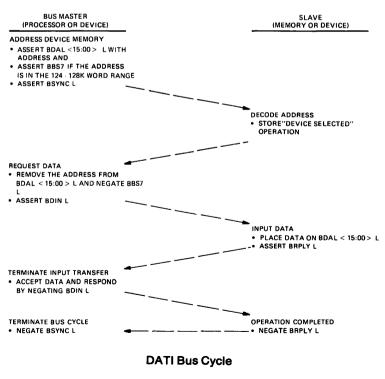

## **Bus Cycles**

The bus cycles (with respect to the processor) are:

| DATI  | Data word transfer in-<br>put                                     | Equivalent to Read operation       |

|-------|-------------------------------------------------------------------|------------------------------------|

| DATIO | Data word transfer in-<br>put followed by word<br>transfer output | Equivalent to Read/Modify<br>Write |

| DATIOB | Data word transfer in-<br>put followed by byte | Equivalent to Read/Modify<br>Write |

|--------|------------------------------------------------|------------------------------------|

|        | transfer output                                |                                    |

## **Addressing Memory and Peripherals**

The maximum direct address space of the LSI-11 is 64K bytes. LSI-11 memory locations and peripherals device registers are addressed in the same manner. The upper 4096 addresses (56K-64K bytes) are reserved (by PDP-11 convention) for peripheral device addressing.

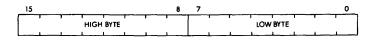

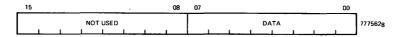

An LSI-11 word is divided into high byte and a low byte as shown in this figure.

High and Low Byte

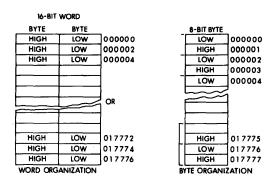

Word addresses are always even-numbered. Byte addresses can be either even- or odd-numbered. Low bytes are stored at even-numbered memory locations and high bytes at odd-numbered memory locations. Thus, it is convenient to view the memory as shown in the accompanying figure.

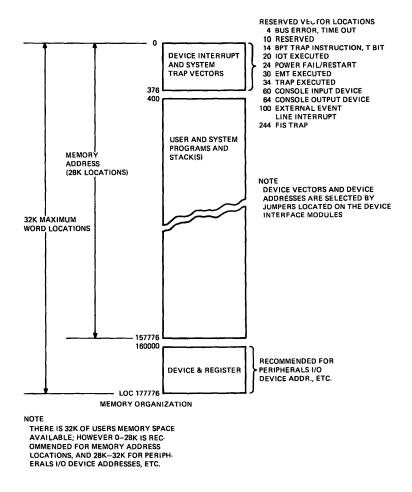

Certain memory locations have been reserved by convention for interrupt and trap handling and peripheral device registers. Addresses from 0 to  $376_8$  are reserved for trap and device interrupt vector locations. Several of these are reserved in particular for system (processor initiated) traps.

#### Word and Byte Addresses for First 4K Bank

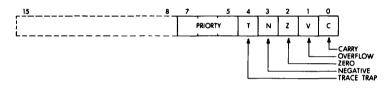

### **Processor Status Word**

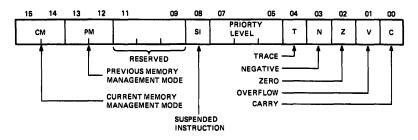

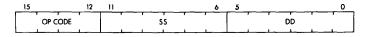

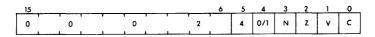

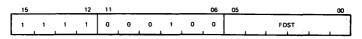

The Processor Status Word (PS) contains information on the current processor status. This information includes the current processor priority, the condition codes describing the arithmetic or logic results of the last instruction, and an indicator for detecting the execution of an instruction to be trapped during program debugging. The PS word format is shown in the figure. Certain instructions allow programmed manipulation of condition code bits and loading or storing (moving) the PS.

Processor Status Word (PS)

## Interrupt Priority Bit

The processor operates with interrupt priority PS bit 7 asserted (1) or cleared (0). When PS bit 7 = 1, an external device cannot interrupt the processor with a request for service. The processor must be operating at PS bit 7 = 0 for the device request to be serviced by the processor. As compared to other PDP-11s, the LSI-11 and LSI-11/2 service interrupts at one priority level. The LSI-11/23 services interrupts at four levels of priority.

## **Condition Codes**

The condition codes contain information on the result of the last CPU operation. The bits are set as follows (the bits are set after execution of arithmetic or logical, single operand or double operand instructions):

- Z = 1, If the result was zero.

- N = 1, If the result was negative.

- C = 1, If the operation resulted in a carry from the MSB (most significant bit) or a 1 was shifted from the MSB or LSB (least significant bit).

- V = 1, If the operation resulted in an arithmetic overflow.

## Trap (T Bit)

The program can only set or clear the trap bit (T) by popping a new PS off the stack. When set, a processor trap will occur through location 14

at completion of the current instruction execution, and a new processor status word will be loaded from location 16. This T bit is especially useful in debugging programs since it allows programs to single-step instructions.

#### **Instruction Set**

1

į

ł

The PDP-11 instruction set permits you to take advantage of Digital Equipment Corporation's years of experience with the PDP-11 family. Available are: application notes, software, documentation, training, and the DECUS user library of application programs.

The instruction set uses the flexibility of the general-purpose registers to provide more than 400 instructions—the most comprehensive and powerful instruction set of any 16-bit computer. Unlike 16-bit computers which have three classes of instructions (memory reference instructions, operate or accumulator control instructions, and I/O instructions), all data manipulation operations in the LSI-11 are accomplished with one set of instructions. Instructions that are used to manipulate memory locations can be used with peripheral device registers. For example, data in an external device register can be tested or modified directly without bringing it into memory or disturbing the general registers. Programs can add or compare data either logically or arithmetically in a device register.

LSI-11 instructions use both single and double operand addresses for words or bytes. The LSI-11, therefore, performs in one step such operations as adding or subtracting two operands, or moving an operand from one location to another.

## LSI-11 Approach

| ADD A, B                              | Add contents of location A to location B;<br>store results at location B |

|---------------------------------------|--------------------------------------------------------------------------|

| <b>Conventional Approach</b><br>LDA A | Load contents of memory location A into accumulator                      |

| ADD B                                 | Add contents of memory location B to accumulator                         |

| STA B                                 | Store result at location B                                               |

#### Addressing

Much of the power of the LSI-11 is derived from its wide range of addressing capabilities. LSI-11 addressing modes include sequential forward or backward addressing, address indexing, indirect addressing, 16-bit word addressing, 8-bit byte addressing, and stack

#### Chapter 1—Introduction

addressing. Variable-length instruction formatting allows a minimum number of words to be used for each addressing mode. The result is efficient use of program storage space.

## LSI-11 MEMORY ORGANIZATON

LSI-11 memory organization is shown in the accompanying figure.

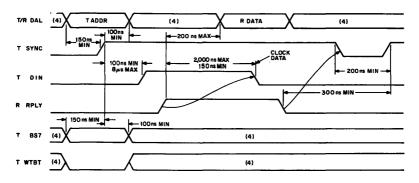

## THE LSI-11 BUS

The LSI-11 bus is a simple, fast, easy-to-use interface between LSI-11 modules. All LSI-11 modules connected to this common bidirectional bus structure receive the same interface signal lines. A detailed description of the LSI-11 bus is included in Chapter 8.

Bus data and control lines (except daisy-chain grant signals) are bidirectional open-collector lines that are asserted low. The LSI-11 processor uses 16 data/address lines and 17 control synchronization and system function lines.

### NOTE

The LSI-11 bus has recently been expanded to accommodate 18-bit addresses, thus increasing maximum system memory size to 248K bytes. More detailed information is available in Chapter 8: LSI-11 Bus and Chapter 9: Memory Management.

Both 16-bit address and 8-bit bytes or 16-bit data words are multiplexed over 16 data/address lines. During a programmed data transfer, the processor will assert an address on the bus for a fixed time. After the address time has been completed, the processor initiates the programmed input or output data transfer. The actual data transfer is asynchronous and requires a reply from the addressed device; bus synchronization and control signals provide this function.

With bidirectional and asynchronous communications on the LSI-11 bus, devices can send, receive, and exchange data at their own rates. The bidirectional nature of the bus allows utilization of common bus interfaces for different devices and simplifies the interface design.

Communication between two devices on the bus is in the form of a master-slave relationship. At any point in time, there is one device that has control of the bus. This controlling device is termed the "bus master." The master device controls the bus when communicating with another device on the bus, termed the "slave". A typical example of the relationship is the processor, as master, fetching an instruction from memory (which is always a slave). Another example is a DMA device interface, as master, transferring data to memory, as slave. Bus master control is dynamic. The bus arbitrator is the processor module; it may pass bus control to a DMA device. The DMA device, as bus master, could then communicate with memory (always a slave) without processor intervention.

**Memory Organization**

Since the LSI-11 Bus is used by the processor and all I/O devices, a hardware priority structure determines which device becomes bus master when more than one device requests control of the bus. Every device on the LSI-11 Bus which is capable of becoming bus master is assigned a priority according to its electrical position on the bus. The device closet to the processor has the highest priority.

Data transfers on the LSI-11 Bus are asynchronous so that communication is independent of the physical bus length and the response time of the slave device. The asynchronous operation between bus master

#### Chapter 1—Introduction

and slave devices precludes the need for synchronizing bus transactions with clock signals. Thus, each device is allowed to operate at the maximum possible speed.

Full 16-bit words or 8-bit bytes of information can be transferred on the bus between a master and a slave. The information can be instructions, addresses, or data. This type of information transfer occurs when the processor, as master, is fetching instructions, operands, and data from memory, and is storing the results in memory after execution of the instruction.

Information is provided in this handbook about the assembly language parameters, processes, and techniques involved in programming the LSI-11. DIGITAL publishes tutorial software documentation that provides detailed information about using the LSI-11 instruction set to develop programs. There are also well-developed courses for customers by DIGITAL's Education Services group.

The material presented on the LSI-11 instruction set, addressing modes, and programming techiques is intended, with the examples included, to illustrate the range of and possibilities for program development.

#### PERIPHERALS

DIGITAL manufactures a full range of peripheral equipment designed to meet specific needs as well as to maintain 11-family compatibility. I/O and storage devices range from paper tape readers through high volume disk packs and from the DECwriter to the intelligent terminals which provide both hard copy and video display. There is a complete spectrum of peripheral devices available to complement the software, and to provide the complete answer to customer needs in all product line areas — business, education, industry, laboratory, and medicine.

The *Microcomputer Interfaces Handbook* describes in detail the optional equipment available for use with the LSI-11 microcomputers.

#### DOCUMENTATION

DIGITAL offers several levels of technical documentation describing 11-family software and hardware. The Microcomputer Handbook series presents an introductory technical level of LSI-11 family information. The hardware user documentation, which accompanies the delivery of LSI-11 computer systems and peripherals, offers the most detailed levels of information. There are also several good books put out by commercial publishers which discuss the LSI-11 family. Specific topics, such as microprogramming, are also well-covered in commercially available books. If you have a specific documentation need, discuss the issue with a DIGITAL salesperson, who will guide you to the appropriate literature.

## NUMERICAL NOTATION

Three number systems are used in this handbook: octal, base eight; binary, base two; and decimal, base ten. **Octal** is used for address locations, contents of addresses, and instruction operation codes. **Binary** is used for descriptions of words and **decimal** for normal quantitative references.

## **EDUCATIONAL SERVICES**

Like DIGITAL's computer systems, training facilities span the globe—Japan, Australia, Great Britain, Germany, France, the Netherlands, Sweden, Italy, Canada and throughout the United States. Services are centered around 14 fully equipped Regional Education Centers and a staff of seasoned educators dedicated to providing all aspects of education and training needed in support of all DIGITAL systems.

Catalog courses are regularly scheduled classes offered at training centers. Presently there are more than 100 scheduled classes that cover the range from first-time user to highly specialized training on theory of operation. Most catalog courses include extensive hands-on laboratory time, and all incorporate the use of a broad assembly of student workbooks, reference manuals, and other instructional materials.

Specialized training is available for users with unique applications or training situations. This approach is designed to give the student the maximum relevant material for specific applications, while minimizing extraneous information. The custom courses are tailored to the individual customer's schedule and typically comprise a series of courses. These can be modified from existing courses or be entirely new programs based on mutually agreed upon objectives.

Customers with a group of individuals to train may find it more economical to have Educational Services conduct courses at the user's home site. On-site instruction of both catalog and custom courses eliminates travel and other expenses incurred by students attending classes at training centers. This method of instruction further enhances training by allowing DIGITAL instructors to emphasize points of particular value to the student's applications and operations.

By taking advantage of the latest in audio-visual techniques, Educational Services has developed a series of courses that offers independent learning. Audio-visual courses are convenient, self-contained, and modular in topic. The self-instructional format allows student to progress at ther own rates, study when and where they wish, and play back modules for review. Audio-visual course material is available in several forms—video-tape, videocassette, or audio/filmstrip cassette—all supported by student workbooks.

## LSI-11 RELATED COURSES

DIGITAL's educational group offers a series of courses on the hardware and software of your LSI-11 systems. For complete information on course content, prerequisites, pricing, and scheduling, consult the Educational Courses Catalog available through DIGITAL's Educational Centers listed below:

#### **Boston area:**

Digital Equipment Corporation Educational Services Department 12 Crosby Drive Bedford, MA 01730

#### Chicago area:

Digital Equipment Corporation Educational Services Department 5600 Apollo Drive Rolling Meadows, Illinois 60008 Telephone: (312) 640-5520

#### Philadelphia area:

Digital Equipment Corporation Educational Services Department Whitpain Office Campus 1740 Walton Road Blue Bell, Pennsylvania 19422 Telephone: (215) 825-4200 Ext. 26

#### Washington, D.C. area:

Digital Equipment Corporation Education Services Department Lanham 30 Office Building 5900 Princess Garden Parkway Lanham, Maryland 20801 Telephone: (301) 459-7900 Ext.315 or 215

#### San Francisco area:

Digital Equipment Corporation Educational Services Department 310 Soquel Way Sunnyvale, Calfornia 94086 Telephone: (408) 984-0200 Ext. 293 or 294

#### DECUS

Additional programs and applications packages may be obtained from DECUS, the Digital Equipment Computer Users Society. DECUS is a not-for-profit computer users group (the largest such group, worldwide) that sponors technical symposia, publishes a periodic newsletter and symposia proceedings, and maintains a large library of programs for the various DIGITAL computers. Every customer who has purchased or ordered a computer manufactured by DIGITAL is eligible for an installation membership in DECUS. Associate membership is also available to any person with a bona fide interest in DIGITAL computers. Membership in DECUS is strictly voluntary, and does not require payment of dues. Programs from the DECUS library are available to all members for nominal reproduction and handling charges. A complete catalog of available programs may be obtained from the society.

Further information on the DECUS Library, publications, and other DECUS activities is available from the DECUS offices listed below:

## AUSTRALIA AND

NEW ZEALAND: DECUS P.O. Box 491 Crows Nest, N.S.W. 2065 Australia

#### CANADA:

DECUS P.O. Box 11500 Ottawa, Ontario K2H 8K8 Canada

#### EUROPE AND MIDDLE EAST:

DECUS Case Postale 340 1211 Geneva 26 Switzerland

## ALL OTHERS:

DECUS 146 Main Street Maynard, Massachusetts 01754 U.S.A

## MAINTENANCE

DIGITAL offers a wide range of maintenance services to LSI-11, PDP-11/03, and PDP-11 customers. These services are provided through DIGITAL's Customer Services Organization and have been designed to meet our customer's complete maintenance needs, either on-site or off-site. These service plans provide complete DIGITAL maintenance on-site by our factory-trained engineers, or provide module and unit repairs off-site for those customers desiring to perform their own maintenance.

## **ON-SITE SERVICE**

DIGITAL's service organization provides on-site maintenance service with a staff of over 5,800 factory-trained engineers in 360 locations world-wide. Each service office maintains adequate inventory to support its customers and is fully supported by our logistics operation in Maynard, Massachusetts.

• Service Agreement — On-site contract service is available for all LSI-11 based systems, subject to minimum hardware configura-

tions. This service provides corrective maintenance, preventive maintenance, and all applicable engineering changes to ensure your products are operational and kept completely up to date. In addition to priority service, contractual maintenance allows DIGITAL customers to budget for their annual maintenance needs. The monthly contract charge covers all travel, labor, and material.

- Per Call DIGITAL also offers on-site per call service. DIGITAL will respond to maintenance needs on a billable travel, time, and materials basis.

- Installation and Warranty On-site installation and warranty-service is also available for LSI-11 based systems, subject to minimum hardware configurations. This service must be purchased at the time of original order.

#### **Off-Site Service**

DIGITAL offers complete unit and module repair services to customers capable of performing their own maintenance. The Customers Returns Area (CRA) has been established in Woburn, Massachusetts, to offer single-point interfacing for all off-site repairs for North American customers. The CRA assures the customer of complete "one-step shopping" for all factory-level warranty and post-warranty services. All repairs are effected at our Module Repair Facility in Woburn.

For Eurpean, Australian, and Japanese customers, we have established Product Repair Centers (PRCs) in eleven countries. Customers can return defective material to the PRC in their country without the burden of customs, duties, and licensing requirements. The PRCs offer the same services to these customers as the CRA in Woburn.

For information on services in Latin and South America, contact the CRA in Woburn.

• Warranty Service—All products are warranted against defects in workmanship and materials under normal proper use in their unmodified condition for a period of ninety (90) days from date of initial shipment. As a condition of this warranty, customers must obtain a DIGITAL Repair Authorization (RA) number and return the products prepaid, together with a written description of the claimed defect, to the nearest authorized DIGITAL Repair Center as listed here.

RA numbers may be obtained by contacting the CRA in Woburn (PRC if non-U.S.) and providing the following information:

- 1. Customer name and location.

- 2. Part number/serial number of failing item.

### Chapter 1—Introduction

- 3. Part number/serial number of next higher assembly if a module or subassembly.

- 4. Product line and date purchased.

- **Post-Warranty Service**—DIGITAL offers its post-warranty services in several forms:

- 1. Loose piece subassembly repair, for a minimum order.

- 2. Prepaid module mailers. Available on specific module types.

- 3. Firm quote product and option repair. For the smaller customer with only occasional service needs, and those who do not have any in-house troubleshooting capability.

For more complete information and pricing on any of the services listed, contact the repair center nearest you.

The following repair centers have been established to provide complete off-site repair services. These centers should be contacted for all off-site warranty and post-warranty services and prices. All defective material should be sent to the address indicated with your RA number appearing on the shipping label.

### North America

Digital Equipment Corporation Customer Returns Area 36 Cabot Road Woburn, MA 01801

RA Number Telephone Number: 617-933-8710

## Canada

Digital Equipment of Canada, Ltd. 100 Herzberg Road Kanata, Ontario, Canada

RA Number Telephone Number: 613-592-5111

## Europe

## Belgium

Product Repair Center Manager Digital Equipment Sa/Nv Brand Whitlock Boulevard 87 B-1040 Bruxelles, Belguim Telephone: (02) 733-9650

## France

Product Repair Center Manager Digital Equipment France 7, Rue de L'Esterel Silic 225 94528 Rungis, Cedex, France Telephone: (01) 687-2333

### Germany

Product Repair Center Manager Digital Equipment GmbH D-8000 Munchen 40 Wallensteinplatz 2 West Germany Telephone: (89) 35031

## Holland

Product Repair Center Manager Digital Equipment Bv Coloradodreef 26-28 P. O. Box 9064 3563 Utrecht, Holland Telephone: (030) 61 1814

## Italy

Product Repair Center Manager Digital Equipment S.P.A. Viale Fulvio Testi 117 Cinisello Balsamo 20092 Milan, Italy Telephone: (02) 61797

## Sweden

Product Repair Center Manager Digital Equipment AB Box 1250 S-17124 Solna 1 Sweden Telephone: (08) 730-08-00

## Switzerland

Product Repair Center Manager Digital Equipment Corp. AG/SA Koeschenruetistr 116 CH-8052 Zurich Switzerland Telephone: (01) 5152 66

#### Chapter 1—Introduction

#### **United Kingdom**

Product Repair Center Manager Digital Equipment Corp., Ltd. Gasworks Road Building V.7.A.B.L. Site Reading RGI-3EF England Telephone: (734) 58 35 55

#### **General International Area**

At this time, the only services offered in the GIA is firm quote product/option and loose piece subassembly repairs through the Tokyo and Sydney repair centers.

### **GIA Product Repair Centers**

#### Australia

Product Repair Center Manager Digital Equip. Autralia Pty. Ltd. 132-125 Willoughby Road P.O. Box 491 Crows Nest New South Wales, 2065 Australia Telephone: (02) 439-3598

## Latin America

South America Contact the CRA, Woburn

#### Japan

Product Repair Center Digital Equipment Corp. Int. #1, Taiso Shinjuku Bldg. 1-26-12, Shinjuku/K.U. Tokyo 160, Japan Telephone: (3) 341 5481

# CHAPTER 2 SYSTEMS AND SOFTWARE

DIGITAL's LSI-11 processors are named as members of the PDP-11 family when they are combined with boxes, power supplies, and back-planes.

The LSI-11 and LSI-11/2 processors, when configured as part of a boxed computer, are known as PDP-11/03 or PDP-11/03L boxes, depending upon the box. When the boxes are configured into packaged systems, they are called PDP-11V03L or PDP-11T03L systems.

The newest member of the LSI-11 family, the LSI-11/23, when configured in a box, is called a PDP-11/23 and in a system configuration is called a PDP-11V23 or PDP-11T23.

DIGITAL makes this family of low-end computers available at several levels of integration allowing you maximum design flexibility.

DIGITAL's family of PDP-11 peripherals includes an extensive line of hardware interfaces that may be used with the LSI bus based systems. These are described in detail in the *Microcomputer Interfaces Handbook*.

## PDP-11/23 SYSTEM DESIGNATIONS

## **Box Option Designations**

The PDP-11/23 box options include: the processor, two or four memory boards (for 128K or 256K bytes), the BA11-N box, and the DLV11 interface.

- 11/23-AA = BA11-NC, KDF11-AA, (2) MSV11-DD, BDV11-AA, DLV11-J, 120V, 50/60 Hz, 128 KB

- 11/23-AB = BA11-ND, KDF11-AA, (2) MSV11-DD, BDV11-AA, DLV11-J, 240V, 50/60 Hz, 128 KB

- 11/23-AC = BA11-NC, KDF11-AA, (4) MSV11-DD, BDV11-AA, DLV11-J, 120V, 50/60 Hz, 256 KB

- 11/23-AD = BA11-ND, KDF11-AA, (4) MSV11-DD, BDV11-AA, DLV11-J, 240V, 50/60 Hz, 256 KB

## **RL Systems Option Designations**

The RL systems include the earlier listed box systems with the RLV11 interface and two RL01s—5.24M bytes of data storage per RL01 (hard) disk drive.

- 11T23-AA = 11/23-AA, RLV11, (2) RL01-AK, H9612-AC cabinet, 871-A power controller, 120V, 50/60 Hz, 12A, 128 Kb

- 11T23-AB = 11/23-AB, RLV11, (2) RL01-AK, H9612-AC cabinet, 871-B power controller, 240V, 50/60 Hz, 8A, 128 Kb

- 11T23-AC = 11/23-AA, RLV11, (2) RL01-AK, H9612-AC cabinet, 871-C power controller, 120V, 50/60 Hz, 16A, 128 Kb

## **RX Systems Option Designations**

The RX systems include the earlier listed boxed systems with the RXV21 interface and two RX02s (floppy drives) with 512K bytes of data storage per drive.

- 11V23-AA = 11/23-AA, RXV21, RX02-BA, H9610-AC cabinet, 871-A power controller, 120V, 60 Hz, 12A, 128 Kb

- 11V23-AC = 11/23-AA, RXV21, RX02-BC, H9610-AC cabinet, 871-A power controller, 120V, 50 Hz, 12A, 128 Kb

- 11V23-AD = 11/23-AB, RXV21, RX02-BD, H9610-AC cabinet, 871-B power controller, 240V, 50 Hz, 8A, 128 Kb

## **BA11-N MOUNTING BOX**

The PDP-11/23 boxes and systems utilize the BA11-N box. For more specific details on the box, see the *Microcomputer Interfaces Handbook*.

## SPECIFICATIONS

| Input Power           |                                                                                                |

|-----------------------|------------------------------------------------------------------------------------------------|

| Voltage:              | 100-126 Vrms or 200-254 Vrms (switch-selected)                                                 |

| Frequency:            | 48-63 Hz                                                                                       |

| Power:                | 1380 W (maximum) including convenience outlet<br>633 W (maximum) power supply and modules      |

| Environmental         |                                                                                                |

| Temperature:          | 5° - 40° C (41° - 104° F)                                                                      |

|                       | Derate at 6° C (11° F)/1000 ft at altitudes above 8000 ft                                      |

| Relative<br>Humidity: | 10% to 95% (no condensation)                                                                   |

| Mechanical            |                                                                                                |

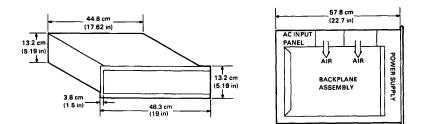

| Height:               | 13.2 cm (5.19 in)                                                                              |

| Width:                | 48.3 cm (19 in)                                                                                |

| Depth:                | without mounting brackets - 57.8 cm (22.75 in)<br>with mounting brackets - 67.98 cm (26.76 in) |

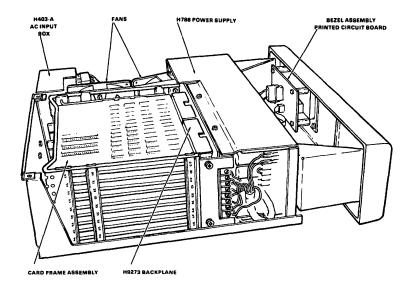

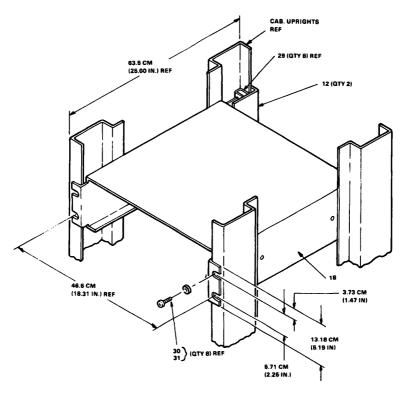

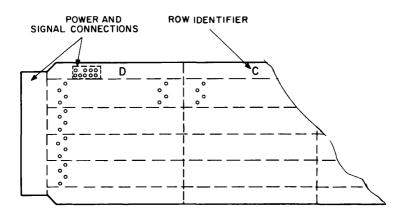

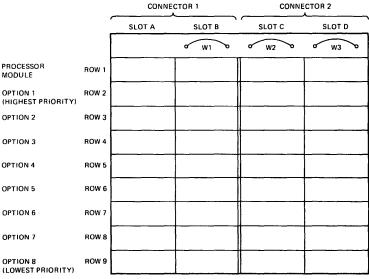

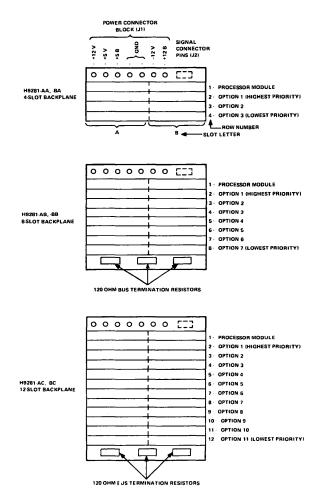

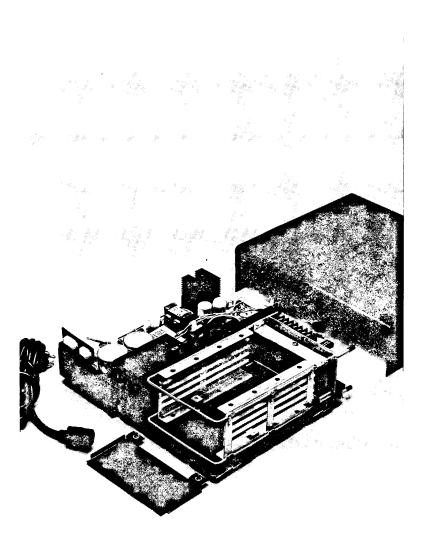

**BA11-N Major Assemblies**

**BA11-N Assembly Unit**

## SOFTWARE

The RL, hard disk based, PDP-11/23 system is offered with two operating systems, **RT-11** and **RSX-11**. Both support the PDP-11/23 memory management feature; however, the design and implementation of this support varies between the two systems.

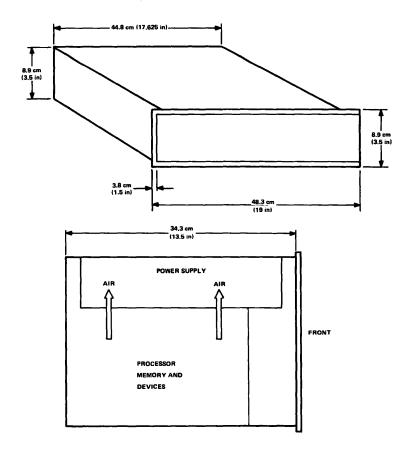

**BA11-N Cover Mounting Dimensions**

The RT-11 XM monitor feature can be utilized by a PDP-11/23 when the system is used by a single user requiring no more that two concurrent tasks. The XM monitor requires the user to handle program mapping above 56 Kb. It is, however, very efficient in supporting large programs where data exists only above 56 Kb. The present release of RT-11 (V3.B) is capable of supporting the PDP-11/23.

#### **RXS-11M Features:**

- multiuser

- multitasking

- checkpointing

- file protection

- mass storage base

- file storage and retrieval

- device independence

RSX-11M supports a variety of high-level languages, including FORTRAN IV, FORTRAN IV-PLUS, BASIC, BASIC PLUS-2, MACRO, CORAL 66, COGO and ANSI 74 COBOL. It also enables a number of programmers to share the 11/23 simultaneously while developing and debugging their programs.

Data management capability is provided by DATATRIEVE, DIGITAL's special inquiry and report writing language, by RMS-11 record management system, and by SORT-11. For intersystem communication, DIGITAL offers 2780/3271 protocol emulation and the industry's most advanced networking system, DECnet-11M.

## **RSX-11S Features:**

- memory-based

- multitasking

- subset of RSX-11M

As the smallest member of the RSX-11 family of real-time, multitasking operating systems, RSX-11S provides a dedicated, execute-only environment for monitoring and controlling many real-time processes concurrently. It is implemented as a memory-based, compatible subset of RSX-11M and, thus, is not dependent on any mass storage device for execution. RSX-11S system generation and program development take place on a host RSX-11M system. It supports non-filestructured data storage, runs programs written in FORTRAN and MACRO, and can be connected to other systems using DECnet-11S.

#### **RT-11 Features:**

- real-time

- single-job or foreground/background program execution

- supports 256 Kb of main memory

- mass storage-based

- easy-to-use command languages

- powerful editor

- debugging facilities

RT-11 is DIGITAL's single-user, foreground/background operating system. Fully interrupt-driven, overlapped input/output provide fast program execution and low overhead. Simultaneous execution of foreground/background tasks optimizes system capability. And a nested "common file" execution allows frequently used groups of system commands to be stored and recalled for execution with one simple command.

Like RSX-11M, RT-11 supports a variety of high-level programming languages, including BASIC and Multiuser BASIC, FORTRANIV, MACRO, APL, and FOCAL, DIGITAL's high-level interactive programming language for data acquisition and analysis. Data management capability is provided by FMS-11, DIGITAL's file management service. Communication with other systems can be effected through 2780 protocol emulation, DECnet-RT, and RT<sup>2</sup>/PDT, software that allows program loading from an RT-11 based system directly into our PDT-11/150 intelligent terminals.

## **CTS-300 Features:**

- timesharing

- fast terminal response

- easy to use

- interactive

- full-service utility routines

- line printer spooling

- dynamic memory allocation

- intertask communications

- multivolume files

- file sharing

CTS-300 (DIGITAL's Commercial Transaction Processing System) is a disk-resident, business-oriented operating system. Using our COBOL-like DIBOL-11 programming language, it provides simultaneous multiuser, multiterminal capability for transaction processing. Depending on the application program size, CTS-300 can support up to eight concurrent tasks. System access is gained through VT100 high-speed video terminals. Fast terminal response and greater memory availability are achieved because programs reside in memory in dynamic partitions while running.

Data management capability is provided by DIGITAL'S DECFORM, DMS-300, SORT/MERGE, and ISMUTL (which creates and maintains ISAM files). Intersystem communication is accomplished via DICAM or 3271/2780 protocol emulation.

## PDP-11/03-S AND PDP-11/03-L BOXES

The PDP-11/03-S and -L are boxed versions of the LSI-11 microcomputer. They includes a rack-mountable enclosure containing the LSI-11 processor, memory, and LSI bus-structured backplane, a power supply for the processor and memory, EIS/FIS chip standard, and use the double height processor and memory modules.

### Chapter 2—Systems and Software

# PDP-11/03-S (SMALL BOXES)

The 11/03-S Small Boxes ( $4 \times 4$  backplane)

### Option # Description

| 11/03-SC  | (KD11-HA, MSV11-DC, KEV11, BA11-MA) |

|-----------|-------------------------------------|

| 11/03-SD  | (KD11-HA, MSV11-DC, KEV11, BA11-MB) |

| 111/03-SE | (KD11-HA, MSV11-DD, KEV11, BA11-MA) |

| 11/03-SF  | (KD11-HA, MSV11-DD, KEV11, BA11-MB) |

### **BA11-M MOUNTING BOX**

The PDP-11/03-S includes the BA11-M box. For specific information on the BA11-M box, see the *Microcomputer Interfaces Handbook*.

### SPECIFICATIONS

### Environmental

| Temperature:       | 5°-40° C (41°-104° F)<br>Derate at 6° C (11°F)/1000 ft at altitudes |  |

|--------------------|---------------------------------------------------------------------|--|

|                    | above 8,000 ft.                                                     |  |

| Relative Humidity: | 10% to 95% (no condensation)                                        |  |

### PDP-11/03-L BOX

The PDP-11/03-L is a packaged and boxed version of the LSI-11 microcomputer. It includes a rack-mountable enclosure, the BA11-N box containing the LSI-11 processor and 32K bytes of memory, an LSI-11 bus-structured backplane, a bootstrap/diagnostic module, a 240 watt power supply, and a switch/indicator panel.

This box system retains the features of the smaller PDP-11/03s; however, the H786 power supply is capable of producing more than twice the dc power available in the smaller system (+5 V, 22 A and +12 V, 11 A). The H9273 backplane also has the added feature of having an interconnect scheme on the -CD side of the bus to let users configure special-purpose system functions.

The PDP-11/03-L box is available in four models, depending upon the memory and line cord supplied. The H786 power supply is universal; it can operate on 115 or 230 Vac, 50 or 60 Hz primary power. A switch is provided on the back of the BA11-N box for this purpose.

| Model    | Description                                 |

|----------|---------------------------------------------|

| 11/03-LH | KD11-HA, MSV11-DC, KEV11, BDV11-AA, BA11-NC |

| 11/03-LJ | KD11-HA, MSV11-DC, KEV11, BDV11-AA, BA11-ND |

| 11/03-LK | KD11-HA, MSV11-DD, KEV11, BDV11-AA, BA11-NC |

| 11/03-LL | KD11-HA, MSV11-DD, KEV11, BDV11-AA, BA11-ND |

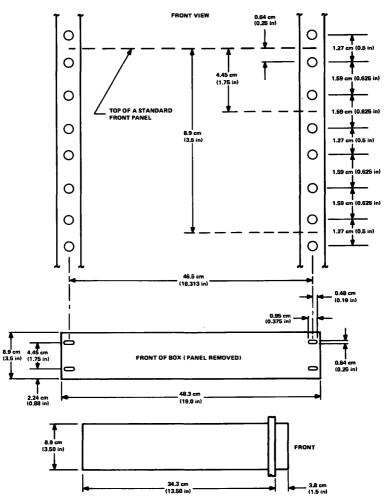

**BA11-M Assembly Unit**

# Packaged Systems are:

| SR-VXSSA | 11/03-LH, LJ |

|----------|--------------|

| SR-VXSSB | 11/03-LK, LL |

| SR-VXLLB | 11/03-LK, LL |

# PDP-11/03-L Specifications

### **Input Power**

Voltage: 100-127 Vrms or 200-254 Vrms (switch-selected)

Frequency: 48-63 Hz

**BA11-M Cabinet Mounting**

Power: 1380 W (maximum) including convenience outlet 633 W (maximum) power supply and modules

# Environmental

| Temperature:            | 5°-40° C (41°-104° F)<br>Derate at 6° C (11°F)/1000 ft at altitudes above 8000<br>ft. |

|-------------------------|---------------------------------------------------------------------------------------|

| Relative Hum-<br>idity: | 10% to 95% (no condensation)                                                          |

| Mechanical              |                                                                                              |

|-------------------------|----------------------------------------------------------------------------------------------|

| Height:                 | 13.2 cm (5.19 in.)                                                                           |

| Width:                  | 48.3 cm (19 in.)                                                                             |

| Depth:                  | without mounting brackets—57.8 cm (22.75 in.)<br>with mounting brackets—67.96 cm (26.75 in.) |

| Mounting<br>Dimensions: | Refer to the information on the BA11-N box in the PDP-11/23 section.                         |

# PDP-11V03-L PACKAGED SYSTEMS

The PDP-11V03-L is a complete, floppy disk-based packaged system that includes all necessary hardware, factory-configured and installed. The dual-drive, floppy disk system stores 1.0M bytes and is mounted in an attractive caster-equipped cabinet. The system is available in several variations, depending upon choice of terminal, input power, and the software operating system. The RT-11 single-user disk operating system is a selectable item in the packaged systems. Other compatible PDP-11 products, such as BASIC, FORTRAN or APL, are available as optional add-ons.

All PDP-11V03-L systems include the PDP-11/03-L microcomputer, which consists of the processor with KEV11 EIS/FIS extended arithmetic capability, 32K byte or 64K byte MOS memory, one or four serial line interfaces, BDV11 bootstrap/loader, and the RXV21 dual floppy disk system.

# PDP-11V03-L Specifications Summary

### Physical

| ,                                  | Heig          | iht               | Depth                | Width              |  |

|------------------------------------|---------------|-------------------|----------------------|--------------------|--|

| H9610-AA, AB<br>Cabinet            | 75.3<br>(30.9 | cm                | 75.3 cm<br>(30.9 in) | 53.3 cm<br>(21.25) |  |

| <b>Electrical</b><br>Input Voltage | 104-          | 126 Vac or 2      | 09-259 Vac           |                    |  |

| Frequency                          | 50 H          | $z \pm 0.5$ Hz or | 60 Hz ± 0.5          | Hz                 |  |

| Environmental<br>Power Consump     | tion:         | Typical (or       | idle)                | Maximum            |  |

| Computer Cabinet                   |               | (115 V) 110       |                      | 1240 W             |  |

|                                    |               | (230 V) 112       | 20 W                 | 1265 W             |  |

### PDP-11T03-L SYSTEMS

The PDP-11T03-L is a hard disk system that contains two top-loading RL01 cartridge disk drives providing a total of 10.4M bytes of storage. The system is available in several variations, depending upon choice

of terminal, input power, and software. The RT-11 operating system software is available as part of the standard packaged systems. Other compatible PDP-11 software products, such as BASIC, FORTRAN, or APL, are available as add-on options.

All PDP-11T03-L systems include the processor with EIS/FIS extended arithmetic capability, 64K byte MOS memory, DLV11-J four-line serial interface, BDV11 bootstrap/loader, and the RLV11 dual disk drive subsystem.

| Physical                                     |                       |                              |                    |                       |

|----------------------------------------------|-----------------------|------------------------------|--------------------|-----------------------|

|                                              | Height                |                              | Depth              | Width                 |

| H9612-AA, -<br>AB<br>Cabinet                 | 101.7 cn<br>(40.5 in) |                              | 75.3 cm<br>(30 in) | 53.3 cm<br>(21.25 in) |

| <b>Electrical</b><br>Input Voltage           |                       | 104-126                      | Vac or 209-2       | 54 Vac                |

| Frequency                                    |                       | 50 Hz ±                      | 0.5 Hz or 60 H     | lz ± 0.5 Hz           |

| Environmental                                |                       |                              |                    |                       |

| Ambient Temperature                          |                       | 10°-43° C(50°-110° F)nominal |                    |                       |

| <b>Relative Humidity</b>                     |                       | 8% to 80% (no condensation)  |                    |                       |

| Barometric Pressure                          |                       | 3,000 m (10,000 ft) maximum  |                    |                       |

| Temperature Change<br>Rate                   |                       | 6° C(10° F) per h            |                    |                       |

| Disk Interchangeability<br>Temperature Range |                       | 17° C(30° F)                 |                    |                       |

# PDP-11T03-L Specifications Summary

# PDP-11/03 SYSTEM SOFTWARE

Software systems include the operating system, programming languages, diagnostic software, paper tape software, and special-purpose software options.

Available PDP-11/03 and PDP-11/03-L system software includes:

- RT-11 Operating System, including Single Job and Foreground/Background Monitors.

- RT-11 FORTRAN

- RT-11/BASIC

- RT-11/MULTI-USER BASIC

- RT-11/FOCAL

# CHAPTER 3 LSI-11/23 PROCESSOR

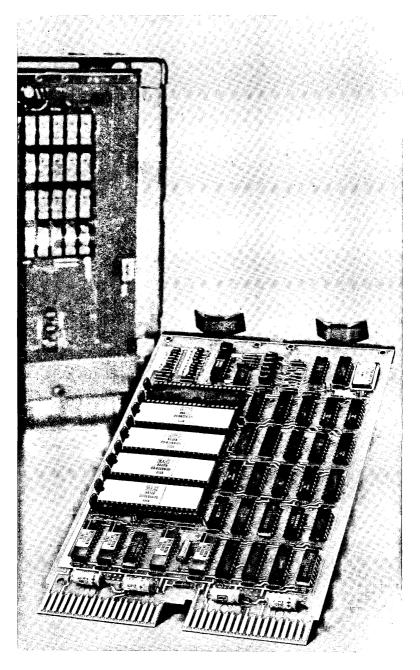

# GENERAL

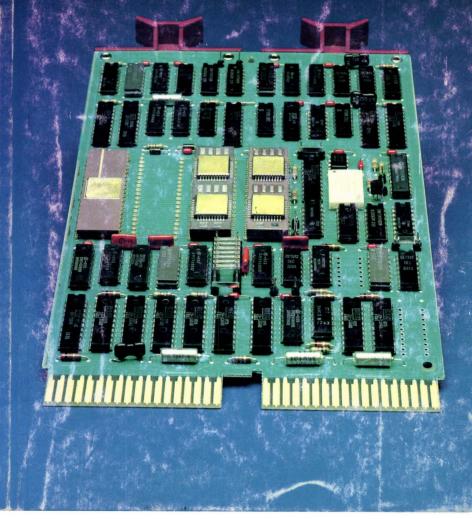

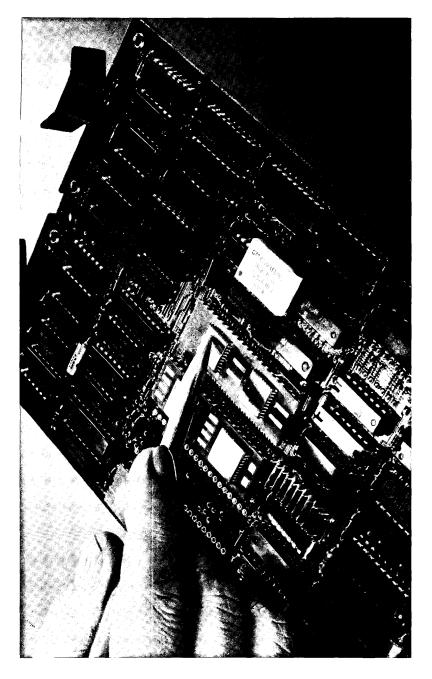

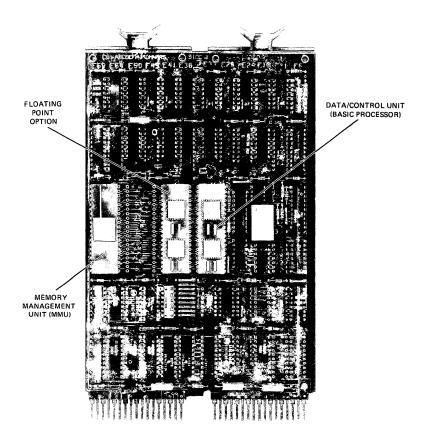

The KDF11-AA is a 16-bit, high-performance microprocessor contained on one dual-height multilayer module (M8186). The figure shows the module with its major components highlighted. Utilizing the latest MOS/LSI technology, the KDF11-AA brings the full PDP-11/34 functionality to a microprocessor that communicates along the LSI-11 bus. The KDF11-AA contains memory management as a standard feature and offers floating point as an option (KEF11-A).

The processor uses the LSI-11 bus with a new 4-level interrupt bus protocol and parity check feature. The KDF11-AA is compatible with existing LSI-11 processors and devices.

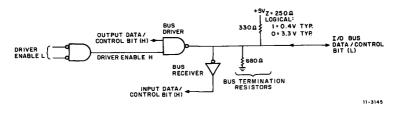

The LSI-11 bus was built around LSI technology requirements consistent with low cost, high performance, and small board form factors. Low cost and high performance are realized, in part, by using multifunction lines such as the data/address lines (DAL) that reduce the number of pins to the bus. Other lines, such as the I/O page address decode line, eliminate hardware by removing the need for identical page decoders on each interface module. A detailed description of the LSI-11 bus is contained in Chapter 8.

The KDF11-AA is software-compatible with the PDP-11 family. A wide range of software is available, including programming languages, diagnostic software, and operating systems.

# FEATURES

The KDF11-AA contains the following features:

- Four-level vectored interrupts provide for fast interrupt response without device polling.

- Optional memory management for 256K bytes of protected, multiuser program space.

- Memory parity errors are recognized during every data-in bus cycle.

- Over 400 instructions for powerful and convenient programming.

- 16-bit word or 8-bit byte addressable locations.

- Eight internal general-purpose registers for use as accumulators and for operand addressing.

- Stack processing for easy handling of structured data, subroutines, and interrupts.

KDF11-AA Processor Module (M8186) (Shown with Optional Floating Point)

- Asynchronous bus operation allows processor and system components (memory and peripherals) to run at their highest possible speed.

- Direct memory access (DMA) allows peripherals to access memory without interrupting processor operation.

- Modular component design allows systems to be easily configured and upgraded.

- Power fail and automatic restart hardware detect and protect against ac power fluctuations.

- Compact, double-height module size for versatile packaging.

- ODT console emulator for ease of program debugging.

| SPECIFICATIONS          |                                                                                                    |

|-------------------------|----------------------------------------------------------------------------------------------------|

| Identification          | M8186                                                                                              |

| Size                    | Double                                                                                             |

| Dimensions              | 13.34 cm × 21.59 cm<br>(5.25 in × 8.5 in)                                                          |

| Power Requirements      | +5 V ± 5%, 2.0 A<br>+12 V ± 5%, 0.2 A                                                              |

| Bus Loads               | ac 2 unit loads<br>dc 1 unit load                                                                  |

| Environmental           |                                                                                                    |

| Storage                 | 40° C to 65° C (104° F to 149° F)<br>10% to 90% relative humidity, non condens-<br>ing             |

| Operating               | 5° C to 60° C, (41° F to 140° F)                                                                   |

|                         | Maximum outlet temperature rise of 5° C<br>(9° F) above 60° C (140° F)                             |

|                         | Derate maximum temperature by 1° C (1.8°<br>F) for each 305 m (1000 ft) above 2440 m<br>(8000 ft). |

| Timing (Based on 300 ns | CPU microcycle time)                                                                               |

(Refer to Appendix A for detailed listing of instruction times.)

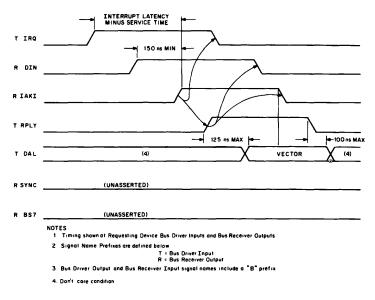

Interrupt Latency (based on MSV11-D without parity, add 500 ns worst case with parity)

Worst Case

\_\_\_\_

55.7 microseconds (for infrequently used instructions) 10.8 microseconds (for more frequently used group)

| Typical                | 6.0 microseconds               |

|------------------------|--------------------------------|

| Interrupt Service Time | 8.2 microseconds               |

| DMA Latency            | 3.49 microseconds (worst case) |

# DESCRIPTION

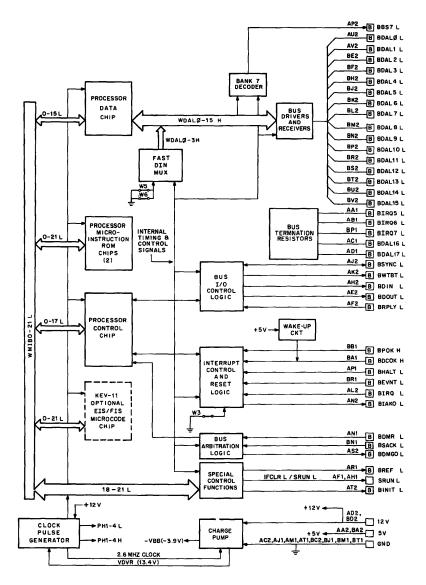

### GENERAL PROCESSOR HARDWARE

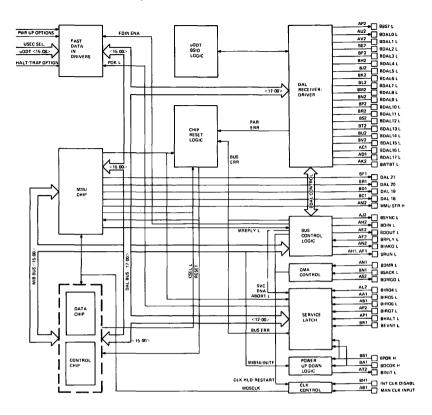

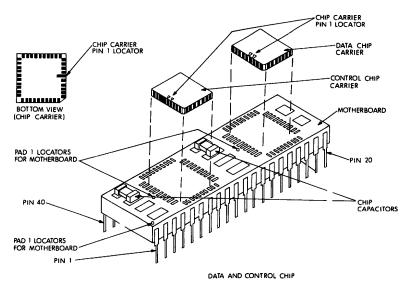

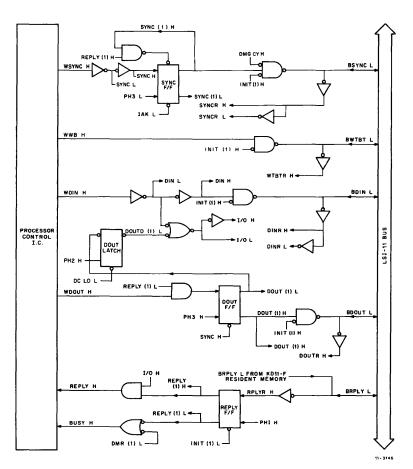

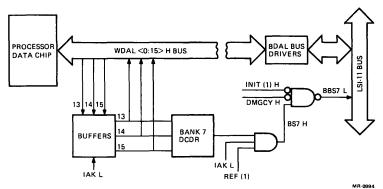

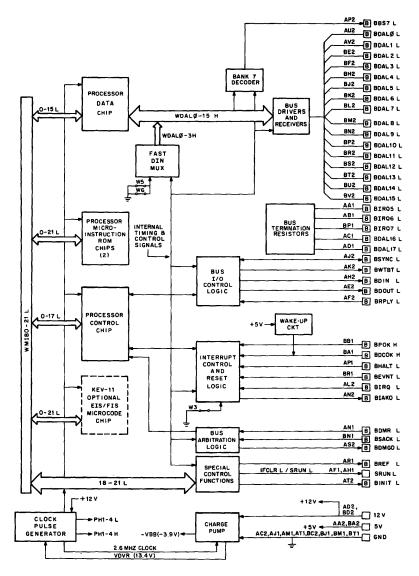

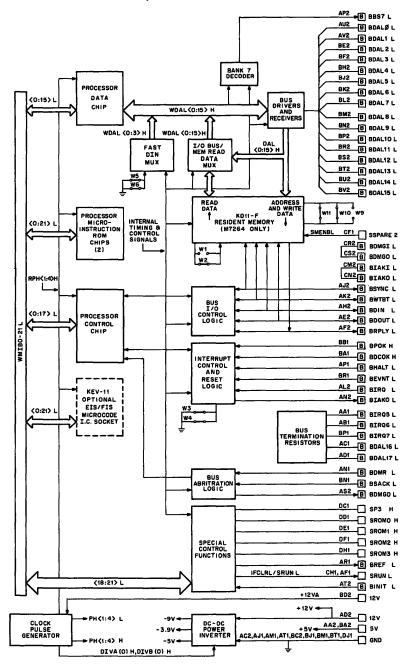

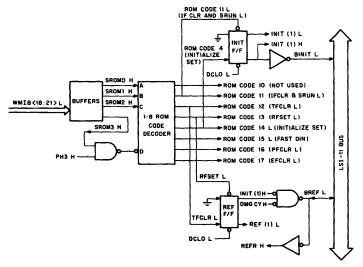

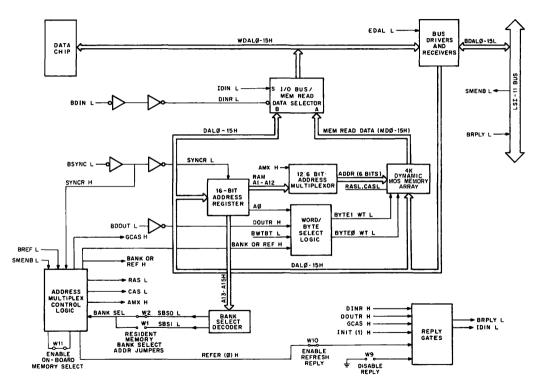

The KDF11-AA processor is implemented using three chips. Two MOS/LSI chips, data and control, implement the basic processor. The memory management unit (MMU), the third chip, provides a PDP-11/34 software-compatible memory mangement scheme.

The data chip (DC302) performs all arithmetic and logical functions, handles data and address transfers with the external world, and coordinates most interchip communication. The control chip (DC303) does microprogram sequencing for PDP-11 instruction decoding and contains the control store ROM. The data and control chips are both contained in one 40-pin package. The MMU chip (DC304) contains the registers for 18-bit memory addressing and also includes the FP11 floating point registers and accumulators. Optional floating point requires the MMU chip. Data and control chips do not need the MMU chip for 16-bit addressing.

# Data Chip

The data chip contains the PDP-11 general registers, the processor status word (PS), several working registers, the arithmetic and logic unit (ALU), and conditional branching logic. The data chip does the following.

- 1. Performs all arithmetic and logical functions.

- 2. Handles all data and address transfers with the LSI-11 bus (except relocation, which is handled by the MMU).

- 3. Generates most of the signals used for interchip communication and external system control.

# **Control Chip**

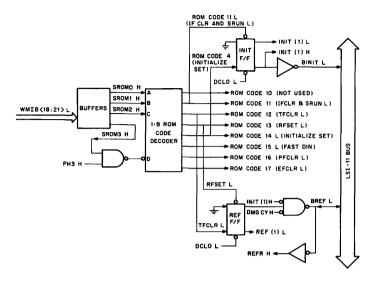

The control chip contains the microprogram sequence logic and 552 words of microprogram storage in programmable logic arrays (PLA) and read-only memory (ROM) arrays.

During the course of a normal microinstruction cycle, the control chip accesses the appropriate microinstruction in the PLA or ROM, sends it along the MIB to the data and MMU chips for execution, and then generates the address for the next microinstruction to be accessed. The next address is constructed from either a next address field associated with the current microinstruction or, if a microprogrammed

### Chapter 3—LSI-11/23 Processor

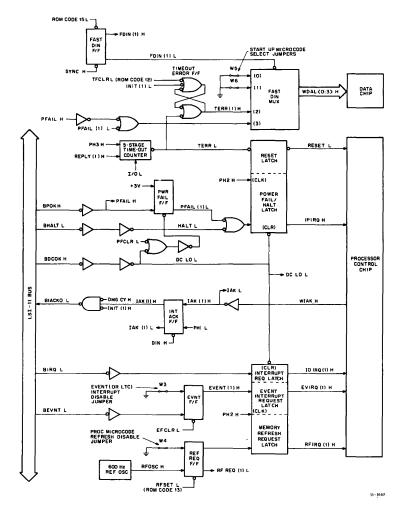

Processor Functional Block Diagram

branch is to be executed, the target address contained within the microinstruction itself. The control chip operation is pipelined for better performance so that the next microinstruction is being accessed while the current one is being executed. This next address is then used in conjunction with various internal status and external service inputs to determine the microprogram sequence. The control chip accesses only its local storage. However, multiple chips (up to 32) can be cascaded with external buffering to provide additional microstore.

**Chip Select (CSEL)** — CSEL is an open collector line which is routed to all MOS chips on the board except the MMU. The active control chip holds the line low. If a nonexistent control chip is selected by the microcode, the line is pulled high. This causes a control chip error and a trap to location  $10_8$ >

LSI-11/23 Data and Control Chip

### **MMU Chip**

The MMU chip serves two purposes: it provides the memory management function, and it provides storage for the FP11 floating point accumulators and status registers. This chip provides dual mode (user and kernel) address relocation of 18 bits. Sixteen-bit virtual addresses are received from the data chip via the data address lines (DAL), relocated to the appropriate 18-bit physical address, and then sent on the DAL to replace the original virtual address for transmission to the external system bus. The MMU chip contains the status registers and active page registers (PAR/PDR register pairs), as well as access protection and error detection capability. The MMU chip also provides the thirtysix 16-bit registers needed for operand storage, scratchpad areas, and status information storage during floating point operations.

The MMU chip is controlled by information received on the microinstruction bus (MIB) from both the data chip and the control chip, and by several discrete control inputs.

The KDF11-AA can operate without the MMU chip; however, the memory would be limited to 64K bytes and the floating point registers would not be available.

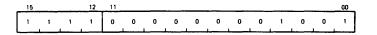

### **General-Purpose Registers**

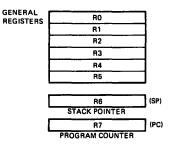

The data chip contains eight 16-bit general-purpose registers that provide for a variety of functions. These registers can serve as

accumulators, index registers, autoincrement registers, autodecrement registers, or as stack pointers for temporary storage of data. Arithmetic operations can be from one general register to another, from one memory location or device register to another, between memory locations, or between a device register and a general register. The figure identifies the eight 16-bit general registers R0 through R7.

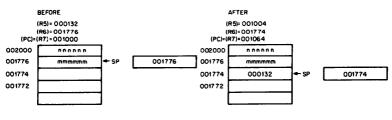

Registers R6 and R7 are dedicated. R6 serves as the stack pointer (SP) and contains the location (address) of the last entry in the stack. Three different SP registers are used to implement the memory management feature. The highest-order PSW bits are used to select the appropriate register for the current operating mode-kernel or user. (Note: the third registers is reserved for future DIGITAL use.) Register R7 serves as the processor's program counter (PC) and contains the address of the next instruction to be executed. It is normally used for addressing purposes only and not as an accumulator. Register operations are internal to the processor and do not require bus cycles (except for instruction fetch); all memory and peripheral device data transfers do require bus cycles and longer execution time. Thus, general registers used for processor operations result in faster execution times.

**General Register**

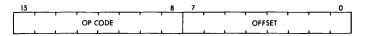

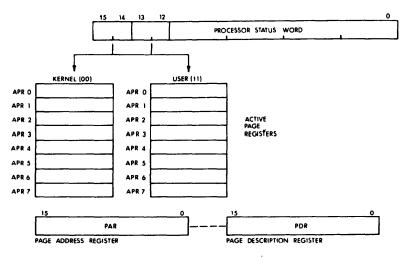

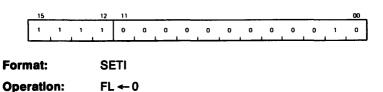

# **Processor Status Word (PS)**

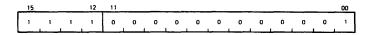

The processor status word (PS) is in the data chip and contains information on the current processor status. As the figure shows, this includes: the condition codes describing the arithmetic or logical results of the last instruction, a trace bit that forces a trap at the end of instruction execution (used during program debug), the current processor priority, an indicator of the previous memory management mode, and an indicator of the current memory management mode.

**Condition Codes (PS bits 3:0)** — The condition codes contain information on the result of the last CPU operation. The bits are set after execution of all arithmetic or logical single-operand or double-operand instructions. The bits are set as follows:

- N = 1 if the result was negative.

- Z = 1 if the result was 0.

- V = 1 if the operation resulted in an arithmetic overflow.

- C = 1 if the operand resulted in a carry from the MSB (most significant bit) or a 1 was shifted from MSB or LSB (least significant bit).

Processor Status Word (PS)

**Trace Bit (PS bit 4)** — The trace bit is used in debugging program since it allows programs to be single-instruction stepped.

**Priority Level (PS bits 7:5)** — These bits are used by software to determine which interrupts will be processed.

| Octal Value of PS<7:5> | Interrupt Level Acknowledged* |

|------------------------|-------------------------------|

| 7                      | none                          |

| 6                      | 7,                            |

| 5                      | 7, 6,                         |

| 4                      | 7, 6, 5,                      |

| 3                      | 7, 6, 5, 4                    |

| 2                      | 7, 6, 5, 4                    |

| 1                      | 7, 6, 5, 4                    |

| 0                      | 7, 6, 5, 4                    |

|                        |                               |

\* Higher levels acknowledged first.

**Suspended Instruction (SI) (PS bit 8)** — This bit is reserved for DIGITAL use and is intended for future optional instruction sets. This bit is read/write and has no protection mechanism.

**Previous Mode (PS bits 13:12)** — These bits are used with memory management to indicate what the last memory management mode was. They are read/write bits and are present even without the memory management option.

**Current Mode (PS bits 15:14)** — These bits indicate what the present memory management mode is. They are read/write and are present even without the memory management option.

# **Memory Management**

Memory management has the following three major features:

- 1. Two software modes that are useful for multiuser (timesharing) systems.

- 2. Extended physical addressing (greater than 64K bytes, up to 256K bytes) for allowing more than one program to reside in memory at the same time.

- 3. Memory protection for controlling user program access to system resources (e.g., memory, I/O).

The first feature has two software modes, kernel and user. Kernel mode is employed for executing a user program and restricts processor privileges (e.g., HALT instruction cannot be executed). The second feature utilizes mapping registers to map the 64K-bytes virtual address space anywhere in the 256K-bytes physical address space. The third feature allows restricted access to virtual memory pages (a page is between 0 and 8K bytes long). This permits the operating system software rather than user programs to control system resources. Chapter 9 contains a complete discussion of memory management.

# **INSTRUCTION SET**

The KDF11-AA instruction set provides over 400 powerful instructions. As a comparison, consider that most other (i.e., accumulator-oriented) 16-bit processors require three separate instructions to execute a common double-operand instruction (e.g., ADD).

# **Conventional Approach**

| LDA A | Load contents of memory location A into accumula-<br>tor. |

|-------|-----------------------------------------------------------|

| ADD B | Add contents of memory location B to accumulator.         |

| STA B | Store result at location B.                               |

By constrast, the KDF11-AA can fetch both operands, execute, and store the result in one instruction.

### KDF11-AA Approach

ADD A, B Add contents of location A to location B; store results at location B.

This greater efficiency not only saves memory space and time, but also improves processor speed since fewer instruction fetches are required.

Another major advantage to the KDF11-AA instruction set is the absence of special-purpose input/output instructions. Special I/O instructions are unnecessary since peripheral device registers are accessed in the same way as main memory locations. This approach to handling I/O devices allows the normal instruction set to be used to test and/or manipulate the various I/O device register bits. For example, a compare instruction can test status bits directly in the I/O device register without bringing them into memory or disturbing any of the general registers; control bits can be set, cleared, or shifted as is most convenient; and peripheral data can be arithmetically or logically altered when received at the device register and before being stored in memory. Refer to Chapter 7 for a complete description of the instruction set@nd its utilization.

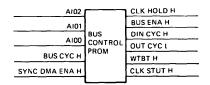

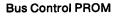

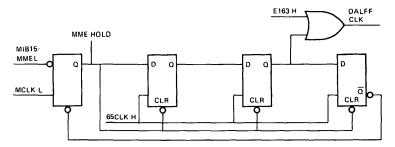

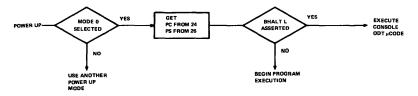

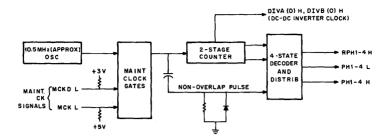

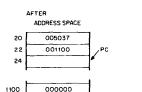

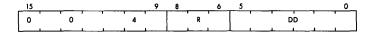

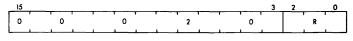

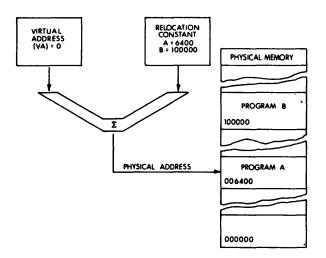

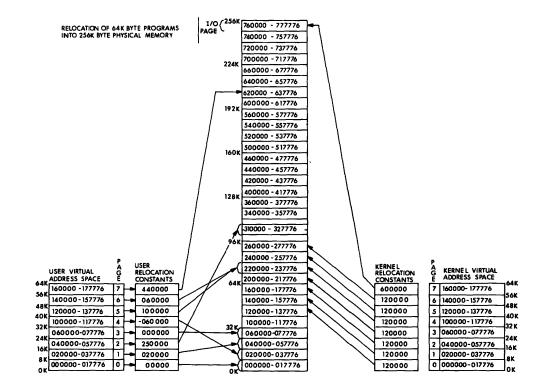

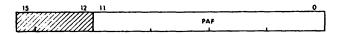

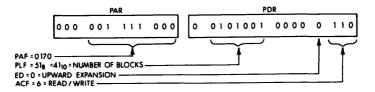

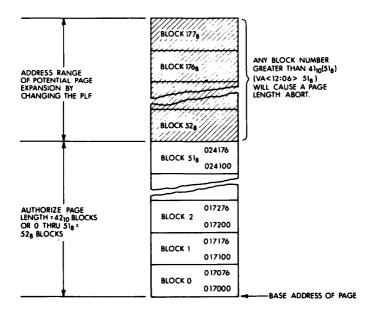

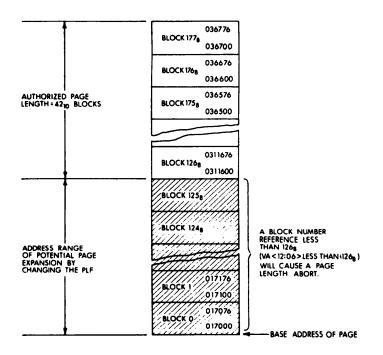

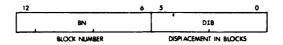

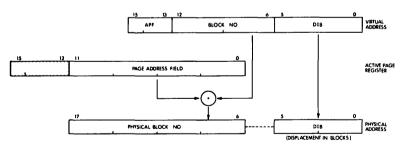

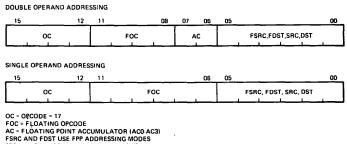

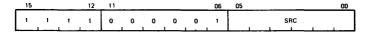

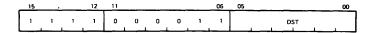

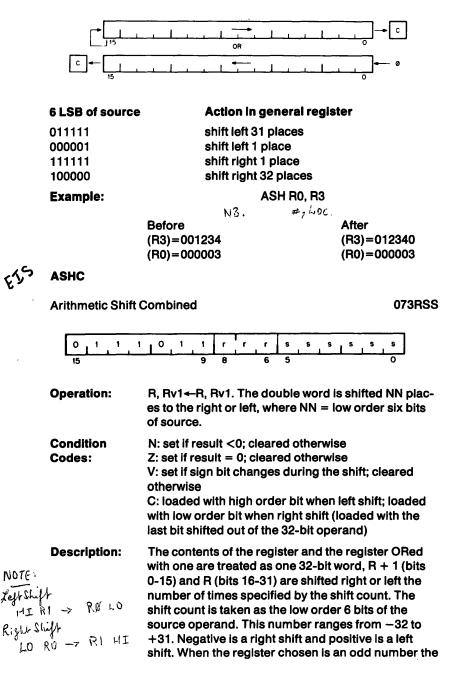

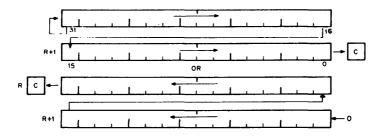

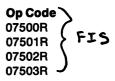

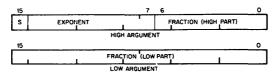

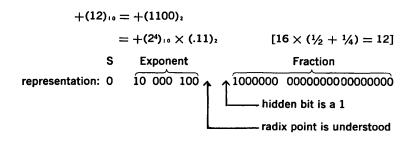

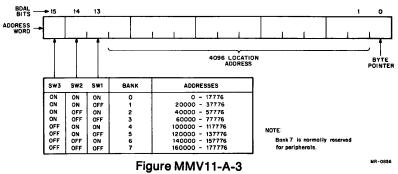

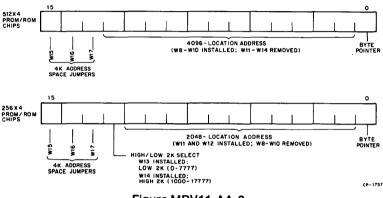

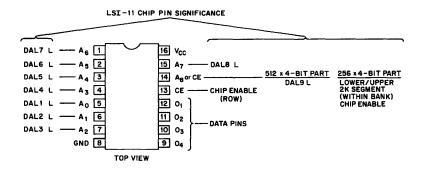

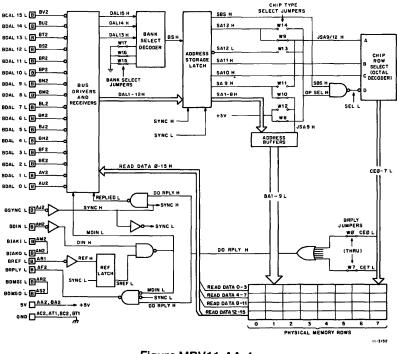

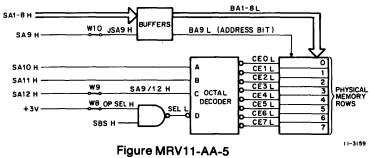

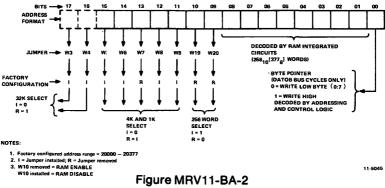

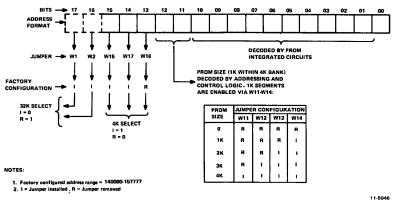

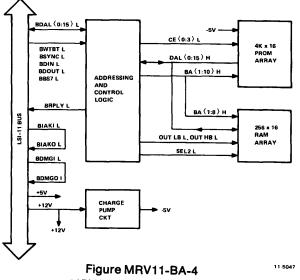

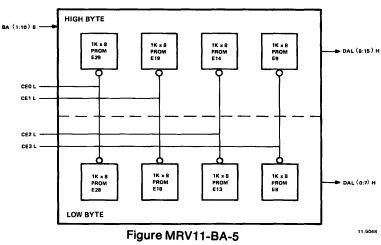

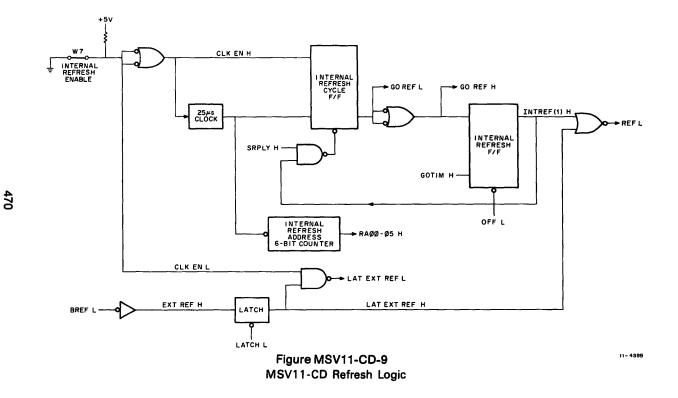

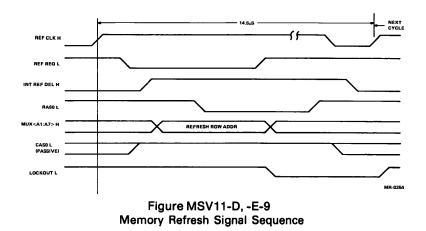

# **Addressing Modes**