# digital

# microcomputer interfaces handbook

DIGITAL facility, Marlboro, Massachusetts

# **CORPORATE PROFILE**

Digital Equipment Corporation designs, manufactures, sells and services computers and associated peripheral equipment, and related software and supplies. The Company's products are used world-wide in a wide variety of applications and programs, including scientific research, computation, communications, education, data analysis, industrial control, timesharing, commercial data processing, word processing, health care, instrumentation, engineering and simulation.

# microcomputer interfaces handbook

#### Copyright<sup>©</sup> 1981 Digital Equipment Corporation. All Rights Reserved.

Digital Equipment Corporation makes no representation that the interconnection of its products in the manner described herein will not infringe on existing or future patent rights, nor do the descriptions contained herein imply the granting of license to make, use, or sell equipment constructed in accordance with this description.

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this manual.

DEC, DECnet, DECsystem-10, DECSYSTEM-20, DECtape, DECUS, DECwriter, DIBOL, Digital logo, IAS, MASSBUS, OMNIBUS, PDP, PDT, RSTS, RSX, SBI, UNIBUS, VAX, VMS, VT are trademarks of Digital Equipment Corporation

> This handbook was designed, produced, and typeset by DIGITAL's New Products Marketing using an in-house text-processing system operating on a DECSYSTEM-20.

## CONTENTS

## **PART 1 INTRODUCTION**

| GENERAL                          |          | <br> | <br>    | <br> | • • | <br>  | 1 |

|----------------------------------|----------|------|---------|------|-----|-------|---|

| LSI-11 FAMILY CHARACTERISTICS    |          | <br> | <br>••• | <br> |     | <br>  | 1 |

| SPECIFICATIONS                   |          | <br> | <br>    | <br> |     | <br>  | 4 |

| DESCRIPTION OF OPTION CATEGORIES | <b>;</b> | <br> | <br>    | <br> |     | <br>  | 5 |

| CONFIGURATION                    |          | <br> | <br>    | <br> |     | <br>2 | 5 |

## **PART 2 LSI-11 BUS INTERFACE DESCRIPTIONS**

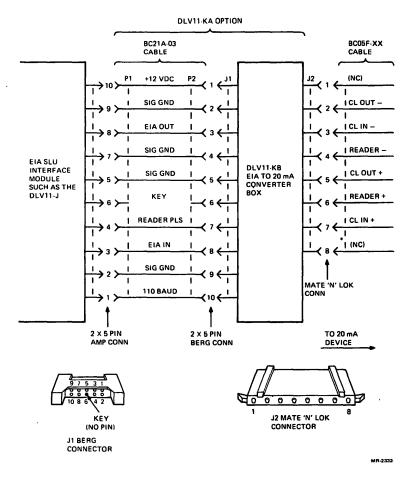

| AAV11-A 4-Channel 12-Bit D/A Converter              | 33  |

|-----------------------------------------------------|-----|

| ADV11-A Analog to Digital Converter                 | 45  |

| BA11-M Expansion Box                                | 67  |

| BA11-N Mounting Box                                 | 74  |

| BA11-VA Expansion Mounting Box                      | 83  |

| BDV11 Diagnostic, Bootstrap, Terminator             | 86  |

| DCK11-AA, -AC Program Transfer Interface            | 114 |

| DCK11-AB, AD Direct Memory Access Interface         | 134 |

| DDV11-B Backplane                                   |     |

| DLV11 Serial Line Unit                              |     |

| DLV11-E Asynchronous Line Interface                 |     |

| DLV11-F Asynchronous Line Interface                 |     |

| DLV11-J Four Asynchronous Serial Interfaces         |     |

| DLV11-KA EIA to 20 mA Converter                     |     |

| DRV11 Parallel Line Unit                            |     |

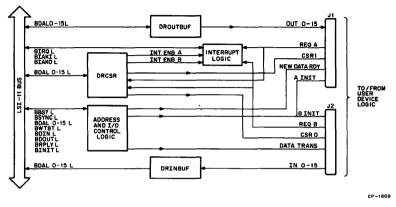

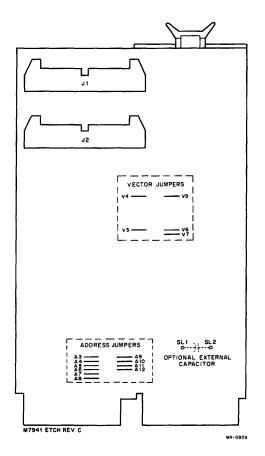

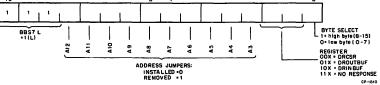

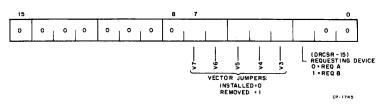

| DRV11-B Direct Memory Access Interface              | 282 |

| DRV11-J High-Density Parallel Interface             |     |

| DRV11-P LSI-11 Bus Foundation Module                |     |

| DUV11 Line Interface                                |     |

| DZV11 Asynchronous Multiplexer                      |     |

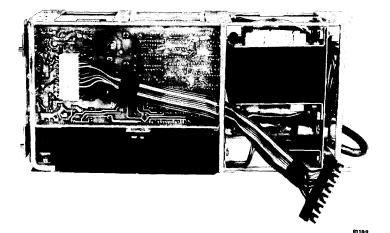

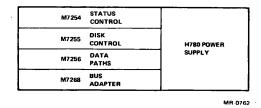

| H780 Power Supply                                   |     |

| H909C General Purpose Logic Enclosure               |     |

| H984 Series Cabinets                                |     |

| H9270 Backplane                                     |     |

| H9273-A Backplane                                   | 431 |

| H9281 Backplane                                     |     |

| H9800-A Cabinet                                     |     |

| IBV11-A Instrument Bus Interface                    |     |

| KPV11-A,-B,-C Power-Fail/Line-Time Clock/Terminator |     |

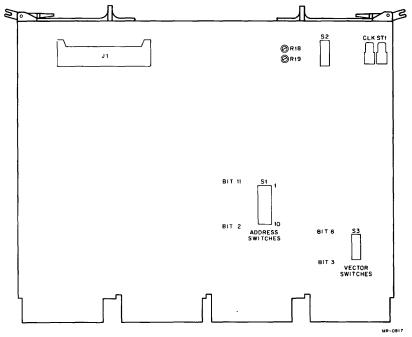

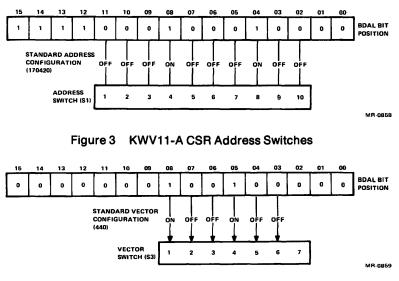

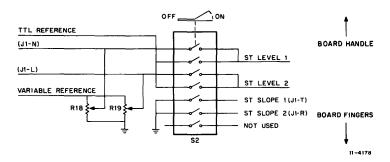

| KWV11-A Programmable Real-Time Clock                |     |

| LAV11 Printer Option                                |     |

| LPV11 Printer Option                                | 517 |

| RKV11-D RK05<br>RLV11 RL01 Dis<br>RXV11 Floppy I<br>RXV21 Floppy I<br>TEV11 Termina<br>TU58 Cartridge<br>VK170-CA Seria | nator, REV11-C DMA Refresh, Bootstrap              |

|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| APPENDIX A                                                                                                              | ASSIGNMENT OF<br>Addresses and vectors             |

| APPENDIX B                                                                                                              | LSI-11 BUS SIGNALS                                 |

| APPENDIX C                                                                                                              | NOMENCLATURE FOR CIRCUIT<br>SCHEMATICS             |

| APPENDIX D                                                                                                              | ASYNCHRONOUS SERIAL LINE UNIT (SLU)<br>COMPARISONS |

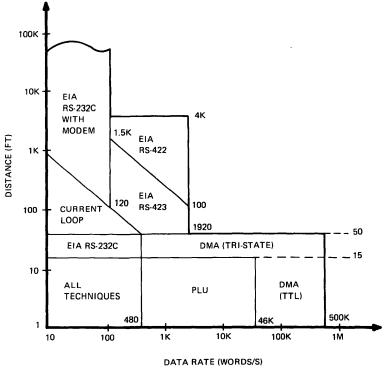

| APPENDIX E                                                                                                              | COMPARISON OF DATA TRANSMISSION<br>TECHNIQUES      |

| APPENDIX F                                                                                                              | INTEGRATED CIRCUITS732                             |

| APPENDIX G                                                                                                              | CABLING SUMMARY                                    |

#### GENERAL

This handbook is a reference guide for the interface and peripheral hardware options that can be installed on the LSI-11 bus. It includes descriptions, specifications, configuration information, programming information as applicable to the options, and functional theory. Because the hardware options described in this handbook are designed to interface with a processor via the LSI-11 bus, the user should be familiar with the contents of the appropriate processor handbook.

The handbook is organized into two parts. Part 1 contains general information about microcomputer interfaces; Part 2 contains description of the interface options in alphanumeric sequence.

Digital Equipment Corporation designs and manufactures the options described in this handbook. The general design criterion was to provide maximum system throughput for options when installed on the LSI-11 bus. LSI-11 bus-compatible processors, interfaces, and peripherals are designed to work together, providing a broad spectrum of system-compatible hardware options. The memory and peripheral devices can be used with various LSI-11 bus configuration; the system can later be expanded or modified to meet new system requirements. This hardware flexibility, when coupled with DIGITAL software and support, provides a single source for all present and future microcomputer processing needs.

### LSI-11 FAMILY CHARACTERISTICS

LSI-11 bus systems include various processors, memory and peripheral device options, and software. Some of the characteristics of the LSI-11 bus systems are:

- Low-cost powerful components for integration into any small- or medium-sized computer system.

- Direct addressing of all memory locations and peripheral device registers.

- Efficient processing of 8-bit bytes (characters) without the need to rotate, swap, or mask.

- Asynchronous bus operation that allows system components to run at their highest possible speed; replacement with faster devices means faster operation without other hardware or software changes.

- A module component design that provides ease and flexibility in configuring systems.

- Inherent direct memory access capabilities for high data rate devices.

- A bus structure that provides position-dependent priority for peripheral device interfaces connected to the I/O bus.

- Vectored interrupts that allow service routine entry without device polling.

#### Processors

The processor is connected to the LSI-11 bus (backplane) as a subsystem that executes programs and arbitrates usage of the LSI-11 bus for peripherals. It contains multiple, high-speed, general-purpose registers that can be used as accumulators, address pointers, index registers, and other specialized functions. The processor can perform data transfers directly between peripheral input/output (I/O) devices and memory without disturbing the processor registers. Data transfers include both 16-bit word and 8-bit byte data.

## LSI-11 Bus

System components, including the processor, memory, and peripherals, are interconnected and communicate with each other via the LSI-11 bus. The form of communication is the same for all devices on the bus; instructions that communicate with memory can communicate with peripheral devices. Each device, including memory locations and peripheral device registers, is assigned an individual byte or word address on the LSI-11 bus.

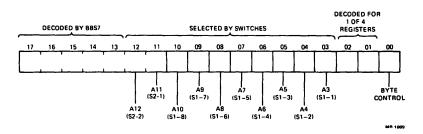

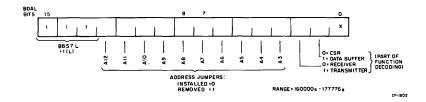

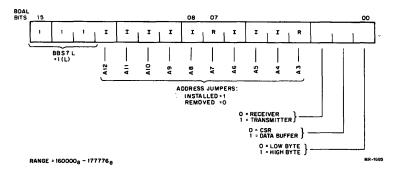

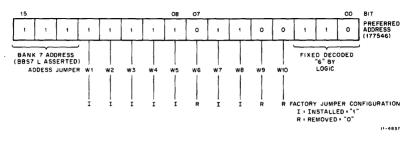

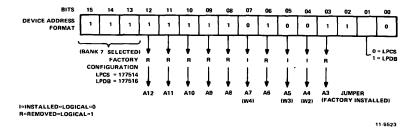

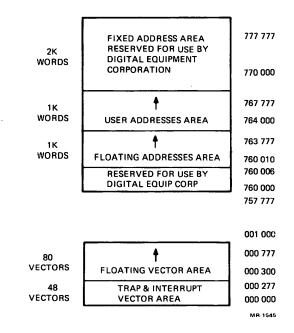

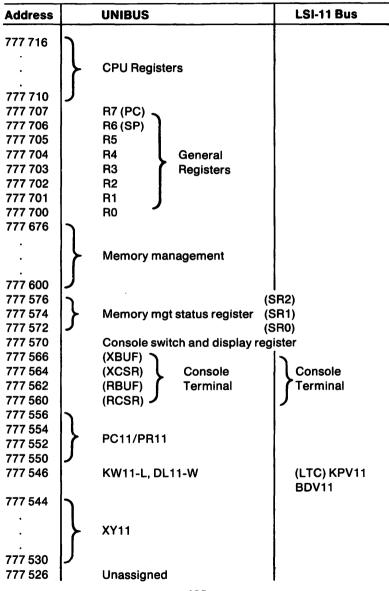

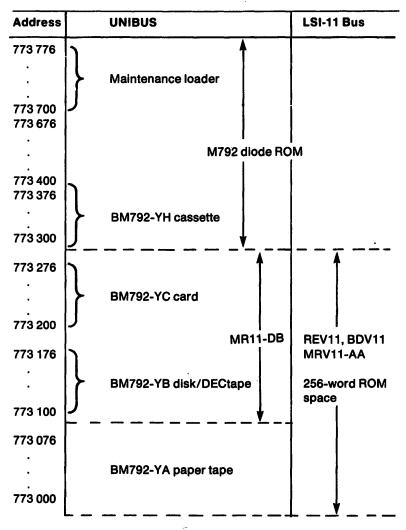

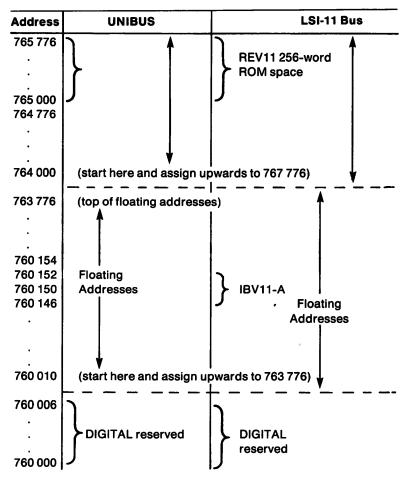

The LSI-11 bus supports 18-bit addresses. However, processors and peripherals having a 16-bit addressing capability are completely PDP-11 hardware- and software-compatible within the 16-bit limitation. By PDP-11 convention, all peripheral device addresses are located within the upper 4K address space in the system, whether 16-bit or 18-bit addresses are used. This 4K address space is called the I/O page or "bank 7."

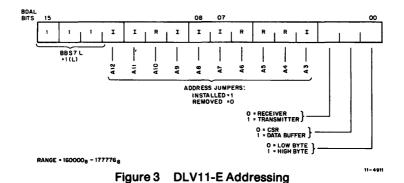

Whenever the I/O page is addressed, the processor must assert the BBS7 L bus signal. All peripheral devices use this signal line during addressing rather than decoding address bits <15:13> or <17:13>. An active (asserted) BBS7 L signal will always indicate an address in the I/O page, enabling peripheral device addressing.

Peripheral device addresses within the I/O page are decoded by each peripheral device. Each peripheral device will include one or more "device register(s)." These registers can be accessed under program

control in exactly the same manner as memory locations. Unique addresses within the I/O page are encoded on address bits <12:00>.

#### NOTE

Address bits, for the purpose of this discussion, are logical states present on LSI-11 bus signal lines BDAL < 17:00 > L during the addressing portion of a bus cycle.

Refer to the appropriate processor handbook for a complete description of bus transactions, including bus cycles, addressing, etc.

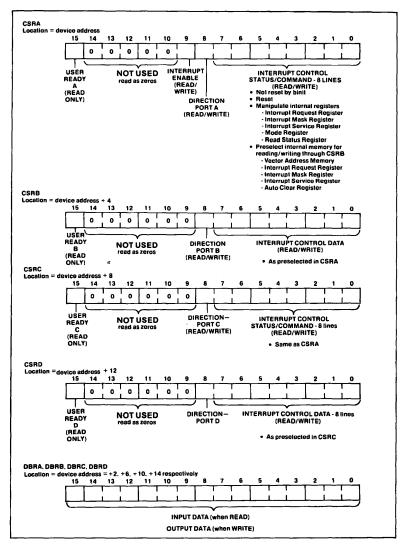

### **Device Registers**

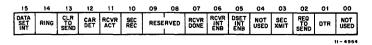

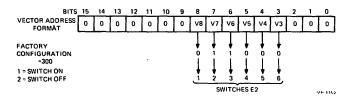

All peripheral devices are defined by one or more device registers that are addressed as part of the main memory. These registers are generally designated control and status registers.

Control and status registers (CSRs) contain all the necessary information to establish communications with the device. Some devices will require fewer than 16 status bits, while other devices could require more than 16 bits and therefore will require additional registers. The bits of the CSR have predetermined assigned functions. Typical bit functions include interrupt enable, error, done or ready, and enabled.

Data buffer registers (DBRs) are for temporarily storing data to be transferred into and out of the processor. The number and type of data registers is a function of the individual peripheral device requirements.

### Interrupts

Interrupts allow devices to obtain processor service when they are "ready" for service, or "done" with a specific operation. The interrupt structure allows the processor to execute other programs while one or more peripherals are "busy." When a peripheral requires service it requests an interrupt. The processor completes execution of the present instruction, saves PC and PS words on the stack, and acknowledges the interrupt. The highest priority peripheral device currently requesting interrupt service responds by inputting its interrupt vector address to the processor. The processor uses this vector address as a pointer to two memory locations containing the PC (starting address) and PS for the peripheral device interrupt service routine. Program control is transferred from the interrupted program to the routine associated with the requesting peripheral device. Note that no device polling is required, since the interrupt vector is unique for that

device. Once the device service routine execution has been completed, control is returned either to the previously interrupted program or to another peripheral device requesting interrupt service.

#### **Memory Address**

Memory addresses are generally limited to the address space other than the I/O page. However, the I/O page can contain read-only memory (ROM) for disk bootstraps, paper tape loaders, diagnostics, etc. or read/write memory for DMA buffers. The system designer must use care in assigning memory addresses within the I/O page to avoid conflicts with peripheral device addresses used for actual system hardware, or addresses that system software may attempt to access for peripheral devices not actually installed in the system. See Appendix A for the standard assignments of the addresses in the I/O page.

#### SPECIFICATIONS

All the LSI-11 bus modules will operate under the following conditions:

| Temperature | 5° to 60° C (41° to 140° F) |

|-------------|-----------------------------|

| Humidity    | 10 to 95% (no condensation) |

When operating at the maximum outlet temperature ( $60^{\circ}$  C or 140° F), adequate air flow must be maintained to control the inlet to outlet temperature rise across the modules to 5° C (9° F) maximum. The air flow should be directed to flow across the modules.

All the individual module specifications are included in the detailed descriptions of the peripheral or option. A summary of the module characteristics is provided in Table 2; these characteristics are defined as follows:

- 1. The option designation is the alphanumerical code assigned to the option.

- 2. The module number is the number assigned to the interface modules that are connected to the LSI-11 bus. This number is printed on the module handle and can be used as a quick reference to determine what specific options are installed in any system. The module numbers are listed numerically in Table 3 so that the user can identify the options installed by using the module numbers.

- 3. The module description identifies the category of the option.

- 4. The power requirements specify the power by the option when connected to the bus backplane. These requirements are used to determine the total power supply loading within a single system.

- 5. The bus loads for ac and dc loading are provided so that the user can calculate the total ac and dc loading for any system.

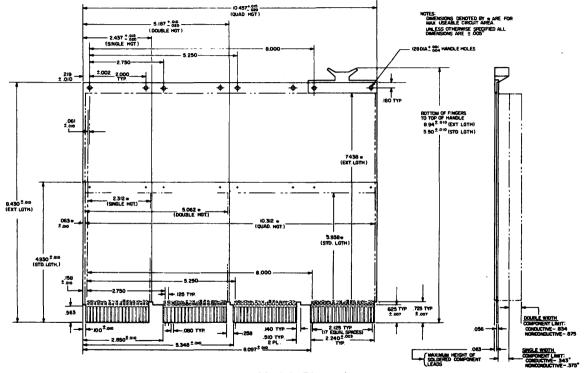

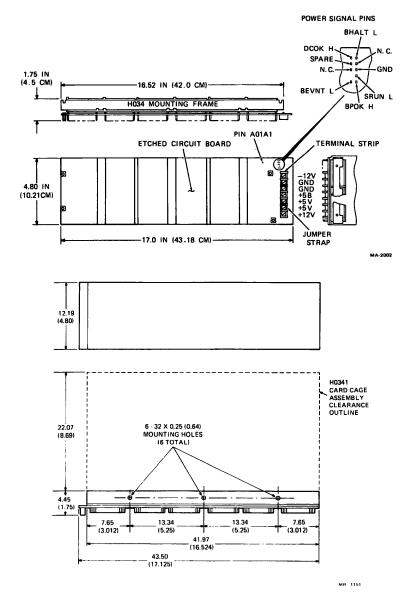

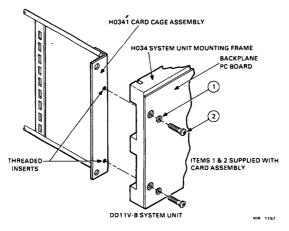

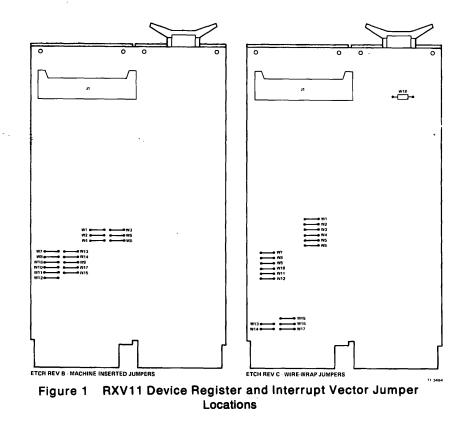

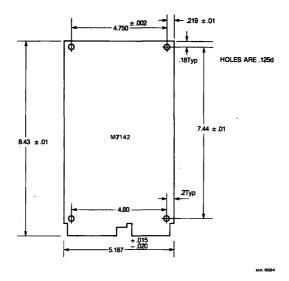

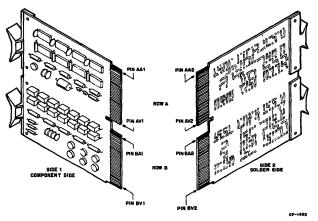

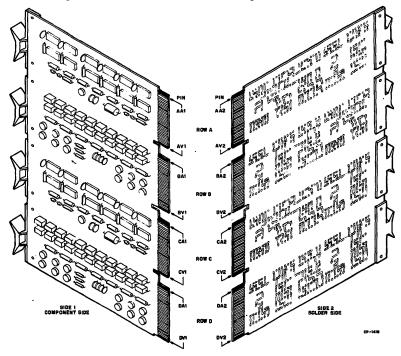

- 6. The interface modules are standarized as either a double or a quad and all are extended length. The double size module is 13.2 cm (5.2 in.) high, 22.8 cm (8.9 in.) long, and 1.27 cm (0.5 in.) wide. The quad size module is 26.5 cm (10.5 in.) high, 22.8 cm (8.9 in.) long, and 1.27 cm (0.5 in.) wide (Figure 1).

## **DESCRIPTION OF OPTION CATEGORIES**

The LSI-11 bus peripherals and options are classified into general categories that pertain to their performance and function. This listing indicates the wide span of equipment capability available to the user

## **Interface Options**

- AAV11-A The AAV11-A is a 4-channel, 12-bit digital-to-analog converter module that includes control and interfacing circuits. It has four D/A converters, a dc-dc converter that provides power to the analog circuits, and a precision voltage reference. Each channel has its own holding register that can be addressed separately and provides 12 bits of resolution. Bits 0, 1, 2, and 3 of the fourth holding register are brought out to the I/O connector so that they can be used as a 4bit digital output register.

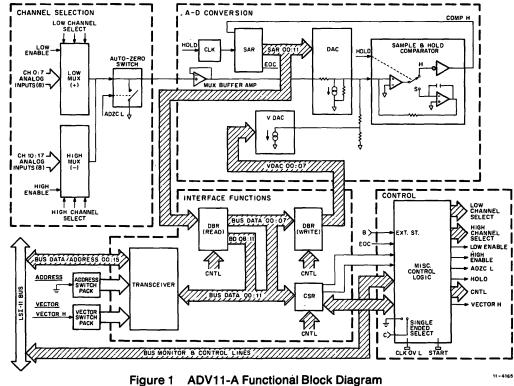

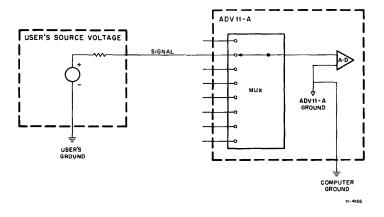

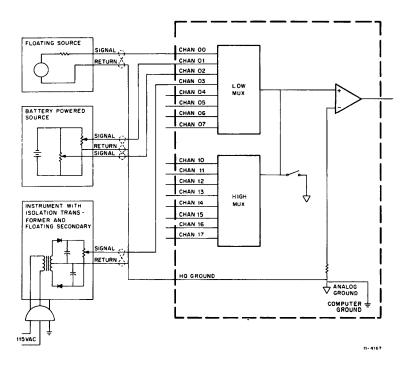

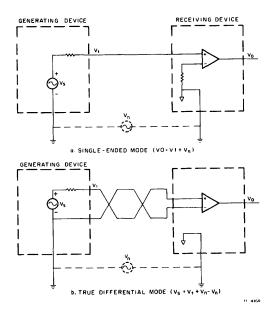

- ADV11-A The ADV11-A is a 12-bit successive approximation analog-to-digital converter that samples analog data at specified rates and stores the digital equivalent value for processing. The multiplexer can accommodate up to 16 single-ended or 8 quasi-differential inputs. The converter uses a patented auto-zeroing design that measures the sampled data with respect to its own offset and therefore cancels out its own offset error.

External event inputs can originate at the user's equipment or from the Schmitt trigger output of the KWV11-A clock. Three reference signals are provided for self-testing any channel input. These signals consist of two dc levels and one bipolar triangular waveform. This output can be used with DIGITAL diagnostic software to produce a data base for extremely precise analog linearity testing.

- DRV11 The DRV11 is a parallel interface module that is used to interconnect the LSI-11 bus with general-purpose, parallel line TTL or DTL devices. It allows programcontrolled data transfers at rates up to 40K words per second and uses LSI-11 bus interface and control logic to generate interrupts and process vector handling. The data are handled by 16 diodeclamped input lines and 16 latched output lines. There are two 40-pin connectors on the module for user interface applications.

- DRV11-B The DRV11-B is an interface module that uses direct memory access (DMA) to transfer data directly between the system memory and an I/O device. The interface is programmed by the processor to move variable length blocks of 8- or 16-bit data words to or from specified locations in the system memory. Once programmed, there is no processor intervention required. The module can transfer up to 250K 16-bit words per second in the single-cycle mode and up to 500K 16-bit words per second in the burst mode. It also allows read-modify-restore operations.

- DRV11-J Sixty-four input/output data lines are now available on a double-height module for the LSI-11/2, LSI-11/23, PDP-11/03, and PDP-11/23. The DRV11-J also includes an advanced interrupt structure with bit interruptability up to 16 lines, programmable interrupt vectors, and program selection of fixed or rotating interrupt priority within the DRV11-J. The DRV11-J's bit interrupts for real-time response make it especially useful for sensor I/O applications. It can also be used as a general-purpose interface to custom devices, and two DRV11-Js can be connected back-to-back as a link between two LSI-11 buses.

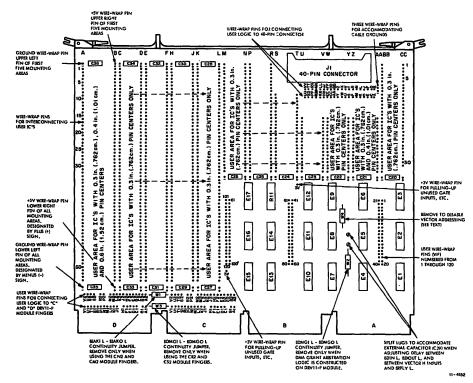

- DRV11-P The DRV11-P is a foundation wire-wrap interface module with a 40-pin I/O connector. Approximately 25 percent of the module is occupied by bus transceivers, interrupt vector generation logic, device comparator logic, protocol logic, and interrupt logic. The remaining 75 percent is for user applications; this portion has plated-through holes for securing

ICs and wire-wrap pins for interconnecting the user's curcuits. The plated-through holes can accept 6-, 8-, 14-, 18-, 20-, 22-, 24-, and 40-pin dual-in-line integrated circuits or discrete components.

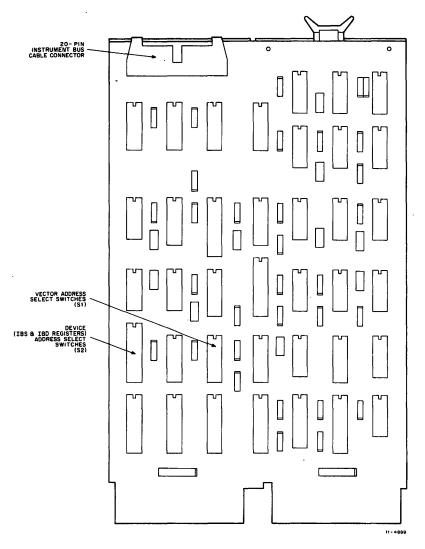

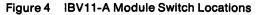

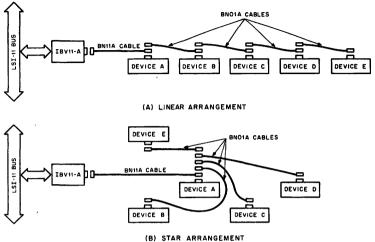

IBV11-A The IBV11-A is an interface module that interconnects the LSI-11 bus with the instrument bus described in IEEE standard 488 1975, "Digital Interface for Programmable Instrumentation." The IBV11-A makes a processor-controlled programmable instrument system possible. The module can accommodate up to 15 IEEE-488 devices and is PDP-11 software-compatible.

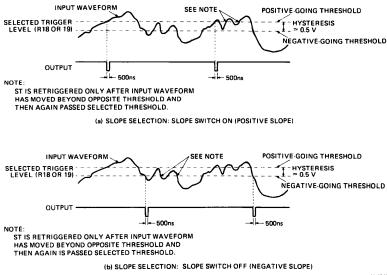

KWV11-A The KWV11-A is a programmable real-time clock/counter that provides a means of determining time intervals or counting events. It can be used to generate interrupts to the processor at predetermined intervals or establish timing between input and output events. It can also initialize the ADV11-A ç analog-to-digital converter by a clock counter overflow or by firing a Schmitt trigger. The clock counter has a resolution of 16 bits and can be driven by any one of five crystal-controlled frequencies (100 Hz to 1 MHz), from a line frequency input, or from a Schmitt trigger fired by an external input. The module can operate in any of four programmable modes: single interval, repeated interval, external event timing, and external event timing from zero base.

#### **Communications Options**

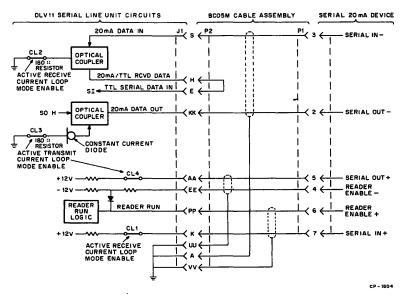

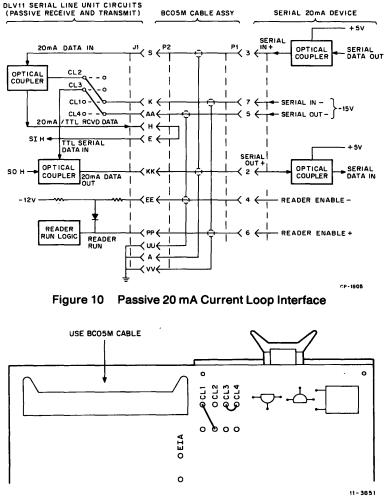

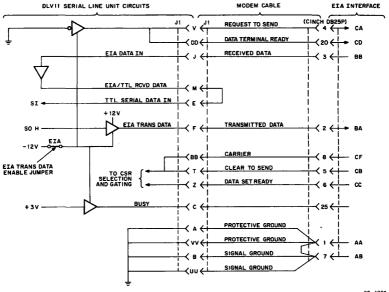

- DLV11 The DLV11 is a serial line unit (SLU) that interfaces with asynchronous serial I/O devices. The module has jumper-selectable baud rates (50-9600) and serial word format that includes the number of stop bits, number of data bits, and even, odd, or no parity bit. The DLV11 can support 20 mA current loop interfaces or EIA "data leads only" interfaces.

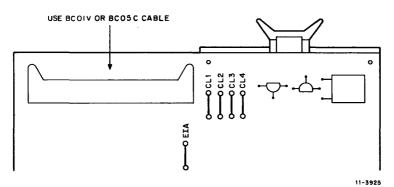

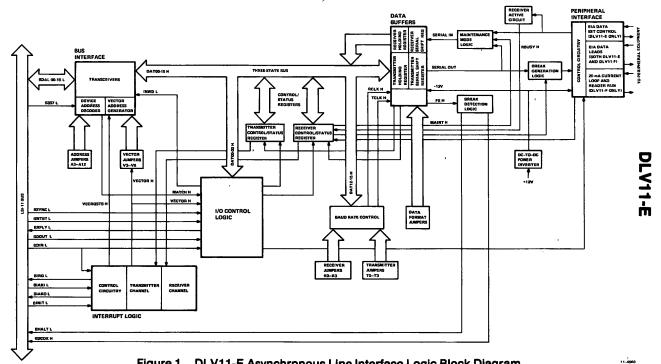

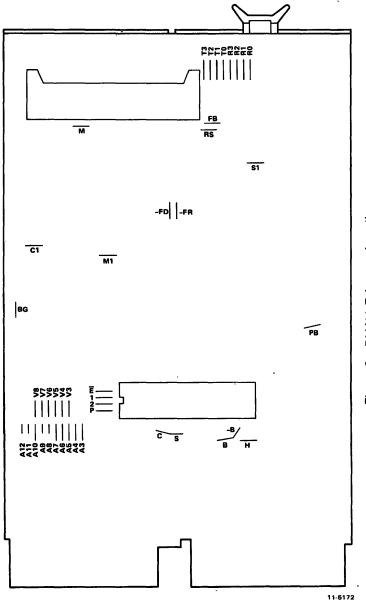

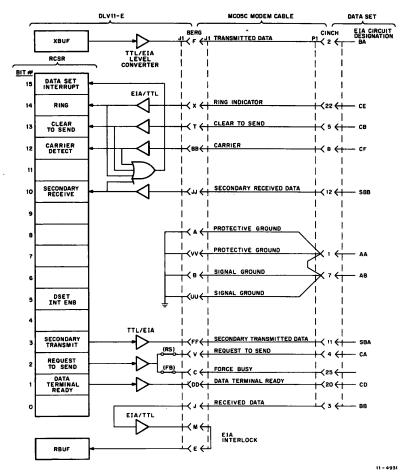

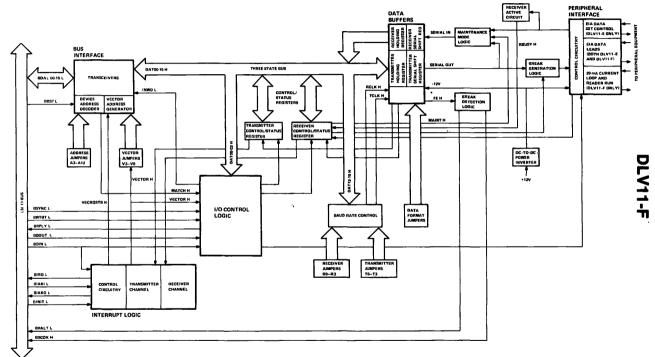

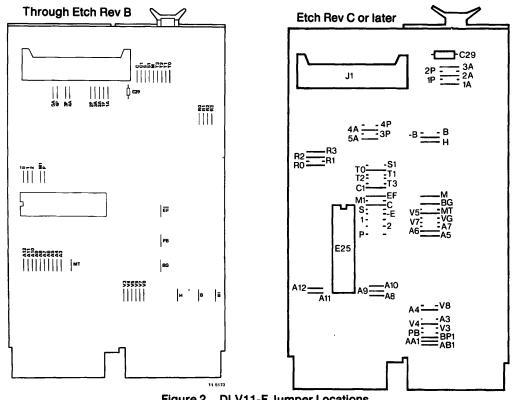

- DLV11-E The DLV11-E is an asynchronous line interface module that interconnects the LSI-11 bus to standard serial communications lines. The module receives serial data, converts it to parallel data, and

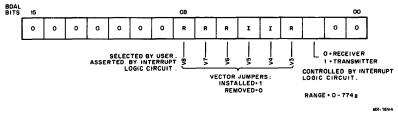

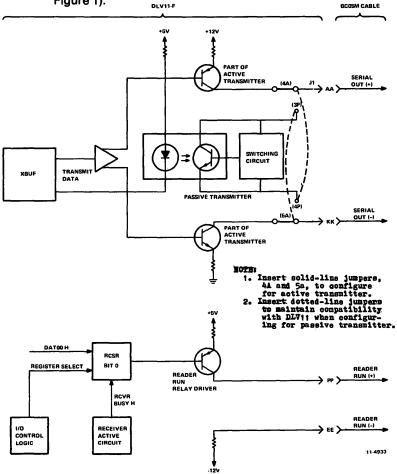

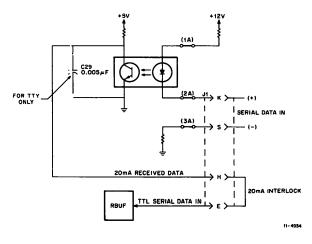

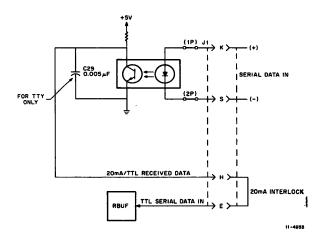

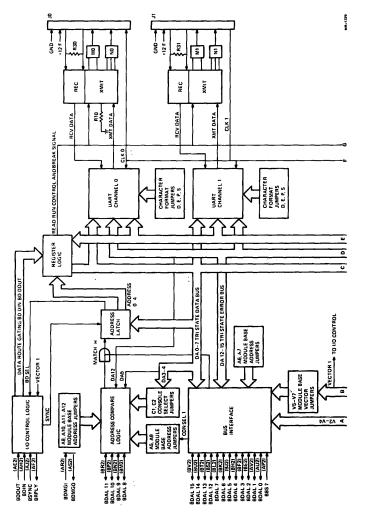

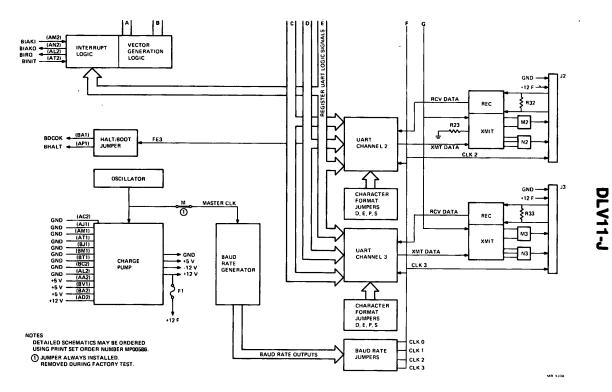

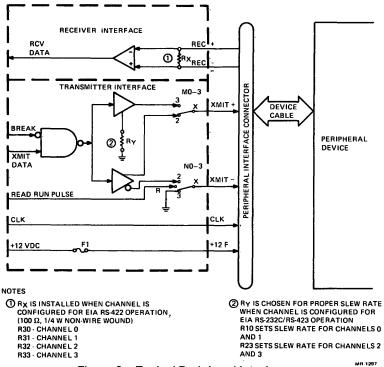

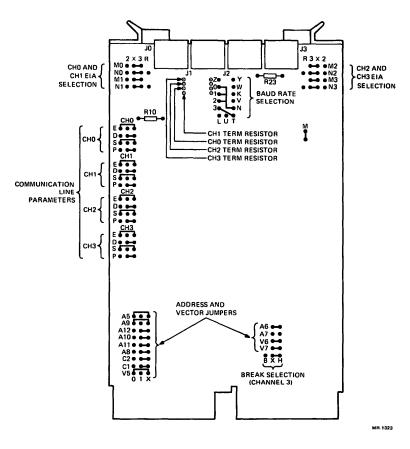

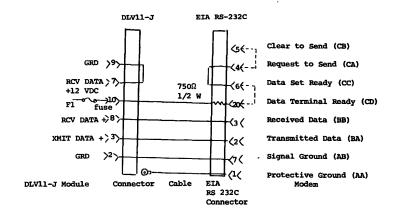

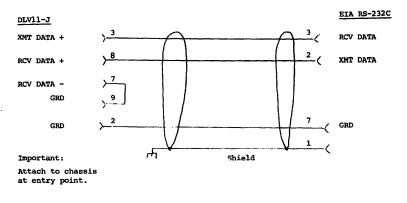

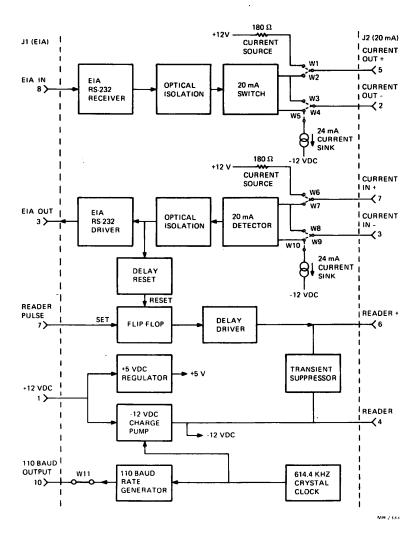

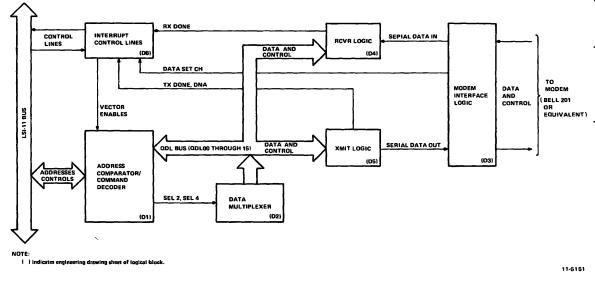

transfers it to the LSI-11 bus. Also, it accepts parallel data from the LSI-11 bus, converts it to serial data. and transmits it to the peripheral device. The module has jumper-selectable or software-selectable baud rates (50-19,200), and jumper-selectable data bit formats. The DI V11-E offers full modem control for EIA/CCITT interfaces. DLV11-F The DLV11-F is an asynchronous line interface module that interconnects the LSI-11 bus to several types of standard serial communications lines. The module receives serial data, converts it to parallel data. and transfers it to the LSI-11 bus. It also accepts parallel data from the LSI-11 bus, converts it to serial data, and transmits it to the peripheral device. The module has jumper-selectable or software-selectable baud rates (50-19,200) and jumper-selectable data bits. The DLV11-F supports either 20 mA current loop or EIA standard lines, but does not include modem control. DLV11-J The DLV11-J contains four independent asynchronous serial line channels used to interface peripheral devices to the LSI-11 bus. Each channel transmits and receives data from the peripheral device over EIA data leads (lines that do not use a control line). The module can be used with 20 mA current loop devices if a DLV11-KA adapter is used. The DLV11-J has jumper-selectable baud rates from 150 to 39.4 K baud. **DUV11** The DUV11 synchronous line interface module establishes a data communication line between the LSI-11 bus and a Bell 201 synchronous modem or equivalent. The module is fully programmable with respect to sync characters, character length (to to 8 bits), and parity selection. The receiver logic accepts serial data for the LSI-11 bus. The transmitter logic converts the parallel LSI-11 bus data into serial data for the transmission line. The interface logic converts the TTL logic levels to the EIA voltage levels required by the Bell 201 modems and also controls the modem for half-duplex or full-duplex operation.

DZV11 The DZV11 is an asynchronous multiplexer interface module that interconnects the LSI-11 bus with up to four asynchronous serial data communications channels. The module provides EIA interface voltage levels and data set control to permit dial-up (autoanswer) options with full-duplex modems such as Bell models 103, 113, 212, or equivalent. The DZV11 does not support half-duplex operations or the secondary transmit and receive operations available in some modems such as Bell 202. The DZV11 has applications in data concentration and collection systems where front-end systems interface to a host computer and for use in a cluster controller for terminal applications.

# Expansion Memories (For detailed memory descriptions, see the Microcomputer Processor Handbook)

**MMV11-A** The MMV11-A is a  $4K \times 16$ -bit core memory option that provides nonvolatile read/write storage. The memory can be configured by bank addressing switches. The module is limited to LSI-11 bus backplanes that contain the LSI-11 bus in both the A/B bus and the C/D slots. MRV11-AA The MRV11-AA is a read-only memory module on which the user can install fusible link, programmable, read-only memory (PROM) chips or masked read-only memory (ROM) chips. The user selects the address space of the memory by configuring removable jumper wires. MRV11-BA The MRV11-BA is a read-only memory module that uses ultraviolet (UV) erasable, programmable, readonly memory (EPROM) integrated circuits. The module also contains a  $256 \times 16$ -bit random access memory (RAM) that can be used as a "scratchpad" or "stack" by the system software. MRV11-C The MRV11-C is a flexible, high-density ROM module used with the LSI-11 bus. The module contains sixteen 24-pin sockets which accept a variety of user-supplied ROM chips. It will accept masked

ROMS, fusible link PROMs, and ultraviolet erasable

PROMs. It accepts several densities of ROM chips up to and including  $4K \times 8$  chips. Using these highdensity chips gives the module a total capacity of 64K bytes. The contents of the module can be accessed in one of two ways—either directly or window-mapped. Direct access provides total random access to all ROM locations on the module. Windowmapping provides two 2K-byte windows in memory address space to access 2K-byte segments of the ROM array. The segments that are viewed through each window can be varied under program control.

- MSV11-B The MSV11-B is a 4K × 16-bit dynamic MOS read/write memory module. The user can select the memory addresses of the module by configuring removable jumpers. The memory refresh must be controlled by external bus signals.

- MSV11-CD The MSV11-CD is a 16K × 16-bit dynamic MOS read/write memory module. Refresh is automatically performed by the module but it can be disabled if the user wishes to use the LSI-11 bus refresh signals. This memory module can be configured to operate in the battery backup mode. The user can configure the memory addresses by selecting switch settings.

MSV11-D,-E The MSV11-D module has either 8K, 16K, or 32K × 16 bits of MOS memory. The MSV11-E is the same as the MSV11-D except that it has an 18-bit word that generates and detects byte parity for each word. The modules have an on-board memory refresh and perform the necessary LSI-11 bus cycles. The memory addressing is selectable by the user by configuring switch settings. The module can use a battery backup system to preserve data when primary power is lost.

MXV11-A The MXV11-A is a dual height multifunction option module for the LSI-11, LSI-11/2 or LSI-11/23. It contains a read/write memory, provisions for read-only memory, two asynchronous serial line interfaces and a 60 Hz clock signal derived from a crystal oscillator. Read/write memory is supplied with either 8K or 32K bytes (4K or 16K words). Two 24-pin sockets are

provided for +5 V read-only memories. 1K  $\times$  8. 2K  $\times$ 8. or 4K × 8 ROMS may be used. The sockets may also be used for 256 words of bootstrap code. The two asynchronous serial lines transmit and receive EIA-423 signal levels from 150 baud to 38.4K baud. 20 mA active or passive current loop operation at 110 baud may be obtained with the DLV11-KA EIA to 20 mA converter option. The serial lines will not support the reader run function of the DLV11-KA option. The serial lines provide error indicator bits for overrun error, frame error, and parity error, but do not have modem controls. Serial line 1 may be configured to respond to a break signal. The serial lines have signal level interrupt logic and should be placed after multi-level devices on an LSI-11/23 system. Serial line 1 may be used as a console port, or, along with serial line 0, may be used with any of several standard types of serial communication devices. The 60 Hz clock signal can be selected by a wirewrap jumper to provide line-time clock interrupts on the bus.

## Peripherals

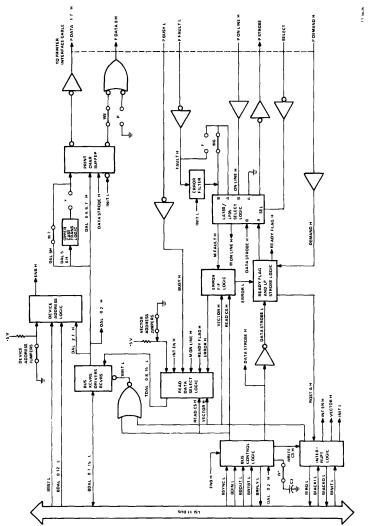

LAV11 The LAV11 option consists of an LA180 DECprinter, an interface module, and a BC11S-25 interface cable. The interface module provides interconnection between the LA180 DECprinter and the LSI-11 bus. The module outputs ASCII characters to the printer and monitors various printer operations that require operator control.

LPV11 The LPV11 printer option consists of an interface module, an interface cable, and either an LP05 or LA180 line printer. The interface module provides programmed control of data transfers and provides printer strobe signals appropriate for either printer. The LA180 DECprinter is a high-speed printer that prints 180 characters per second and the LP05 printer can print 240 or 300 lines per minute, depending on which model is selected.

| RKV11-D | The RKV11-D option consists of an RK05 disk drive<br>controller, an LSI-11 bus interface module, and an<br>RK05J disk drive. The RK05 disk drive controller can<br>be used with up to eight RK05J disk drive units to<br>form a mass memory storage system that contains<br>up to 21M bytes of storage. The RKV11-D system is<br>block-oriented but is capable of transferring from 1<br>to 2 <sup>16</sup> consecutive data words without reinitiation or<br>processor intervention. The data transfers occur<br>from the RKV11-D to the system memory by direct<br>memory access (DMA) and operate at maximum bus<br>bandwidth. The system can use either RK05J or<br>RK05F disk drives and the controller can be mount-<br>ed in a standard 48.3 cm (19 in.) cabinet.                  |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

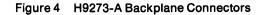

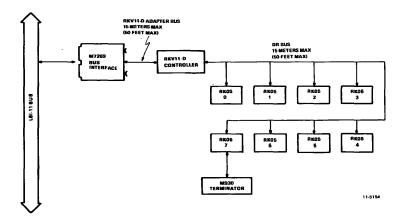

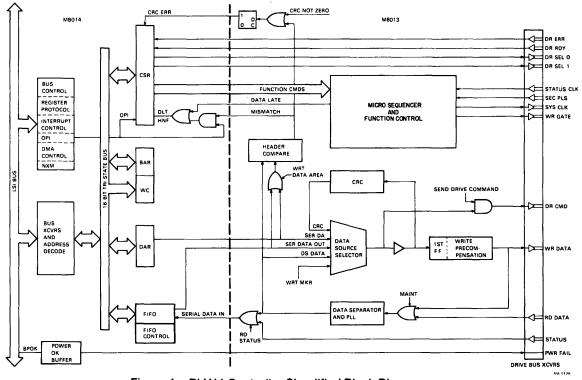

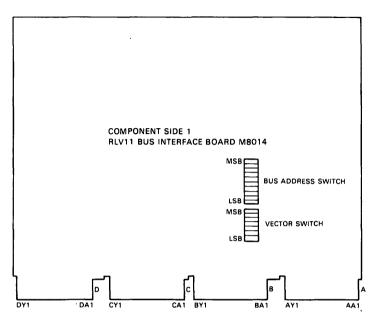

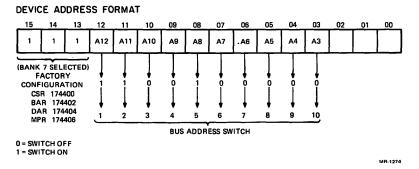

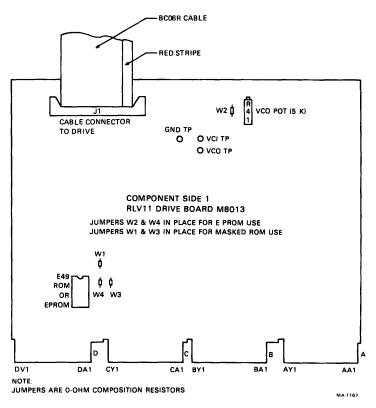

| RLV11   | The RLV11 option interfaces the LSI-11 bus with an RL01 disk drive controller and an RL01 disk drive assembly. The controller can only be used in an H9273-A type backplane which incorporates an LSI-11 bus in slots A and B, with an interboard bus in slots C and D. The controller can interface up to four RL01 disk drives for a complete system of 21M bytes of storage. The RL01 disk drive is a random access, mass storage system that stores data in fixed length blocks on a preformatted disk cartridge. Each drive can store up to 5.24 million bytes and the complete system can store up to 21 million bytes. The RLV11 transfers data using direct memory access (DMA) techniques; this allows data transfers without processor intervention and at bus bandwidth speed. |

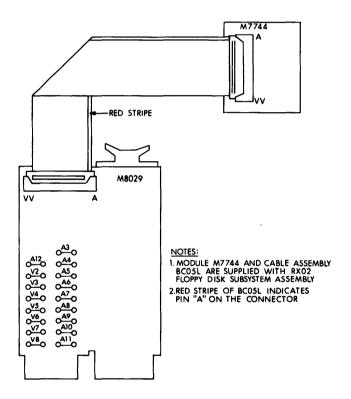

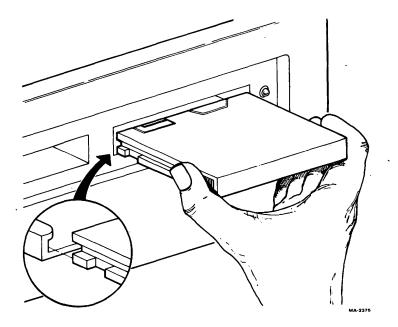

| RXV11   | The RXV11 option consists of an interface module,<br>cable assembly, and either a single or dual drive<br>RX01 floppy disk. This option is a random access<br>mass storage device that stores data in fixed-length<br>blocks on a preformatted flexible diskette. Each<br>diskette can store and retrieve up to 256K, 8-bit<br>bytes of data. The RXV11 system is rack mountable<br>in the standard 48.3 cm (19 in.) cabinet.                                                                                                                                                                                                                                                                                                                                                             |

| RXV21   | The RXV21 floppy disk option is a random access<br>mass memory device that stores data in fixed-length<br>blocks on a preformatted, flexible diskette. Each                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

diskette can store and retrieve up to 512K 8-bit bytes of data. The RXV21 system is rack-mountable and consists of an interface module, an interface cable, and either a single or dual RX02 floppy disk drive. The interface module converts the RX02 I/O bus to the LSI-11 bus structure. It controls the RX02 interrupts to the processor, decodes device addresses for register selection, and handles the data interchange between the RX02 and the processor via DMA transfers. Power for the interface module is supplied by the LSI-11 bus.

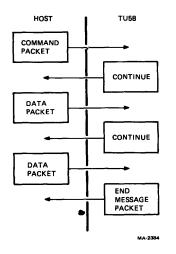

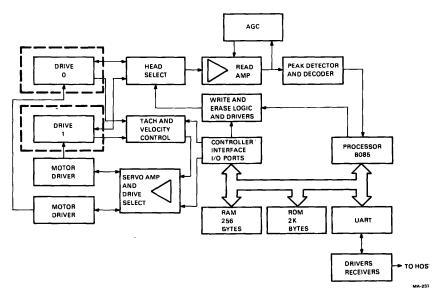

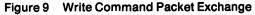

The TU58 is a low-cost intelligent mass memory device that offers random access to block-formatted data on pocket-size cartridge media. It is ideal as a small computer systems device, as inexpensive archive mass storage, or as a software update distribution medium. A dual drive TU58 offers 512 Kb of storage space, making it one of the lowest cost complete mass storage subsystems available. For mounting flexibility, the TU58 is offered both as a component level subsystem and as a fully powered 51/2" rack-mount subsystem.

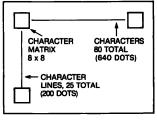

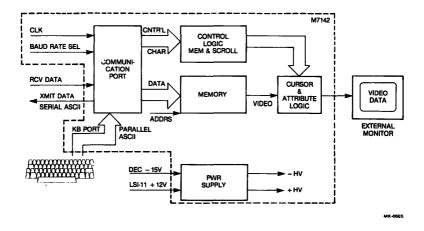

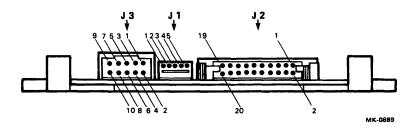

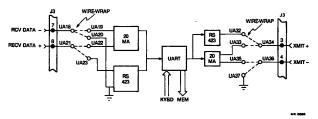

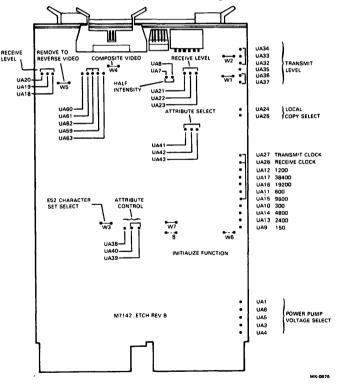

VK170-CA The VK170 module forms an integral part of a terminal. The module accepts serial ASCII encoded data to be stored in a refresh memory to generate a display for a video monitor. The VK170 also accepts parallel data from a keyboard (on strobe demand) to generate serial ASCII output. The VK170 is an extended-length, double-height, single-width board. Mounting holes are provided for stand-off mounting via handle rivets and two holes located near the module fingers.

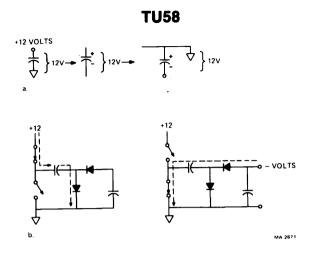

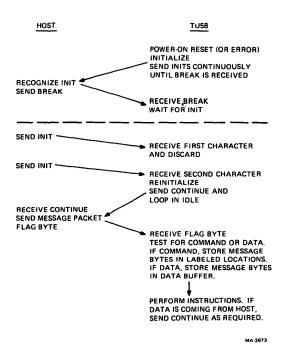

**TU58**

## Backplanes

The four backplane options available for the LSI-11 bus are presented in the following paragraphs.

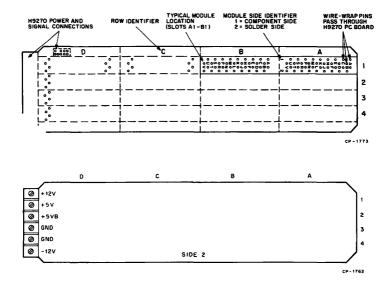

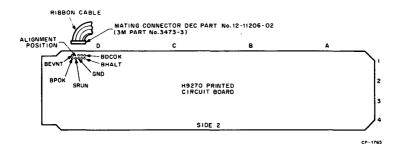

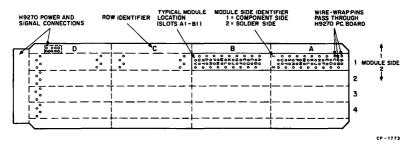

| H9270   | A 4 $\times$ 4 (four rows of four slots each) backplane with<br>card guide assembly. LSI-11 bus in rows A-B and C-<br>D. Accepts 8 double-height modules or 4 quad-<br>height modules or combinations of both.                    |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

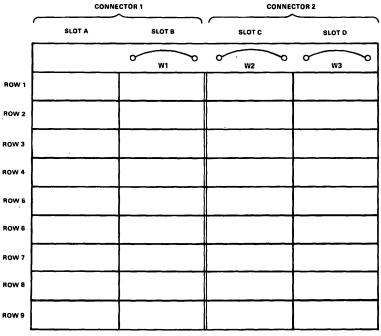

| H9273-A | A 9 $\times$ 4 (nine rows of four slots each) backplane with<br>card guide assembly. LSI-11 bus in rows A-B only.<br>Special interconnect bus in rows C-D.A ccepts dou-<br>ble-height or quad-height modules.                     |

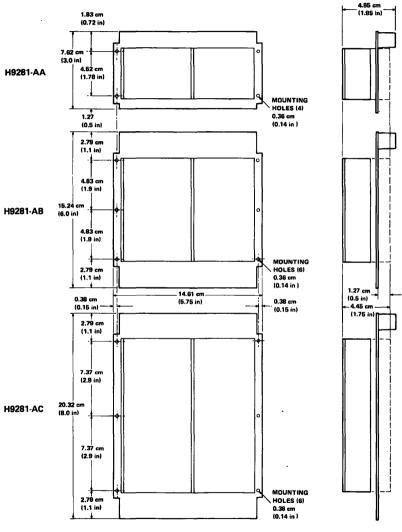

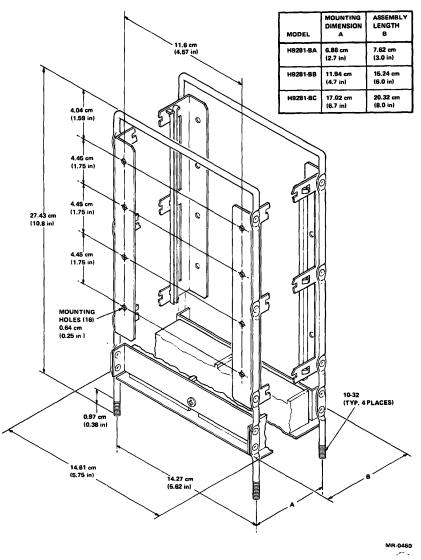

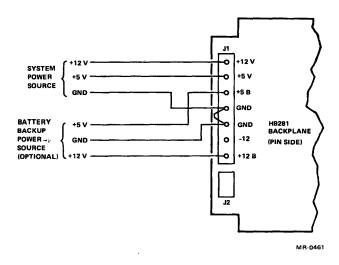

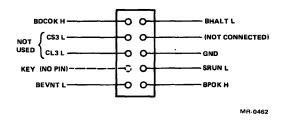

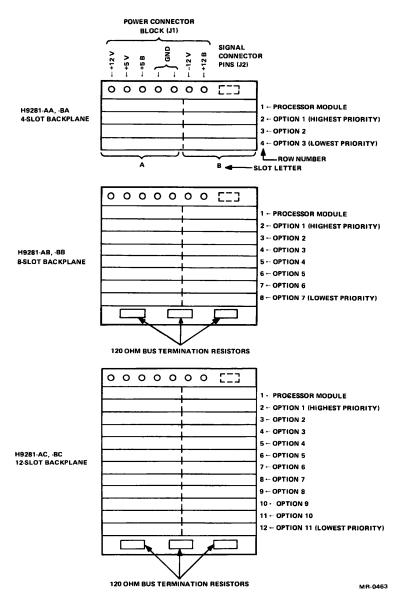

| H9281   | A 2-slot backplane available in 4-, 8-, or 12-slot op-<br>tions. Accepts double-height modules only.                                                                                                                              |

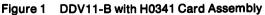

| DDV11-B | A 9 $\times$ 6 (nine rows of six slots each) backplane. LSI-<br>11 bus in rows A-B and C-D. Rows E-F are unbussed<br>except for +5V and ground. Accepts 18 double-<br>height or 9 quad-height modules or combinations of<br>both. |

## Enclosures

| H909-C | $\hat{A}$ 13.3 cm (5.25 in.) high, 48.3 cm (19 in.) wide enclo-<br>sure which can be mounted in a 48.3 cm (19 in.) rack<br>or as a stand-alone. Accommodates the DDV11-B<br>backplane or a 9 $\times$ 6 system mounting unit or<br>houses non-standard mounting arrangement. In-<br>cludes cooling fan, cord guide, cable restraints, front<br>bezel, and connector block. |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

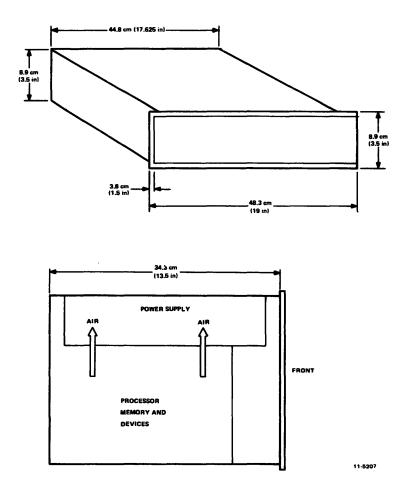

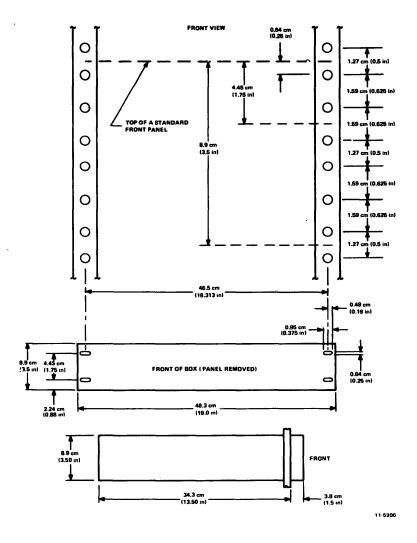

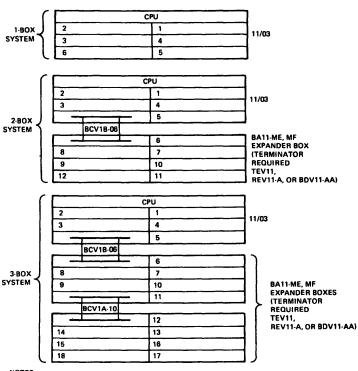

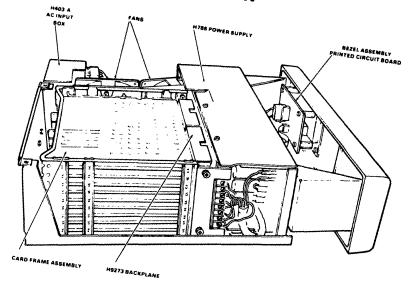

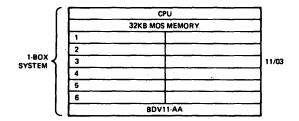

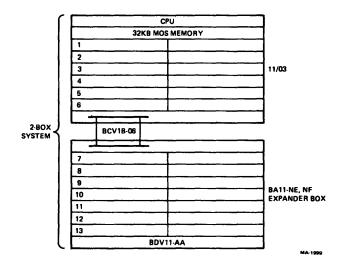

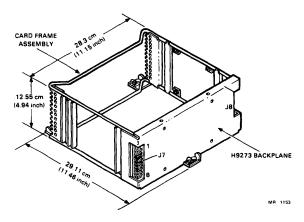

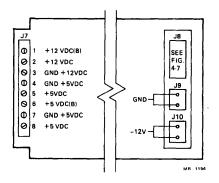

| BA11-M | A 8.9 cm (3.5 in.) high , 48.3 cm (19 in.) wide expan-<br>sion box which can be mounted in 48.3 cm (19 in.)<br>rack. Includes H9270 backplane, H780 power sup-<br>ply, blank front panel or bezel, and cooling fan.                                                                                                                                                        |

| BA11-N | A 13.2 cm (5.19 in.) high, 48.3 cm (19 in.) wide<br>mounting box which can be mounted in a 48.3 cm<br>(19 in.) rack. Includes H9273-A backplane, H786<br>power supply, H403-A ac input panel, blank front<br>panel or bezel, and cooling fan.                                                                                                                              |

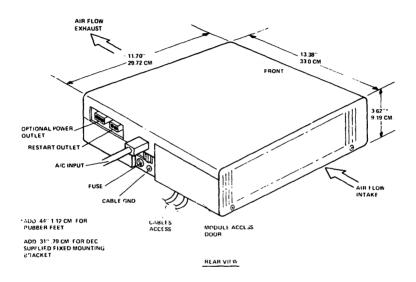

BA11-VA The BA11-VA is a small form-factor package providing mounting space and power for four LSI-11/2 or LSI-11/23 family modules. This package, plus the high functionality of DIGITAL's microcomputer products, allows LSI-11 microcomputer applications to be implemented within a space smaller than that required for many 8-bit systems.

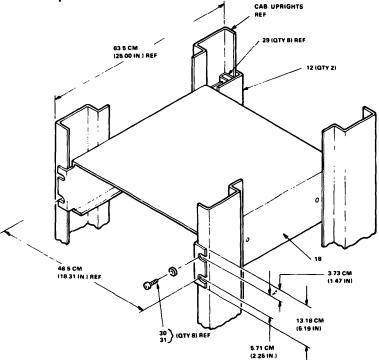

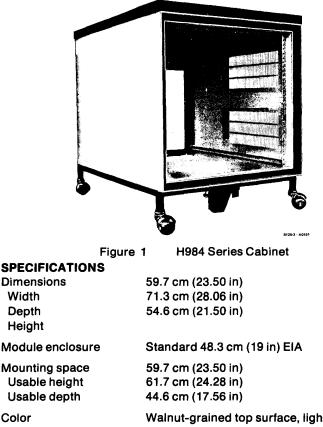

#### Cabinets

- H984-B A low-profile cabinet with four casters. Provides mounting space for standard 48.3 cm (19 in.) panels and enclosures in rack at front or rear. Includes distribution panel (115 Vac, 230 Vac)

- H9800-A A low-profile system desk with casters. Provides mounting space for standard 48.3 cm (19 in.) panels and enclosures. Includes distribution panel (115 Vac, 230 Vac)

#### **Power Supplies**

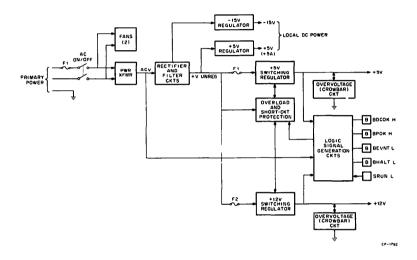

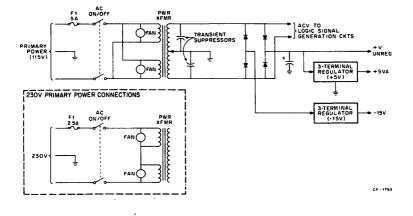

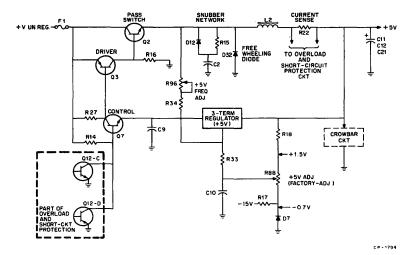

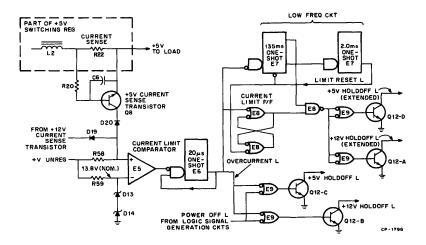

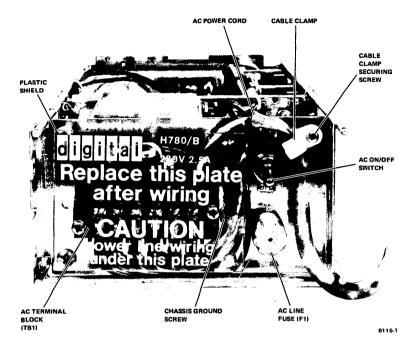

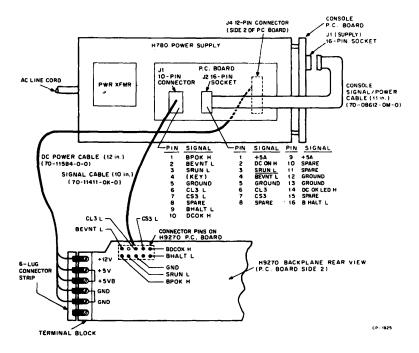

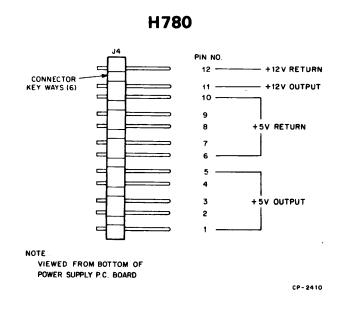

H780

Provides  $+5V \pm 4\%$ , 18 A (max) and  $+12V \pm 3\%$ , 3.5 A (max) at 110 Vac and features line-time clock, and power-fail/automatic restart. Available primary power of 115 or 230 Vac and with or without master and slave console.

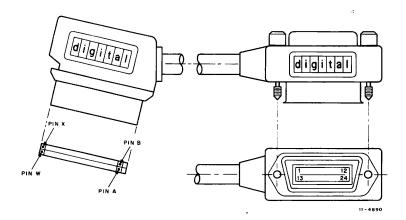

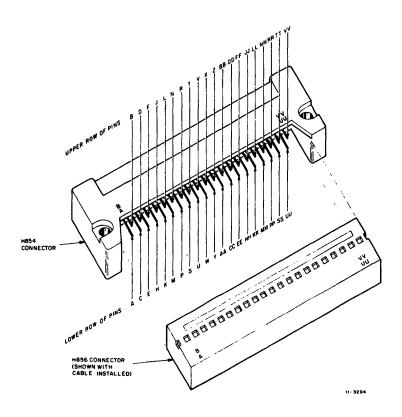

#### **Cables and Connectors**

Various preassembled cables in different lengths are available for use with interface and communications options. See Appendix C for commonly used cables.

#### Wire-Wrappable Modules

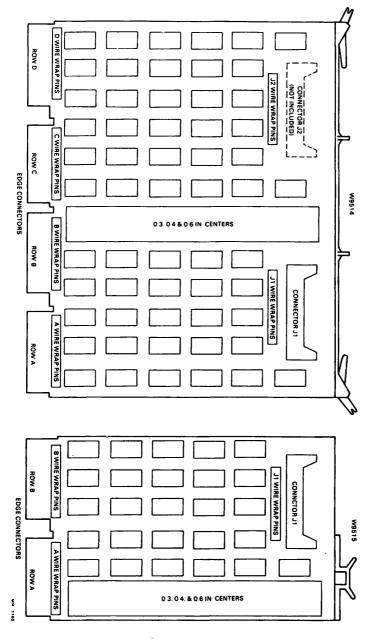

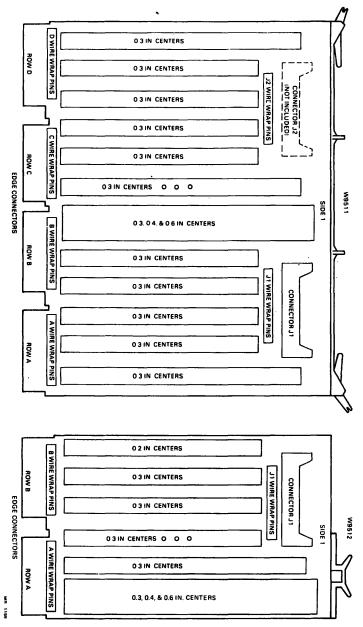

**W9500 Series: LSI-11 Bus-Compatible Wire-Wrappable Modules** (W9511, W9512, W9514 AND W9515) — The LSI-11 bus-compatible wire-wrappable modules consist of quad-height and double-height modules. Two LSI-11 bus-compatible modules are available without DIP sockets.

W9511

Quad-height, extended-length, single-width module with extractor handle. No DIP sockets included. One 40-pin male cable connector premounted on board and space for additional 40-pin connector provided.

|       | Power and ground connections are<br>V—AA2, BA2, CA2, DA2<br>GND—AT1, BT1, CT1, DT1, AC2, BC2, CC2,<br>DC2                                                      |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| W9514 | Same as W9511 except with 58 pre-mount-<br>ed DIP sockets.                                                                                                     |

|       | Power and ground connections are the same as W9511                                                                                                             |

| W9512 | Double-height, extended-length, single-<br>width module with Flip-Chip handle. No DIP<br>sockets included. One 40-pin male connec-<br>tor premounted on board. |

|       | Power and ground connections are<br>GND—AT1, BT1,AC2, BC2                                                                                                      |

| W9515 | Same as W9512 except with 25 pre-mount-<br>ed DIP sockets.                                                                                                     |

|       | Power and ground connections are the<br>same as W9512                                                                                                          |

## **Integrated Circuits**

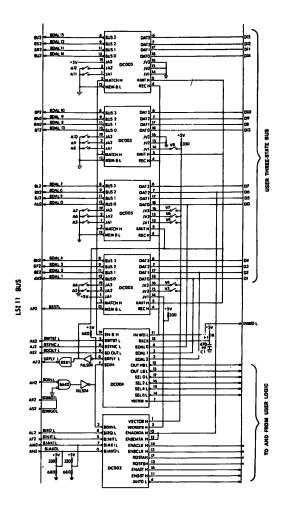

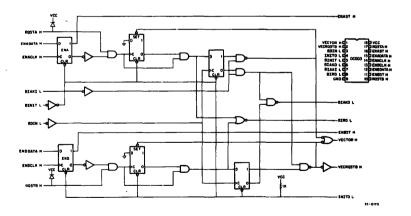

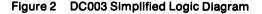

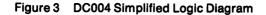

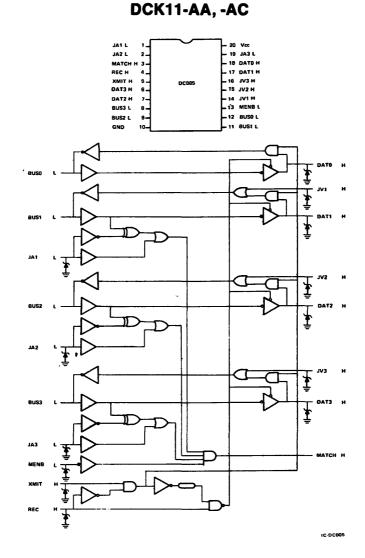

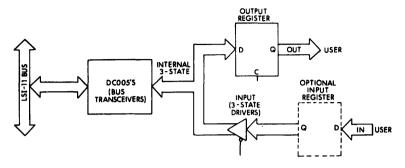

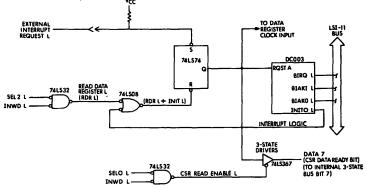

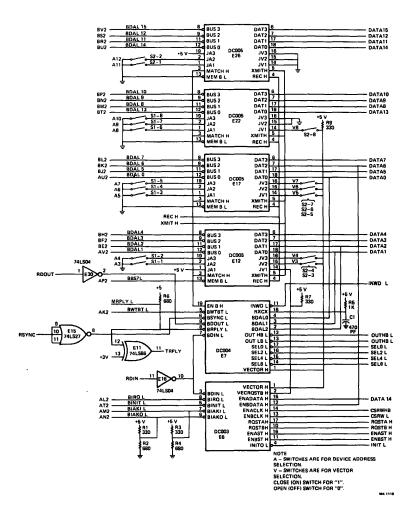

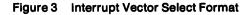

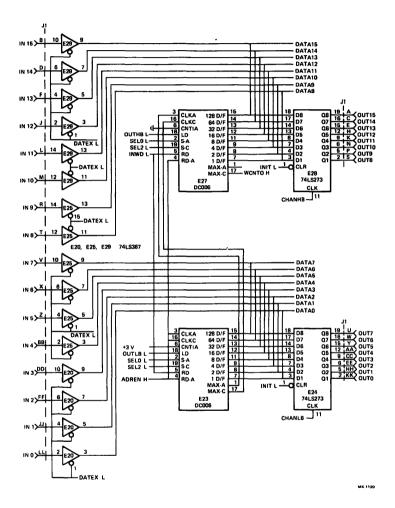

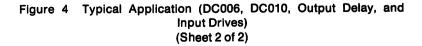

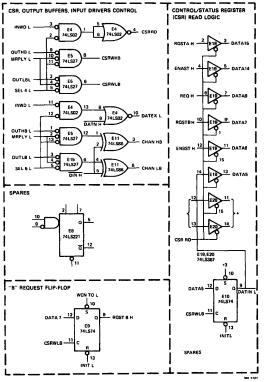

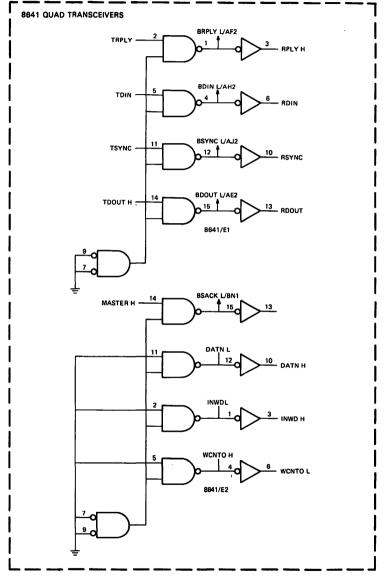

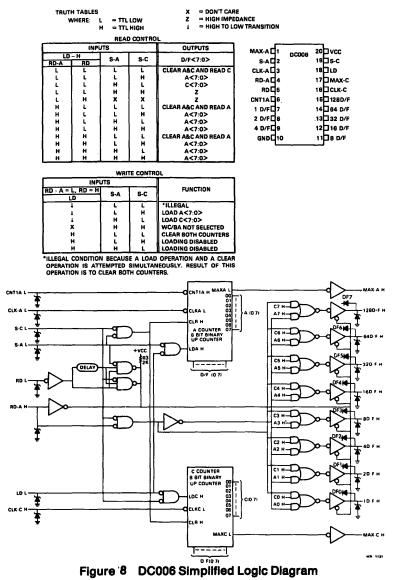

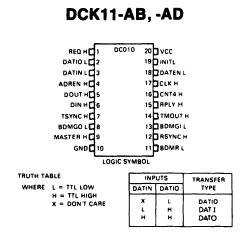

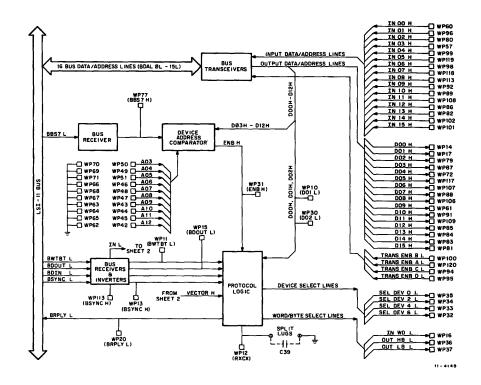

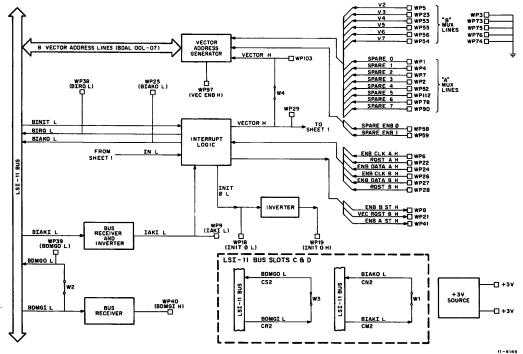

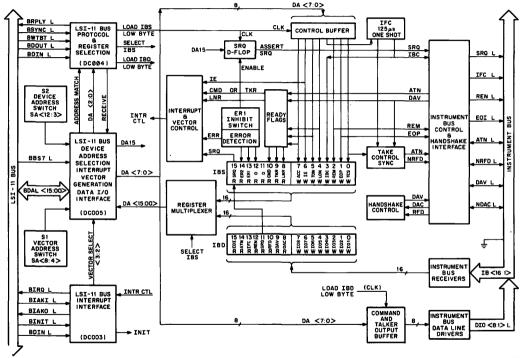

| DCK11-AA, -<br>AC | The DCK11-AA and -AC CHIPKITs provide the logic<br>necessary for a program transfer interface to the<br>LSI-11 bus. The DCK11-AA kit contains one DC003<br>Interrupt Chip, one DC004 Protocol Chip, and four<br>DC005 Transceiver/Address Decoder/Vector Select<br>Chips. The DCK11-AC kit contains previous chips<br>plus one W9512 double-height, extended length,<br>high-density wire-wrappable module and one<br>BC07D-10 ten-foot, 40-connector plug-in cable.                                            |

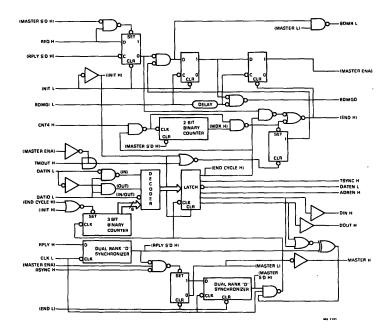

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DCK11-AB, -<br>AD | The DCK11-AB and -AD CHIPKITs provide the logic<br>necessary for a Direct Memory Access (DMA) inter-<br>face to the LSI-11 bus. The DCK11-AB. The DCK11-<br>AB kit contains one DC003 Interrupt Chip, one<br>DC004 Protocol Chip, four DC005 Transceiv-<br>er/Address Decoder/Vector Select Chips, two<br>DC006 Word Count/Bus Address Chips, and one<br>DC010 DMA Control Chip. The DCK11-AD kit con-<br>tains the previous chips plus one W9512 double-<br>height, extended-length, high-density wire-wrappa- |

ble module and one BC07D-10 ten-foot, 40-connector plug-in cable. DMA applications use the same chips as program control interfaces, plus two DC006s for word or byte address counters and a DC010 DMA bus control IC.

#### **Miscellaneous Options**

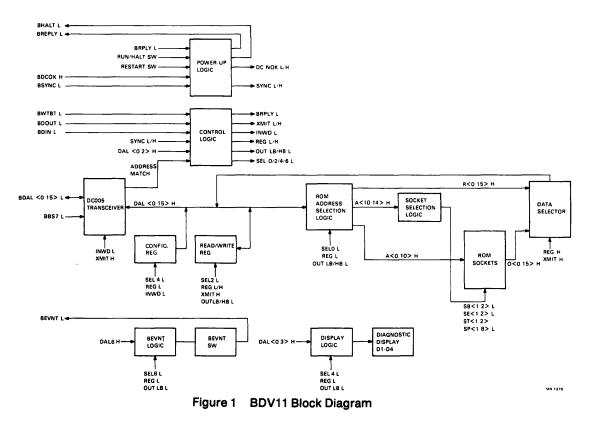

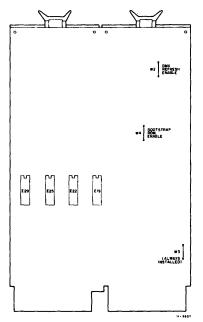

BDV11

The BDV11 module has 2K words of read-only memory (ROM) that contains diagnostic and bootstrap programs. These programs are user-selectable by setting dip switches. The diagnostic programs will test the processor, the memory, and the user's console. The bootstrap programs can boot most LSI-11 peripheral devices. The module also has 120-ohm bus terminator circuits.

The user can add up to 16K of read-only memory (ROM) and up to 2K words of erasable programmable ROM (EPROM) on the module. This 18K words of additional memory can be used with no increase in the amount of I/O address space.

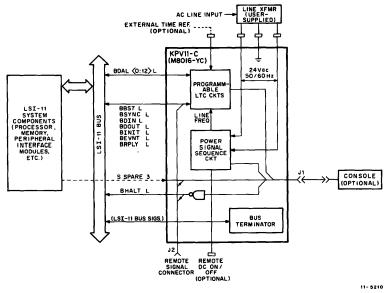

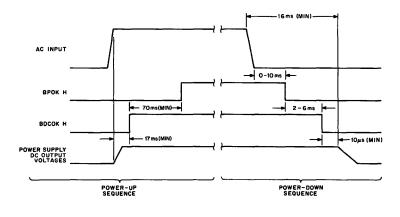

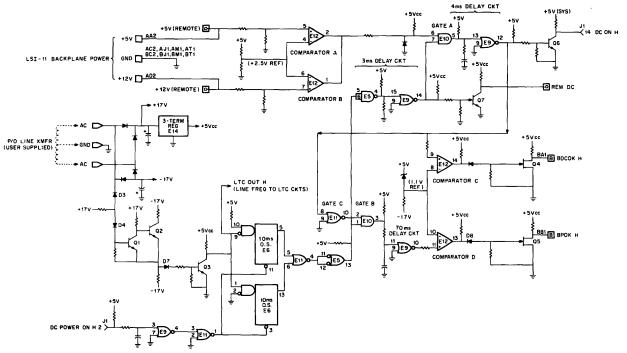

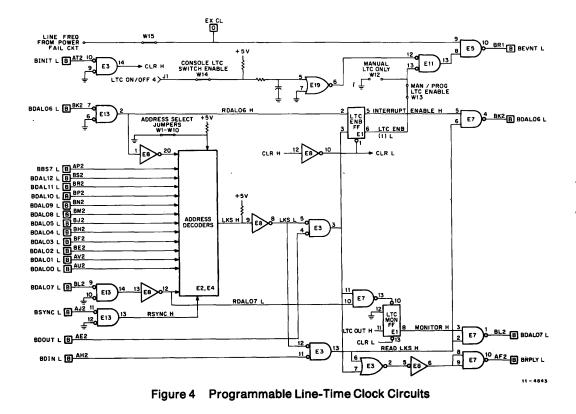

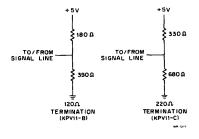

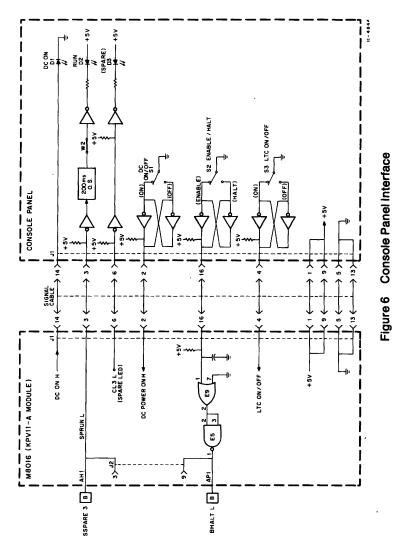

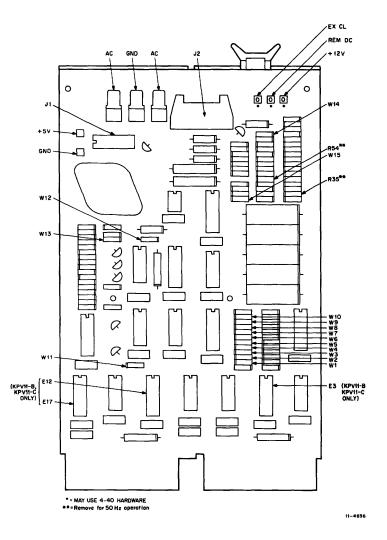

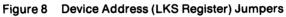

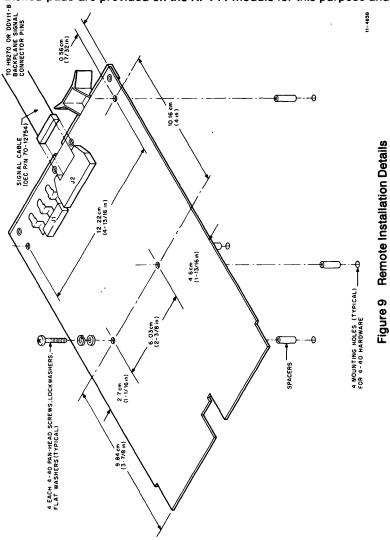

- KPV11-A, -B, The KPV11-A module generates power-up and power-down sequences, monitors for a power-fail condition, and generates the line-time clock (LTC) function. The KPV11-B is the same as the "A" except that it provides 120-ohm termination circuits. The KPV11-C is the same as the "A" except that it provides 220-ohm termination circuits. The module can be installed on any backplane or remotely installed via an optional cable.

- REV11-A, -C The REV11-C module has a bootstrap ROM and direct memory access (DMA) refresh circuits. The refresh REV11-A is identical to the REV11-C except it has additional 120-ohm termination circuits.

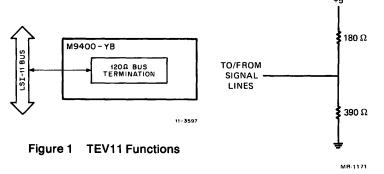

- TEV11 The TEV11 is a bus terminator module that provides ` 120-ohm bus termination circuits.

| Option  | Module |                                         | Power Re | quirements | Bus Loads | *  |        |             |

|---------|--------|-----------------------------------------|----------|------------|-----------|----|--------|-------------|

| Desig.  | No(s). | Description                             | + 5V     | + 12V      |           | 50 | Clas   |             |

|         |        |                                         | ±5%      | ±3%        | AC(Max)   | DC | Size   |             |

| AAV11-A | A6001  | 4-channel, 12-bit<br>D/A converter      | 1.5 A    | 0.4 A      | 1.9       | 1  | Quad   |             |

| ADV11-A | A012   | 16-channel, 12-bit<br>A/D converter     | 2.0 A    | 0.45 A     | 3.25      | 1  | Quad   | =           |

| BDV11   | M8012  | Bootstrap,<br>terminator,<br>diagnostic | 1.6 A    | 0.07 A     | 2.0       | 1  | Quad   | NTRODUCTION |

| DDV11-B |        | 6 	imes 9 backplane                     |          |            | 6.4       | 0  |        | č           |

| DLV11   | M7940  | Asynchronous serial<br>line interface   | 1.0 A    | 0.18 A     | 2.5       | 1  | Double | CTI         |

| DLV11-E | M8017  | Asynchronous line<br>interface          | 1.0 A    | 0.18 A     | 1.6       | 1  | Double | ON<br>N     |

| DLV11-F | M8028  | Asynchronous line<br>interface          | 1.0 A    | 0.18A      | 2.2       | 1  | Double |             |

| DLV11-J | M8043  | 4 asynchronous<br>serial interfaces     | 1.0 A    | 0.25 A     | 1         | 1  | Double |             |

| Option        | Module |                                   | Power Requi           |              | Bus Loads | *  |        |             |

|---------------|--------|-----------------------------------|-----------------------|--------------|-----------|----|--------|-------------|

| Desig. No(s). | No(s). | Description                       | + 5V<br>±5%           | + 12V<br>±3% | AC(Max)   | DC | Size   |             |

| DRV11         | M7941  | Parallel line unit interface      | 0.9 A                 | -            | 1.4       | 1  | Double |             |

| DRV11-B       | M7950  | DMA interface                     | 1.9 A                 | -            | 3.3       | 1  | Quad   | Z           |

| DRV11-J       | M8049  | 64-line parallel I/O              | 1.6A                  | 1.8A         | 2.0       | 1  | Double | 3           |

| DRV11-P       | M7948  | Foundation module                 | 1.0 A<br>+ user logic | -            | 2.1       | 1  | Quad   | NTRODUCTION |

| DUV11         | M7951  | Synchronous serial line interface | 0.86 A                | 0.32         | 1.00      | 1  | Quad   | CTI         |

| DZV11         | M7957  | Asynchronous<br>line interface    | 1.15 A                | 0.39 A       | 3.95      | 1  | Quad   | 0<br>Z      |

| H9270         |        | 4 	imes 4 backplane               |                       |              | 5.1       | 0  |        |             |

| H9273         |        | 4 	imes 9 backplane               |                       |              | 2.6       | 0  | •      |             |

| H9281A        |        | $2 \times 4$ backplane            |                       |              | 1.3       | 0  |        |             |

| H9281B        |        | $2 \times 8$ backplane            |                       |              | 2.4       | 0  |        |             |

## Table 1 Module Specifications

| Table 1 Module Specifi | cations |

|------------------------|---------|

|------------------------|---------|

X

| Option  | Module   |                                                               | <b>Power Requirements</b> |                                        | Bus Loads* |    |          |             |

|---------|----------|---------------------------------------------------------------|---------------------------|----------------------------------------|------------|----|----------|-------------|

| Desig.  | No(s).   | Description                                                   | + 5V<br>±5%               | + 12V<br>±3%                           | AC(Max)    | DC | Size     |             |

| H9281C  |          | 2 × 12 backplane                                              |                           | ······································ | 3.6        | 0  | <u> </u> |             |

| IBV11-A | M7954    | Instrument bus<br>interface                                   | 0.8 A                     | _                                      | 1.9        | 1  | Double   | 7           |

| KD11-F  | M7264    | LSI-11 CPU with<br>4K RAM                                     | 1.8A                      | 0.8A                                   | 2.4        | 1  | Quad     | NTRODUCTION |

| KD11-H  | M7264-YA | LSI-11 CPU<br>without RAM                                     | 1.6A                      | 0.25A                                  | 2.4        | 1  | Quad     | B           |

| KD11-HA | M7270    | LSI-11/2 CPU                                                  | 1. <b>0A</b>              | 0.22A                                  | 1.7        | 1  | Double   | <u> </u>    |

| KDF-11  | M8186    | LSI-11/23 CPU                                                 | 2.0A                      | 0.2A                                   | 2.0        | 1  | Double   | ō           |

| KPV11-A | M8016    | Power-fail/line-<br>time clock                                | 0.56 A                    | _                                      | 1.63       | 1  | Double   | Ž           |

| KPV11-B | M8016-YB | Power-fail/line-<br>time clock/120 $\Omega$<br>bus terminator | 0.56 A                    | -                                      | 1.63       | 1  | Double   |             |

## Table 1 Module Specifications

| Option `<br>Desig. | Module<br>No(s). | Description                                                       | Power Requirements<br>+ 5V + 12V |                | Bus Loads* |    |        |             |

|--------------------|------------------|-------------------------------------------------------------------|----------------------------------|----------------|------------|----|--------|-------------|

|                    |                  |                                                                   | ±5%                              | ±3%            | AC(Max)    | DC | Size   |             |

| KPV11-C            | M8016-YC         | Power-fail/line-<br>time clock/220 Ω<br>bus terminator            | 0.56 A                           | _              | 1.63       | 1  | Double |             |

| KUV-11             | M8018            | WCS module                                                        | 3.0A                             |                |            | 1  | Quad   | =           |

| KWV11-A            | M7952            | Programmable<br>real-time clock                                   | 1.75A                            | 0.01A          | 3.4        | 1  | Quad   | NTRODUCTION |

| LAV11              | M7949            | LA 180 line printer<br>interface                                  | 0.8 A                            | _              | 1.8        | 1  | Double |             |

| LPV11              | M8027            | LA180/LP05<br>printer interface                                   | 0.8 A                            | _              | 1.4        | 1  | Double | CTI         |

| MMV11-A            | G653             | 4K X 16 core<br>memory                                            |                                  | 1.91           | 1          | 2  | Quads  | N           |

|                    |                  | (standby current)                                                 | 3.0 A<br>7.0 A                   | 0.2 A<br>0.6 A |            |    |        |             |

|                    |                  | (operating current)                                               |                                  | 0.0 A          | 10         |    | Dauble |             |

| MRV11-AA           | M7942            | 4K X 16 read-only<br>memory (less<br>PROM integrated<br>circuits) | 0.4 AA                           | _              | 1.8        | 1  | Double |             |

\* These ac load figures were measured using standard TDR (time domain reflectometry) techniques. The conversion factor is 9.35 pF/ac load. These numbers are nominal values which will tend to vary from module to module due to normal tolerances of components used in the manufacturing of the product.

.

| Table 1 Mo | dule Sp | ecifications |

|------------|---------|--------------|

|------------|---------|--------------|

| Option<br>Desig. | Module   | Power Requirements                                            |             | Bus Loads    | ;*      |    |        |             |

|------------------|----------|---------------------------------------------------------------|-------------|--------------|---------|----|--------|-------------|

|                  | No(s).   | Description                                                   | + 5V<br>±5% | + 12V<br>±3% | AC(Max) | DC | Size   |             |

|                  |          | (with 32 512 X 4<br>PROM integrated<br>circuts)<br>(MRV11-AC) | 2.8 A       |              |         | -  |        | Ĩ           |

| MRV11-BA         | M8021    | UV PROM-<br>RAM (less PROM<br>integrated circults)            | 0.58 A      | 0.34 A       | 2.8     | 1  | Double | TROD        |

|                  |          | (with 8 1K X 8<br>PROM integrated<br>circuits)<br>(MRV11-BC)  | 0.62 A      | 0.5 A        |         |    |        | NTRODUCTION |

| MRV11-C          | M8048    | PROM/ROM module                                               | 0.8A        |              | 2.0     | 1  | Double | -           |

| MSV11-B          | M7944    | 4K X 16 read/write<br>MOS memory                              | 0.6 A       | 0.54 A       | 1.9     | 1  | Double |             |

| MSV11-CD         | M7955-YD | 16K X 16 read/write<br>MOS memory                             | 1.1 A       | 0.54 A       | 2.3     | 1  | Quad   |             |

## Table 1 Module Specifications

| Option<br>Desig. | Module<br>No(s). | Description                                        | Power Requirements + 5V + 12V |        | Bus Loads* |    |         |             |

|------------------|------------------|----------------------------------------------------|-------------------------------|--------|------------|----|---------|-------------|

|                  |                  |                                                    | ±5%                           | ±3%    | AC(Max)    | DC | Size    |             |

| MSV11-D          | M8044            | 4K/16K/32K<br>MOS memory                           | 1.7 A                         | 0.34 A | 2.0        | 1  | Double  |             |

| MSV11-E          | M8045            | 4K/16K/32K<br>MOS memory                           | 2.0 A                         | 0.41 A | 2.0        | 1  | Double  | IN          |

| MXV11-A          | M8047            | Multifunction module                               | 1.2A                          | 0.1A   | 2.0        | 2  | Double  | RO          |

| REV11-A          | M9400-YA         | 120 Ω terminator,<br>DMA refresh,<br>bootstrap ROM | 1.6 A                         | -      | 2.2        | 1  | Double  | NTRODUCTION |

| REV11-C          | M9400-YC         | DMA refresh,<br>bootstrap                          | 1.6 A                         | -      | 2.2        | 1  | Double  | NOI.        |

| RKV11-D          | M7269            | LSI-11 Bus control<br>for RKV11-D                  | 1.8 A                         | _      | 1.9        | 1  | Double  |             |

| RLV11            | M8013<br>M8014   | RL01 disk<br>drive                                 | 6.5 A                         | 1.0 A  | 3.2        | 1  | 2 Quads |             |

| RXV11M7946RX01 interface1.5 A—1.81RXV21N8029Double density1.1A2.01floppy interfacefloppy interface00TEV11M9400-YB120 Ω terminator0.5 A—00                                                                                                                                                                                                                                     |         |         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|

| RXV11         M7946         RX01 interface         1.5 A         —         1.8         1           RXV21         N8029         Double density         1.1A         2.0         1           floppy interface         1         1         1         1         0         0           TEV11         M9400-YB         120 Ω terminator         0.5 A         —         0         0 | DC Size |         |

| RXV21N8029Double density<br>floppy interface1.1A2.01<br>floppyTEV11M9400-YB120 Ω terminator0.5 A—00                                                                                                                                                                                                                                                                           | l Doubl |         |

| floppy interface<br>TEV11 M9400-YB 120 Ω terminator 0.5 A — 0 0                                                                                                                                                                                                                                                                                                               |         |         |

|                                                                                                                                                                                                                                                                                                                                                                               | i Doubl | _       |

| TU58 Serial/cartridge 0.75 1.24 may                                                                                                                                                                                                                                                                                                                                           | ) Doubl |         |

| cassette Appr.                                                                                                                                                                                                                                                                                                                                                                |         | NTRODUC |

| VK170 CAM7142 Serial video module 1.2A 0.15                                                                                                                                                                                                                                                                                                                                   | Doubl   |         |

## CONFIGURATION

The LSI-11 bus permits a unified addressing structure in which control/status and data registers for peripheral devices are directly addressed as memory locations. All operations on these registers, such as transferring informaton to or from them or manipulating data within them, are performed by normal memory address instructions. The use of memory address instructions on peripheral device registers greatly increases the flexibility of input/output communications.

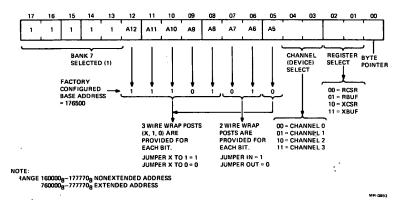

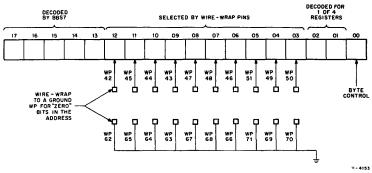

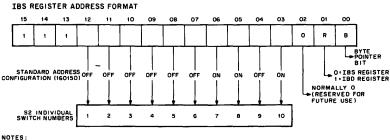

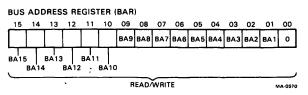

#### Addresses

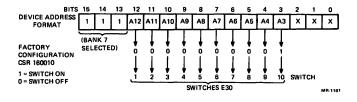

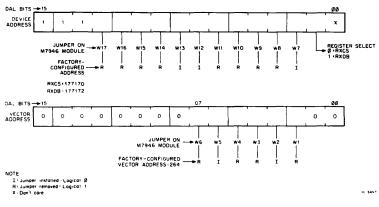

All the options except memories have at least one control and status register and may have several data registers. Each register is assigned an address through which the option can communicate with the processor. The upper 4K of memory address space is reserved for the processor and external input/output (I/O) registers. The user can select any address (Appendix A) in the range of 160000 through 177776 and assign it to the option interface module. The modules are configured to the desired address by selecting dip switches, connecting or disconnecting wire-wrap pins, or installing or removing wired jumpers on the module.

## Figure 1 Module Dimensions

INTRODUCTION

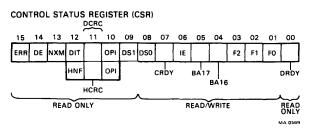

## **Control and Status Registers**

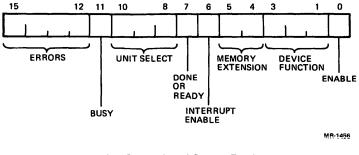

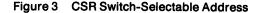

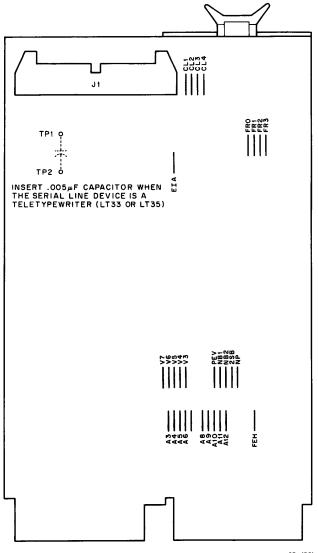

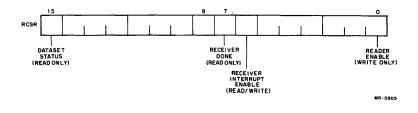

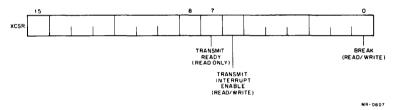

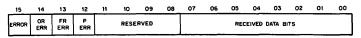

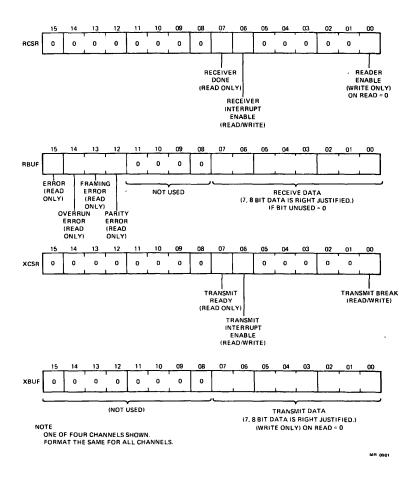

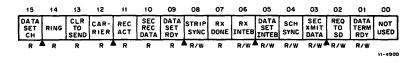

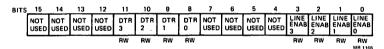

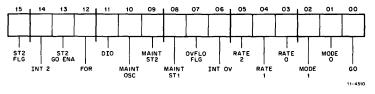

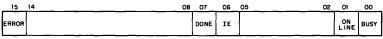

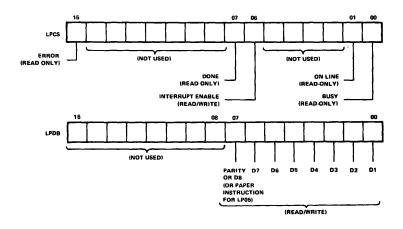

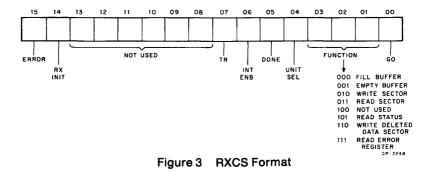

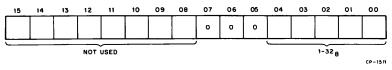

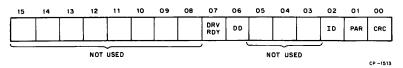

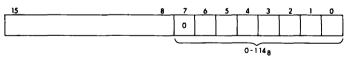

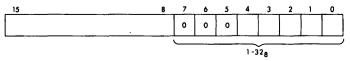

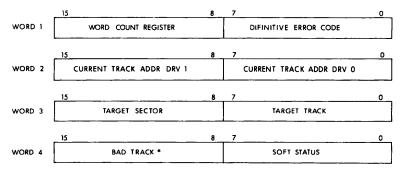

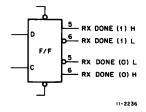

The general form for the control and status registers, shown in Figure 2, does not necessarily apply to every device, but is presented as a guide.

Figure 2 Control and Status Registers

Many devices require less than 16 status bits. Other devices will require more than 16 and therefore will require additional status and control registers.

The bits in the control and status registers are generally assigned as described below.

## **Typical Control and Status Register**

## Bit: 15-12 Name: Errors

**Function:** Generally there is an individual bit associated with a specific error. When more bits are required for errors, they can be obtained by expanding the error section in the word or by using another status word. Generally bit 15 is the inclusive-OR of all other error bits (If there is more than one). Most devices will have "hard" error conditions which will cause an interrupt if bit 6 is set. Some may also have "soft" errors (warning types) which do not cause immediate interrupts.

## Bit: 11 Name: Busy

Function: Set to indicate that a device operation is being performed.

## Bit: 10-8 Name: Unit Select

**Function:** Some peripheral systems have more than one device per control. For example, a disk system can have multiple surfaces per control and an analog-to-digital converter can have multiple channels. The unit bits select the proper surface or channel.

## Bit: 7 Name: Done or Ready

**Function:** The register can contain a done bit, a ready bit or a donebusy pair of bits, depending on the device. These bits are set and cleared by the peripheral device, but may be queried by the program to determine the availability of the device.

## Bit: 6 Name: Interrupt Enable

**Function:** Set by the program to allow an interrupt to occur as a result of a function done or error condition.

#### Bit: 5-4 Name: Memory Extension

**Function:** Allows devices to use a full 18 bits to specify addresses on the bus.

#### Bit: 3-1 Name: Device Function Bits

Function: Specifies the operation that a device is to perform.

Bit: 0 Name: Enable

Function: Set to enable the device to perform an operation.

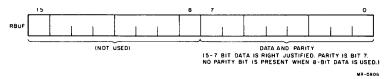

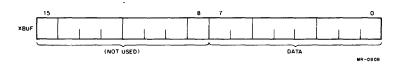

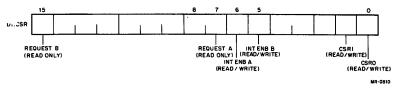

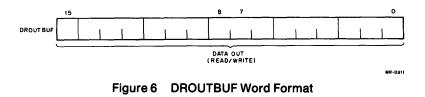

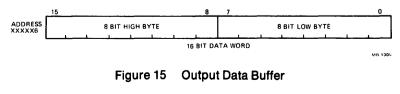

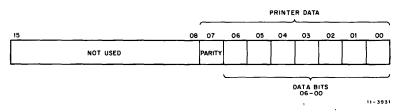

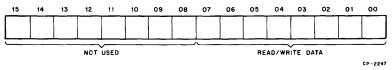

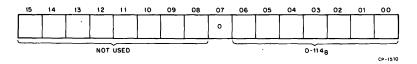

### Data Buffer Registers

The data buffer register is used for temporarily storing data to be transferred into or out of the computer. The number and type of data registers is a function of the device.

#### Interrupts

Interrupts are requests, made by peripheral devices, which cause the processor to temporarily suspend its present (background) program execution to service the requesting device. Each device that is capable of requesting an interrupt must have a user-supplied service routine that is automatically entered when the processor acknowledges the interrupt request. After completing the service routine execution, program control is returned to the interrupted program. This type of operation is especially useful for the slower peripheral devices.

A device can interrupt the processor only when interrupts are enabled and services interrupts only when the appropriate PSW bits are cleared. Device priority is highest for devices electrically closest to the processor along the bus. Any device that can interrupt the processor can also interrupt the service routine execution of a lower priority device if the processor's priority is set during the execution; hence, interrupt nesting to any level is possible with this interrupt structure. Each device normally contains a control/status register (CSR), which includes an interrupt enable bit. A program must set this bit before an interrupt can be generated by the device.

## INTRODUCTION

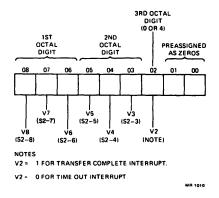

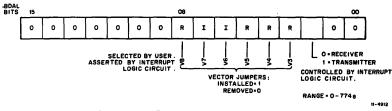

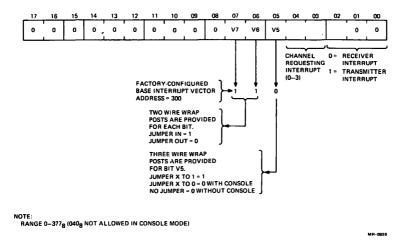

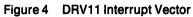

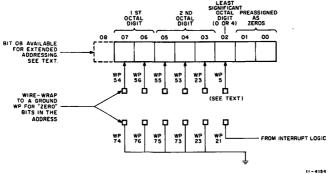

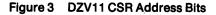

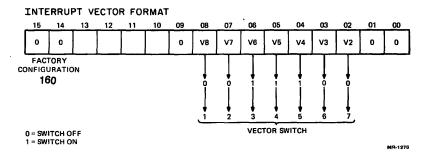

#### **Interrupt Vectors**

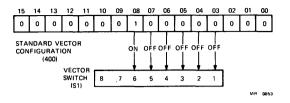

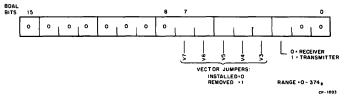

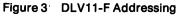

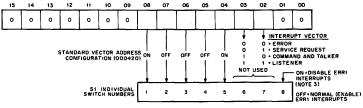

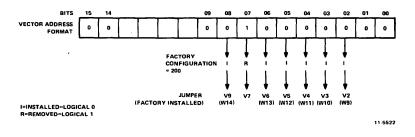

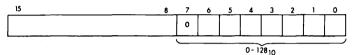

An interrupt vector associated with each device is hard-wired into the devices's interface/control logic. This vector is an address pointer that is transmitted to the processor duing the interrupt acknowledge sequence, allowing automatic entry into the service routine without device polling. The user can select an interrupt vector from the range of 000 to 777 for any interrupting options. The module can be configured to the desired interrupt vector by either selecting dip switches, connecting or disconnecting wire-wrap pins, or installing or removing wired jumpers on the module.

• • . · · ~

the interfaces

### AAV11-A 4-CHANNEL 12-BIT D/A CONVERTER

### GENERAL

The AAV11-A is a 4-channel, digital-to-analog converter module that includes control and interfacing circuits. It has four D/A converters, a dc-dc converter that provides power to the analog circuits, and a precision voltage reference. Each channel has its own holding register that can be addressed separately and provides 12 bits of resolution. These registers can be written and read, using either word or byte format. In addition, bits 0, 1, 2, and 3 of the fourth holding register are brought out to the I/O connector so they can be used as a 4-bit digital output register.

### **FEATURES**

- Four 12-bit digital input channels, binary encoded for either unipolar mode or bipolar mode.

- Jumper-selected output ranges and modes: Bipolar mode ±2.56 V, ±5.12 V, ±10.24 V Unipolar mode 0 to +5.12 V, 0 to +10.24 V

- One part in 4096 resolution

- 5V/µs slew rate

- ±5 mA drive capability per converter

### SPECIFICATIONS

| Identification           | A6001                                                                                       |

|--------------------------|---------------------------------------------------------------------------------------------|

| Size                     | Quad                                                                                        |

| Power                    | +5.0 Vdc ±5% at 1.5 A<br>+12.0 Vdc ±3% at 0.4 A                                             |

| Bus loads<br>AC<br>DC    | 1.9<br>1.0                                                                                  |

| Resolution               | 12-bits (1 part in 4096)                                                                    |

| Number of D/A converters | 4                                                                                           |

| Digital input            | 12-bits (binary encoded for uni-<br>polar mode; offset binary encod<br>ed for bipolar mode) |

| Digital storage          | Read/write, word or byte opera-<br>ble, single buffered                                     |

| Output voltage range<br>(jumper selected)       | ±2.56 V, ±5.12 V, ±10.24 V bipo-<br>lar, 0 V to +5.12 V, 0 V to +10.24<br>V unipolar |

|-------------------------------------------------|--------------------------------------------------------------------------------------|

| Gain accuracy                                   | Adjustable (factory set for bipolar $\pm 5.12$ V)                                    |

| Gain temperature coefficient                    | 10 PPM per °C, max.                                                                  |

| Offset temperature coefficient                  | 20 PPM of full scale range per °C, max.                                              |

| Linearity                                       | $\pm \frac{1}{2}$ LSB max, non-linearity                                             |

| Differential linearity                          | $\pm \frac{1}{2}$ LSB, monotonic                                                     |

| Output impedance                                | 1 ohm max.                                                                           |

| Drive capability                                | $\pm 6$ mA max. per converter                                                        |

| Slewing speed                                   | 5 V/µs                                                                               |

| Rise and settling time (to 0.1% of final value) | 4 $\mu s$ (8 $\mu s$ wth 5000 pF load in parallel with 1 $k\Omega$                   |

### DESCRIPTION

#### General

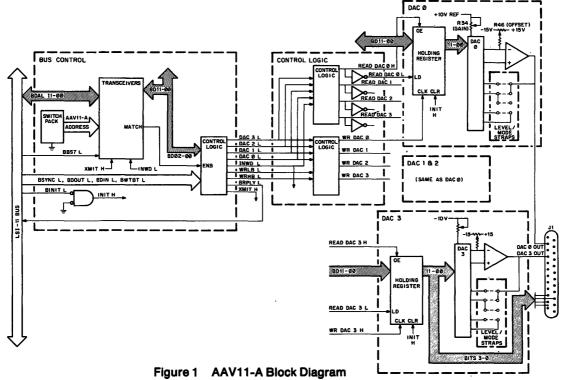

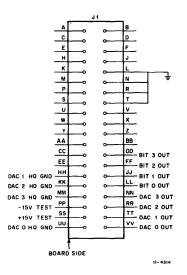

The function of the AAV11-A module is to convert digital data input to an analog dc voltage output that is representative of the input. This is accomplished by the bus interface, the control logic, and the D/A converter functions as shown in Figure 1.

<u>3</u>5

11-4179

### **Bus Interface**

The logic associated with the bus interface section maintains proper communications protocol between the processor LSI-11 bus and the AAV11-A. This logic generates and monitors the bus signals involved during data transfers between the processor and the AAV11-A, permitting the AAV11-A to recognize when it is being addressed by the processor (address defined by setting on the address switch pack) to accept input data from the processor, and to output data to the processor.

### **Control Logic**

The AAV11-A has no control/status register. The four digital-to-analog converters continually generate voltages at their outputs that reflect whatever digital values have most recently been written into their respective holding registers. The role of the control logic is to make the necessary discriminations between requests to change the state of the holding registers (i.e., to *write* into the holding registers), and requests to put the holding register contents onto the BD lines where they can be picked up through the transceivers by the processor.

### DACs 0, 1, and 2

Digital-to-analog conversion functions are performed in each of the four AAV11-A channels by identical circuits:

- a holding register which stores the digital value output by the processor

- a digital-to-analog converter (DAC) proper which generates a current that is a function of the holding register value and of the mode/level jumper conditions

- an amplifier that translates the current into a proportional voltage, provides a low output impedance for the channel, and permits adjustment of signal offset

### DAC 3

DAC 3 is identical to DACs 0, 1, and 2 except that holding register bits 0-3 are routed to the I/O connector as well as to the DAC. This arrangement permits these bits to be routed to external equipment that requires binary control signals at programmable intervals. Control data in these bit positions affects any 12-bit D/A conversion that they coincide with, but since they involve the least significant bits of the word, the worst-case error is less than 0.5 percent. Consequently, DAC 3 can be used as a 12-bit DAC or as an 8-bit DAC plus four output bits for CRT Intensify, Store, Non-Store, Erase, etc.

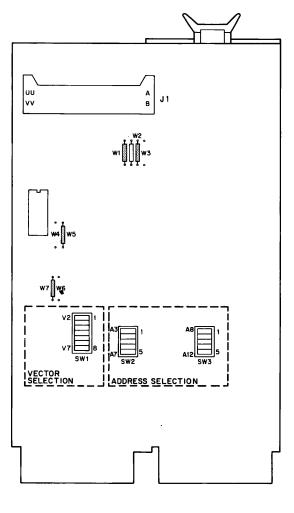

### CONFIGURATION

#### General

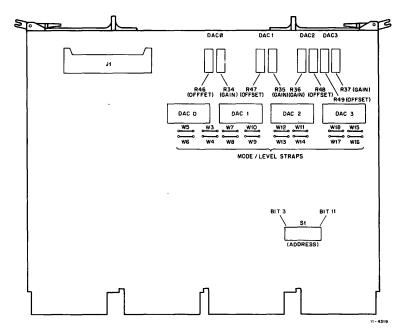

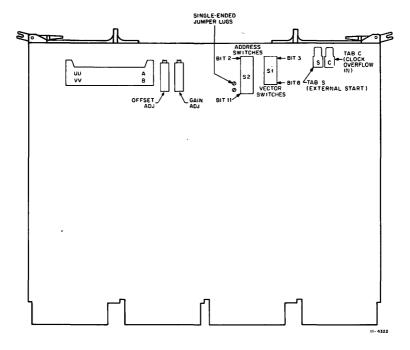

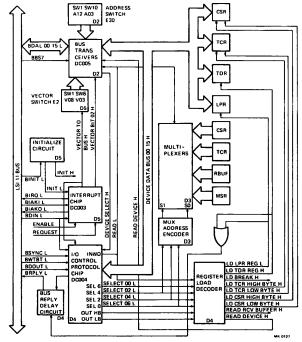

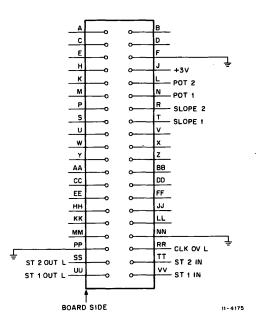

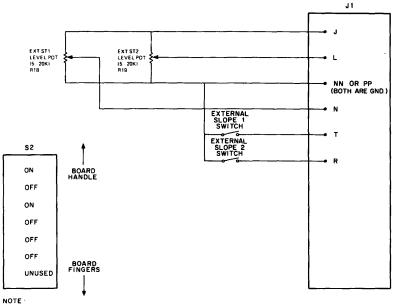

This section describes how the user can configure the module to function within his system by setting dip switches (Figure 2) to obtain the desired device address. The voltage range for each D/A converter (DAC 0—DAC 3) can be configured independently by installing or removing the designated jumpers (Figure 2) associated with a specific D/A converter. This section also describes how to connect external devices to the module. The standard factory addresses for the registers are listed in Table 1.

| Register  | Mnemonic | Address |

|-----------|----------|---------|

| Holding 0 | DAC 0    | 170440  |

| Holding 1 | DAC 1    | 170442  |

| Holding 2 | DAC 2    | 170444  |

| Holding 3 | DAC 3    | 170446  |

#### Table 1 Standard Addresses

Figure 2 AAV11-A Connectors, Switches, and Jumpers

#### **Device Registers**

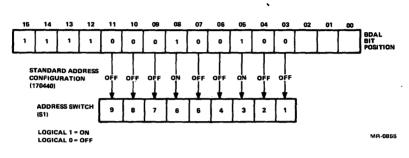

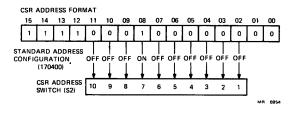

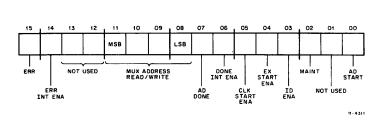

The device registers can be configured to respond to any address within the range 170000 to 177777. Each register address does not have to be individually set. The DAC 0 register address is selectable and the last digit will be zero. The remaining registers will use addresses 17XXX2, 17XXX4, and 17XXX6 for DAC 1, DAC 2, and DAC 3 registers, respectively. The factory-configured device address is 170440 as shown in Figure 3. The word formats for the DAC registers are described in Table 2. Note that all device registers are always a sequence of four consecutive even locations. There is no vector used for this module.

### D/A Converter Range and Mode

The range and mode (bipolar or unipolar) voltages can be selected by the user inserting or removing jumpers as shown in Figure 2. Four jumpers are associated with each D/A converter. The module is facto-

ry-configured for -5.12 to +5.12 V bipolar operation. The jumper configurations for the bipolar mode ranges are shown in Table 3; the unipolar ranges are shown in Table 4.

| Bit   | DAC 0, DAC 1, DAC 2 | DAC 3              |

|-------|---------------------|--------------------|

| 15-12 | Not used            | Not used           |

| 11    | Binary 11           | Binary 11          |

| 10    | Binary 10           | Binary 10          |

| 9     | Binary 9            | Binary 9           |

| 8     | Binary 8            | Binary 8           |

| 7     | Binary 7            | Binary 7           |

| 6     | Binary 6            | Binary 5           |

| 5     | Binary 5            | Binary 5           |

| 4     | Binary 4            | Binary 4           |

| 3     | Binary 3            | Binary 3/Control 3 |

| 2     | Binary 2            | Binary 2/Control 2 |

| 1     | Binary 1            | Binary 1/Control 1 |

| 0     | Binary 0            | Binary 0/Control 0 |

|       | ±2.56 V | ±5.12 V | ±10.24 V |

|-------|---------|---------|----------|

| DAC 1 |         |         |          |

| W3    | IN      | IN      | OUT      |

| W4    | OUT     | OUT     | IN       |

| W5    | IN      | OUT     | OUT      |

| W6    | IN      | IN      | IN       |

| DAC 2 |         |         |          |

| W7    | IN      | IN      | OUT      |

| W8    | OUT     | OUT     | IN       |

| W9    | IN      | OUT     | OUT      |

| W10   | IN      | IN      | IN       |

| DAC 3 |         |         |          |

| W11   | IN      | IN      | OUT      |

| W12   | OUT     | OUT     | IN       |

| W13   | IN      | OUT     | OUT      |

| W14   | IN      | IN      | IN       |

| DAC 4 |         |         |          |

| W15   | IN      | IN      | OUT      |

| W16   | OUT     | OUT     | IN       |

| W17   | IN      | OUT     | OUT      |

| W18   | IN      | IN      | IN       |

### Table 3 Jumper Configurations for Bipolar Operation

|       | 0 V—+5.12 V | 0 V—+10.24 \ |

|-------|-------------|--------------|

|       |             |              |

| DAC 1 |             |              |

| W3    | IN          | IN           |

| W4    | OUT         | OUT          |

| W5    | IN          | OUT          |

| W6    | OUT         | OUT          |

| AC 2  |             |              |

| W7    | IN          | IN           |

| W8    | OUT         | OUT          |

| W9    | IN          | OUT .        |

| W10   | OUT         | OUT          |

| AC 3  |             |              |

| W11   | IN          | IN           |

| W12   | OUT         | OUT          |

| W13   | IN          | OUT          |

| W14   | OUT         | OUT          |

| AC 4  |             |              |

| W15   | IN          | IN           |

| W16   | OUT         | OUT          |

| W17   | IN          | OUT          |

| W18   | OUT         | OUT          |

#### Table 4 Jumper Configurations for Unipolar Operation

#### **J1 Output Connections**

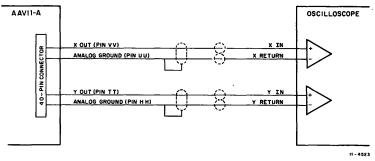

Analog output devices such as oscilloscopes may be either grounded or floating. If the oscilloscope is grounded, either through its power plug or through contact between its chassis and a grounded cabinet, the oscilloscope ground should not be connected to any of the AAV11-A ground pins. Doing so may result in a ground loop which will adversely affect oscilloscope control results as well as ADV11-A operation (if used). If the oscilloscope is floating, its ground should be connected to the AAV11-A logic ground, J1 pins L, N, R, or T. Note that the foregoing assumes that the LSI-11 power suppy ground is connected to power line (earth) ground. If continuity checks reveal no such connection, attach a length of 12-gauge wire between the power supply ground and a convenient point associated with earth ground.

Oscilloscope X and Y inputs may be either differential or single-ended. Differential inputs should be driven as in Figure 4.

Figure 4 Connection to Oscilloscope with Differential Input

When oscilloscopes with single-ended inputs are involved, the AAV11-A analog grounds (pins UU and HH) are not used. The return path for X and Y signal currents is through ground for a grounded oscilloscope or through logic ground (pins L, N, R, or T) for a floating oscilloscope. Since the grounded, single-ended oscilloscope receives an input voltage which is the sum of the AAV11-A output and the ground difference voltage between the oscilloscope and the AAV11-A, noise and line frequency errors may be minimized by plugging the oscilloscope into an ac socket as close as possible to the LSI-11 system. Running single-ended oscilloscopes in a floating configuration will eliminate noise

-

and line frequency errors which are due to ground voltage differences.

The effect of magnetic coupling into the oscilloscope input lines can be minimized for a differential-input oscilloscope by running the AAV11-A output and its return line in a twisted pair. No benefit is derived from a twisted pair with a single-ended oscilloscope input.

The effect of electrostatic coupling into the oscilloscope input lines can be minimized by shielding the input lines from AAV11-A to the oscilloscope. The shield should be connected to ground at one end only. Grounding the shield at both ends may result in a ground loop which will adversely affect oscilloscope control results and any ADV11-A A/D operations (if used).

Careful selection of cabling is essential. The D/A outputs are capable of driving a maximum of 5000 pF. Output impedance is 1 ohm. Output current limit is 5 mA.

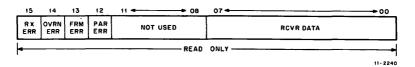

### **Optional Equipment**