# peripherals handbook

DIGITAL Facility, Parker Street, Maynard, Massachusetts

### **CORPORATE PROFILE**

Digital Equipment Corporation designs, manufactures, sells and services computers and associated peripheral equipment, and related software and supplies. The Company's products are used world-wide in a wide variety of applications and programs, including scientific research, computation, communications, education, data analysis, industrial control, timesharing, commercial data processing, word processing, health care, instrumentation, engineering and simulation.

# peripherals handbook

Copyright<sup>©</sup> 1981 Digital Equipment Corporation. All Rights Reserved.

Digital Equipment Corporation makes no representation that the interconnection of its products in the manner described herein will not infringe on existing or future patent rights, nor do the descriptions contained herein imply the granting of license to make, use, or sell equipment constructed in accordance with this description.

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this manual.

DEC, DECnet, DECsystem-10, DECSYSTEM-20, DECtape DECUS, DECwriter, DIBOL, Digital logo, IAS, MASSBUS, OMNIBUS PDP, PDT, RSTS, RSX, SBI, UNIBUS, VAX, VMS, VT are trademarks of Digital Equipment Corporation

This handbook was designed, produced, and typeset by DIGITAL's New Products Marketing Group using an in-house text-processing system.

### CONTENTS

| CHAPTER · | 1 | INTRODUCTION | <br>1 |

|-----------|---|--------------|-------|

|           |   |              |       |

### CHAPTER 2 DISK DRIVES

| RX211 . |     |    |   |     |    |   |    |    |    |    | • | <br> | <br> |  | <br> |   | • |   |  |    |  |   |     | .4 |

|---------|-----|----|---|-----|----|---|----|----|----|----|---|------|------|--|------|---|---|---|--|----|--|---|-----|----|

| RL01/02 |     |    |   |     |    |   |    |    |    |    |   | <br> |      |  |      |   |   |   |  |    |  |   |     | 14 |

| RK07    |     |    |   |     |    |   |    |    |    |    |   | <br> |      |  |      |   |   | • |  |    |  | • |     | 24 |

| RM02/03 |     |    |   |     |    |   |    |    |    |    |   |      |      |  |      | • |   |   |  |    |  |   |     | 34 |

| RM80    |     |    |   |     |    |   |    |    |    |    |   |      |      |  |      |   |   |   |  |    |  | • |     | 48 |

| RP06    |     |    |   |     |    |   |    |    |    |    |   |      |      |  |      |   |   |   |  |    |  |   |     |    |

| RM05    |     |    |   |     |    |   |    |    |    |    |   |      |      |  |      |   |   |   |  |    |  |   |     |    |

| RP07    |     |    |   |     |    |   |    |    |    |    |   |      |      |  |      |   |   |   |  |    |  |   |     |    |

| disk dr | IVE | co | M | PAF | NS | 0 | 10 | CF | 1/ | ١R | Т |      |      |  |      | • |   |   |  | •• |  | • | • • | 91 |

### CHAPTER 3 MAGNETIC TAPES

| TU58 |     |    |     | •  |    |    |    |   |   |   |    | •  |   |   |    |    |   | • |     |   |   |   | • • |    |  |      |  |  |  | <br> |  |  | • • | <br>. 9 | 92 |

|------|-----|----|-----|----|----|----|----|---|---|---|----|----|---|---|----|----|---|---|-----|---|---|---|-----|----|--|------|--|--|--|------|--|--|-----|---------|----|

| TS11 |     |    |     |    |    |    |    |   |   |   |    |    |   |   |    |    |   |   |     |   |   |   |     |    |  | <br> |  |  |  |      |  |  |     | <br>10  | )8 |

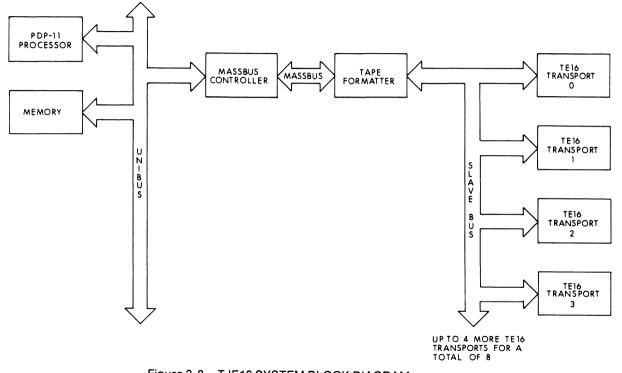

| TE16 |     |    |     |    |    |    |    |   |   |   |    |    |   |   |    |    |   |   |     |   |   |   |     |    |  |      |  |  |  |      |  |  |     |         |    |

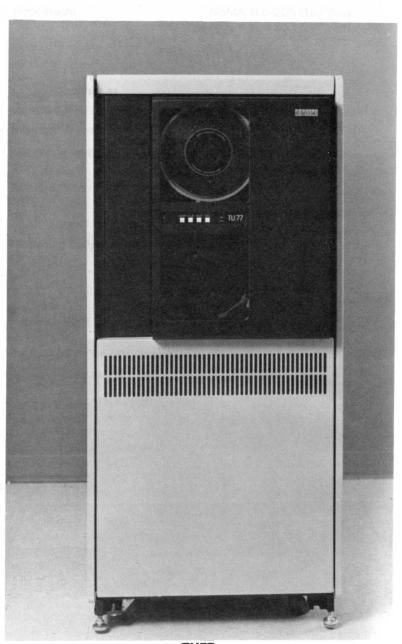

| TU77 |     |    |     |    |    |    | •  |   |   |   |    |    |   |   |    |    |   |   |     |   |   |   |     |    |  |      |  |  |  |      |  |  |     | <br>13  | 34 |

| TU78 |     |    |     |    |    |    |    |   |   |   |    |    |   |   |    |    | • |   |     |   |   |   |     |    |  | <br> |  |  |  |      |  |  |     | <br>14  | 18 |

| MAGN | IET | 10 | ; 1 | ٢A | ١F | PE | Ξ( | С | 0 | ٨ | 11 | Р, | 4 | R | 18 | 30 | 0 | N | 1 ( | C | Н | A | F   | 11 |  | <br> |  |  |  |      |  |  |     | <br>15  | 59 |

### CHAPTER 4 LINEPRINTERS

| LXY11/21      |           |         | <br> | 160 |

|---------------|-----------|---------|------|-----|

| LP11 SERIES   |           |         |      |     |

| LINEPRINTER C | COMPARISO | N CHART | <br> | 189 |

### CHAPTER 5 CARD READERS

| CR11 SERIES                  | 190 |

|------------------------------|-----|

| CMS11-K/CME11-K              | 202 |

| CARD READER COMPARISON CHART |     |

### CHAPTER 6 SENSOR I/O DEVICES

| AA11-K        |  | • | <br> |  |  |      |  |  |      | <br> |  |  | • |      |  |  |      |  | <br> |  |  |   | <br> | . : | 21 | 4  |

|---------------|--|---|------|--|--|------|--|--|------|------|--|--|---|------|--|--|------|--|------|--|--|---|------|-----|----|----|

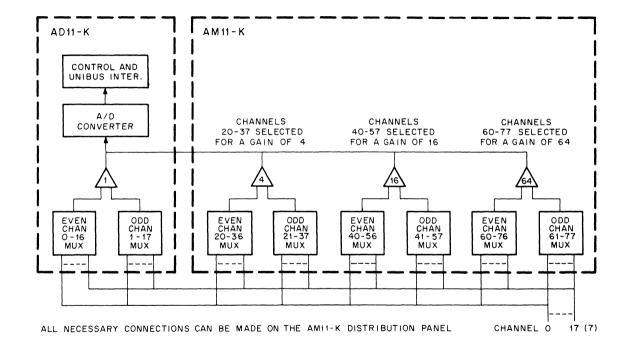

| AD11-K        |  |   | <br> |  |  |      |  |  |      | <br> |  |  |   |      |  |  | <br> |  | <br> |  |  |   | <br> | . : | 22 | 20 |

| AM11-K        |  |   | <br> |  |  |      |  |  |      | <br> |  |  |   | <br> |  |  |      |  | <br> |  |  |   | <br> | . : | 22 | 26 |

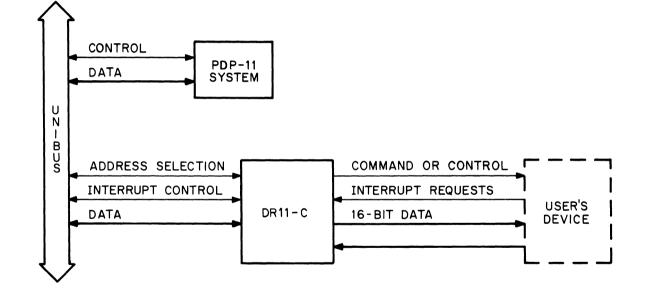

| DR11-C        |  | • | <br> |  |  |      |  |  | <br> | <br> |  |  | • | <br> |  |  |      |  | <br> |  |  |   | <br> | . : | 23 | 33 |

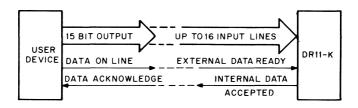

| DR11-K        |  |   | <br> |  |  |      |  |  |      | <br> |  |  |   | <br> |  |  |      |  | <br> |  |  |   | <br> | .:  | 23 | 38 |

| <b>DR11-W</b> |  |   | <br> |  |  | <br> |  |  | <br> | <br> |  |  | • | <br> |  |  |      |  |      |  |  | • |      | . 1 | 24 | 4  |

| IB11    | <br> |

|---------|------|

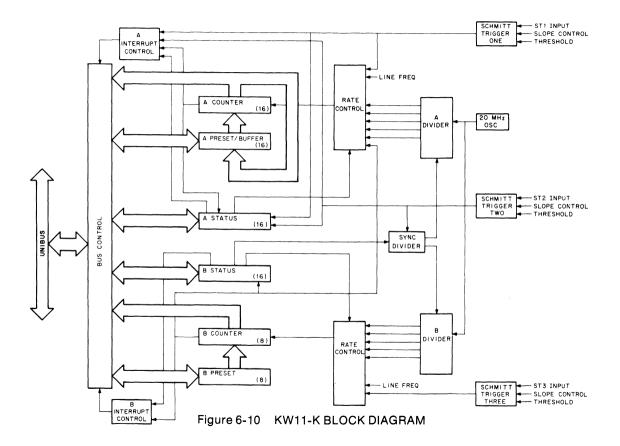

| KW11-K  | <br> |

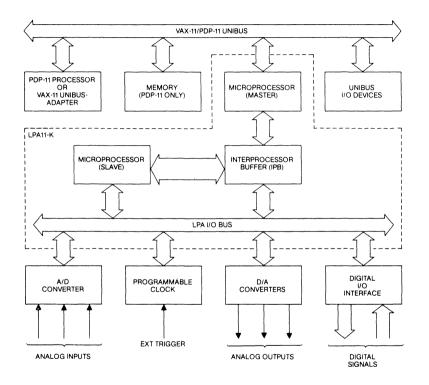

| LPA11-K | <br> |

| DISK REGISTER<br>MAGNETIC TAP<br>LINEPRINTER R<br>CARD READER I | REGISTER DIAGRAMS AND BIT DEFINITION<br>RS<br>E REGISTERS<br>EGISTERS<br>REGISTERS<br>REGISTERS<br>VICE REGISTERS | 275<br>368<br>439<br>442 |

|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------|

|                                                                 | STANDARD AND COMPRESSED HOLLE                                                                                     |                          |

|                                                                 | EXAMPLES OF LXY11/LXY21 PRINT COPY                                                                                |                          |

| APPENDIX C                                                      | ASCII CODE CHART                                                                                                  | C1                       |

|                                                                 | UNIBUS I/O PAGE DEVICE ADDRESSES                                                                                  |                          |

| APPENDIX E                                                      | EXPANSION BOX COMPARISON CHART                                                                                    | E1                       |

| INDEX                                                           |                                                                                                                   | <b>I</b> 1               |

# CHAPTER 1 INTRODUCTION

DIGITAL's family of computer peripherals is continually growing to provide you with the hardware that most precisely meets your needs. Cost effectiveness, capacity, ease of use, reliability, maintainability, and serviceability are constantly being upgraded.

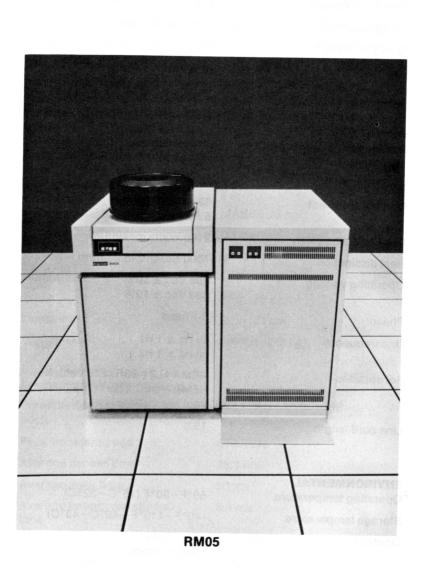

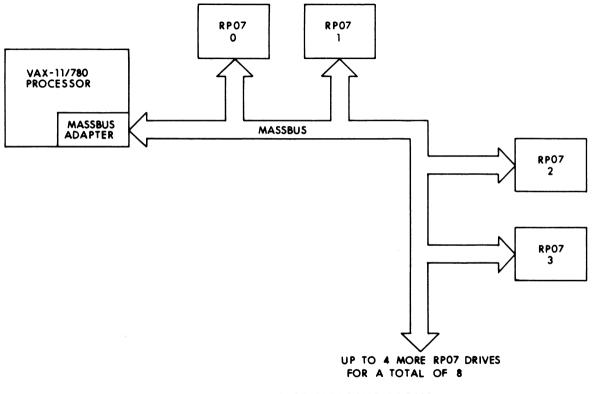

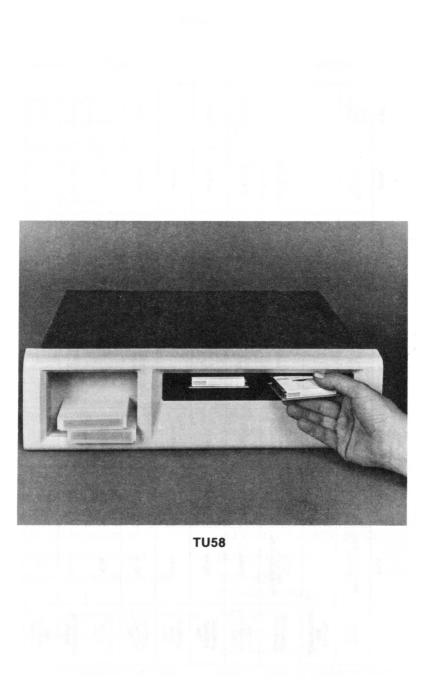

The two most recent additions to DIGITAL's family of computer peripherals supported by VAX systems are the RP07 disk drive, utilizing Winchester fixed-media technology, and the TU78 magnetic tape transport, using Group Coded Recording (GCR) technology. These new peripherals combine state-of-the-art microprocessor control, large capacity, high speed, and self-test diagnostics. Other new disk drives include the RM80 and RM05. The RM80 disk drive, which also utilizes Winchester fixed-media technology and advanced microprocessor control, is supported on VAX systems. The RM05 is supported on both VAX-11/780 and PDP-11/70 systems. The latest lineprinters include the high-speed LP11-E band lineprinter with 64- and 96-character sets and the high-speed LXY21 printer/plotter, both supported by UNIBUS PDP-11 systems and VAX systems.

With the purchase of one of DIGITAL's peripherals, you will receive detailed user and maintenance documentation. This information may be supplemented by the excellent tutorial guides to DIGITAL's software languages and operating systems and by other volumes in the Handbook series. DIGITAL's Educational Services group offers a wide range of hardware and software courses specifically designed to address customers' needs.

In addition, DIGITAL's Computer Special Systems (CSS) group provides customers with design service and products to complement the corporation's high volume offerings. CSS products address the customers' needs in the process I/O, graphics, networks products, and special terminals marketplaces.

The Peripherals Handbook contains chapters on all of DIGITAL's currently-marketed UNIBUS PDP-11 and VAX disks, magnetic tapes, lineprinters, card readers, and sensor I/O devices. It should be used in conjunction with the Terminals and Communications Handbook which describes DIGITAL's terminals and communications equipment.

### INTRODUCTION

This book is divided into chapters by device type. Each chapter is further subdivided into sections by device. Each section contains the following:

- an introduction

- a list of features

- a general description

- packaging information

- data formats and data organization information (where applicable)

- operation description

- interrupt information

- reliability/maintainability features

- controls and indicators (where applicable)

- specifications

At the end of the disk, magnetic tape, lineprinter, and card reader chapters is a comparison chart of the peripherals in that chapter. This allows easy comparison among like devices to ensure the best selection for your needs. The specification information is subject to change without notice, and should be considered as a guide only. For specific site preparation information, please consult your local DIGITAL sales office.

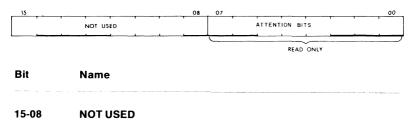

Chapter 7 contains the register diagrams and bit definitions for all the peripherals described in this book. The appendices contain additional, relevant information including an ASCII code chart, a standard and compressed Hollerith code chart, and UNIBUS addresses and vector assignments for DIGITAL'S peripherals.

In addition to the Peripherals Handbook, DIGITAL's series of handbooks includes the Terminals and Communications Handbook, the PDP-11 Processor and Software Handbooks, the Microcomputer Processor, Microcomputer Interfaces, and Microcomputers and Memories Handbooks, and the VAX Hardware, Software, and Architecture Handbooks.

**RX211**

### CHAPTER 2 DISK DRIVES

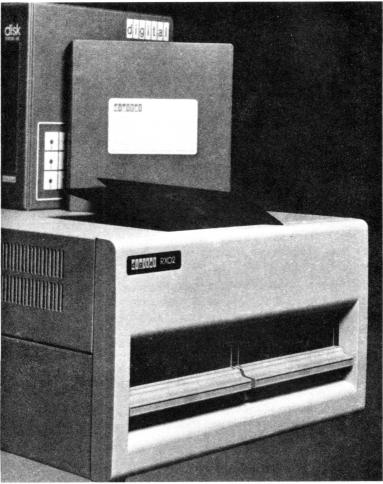

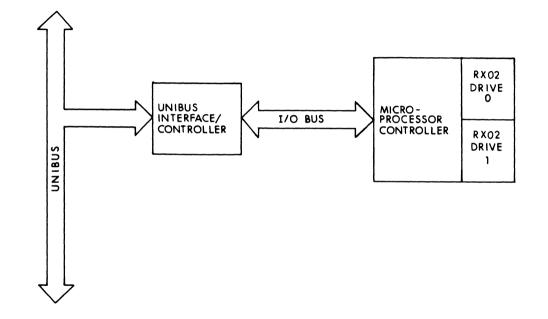

### RX211

The RX211 is a dual-drive, double density, floppy disk subsystem connected to the UNIBUS via an interface/controller. The RX211-BA(BD) subsystems are supported by UNIBUS PDP-11 systems. VAX-11/750 systems also support the RX211-BA(BD) subsytems, but only as a data file resident device for transport of data to and from other DIGITAL systems. The low cost of the RX211 subsystem makes it ideal for archive storage, diagnostic loading, or software updates.

### FEATURES

- Double density recording provides greater data storage capacity

- Program-selectable single density mode provides compatibility with other floppy disk subsystems

- 0.5 MB of formatted data storage capacity per diskette (1 MB total per RX211 subsystem)

- Direct Memory Access (DMA) data transfers

- Microprocessor controller

- Compact, removable diskettes

### DESCRIPTION

The RX211-BA(BB) floppy disk subsystems consist of two RX02 floppy disk drives, a microprocessor controller, an interface/controller, and a 15 ft (4.6 m) I/O cable. Up to two RX211 subsystems (a total of four RX02 floppy disk drives) are supported by UNIBUS PDP-11 systems and VAX-11/750 systems.

The RX211 floppy disk subsystems use industry standard diskettes. They are thin, flexible disks similar in size to a 45-rpm phonograph record. These diskettes are recorded on one side only. In double density mode, each diskette can store 0.5 MB of data. The programselectable single density mode provides compatibility with other floppy disk subsystems, such as the RX11.

### **RECORDING METHODS**

The RX211 reads/writes data in two modes: single density, which utilizes frequency modulation (FM) recording, and double density, which utilizes modified frequency modulation (MFM) recoding. The RX211 normally reads/writes data in double density mode. Single density mode can be read or written by the RX211 subsystem to provide

မု

compatability with other floppy disk subsystems. Data is written on the diskette by magnetizing small sections (bit cells) of the oxide on the diskette in different directions, i.e. either positively or negatively. A change in the direction of magnetization (flux transition) in the clock area or data area of a bit cell indicates whether the bit represented is a 1 or a 0.

### DATA ORGANIZATION

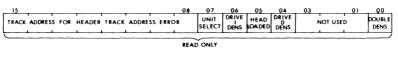

The RX211 has one read/write head that is used to both read and write data. The diskette surface is divided into 77 tracks. Each track is divided into 26 sectors with a data storage capacity of 2048 bits (256 bytes). Each sector is divided into a header field and a data field. The header field consists of a header preamble, a 56-bit header that contains the track and sector addresses, and a 16-bit header CRC (Cyclic Redundancy Check). The data field consists of a data preamble, an 8-bit code specifying the recording density, 2048 bits (256 bytes) of data, and a 16-bit data CRC. The header field is permanently recorded and can not be written by the RX211.

### **OPERATION**

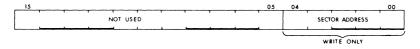

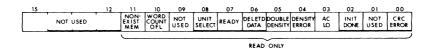

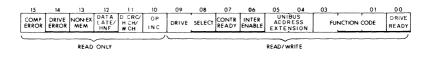

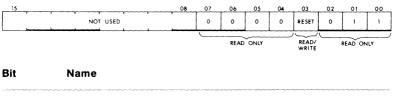

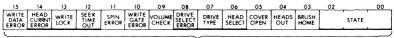

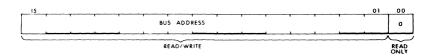

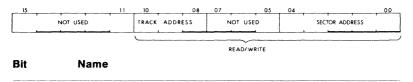

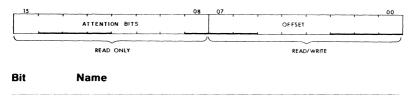

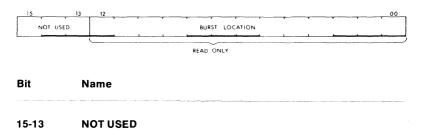

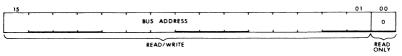

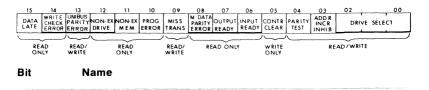

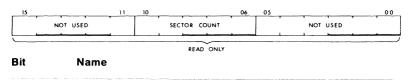

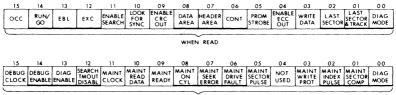

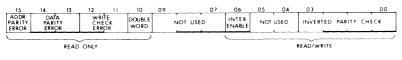

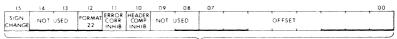

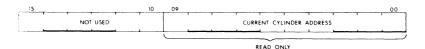

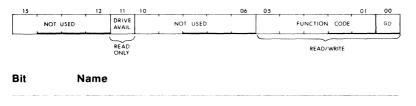

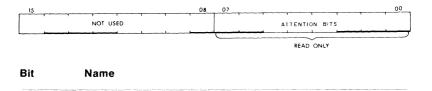

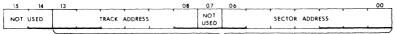

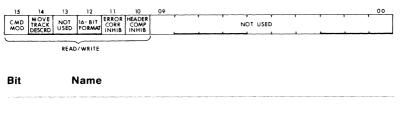

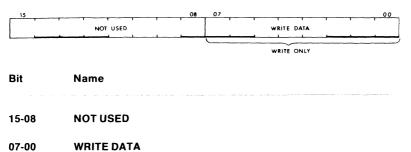

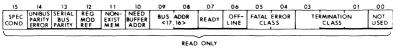

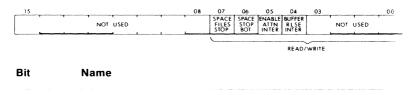

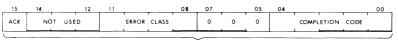

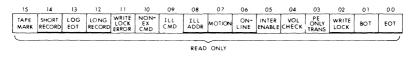

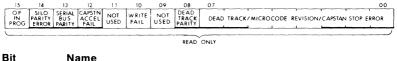

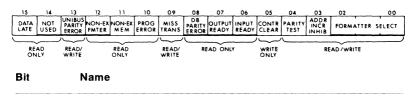

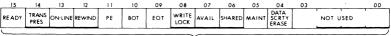

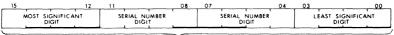

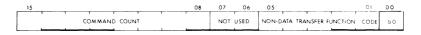

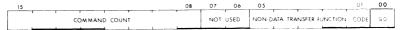

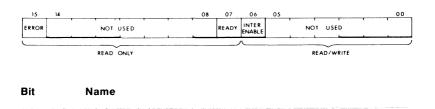

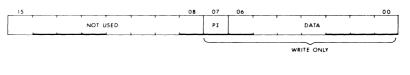

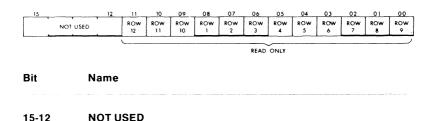

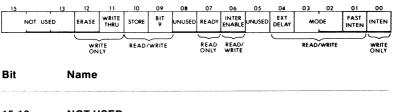

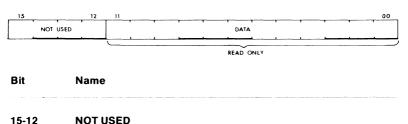

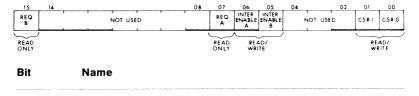

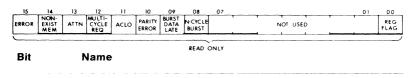

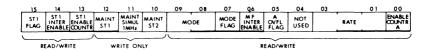

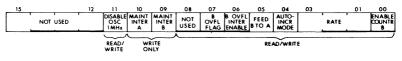

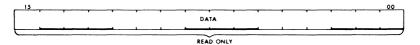

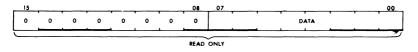

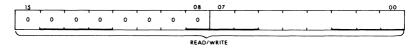

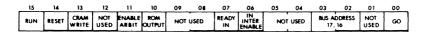

The RX211 controller has two registers: the Command and Status register and the Data Buffer register. The Data Buffer register is used to perform five different functions. When used to specify the diskette track, it is called the Track Address register. When used to specify the diskette sector, it is called the Sector Address register. When used to specify the number of data words to be transferred, i.e. the word count, it is called the Word Count register. When used to specify the starting memory address of the data to be transferred to or from memory, it is called the Bus Address register. When used to provide status information and specify errors, it is called the Error and Status register. When an error is detected, a READ ERROR CODE command will cause the controller to write four extended status words into memory. These extended status words contain detailed error and status information. (Refer to the register section at the back of this book for register and extended status word diagrams and bit definitions.)

To begin a READ operation, the processor loads the command and status register with a READ SECTOR command. The microprocessor controller responds with a request for the sector address by setting TRANSFER REQUEST <07> in the command and status register. The processor then loads the sector address into the data buffer register. The microprocessor controller next requests the track address by again setting TRANSFER REQUEST <07>, and the processor responds by loading the track address into the data buffer register. The READ operation has now been initiated.

The microprocessor controller positions the RX211 head to the track specified and reads each sector address from the sector header as it passes by on the rotating diskette until the specified sector is reached. The 2048 bits of data are then read and stored in the microprocessor's internal data buffer. When the data buffer is full, the microprocessor generates an interrupt to alert the processor that the data has been read off the diskette.

To transfer the data read off the diskette into memory, the processor loads the command and status register with an EMPTY BUFFER command. The microprocessor controller responds with a request for the number of data words to be transferred by setting TRANSFER REQUEST <07> in the command and status register. The processor then loads the word count into the data buffer register. The microprocessor next requests the starting memory address where the data read off the diskette is to be stored in memory by again setting TRANSFER REQUEST <07>, and the processor responds by loading the bus address into the data buffer register.

The microprocessor controller assembles the 2048 bits of data in its internal data buffer into 16-bit words and generates a parity bit for each word. Each 16-bit word plus parity is written into the memory location specified. This process continues until the proper word count is reached. Finally, the microprocessor generates an interrupt to alert the processor that the data read off the diskette has been stored in memory.

To begin a WRITE operation, the processor loads the command and status register with a FILL BUFFER command. The microprocessor controller responds with a request for the number of data words to be transferred by setting TRANSFER REQUEST <07>. The processor then loads the word count into the data buffer register. The microprocessor next requests the starting memory address of the data to be written onto the diskette by again setting TRANSFER REQUEST <07>, and the processor responds by loading the bus address into the data buffer register. The WRITE operation has now been initiated.

The microprocessor controller transfers the 16-bit words of data from memory, one by one, into its internal data buffer. This process continues until the proper word count is reached. The microprocessor generates an interrupt to alert the processor that the internal data buffer has been loaded.

To write the data onto the diskette, the processor loads a WRITE SECTOR command into the command and status register. The microprocessor controller responds with a request for the sector address by setting TRANSFER REQUEST <07>. The processor then loads the sector address into the data buffer register. The microprocessor next requests the track address by again setting TRANSFER REQUEST <07>, and the processor responds by loading the track address into the data buffer register.

The microprocessor controller positions the RX211 head to the track specified and reads each sector address from the sector header as it passes by on the rotating diskette until the specified sector is reached. The microprocessor then serially writes the 2048 bits of data into the sector and generates an interrupt to alert the processor that the data has been written onto the diskette.

### DATA INTEGRITY

Several error checking and correction features of the RX211 ensure that the data is correct.

The RX211 locates the specified track and then reads the header information to verify that it is the specified track. The header CRC is used to ensure that the header field has been read correctly. The header bits are used to generate a second CRC, which is then compared to the CRC read from the end of the header field on the diskette. If there is a discrepancy between the two CRCs, the microprocessor controller alerts the processor via an error code in the extended status word 1.

The data CRC is used to ensure that the data field has been read correctly. The data bits are used to generate a second CRC, which is then compared to the CRC read from the end of the data field on the diskette. If there is a discrepancy between the two CRCs, the microprocessor controller alerts the processor by setting a bit in the error and status register.

### INTERRUPTS

The RX211 floppy disk subsystem microprocessor controller uses a vectored interrupt to cause the program to branch to an interrupt service routine. An interrupt can occur only if the INTERRUPT EN-ABLE bit in the command and status register is set. Once the INTER-RUPT ENABLE bit is set, an interrupt request is generated whenever either the ERROR or DONE bit in the command and status register is also set.

When the ERROR bit is set, it indicates that some error condition exists and an interrupt is generated to cause the program to branch to an error handling routine. When the DONE bit is set, the microprocessor controller has successfully completed the operation and is ready to accept a command. An interrupt request is made so that the program can branch to an interrupt service routine.

The interrupt priority level is 5 and the interrupt vector address is 264. Note that the priority level can be changed with a priority plug and the vector address can be changed by switches in the interrupt control logic. However, any DIGITAL programs or other software referring to the priority level or interrupt vector address must also be changed if the priority plug or the vector address is changed.

### **RELIABILITY/MAINTAINABILITY**

Reliability means long life expectancy and uninterrupted processing of the floppy disk subsystem. Special design features of the RX211 subsystems provide these qualities of high reliability as well as ease of maintenance.

- Modular construction of the RX211 enables parts to be quickly removed and replaced during routine servicing and maintenance.

- Long head and diskette life due to minimal contact since the head only touches the diskette during an operation.

### SPECIFICATIONS

| MECHANICAL<br>Cabinet                | Cabinet-mountable |

|--------------------------------------|-------------------|

| Controller mounting code             | One quad slot     |

| Height                               | 10.5 in (26.7 cm) |

| Width                                | 19 in (48.3 cm)   |

| Depth                                | 17 in (43.2 cm)   |

| Weight                               | 60 lbs (27 kg)    |

| PERFORMANCE<br>Drives per controller | 2                 |

| Formatted capacity per diskette      | 0.5 MB            |

| Peak transfer speed                  | 61 KB/s           |

| Average access time*                 | 262 ms            |

\* Average access time is defined as the sum of the average seek time, the settling time, and the average latency (rotational) time.

| Average seek time                    | 154 ms             |

|--------------------------------------|--------------------|

| Average latency (rotational)<br>time | 83 ms              |

| Settling time                        | 25 ms              |

| Track-to-track seek                  | 6 ms               |

| Rotational speed                     | 360 rpm            |

| Data surfaces per diskette           | 1                  |

| Tracks per diskette                  | 77                 |

| Sectors per track                    | 26                 |

| Bytes per sector                     | 256 (8-bit format) |

| Tracks per inch                      | 48                 |

| Bits per inch                        | 3200               |

| Е | L | E | C. | Т | R | I | С | A | L |  |

|---|---|---|----|---|---|---|---|---|---|--|

|   |   |   |    |   |   |   |   |   |   |  |

| Operating current              | 4 A at 120 Vac<br>2 A at 240 Vac                |

|--------------------------------|-------------------------------------------------|

| Interface (controller) current | 1.5 A at +5 Vdc                                 |

| Power Consumption              | 500 Watts                                       |

| Heat dissipation               | 1700 Btus/hr                                    |

| Operating voltage              | 120 Vac ± 10%<br>240 Vac ± 10%                  |

| Phase                          | 1-Phase                                         |

| Line frequency                 | 60 Hz ± 0.5 Hz<br>50 Hz ± 0.5 Hz                |

| Receptacles                    | NEMA #5-15R (120 Vac), NEMA<br>#6-15R (240 Vac) |

| Line cord length               | 9 ft                                            |

|                                |                                                 |

### ENVIRONMENTAL

| Operating temperature | 59°F–90°F (15°C–32°C)    |

|-----------------------|--------------------------|

| Storage temperature   | -40°F-151°F (-40°C-66°C) |

| Operating relative humidity  | 20%–80%<br>(non-condensing)       |

|------------------------------|-----------------------------------|

| Storage relative humidity    | 5%–98%<br>(non-condensing)        |

| Maximum wet bulb temperature | 78°F (26°C)                       |

| Maximum operating altitude   | 8,000 ft (2440 m) above sea level |

~

### DISK DRIVES

RL01/02

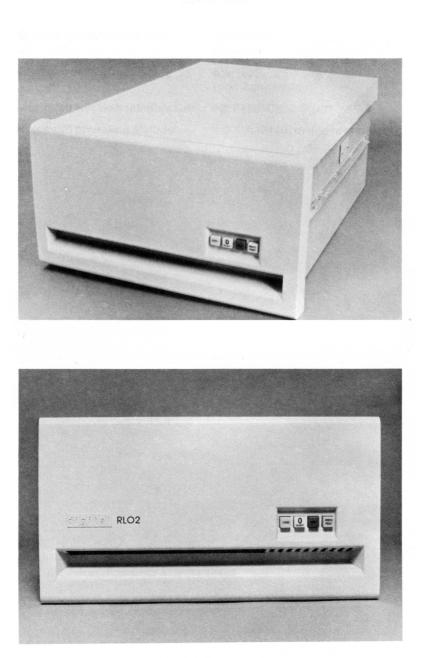

### RL01/02

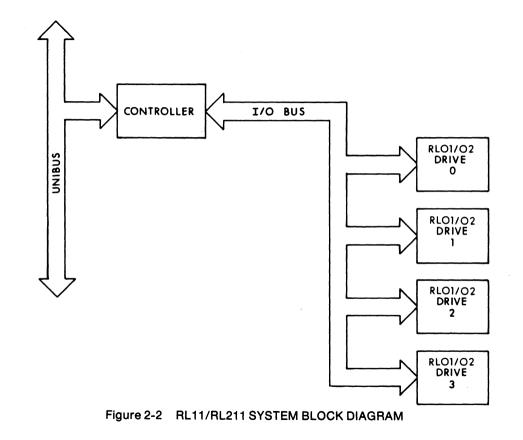

The RL01/02 is a random-access, cartridge disk storage system which connects to the UNIBUS via the controller. The RL11-AK and RL211-AK subsystems are supported by UNIBUS PDP-11 systems. VAX-11/750 systems also support the RL211-AK subsytems, but only as a data file resident device for transport of data to and from other DIGITAL systems. The RL01/02 was designed to operate at medium speeds in moderate usage environments in a wide range of commercial, engineering, laboratory, educational, and even some industrial and military applications.

### FEATURES

- Formatted capacity of 10.4 MB (RL02) and 5.2 MB (RL01)

- Removable disk cartridge provides unlimited off-line storage

- Overlapped seeks optimize seek time and provide increased system throughput on multidrive systems

- Direct Memory Access (DMA) data transfers

- Expandable up to a total of 4 disk drives per subsystem

### DESCRIPTION

The RL11-AK subsystem consists of a toploading, RL01 cartridge disk drive, a controller, an I/O cable, and a disk cartridge. Up to three more add-on RL01-AK cartridge disk drives may be added to this subsystem. Each processor will support a maximum of two controllers. The RL211-AK subsystem consists of a toploading, RL02 cartridge disk drive, a controller, an I/O cable, and a disk cartridge. Up to three more add-on RL02-AK cartridge disk drives may be added to this subsystem. Each processor will support a maximum of two controllers.

### **RECORDING METHOD**

The RL01/02 utilizes Modified Frequency Modulation (MFM) to read and write data. Data is written on the disk by magnetizing small sections (bit cells) of the oxide on the disk in different directions, i.e. either positively or negatively. A change in the direction of magnetization (flux transition) in the clock area or the data area of a bit cell indicates whether the bit represented is a 1 or a 0.

### DATA ORGANIZATION

The RL01/02 disk cartridge consists of one disk platter, recorded on both sides, enclosed in a protective case. The RL01/02 has 2 heads which correspond to the 2 data surfaces. The RL02 disk cartridge is divided into 512 cylinders (256 for the RL01). Each cylinder is divided into 2 tracks, corresponding to the 2 data surfaces. Each track is divided into 40 sectors with a data storage capacity of 2048 bits (256

-16-

bytes). Each sector is divided into a servo field, a header field, and a data field. The header field consists of a 16-bit header that contains the cylinder, track, and sector addresses and a 16-bit header CRC (Cyclic Redundancy Check). The data field consists of 2048 bits (256 bytes) of data and a 16-bit data CRC. The sector field and the header field are permanently recorded and can not be rewritten by the disk drive.

### OPERATION

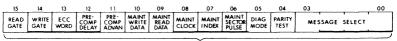

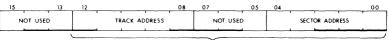

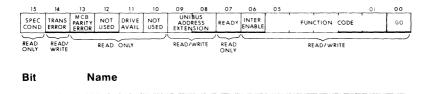

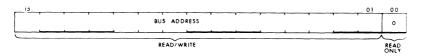

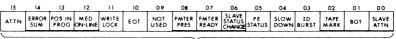

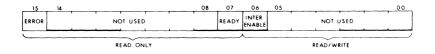

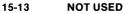

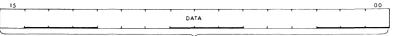

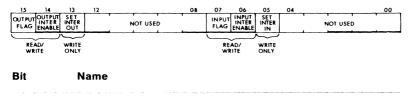

The RL11/RL211 subsystems have the following four registers: the Control and Status Register, the Bus Address Register, the Disk Address Register, and the Multipurpose Register. (Refer to the register section at the back of this book for register diagrams and bit definitions.)

Before a READ or a WRITE operation can begin, the processor must issue a SEEK command unless the heads are already positioned at the desired cylinder. To initiate a SEEK command, the processor loads the disk address register with the number of cylinders the heads are to be moved, the direction they are to be moved (toward or away from the spindle), and the head to be used (track 0 or 1). The control and status register is then loaded to select the drive number (0-3) and specify the SEEK command. The drive moves the heads the number of cylinders specified and generates an interrupt when the SEEK operation has been completed.

Once the heads are positioned at the desired cylinder, the processor loads the multipurpose, bus address, and disk address registers respectively. The multipurpose register specifies the number of words to be transferred between the disk and memory. The bus address register specifies the starting memory address of the location for the data to be read from or written onto the disk. The disk address register specifies the sector of the disk to be read or written.

After the multipurpose, bus address, and disk address registers have been loaded, the control and status register is loaded to specify the drive number (0-3) and whether this is to be a READ or WRITE operation. The READ or WRITE command is then executed. The specified head then reads the sector header fields to locate the specified sector on the rotating disk.

During a READ operation, data bits are read from the disk serially. The controller assembles the bits into 16-bit parallel words and generates a parity bit for each 16-bit word. The controller then transfers each 16-bit word plus parity to the specified memory location. This process continues until the specified number of words is reached or until the

end of the current track, whichever comes first. When the READ operation has been completed, an interrupt is generated to alert the processor that the data has been read off the disk and is stored in the specified memory location.

During a WRITE operation, the controller reads each 16-bit parallel word from the specified memory location and generates a parity bit for each 16-bit word. The controller then transfers each 16-bit word plus parity to the drive. The drive serially writes the bits onto the disk. This process continues until the specified number of words is reached or until the end of the current track, whichever comes first. When the WRITE operation has been completed, an interrupt is generated to alert the processor that the data has been written onto the disk.

### **DATA INTEGRITY**

Several error checking and correction features of the RL01/02 ensure that the data is correct.

During a data transfer operation, the RL01/02 reads the sector header field to verify that it has reached the specified cylinder, track, and sector. The header CRC is used to ensure that the header field has been read correctly. The header bits are used to generate a second CRC, which is then compared to the CRC read from the end of the header field on the disk. If there is a discrepancy between the two CRCs, the controller alerts the processor by setting a bit in the control and status register.

The data CRC is used to ensure that the data field has been read correctly. The data bits are used to generate a second CRC, which is then compared to the CRC read from the end of the data field on the disk. If there is a discrepancy between the two CRCs, the controller alerts the processor by setting a bit in the control and status register. If a sector contains an error, the processor issues a RETRY command.

To ensure that data is written correctly, a WRITE CHECK command may be issued by the software. This causes the RL01/02 to read the data just written and the RL01/02 controller to compare it to the data stored in memory.

### INTERRUPTS

The RL01/02 disk system controller uses a vectored interrupt to cause the program to branch to an interrupt service routine. An interrupt can occur only if the INTERRUPT ENABLE bit in the control and status register is set. Once the INTERRUPT ENABLE bit is set, an interrupt request is generated whenever either the CONTROLLER READY or DRIVE READY bit in the control and status register is also set. When the COMPOSITE ERROR bit is set in addition to the DRIVE READY bit, it indicates that some error or unusual condition exists and an interrupt is generated to cause the program to branch to an error handling routine. When the CONTROLLER READY bit is set, the controller has successfully completed the operation and is ready to accept a command. An interrupt request is made so that the program can branch to an interrupt service routine.

The interrupt priority level is 5 and the interrupt vector address is 160. Note that the priority level can be changed with a priority plug and the vector address can be changed by jumpers in the interrupt control logic. However, any DIGITAL programs or other software referring to the priority level or interrupt vector address must also be changed if the priority plug or the vector address is changed.

### **RELIABILITY/MAINTAINABILITY**

Reliability means long life expectancy and uninterrupted processing of the disk system. Special design features of the RL01/02 disk systems provide these qualities of high reliability as well as ease of maintenance.

- Modular construction of the RL01/02 enables parts to be quickly removed and replaced during routine servicing and maintenance.

- Easy access from the top of the drive to the subassemblies and heads.

- Track-following embedded servo system minimizes maintenance by eliminating drive head alignment.

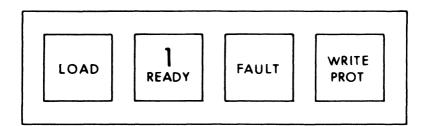

## Figure 2-3 RL01/02 FRONT PANEL CONTROLS AND INDICATORS

### PANEL CONTROLS AND INDICATORS

The front panel controls allow the operator to control the disk drive manually. The indicator lights provide drive status information.

• LOAD switch (alternate-action pushbutton/white light indicator on front panel)

Depressing this switch causes the indicator light to go out and the drive to accelerate the disk up to speed. Once the disk is up to speed, the READY indicator will light. Depressing the switch again causes the drive to stop the disk and the LOAD indicator to light.

DRIVE NUMBER receptacle/READY indicator (unlabeled receptacle/white light indicator on front panel)

Each drive comes with four numbered (0-3) plugs. The drive number is set by inserting one of the numbered plugs into the receptacle. If no plug is in the receptacle, the drive cannot be selected by the processor. Note that drive number units cannot be duplicated. When lit, the disk is up to speed and the drive is ready to execute a command.

• FAULT indicator (white light indicator on front panel)

When lit, the drive has detected a hardware fault such as write current failure or loss of system clock.

WRITE PROTECT switch (alternate-action pushbutton/white light indicator on front panel)

Depressing this switch causes the indicator to light and prevents the processor from writing on the disk cartridge. Depressing this switch again causes the indicator light to go out and enables WRITE operations.

### SPECIFICATIONS

### MECHANICAL

| Cabinet                  | Cabinet-mountable |

|--------------------------|-------------------|

| Controller mounting code | One hex slot      |

| Height                   | 10.5 in (26.7 cm) |

| Width                    | 19 in (48.3 cm)   |

| Depth                    | 25 in (63.5 cm)   |

| Weight                   | 75 lbs (33.8 kg)  |

|                          |                   |

| PERFORMANCE<br>Drives per controller                     | 4                                    |

|----------------------------------------------------------|--------------------------------------|

| Form <b>atted capacity per disk</b><br>cartri <b>dge</b> |                                      |

| RL01                                                     | 5.2 MB                               |

| RL02                                                     | 10.4 MB                              |

| Peak transfer speed                                      | 512 KB/s                             |

| Average access time*                                     | 67.5 ms                              |

| Average seek time                                        | 55 ms                                |

| Average latency (rotational)<br>time                     | 12.5 ms                              |

| Track-to-track seek                                      | 15 ms                                |

| Rotational Speed                                         | 2400 rpm                             |

| Surfaces per disk cartridge                              | 2                                    |

| Tracks per surface                                       |                                      |

| RL01                                                     | 256                                  |

| RL02                                                     | 512                                  |

| Sectors per track                                        | 40                                   |

| Bytes per sector                                         | 256                                  |

| Tracks per inch                                          | 250                                  |

| Bits per inch                                            | 3725                                 |

| ELECTRICAL                                               |                                      |

| Starting (surge) current                                 | 5 A at 120 Vac<br>2.5 A at 240 Vac   |

| Surge duration                                           | 10 s                                 |

| Operating current                                        | 1.5 A at 120 Vac<br>0.8 A at 240 Vac |

\* Average access time is defined as the sum of the average seek time and the average latency (rotational) time.

| Controller (Interface) current | 5 A at 5 Vdc,<br>0.5 A at + 15 Vdc,<br>0.5 A at -15 Vdc |

|--------------------------------|---------------------------------------------------------|

| Power consumption              | 150 Watts                                               |

| Heat dissipation               | 600 Btus/hr                                             |

| Operating voltage              | 120 Vac ± 10%<br>240 Vac ± 10%                          |

| Phase                          | 1-Phase                                                 |

| Line frequency                 | 60 Hz ± 3 Hz<br>50 Hz ± 2.5 Hz                          |

| Receptacles                    | NEMA #5-15R (120 Vac), NEMA<br>#6-15R (240 Vac)         |

| Line cord length               | 10 ft (3 m)                                             |

| ENVIRONMENTAL<br>Operating temperature | 50°F-104°F (10°C-40°C)           |

|----------------------------------------|----------------------------------|

| Storage temperature                    | -40°F–151°F (-40°C–66°C)         |

| Operating relative humidity            | 10%–90%<br>(non-condensing)      |

| Storage relative humidity              | 10%–95%<br>(non-condensing)      |

| Maximum wet bulb temperature           | 82°F (28°C)                      |

| Maximum operating altitude             | 8000 ft (2440 m) above sea level |

|                                        |                                  |

### DISK DRIVES

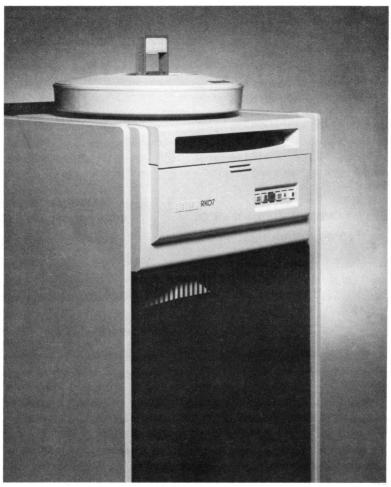

RK07

### R**K07**

The RK07 is a freestanding, random-access, disk storage system which connects to the UNIBUS via the controller. The RK711 subsystems are supported by UNIBUS PDP-11 systems and VAX-11/780 systems. The RK07 was designed to operate at medium speeds in moderate usage environments in a variety of commercial and scientific applications.

### FEATURES

- Formatted capacity of 28 MB

- Removable disk cartridge provides unlimited off-line storage

- Overlapped seeks optimize seek time and provide increased system throughput on multidrive systems

- Static dual-access capability

- Direct Memory Access (DMA) data transfers

- Expandable up to a total of 8 disk drives per subsystem

### DESCRIPTION

The RK711-EA(ED) and RK711-PA(PD) disk storage subsystems consist of a single-access, freestanding RK07 disk drive, a controller, an I/O cable, and a disk cartridge. Up to seven more add-on RK07 drives (single- or dual-access) may be added to these subsystems. The RK711-EA(ED) subsystems and the RK07-EA(ED) add-on drives are compatible with UNIBUS PDP-11 and VAX-11/780 systems configured in H960 and H9600 series cabinets. The RK711-PA(PD) subsytems and the RK07-PA(PD) add-on drives are compatible with UNIBUS PDP-11 systems configured in H9640 series cabinets. The RK07-PA(PD) add-on drive may also be added to VAX-11/750 systems confiugred with an RK711 subsystem.

The RK711-FA(FD) disk storage subsystems consist of a dual-access, freestanding RK07 disk drive, two UNIBUS controllers, two I/O cables, and a disk cartridge. Up to seven more add-on RK07 disk drives (single- or dual-access) may be added to these subsystems. The RK711-FA(FD) subsystems and the RK07-FA(FD) add-on drives are compatible with UNIBUS PDP-11 and VAX-11/780 systems configured in H960 and H9600 series cabinets. Note that dynamic (simultaneous access) dual-port capability of disk subsystems is not supported by DIGITAL operating system software or diagnostics. However, the RK711-FA(FD) subsystems can be statically shared by two processors or connected to one processor through two UNIBUS controllers for maximum system availability.

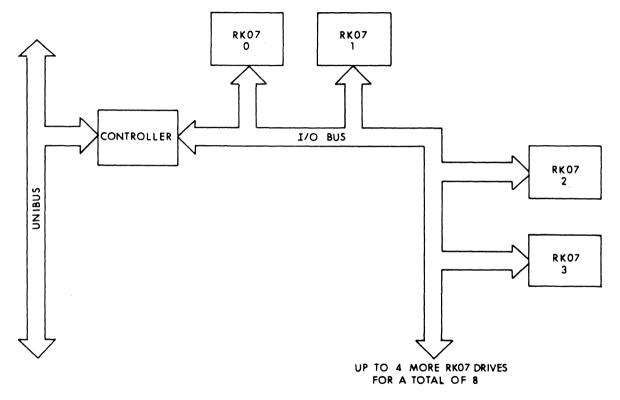

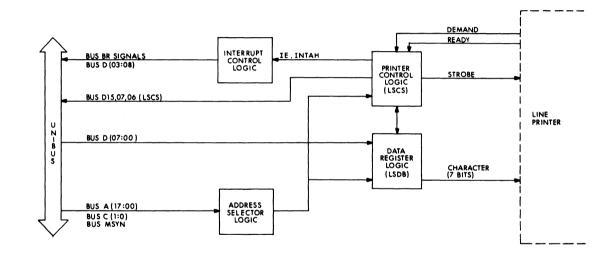

Figure 2-4 RK711 SYSTEM BLOCK DIAGRAM

### **RECORDING METHOD**

The RK07 utilizes Modified Frequency Modulation (MFM) to read and write data. Data is written on the disk by magnetizing small sections (bit cells) of the oxide on the disk in different directions, i.e. either positively or negatively. A change in the direction of magnetization (flux transition) clock area or the data area of a bit cell indicates whether the bit represented is a 1 or a 0.

### DATA ORGANIZATION

The RK07 disk cartridge consists of 2 disk platters, each recorded on both sides, enclosed in a protective cover. Each disk cartridge contains a total of 4 surfaces: 3 data surfaces for recording and 1 servo surface permanently recorded with information used to position the read/write heads at the specified cylinder. The RK07 has 4 heads-3 are read/write heads which correspond to the 3 data surfaces and the additional head is the servo read head, which corresponds to the servo surface. The disk cartridge is divided into 815 cylinders. Each cylinder is divided into 3 tracks, corresponding to the 3 data surfaces. Each track is divided into 22 sectors with a data storage capacity of 4096 bits (512 bytes). Each sector is divided into a preamble, a header field, and a data field. The header field consists of a 32-bit header that contains the cylinder, track, and sector addresses and a 16-bit header check word. The data field consists of 4096 bits (512 bytes) of data and a 32-bit data ECC (Error Correcting Code). The preamble and the header field can only be written by the utility program that formats these disk cartridges.

### OPERATION

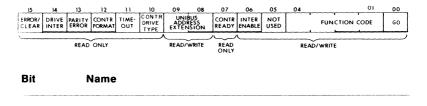

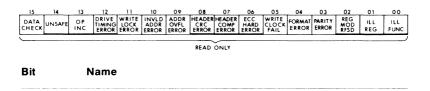

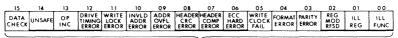

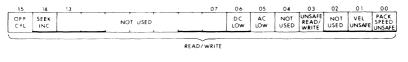

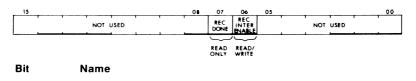

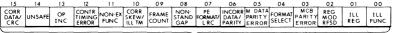

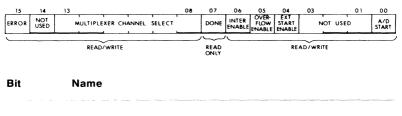

The RK711 subsystems have 15 registers. (Refer to the register section at the back of this book for register diagrams and bit definitions).

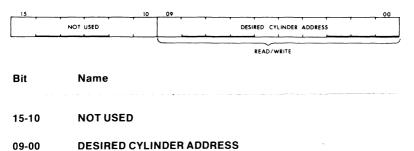

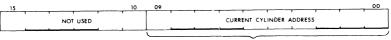

Before a READ or a WRITE operation can begin, the processor loads the bus address, word count, control and status 2, desired cylinder, disk address, and control and status 1 registers respectively.

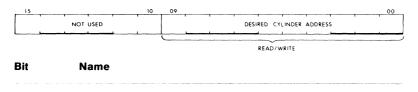

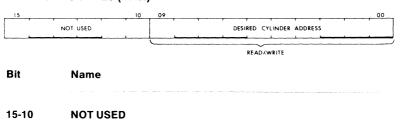

The bus address register specifies the starting memory address of the location for the data to be read from or written onto the disk. The word count register specifies the number of words to be transferred between the disk and memory. The control and status 2 register selects which of the disk drives (up to 8 per controller) is to perform the operation. The desired cylinder register and the disk address register specify the sector of the disk to be read or written.

After the bus address, word count, control and status 2, desired cylinder, and disk address registers have been loaded, the control and status 1 register is loaded with the READ or WRITE command from the

processor. The command is then executed. If the heads are not currently positioned at the specified cylinder, the drive will do an implied SEEK, which moves the heads to the correct cylinder. The read/write data heads then begin reading the headers on the specified track to locate the specified sector.

During a READ operation, data bits are read from the disk serially. The controller assembles the bits into 16-bit parallel words and generates a parity bit for each 16-bit word. The controller then transfers each 16-bit word plus parity to the specified memory location. This process continues until the proper word count is reached. When the READ operation has been completed, an interrupt is generated to alert the processor that the data has been read off the disk and is stored in the specified memory location.

During a WRITE operation, the controller reads each 16-bit parallel word from the specified memory location and generates a parity bit for each 16-bit word. The controller then transfers each 16-bit word plus parity to the drive. The drive serially writes the bits onto the disk. This process continues until the proper word count is reached. When the WRITE operation has been completed, an interrupt is generated to alert the processor that the data has been written onto the disk.

### DATA INTEGRITY

Several error checking and correction features of the RK07 ensure that the data is correct.

The RK07 uses the servo disk surface to position the read/write heads at the specified cylinder. The sector header field is read to verify that it is the specified cylinder, track, and sector. The header check word is used to ensure that the header field has been read correctly. The header bits are used to generate a second header check word, which is then compared to the word read from the end of the header field on the disk. If there is a discrepancy between the two header check words, the controller alerts the processor by setting a bit in the error register.

To ensure that data is written correctly, a WRITE CHECK command may be issued by the software. This causes the RK07 to read the data just written and the RK07 controller to compare it to the data stored in memory.

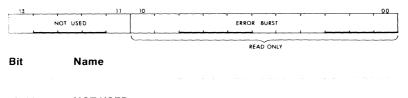

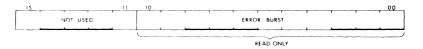

The ECC (Error Correction Code) logic is used to ensure that the data field has been read correctly. The data bits are used to generate a second ECC, which is then compared to the ECC read from the end of the data field on the disk. If there is a discrepancy between the two ECCs, the processor uses them to determine which bits are in error

and to reconstruct the correct data. One error of up to 11 incorrect bits in a row can be reconstructed in a sector. The controller reports the position of the error to the processor and sends the processor an error burst pattern and an error correction pattern to allow the software to correct the error in memory. If a sector containing more than one error is reported to the processor by the controller as an incorrectable error, the processor may invoke a suitable error recovery procedure consisting of OFFSET positioning, RECALIBRATION, and REREAD operations.

### INTERRUPTS

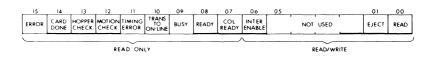

The RK07 disk system controller uses a vectored interrupt to cause the program to branch to an interrupt service routine. An interrupt can occur only if the INTERRUPT ENABLE bit in the control and status 1 register is set. Once the INTERRUPT ENABLE bit is set, an interrupt request is generated whenever either the COMBINED ERROR, DRIVE INTERRUPT, or CONTROLLER READY bit in the control and status 1 register is also set.

When the COMBINED ERROR or DRIVE INTERRUPT bits are set, they indicate that some error or unusual condition exists and an interrupt is generated to cause the program to branch to an error handling routine. When the READY bit is set, the controller has successfully completed the operation and is ready to accept a command. An interrupt request is made so that the program can branch to an interrupt service routine.

The interrupt priority level is 5 and the interrupt vector address is 210. Note that the priority level can be changed with a priority plug and the vector address can be changed by switches in the interrupt control logic. However, any DIGITAL programs or other software referring to the priority level or interrupt vector address must also be changed if the priority plug or the vector address is changed.

### RELIABILITY/MAINTAINABILITY

Reliability means long life expectancy and uninterrupted processing of the disk system. Special design features of the RK07 disk systems provide these qualities of high reliability as well as ease of maintenance.

- Modular construction and easy access to the subassemblies and heads of the RK07 enables parts to be quickly removed and replaced during routine servicing and maintenance.

- Off-line tester allows the RK07 to be serviced independent of the host processor.

- Light-emitting diodes on key status bits permit fast, easy error diagnosis and repair.

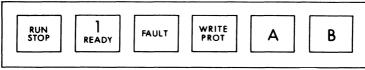

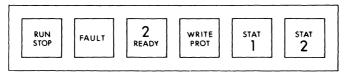

Figure 2-5 RK07 FRONT PANEL CONTROLS AND INDICATORS

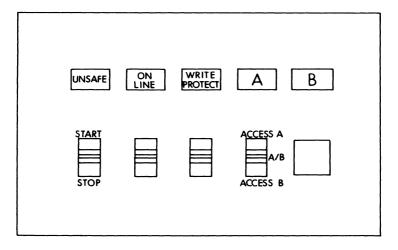

### PANEL CONTROLS AND INDICATORS

The front panel controls allow the operator to control the disk drive manually. The indicator lights provide drive status information.

RUN/STOP switch (alternate-action pushbutton/yellow light indicator on front panel)

Depressing this switch causes the indicator to light and the drive to accelerate the disk cartridge up to speed. Once the disk cartridge is up to speed, the READY indicator will light. Depressing the switch again causes the drive to stop the disk cartridge and the START indicator light to go out.

• DRIVE NUMBER receptacle/READY indicator (unlabeled receptacle/white light indicator on front panel)

Each drive comes with eight numbered (0-7) plugs. The drive number is set by inserting one of the numbered plugs into the receptacle. If no plug is in the receptacle, the drive cannot be selected by the processor. Note that drive number units cannot be duplicated.

When this READY indicator is lit, the disk cartridge is up to speed and the drive is ready to execute a command.

• FAULT indicator (red light indicator on front panel)

When lit, the drive has detected a hardware fault such as write current failure or a dc power supply failure.

• WRITE PROTECT switch (alternate-action pushbutton/yellow light indicator on front panel)

Depressing this switch causes the indicator to light and prevents the processor from writing on the disk cartridge. Depressing this switch again causes the indicator light to go out and enables WRITE operations.

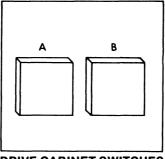

• A and B switches (alternate-action pushbuttons/white light indicators on front panel)

Depressing switch A enables port A. Depressing switch B enables port B. When both switches are depressed both ports are enabled. The A indicator lights when the drive is being accessed by port A and the B indicator lights when the drive is being accessed by port B.

| SPECIFICATIONS<br>MECHANICAL |                    |

|------------------------------|--------------------|

| Cabinet                      | Freestanding       |

| Controller mounting code     | 2 Sus              |

| Height                       |                    |

| RK07-EA(ED, RK07-FA(FD)      | 39 in (99 cm)      |

| RK07-PA(PD)                  | 41.75 in (106 cm)  |

| Width                        |                    |

| RK07-EA(ED), RK07-FA(FD)     | 21.7 in (55.2 cm)  |

| RK07-PA(PD)                  | 21.25 in (54.1 cm) |

| Depth                        |                    |

| RK07-EA(ED), RK07-FA(FD)     | 30 in (76.2 cm)    |

| RK07-PA(PD)                  | 30 in (76.2 cm)    |

| Weight                       |                    |

| RK07-EA(ED), RK07-FA(FD)     | 326 lbs (148 kg)   |

| RK07-PA(PD)                  | 339 lbs (153.9 kg) |

PERFORMANCE

| Drives per controller                 | 8               |

|---------------------------------------|-----------------|

| Formatted capacity per disk cartridge | 28 MB           |

| Peak transfer speed                   | 538 KB/s        |

| Average access time*                  | 49 ms           |

| Average seek time                     | 36.5 ms         |

| Average latency (rotational) time     | 12.5 ms         |

| Track-to-track seek                   | 6.5 ms          |

| Rotational Speed                      | 2400 rpm        |

| Surfaces per disk cartridge           | 3 data, 1 servo |

| Tracks per surface                    | 815             |

\* Average access time is defined as the sum of the average seek time and the average latency (rotational) time.

| Sectors per track              | 22 (16-bit format)                   |

|--------------------------------|--------------------------------------|

| Bytes per sector               | 512                                  |

| Tracks per inch                | 384                                  |

| Bits per inch                  | 4040                                 |

|                                |                                      |

|                                |                                      |

| ELECTRICAL                     |                                      |

| Operating current              | 4 A at 120 Vac<br>2 A at 120 Vac     |

| Controller (Interface) current | 12 A at 5 Vdc,                       |

|                                | 12  A at 5 Vdc,<br>.18 A at +15 Vdc, |

|                                | .40 A at -15 Vdc                     |

| Power Consumption              | 500 Watts maximum (60 Hz)            |

|                                | 550 Watts maximum (50 Hz)            |

| Heat dissipation               | 1700 Btus/hr maximum (60 Hz)         |

|                                | 1900 Btus/hr maximum (50 Hz)         |

| Operating voltage              | 120 Vac ± 10%<br>240 Vac ± 10%       |

| Phase                          | 1-Phase                              |

|                                | $60 \text{ Hz} \pm 3 \text{ Hz}$     |

| Line frequency                 | $50 \text{ Hz} \pm 3 \text{ Hz}$     |

| Receptacles                    | NEMA #5-15R (120 Vac), NEMA          |

|                                | #6-15R (240 Vac)                     |

| Line cord length               | 9 ft (2.7 m)                         |

|                                |                                      |

| ENVIRONMENTAL                  |                                      |

| Operating temperature          | 50°F-104°F (10°C-40°C)               |

| Storage temperature            | -40°F–151°F (-40°C–66°C)             |

| Operating relative humidity    | 10%-90%                              |

|                                | (non-condensing)                     |

| Storage relative humidity      | 10%-95%                              |

|                                | (non-condensing)                     |

| Maximum wet bulb temperature   | 82°F (28°C)                          |

| Maximum operating altitude     | 8000 ft (2440 m) above sea level     |

|                                |                                      |

•

# RM02/03

## RM02/03

The RM02/03 is a freestanding, random-access, disk storage system which connects to the processor via the MASSBUS controller/adapter. The RJM02 subsystems are supported by UNIBUS PDP-11 systems except the PDP-11/70, the RWM03 subsystems are supported by PDP-11/70 systems, the REM03 subsystems are supported by VAX-11/780 systems, and the RGM03 subsystems are supported by VAX-11/750 systems. The RM02/03 was designed to operate at high speeds in high usage environments in a variety of applications.

## FEATURES

- Formatted capacity of 67 MB

- Removable disk pack provides unlimited off-line storage

- Overlapped seeks optimize seek time and provide increased system throughput on multidrive systems

- Static dual-access capability

- Direct Memory Access (DMA) data transfers

- Expandable up to a total of 8 disk drives per subsystem

### DESCRIPTION

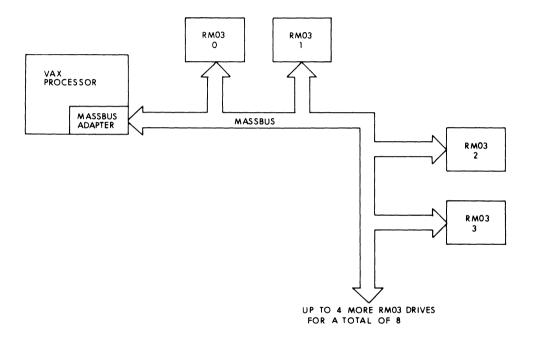

The RJM02-AA(AD) disk storage subsystems consist of a single-access, freestanding RM02 disk drive, a MASSBUS controller, a MASS-BUS cable, and a disk pack. Up to seven more add-on RM02 disk drives (single- or dual-access) may be added to these subsystems. The RWM03-AA(AD), REM03-AA(AD), and RGM03-AA(AD) disk storage subsystems consist of a single-access, freestanding RM03 disk drive, a MASSBUS controller/adapter, a MASSBUS cable, and a disk pack. Up to seven more add-on RM03 disk drives (single- or dual-access) may be added to these subsystems.

The RJM02-BA(BD) disk storage subsystems consist of a dual-access, freestanding RM02 disk drive, two MASSBUS controllers, two MASS-BUS cables, and a disk pack. Up to seven more add-on RM02 disk drives (single- or dual-access) may be added to these subsystems. The RWM03-BA(BD), REM03-BA(BD), and RGM03-BA(BD) disk storage subsystems consist of a dual-access, freestanding RM03 disk drive, two MASSBUS controllers/adapters, two MASSBUS cables, and a disk pack. Up to seven more add-on RM03 disk drives (singleor dual-access) may be added to these subsystems. Note that dynamic (simultaneous access) dual-port capability of disk subsystems is not supported by DIGITAL operating system software or diagnostics. However, the RJM02-BA(BD), RWM03-BA(BD), REM03-BA(BD), and the RGM03-BA(BD) subsystems can be statically shared by two processors or connected to one processor through two MASSBUS controllers/adapters for maximum system availability.

-36-

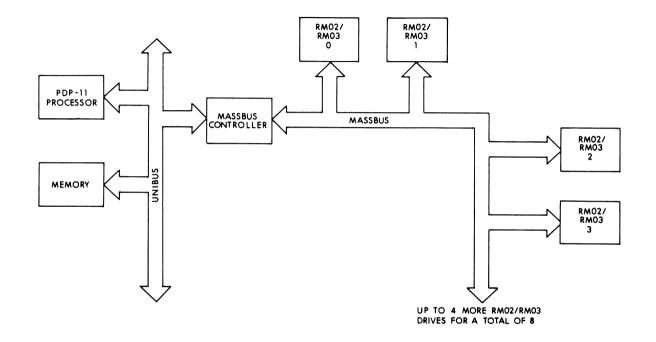

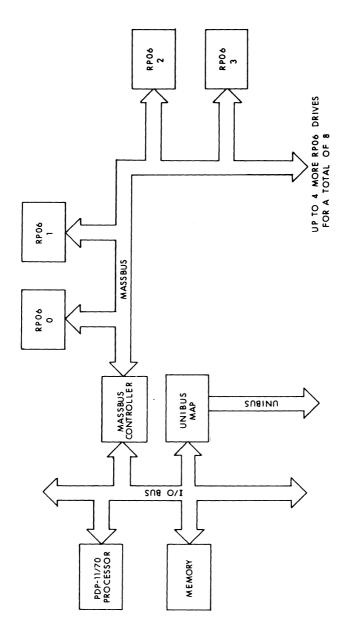

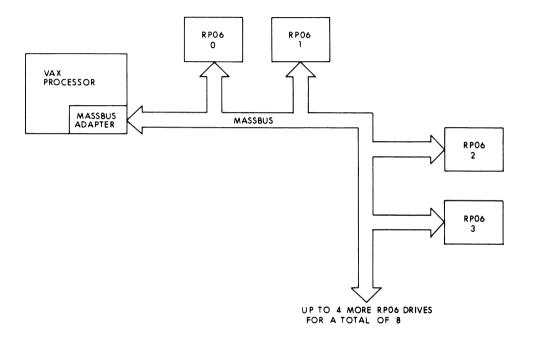

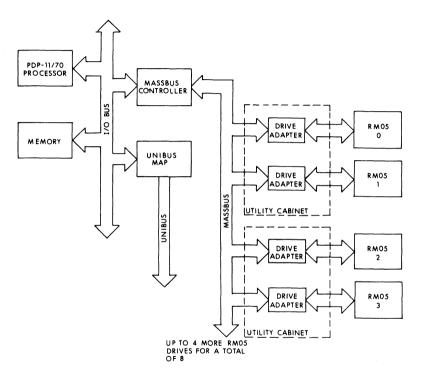

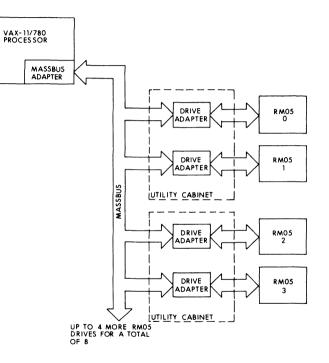

Figure 2-6 RJM02 SYSTEM BLOCK DIAGRAM

-37-

Figure 2-7 RWM03 SYSTEM BLOCK DIAGRAM

-38-

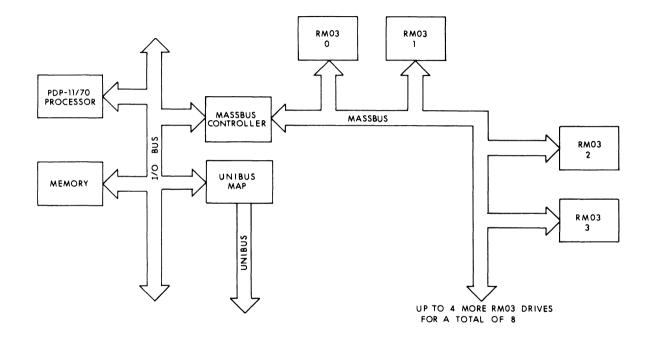

Figure 2-8 REM03/RGM03 SYSTEM BLOCK DIAGRAM

### **RECORDING METHOD**

The RM02/03 utilizes Modified Frequency Modulation (MFM) to read and write data. Data is written on the disk by magnetizing small sections (bit cells) of the oxide on the disk in different directions, i.e. either positively or negatively. A change in the direction of magnetization (flux transition) in the clock area of a bit cell indicates whether the bit represented is a 1 or a 0.

### DATA ORGANIZATION

The RM02/03 disk pack consists of 3 disk platters, each recorded on both sides, enclosed between two outside platters for protection of the pack. Each disk pack contains a total of 6 surfaces: 5 data surfaces for recording and 1 servo surface permanently recorded with information used to position the read/write heads at the specified cylinder. The RM02/03 has 6 heads-5 are read/write heads which correspond to the 5 data surfaces and the additional head is the servo read head. which corresponds to the servo surface. The disk pack is divided into 823 cylinders. Each cylinder is divided into 5 tracks, corresponding to the 5 data surfaces. Each track is divided into 32 sectors with a data storage capacity of 4096 bits (512 bytes). Each sector is divided into a header field and a data field. The header field consists of an 48-bit header that contains the cylinder, track, and sector addresses and a 16-bit header CRC (Cyclic Redundancy Check). The data field consists of 4096 bits (512 bytes) of data and a 32-bit data ECC (Error Correction Code). The preamble and the header field can only be written by the utility program that formats these disk packs.

### OPERATION

The RJM02 subsystems have 20 registers, the RWM03 subsystems have 22 registers, and the REM03 and RGM03 subsystems have 16 registers plus the MASSBUS adapter registers. (Refer to the register section at the back of this book for register diagrams and bit definitions).

Before a READ or a WRITE operation can begin, the processor loads the bus address, word count, control and status 2, desired cylinder, desired sector/track address, and control and status 1 registers respectively.

The bus address register specifies the starting memory address of the location for the data to be read from or written onto the disk. The word count register specifies the number of words to be transferred between the disk and memory. The control and status 2 register selects which of the disk drives (up to 8 per controller) is to perform the operation. The desired cylinder register and the desired sector/track address register specify the sector of the disk to be read or written.

After the bus address, word count, control and status 2, desired cylinder, and desired sector/track address registers have been loaded, the control and status 1 register is loaded with the READ or WRITE command from the processor. The command is then executed. If the heads are not currently positioned at the specified cylinder, the drive will do an implied SEEK, which moves the heads to the correct cylinder. The read/write heads then read the headers on the specified track to locate the specified sector.

During a READ operation, data bits are read from the disk serially. The controller/adapter assembles the bits into 16-bit parallel words and generates a parity bit for each 16-bit word. The controller/adapter then transfers each 16-bit word plus parity to the specified memory location. This process continues until the proper word count is reached. When the READ operation has been completed, an interrupt is generated to alert the processor that the data has been read off the disk and is stored in the specified memory location.

During a WRITE operation, the controller/adapter reads each 16-bit parallel word from the specified memory location and generates a parity bit for each. The controller/adapter transfers each 16-bit word plus parity to the drive. The drive then serially writes the bits onto the disk. This process continues until the proper word count is reached. When the WRITE operation has been completed, an interrupt is generated to alert the processor that the data has been written onto the disk.

#### DATA INTEGRITY

Several error checking and correction features of the RM02/03 ensure that the data is correct.

The RM02/03 uses the servo disk surface to position the read/write heads at the specified cylinder. The sector header field is read to verify that it is the specified cylinder, track, and sector. The header CRC is used to ensure that the header field has been read correctly. The header bits are used to generate a second CRC, which is then compared to the CRC read from the end of the header field on the disk. If there is a discrepancy between the two CRCs, the controller/adapter alerts the processor by setting a bit in the error 1 register.

To ensure that data is written correctly, a WRITE CHECK command may be issued by the software. This causes the RM02/03 to read the data just written and the controller/adapter to compare it to the data stored in memory.

The ECC (Error Correction Code) logic is used to ensure that the data field has been read correctly. The data bits are used to generate a second ECC, which is then compared to the ECC read from the end of

the data field on the disk. If there is a discrepancy between the two ECCs, the processor uses them to determine which bits are in error and to reconstruct the correct data. One error of up to 11 incorrect bits in a row can be reconstructed in a sector. The controller/adapter reports the position of the error to the processor and sends the processor an error burst pattern and an error correction pattern to allow the software to correct the error in memory. If a sector containing more than one error is reported to the processor by the controll-er/adapter as an incorrectable error, the processor may invoke a suitable error recovery procedure consisting of OFFSET positioning, RECALIBRATION, and REREAD operations.

### INTERRUPTS

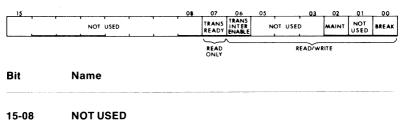

The RM02/03 disk system controller/adapter uses a vectored interrupt to cause the program to branch to an interrupt service routine. An interrupt can occur only if the INTERRUPT ENABLE bit in the control and status 1 register is set. Once the INTERRUPT ENABLE bit is set, an interrupt request is generated whenever either the SPECIAL CON-DITION or READY bit in the control and status 1 register is also set.

When the SPECIAL CONDITION bit is set, it indicates that some error or unusual condition exists and an interrupt is generated to cause the program to branch to an error handling routine. When the READY bit is set, the controller/adapter has successfully completed the operation and is ready to accept a command. An interrupt request is made so that the program can branch to an interrupt service routine.

The interrupt priority level is 5 and the interrupt vector address is 254. Note that the priority level can be changed with a priority plug and the vector address can be changed by jumpers in the interrupt control logic. However, any DIGITAL programs or other software referring to the priority level or interrupt vector address must also be changed if the priority plug or the vector address is changed.

### RELIABILITY/MAINTAINABILITY

Reliability means long life expectancy and uninterrupted processing of the disk system. Special design features of the RM02/03 disk systems provide these qualities of high reliability as well as ease of maintenance.

- Modular construction of the RM02/03 enables parts to be quickly removed and replaced during routine servicing and maintenance.

- Off-line tester allows the RM02/03 to be serviced independent of the host processor.

- Fault-isolation diagnostics simplify troubleshooting and provide extended maintenance and serviceability.

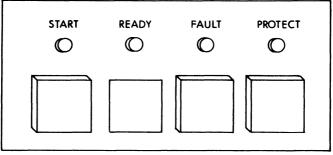

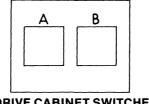

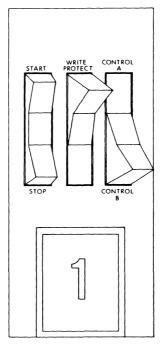

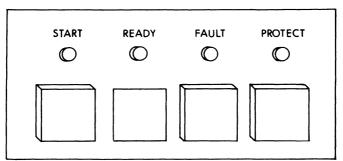

FRONT PANEL CONTROLS AND INDICATORS

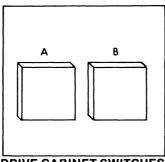

DRIVE CABINET SWITCHES

## CONTROLS AND INDICATORS

The front panel controls allow the operator to control the disk drive manually and the indicator lights provide drive status information. The A and B swtiches located on the drive cabinet door allow the operator to enable different MASSBUS ports.

• START switch and associated lamp (alternate-action pushbutton and associated red light indicator on front panel)

Depressing this switch causes the START indicator light to come on and the drive to accelerate the disk pack up to speed. Once the disk pack is up to speed, the READY indicator will light. Depressing the switch again causes the drive to stop the disk pack and the START indicator light to go out.

• READY lamp (red light indicator on front panel)

When lit, indicates that the disk pack is up to speed and the drive is ready to execute a command. This lamp will blink during start/stop sequences.

• DRIVE NUMBER receptacle (unlabeled receptacle on front panel)

Each drive comes with eight numbered (0-7) plugs. The drive number is set by inserting one of the numbered plugs into the receptacle. If no plug is in the receptacle, the drive cannot be selected by the processor. Note that drive number units cannot be duplicated.

• FAULT CLEAR switch and associated lamp (momentary pushbutton and associated red light indicator on front panel)

Depressing this switch causes the indicator light to go out if the fault condition has been corrected.

When lit, the drive has detected a hardware fault such as write current failure or a dc power supply failure.

• WRITE PROTECT switch and associated lamp (alternate-action pushbutton and associated red light indicator on front panel)

Depressing this switch causes the associated indicator to light and prevents the processor from writing on the disk pack. Depressing this switch again causes the indicator light to go out and enables WRITE operations.

• A and B switches/lamps (alternate-action pushbuttons/red light indicators on drive cabinet door)

Depressing the A switch enables MASSBUS port A. Depressing the B switch enables MASSBUS port B. When both switches are depressed or when neither switch is depressed, both MASSBUS ports are enabled.

The A indicator lights when the drive is being accessed by MASS-BUS port A and the B indicator lights when the drive is being accessed by MASSBUS port B.

### SPECIFICATIONS

| MECHANICAL<br>Cabinet            | Freestanding       |

|----------------------------------|--------------------|

| Controller/adapter mounting code |                    |

| RJM02                            | 2 SUs              |

| RWM03                            | MASSBUS port       |

| REM03                            | Option panel space |

| RGM03                            | MBA slot           |

| Height                           | 39 in (99 cm)      |

| Width                            | 21.7 in (55.1 cm)  |

| Depth                            | 31 in (79 cm)      |

| Weight                           | 430 lbs (195 kg)   |

### PERFORMANCE

| Drives per controller/adapter        | 8         |

|--------------------------------------|-----------|

| Formatted capacity per disk<br>pack  | 67 MB     |

| Peak transfer speed                  |           |

| RM02                                 | 806 KB/s  |

| RM03                                 | 1200 KB/s |

| Average access time*                 |           |

| RM02                                 | 42.5 ms   |

| RM03                                 | 38.3 ms   |

| Average seek time                    | 30 ms     |

| Average latency (rotational)<br>time |           |

| RM02                                 | 12.5 ms   |

\* Average access time is defined as the sum of the average seek time and the average latency (rotational) time.

| R <b>M03</b>           | 8.3 ms             |

|------------------------|--------------------|

| Track-to-track seek    | 6 ms               |

| Rotational speed       |                    |

| R <b>M02</b>           | 2400 rpm           |

| R <b>M03</b>           | 3600 rpm           |

| Surfaces per disk pack | 5 data, 1 servo    |

| Tracks per surface     | 823                |

| Sectors per track      | 32 (16-bit format) |

| Bytes per sector       | 512                |

| Tracks per inch        | 384                |

| Bits per inch          | 6038               |

| ELECTRICAL<br>Starting (surge) current | 30 A at 120 Vac<br>22 A at 240 Vac              |

|----------------------------------------|-------------------------------------------------|

| Surge duration                         | 10-12 s                                         |

| Drive operating current                | 11 A at 120 Vac<br>5.3 A at 240 Vac             |

| Power consumption                      | 1050 Watts maximum                              |

| Heat dissipation                       | 4128 Btus/hr maximum                            |

| Drive operating voltage                | 120 Vac +8, -18<br>240 Vac +17, -27             |

| Phase                                  | 1-phase                                         |

| Line frequency                         | 60 Hz +0.6, -1<br>50 Hz +0.5, -1                |

| Drive receptacles                      | NEMA #5-15R (120 Vac), NEMA<br>#6-15R (240 Vac) |

| Line cord length                       | 6 ft                                            |

| ENVIRONMENTAL                          |                                                 |

| Operating temperature | 59°F–90°F (15°C–32°C)    |

|-----------------------|--------------------------|

| Storage temperature   | -40°F–158°F (-40°C–70°C) |

| Operating relative humidity  | 20%–80%<br>(non-conđensing)      |

|------------------------------|----------------------------------|

| Storage relative humidity    | 5%—95%<br>(non-condensing)       |

| Maximum wet bulb temperature | 78°F (26°C)                      |

| Maximum operating altitude   | 6500 ft (2000 m) above sea level |

**RM80**

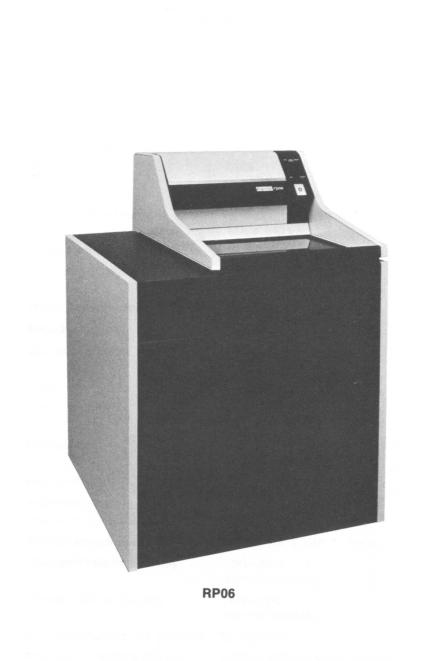

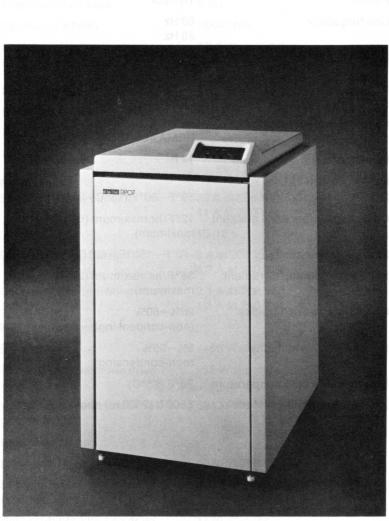

#### RM80

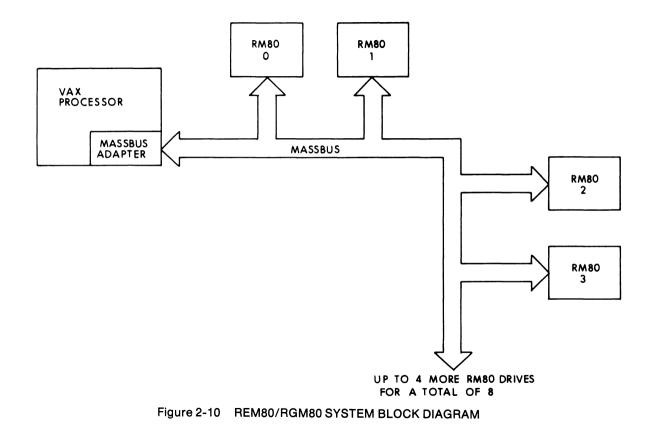

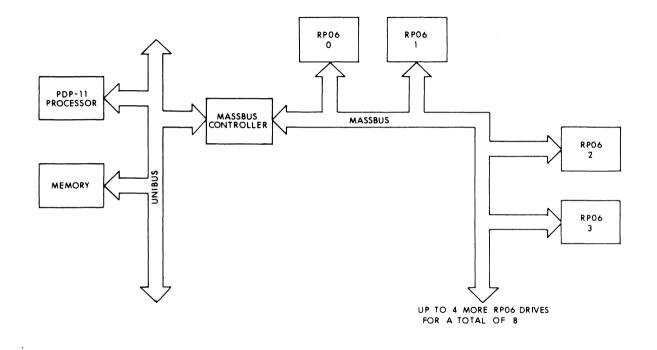

The RM80 is a freestanding, random-access, disk storage system which connects to the processor via the MASSBUS adapter (MBA). The REM80 subsystems are supported by VAX-11/780 systems and the RGM80 subsystems are supported by VAX-11/750 systems. The RM80 was designed to operate at very high speeds in high usage environments in a wide range of applications.

#### FEATURES

- Formatted capacity of 124 MB

- Winchester fixed-media technology

- Sealed Head Disk Assembly (HDA)

- Internal microprocessor-controlled diagnostics

- Overlapped seeks optimize seek time and provide increased system throughput on multidrive systems

- Static dual-access capability

- Direct Memory Access (DMA) data transfers

- Expandable up to a total of 8 disk drives per subsystem

### DESCRIPTION

The REM80-AA(AD) and RGM80-AA(AD) disk storage subsystems consist of a single-access, freestanding RM80 disk drive with nonremovable head disk assembly, a MASSBUS adapter (MBA), and a MASSBUS cable. Up to seven more add-on RM80 disk drives (singleor dual-access) may be added to these subsystems.

The REM80-BA(BD) and RGM80-BA(BD) disk storage subsystems consist of a dual-access, freestanding RM80 disk drive with non-removable head disk assembly, two MASSBUS adapters (MBAs), and two MASSBUS cables. Up to seven more add-on RM80 disk drives (single- or dual-access) may be added to these subsystems. Note that dynamic (simultaneous access) dual-port capability of disk subsystems is not supported by DIGITAL operating system software or diagnostics. However, the REM80-BA(BD) and RGM80-BA(BD) subsystems can be statically shared by two processors or connected to one processor through two MBAs for maximum system availability.

#### **RECORDING METHOD**

The RM80 utilizes Modified Frequency Modulation (MFM) to read and write data. Data is written on the disk by magnetizing small sections (bit cells) of the oxide on the disk in different directions, i.e. either positively or negatively. A change in the direction of magnetization (flux transition) in the clock area of a bit cell indicates whether the bit represented is a 1 or a 0.

#### DATA ORGANIZATION

The RM80 head disk assembly consists of 4 disk platters, each recorded on both sides. Each head disk assembly contains a total of 8 surfaces: 7 data surfaces for recording and 1 servo surface permanently recorded with information used to position the read/write heads at the specified cylinder. The RM80 has 15 heads—14 are read/write heads (two per data surface) and the additional head is the servo read head, which corresponds to the servo surface. The head disk assembly is divided into 561 cylinders: 559 are used for data and 2 are used for diagnostics. Each cylinder is divided into 14 tracks (two per data surface). Each track is divided into 32 sectors: 31 data sectors and one additional sector used when one of the sectors on that track is bad. Each sector has a data storage capacity of 4096 bits (512 bytes). Each sector is divided into a header field and a data field. The header field consists of a 48-bit header that contains the cylinder, track, and sector addresses and a 16-bit header CRC (Cyclic Redundancy Check). The data field consists of 4096 bits (512 bytes) of data and a 32-bit data ECC (Error Correction Code). The header field can only be written by the utility program that formats these head disk assemblies.

#### **OPERATION**

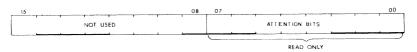

The REM80 and the RGM80 subsystems have sixteen registers plus the MASSBUS adapter registers. (Refer to the register section at the back of this book for register diagrams and bit definitions).

Before a READ or WRITE operation can begin, the processor loads the MBA virtual address, MBA byte counter, desired cylinder, desired sector/track address, and control and status 1 registers respectively.

The MBA virtual address register specifies the starting memory address of the storage location for the data to be read from or written onto the disk. The MBA byte counter register specifies the total number of bytes to be transfered between the disk and memory. The desired cylinder register and the desired sector/track address register specify the sector of the disk to be read or written.

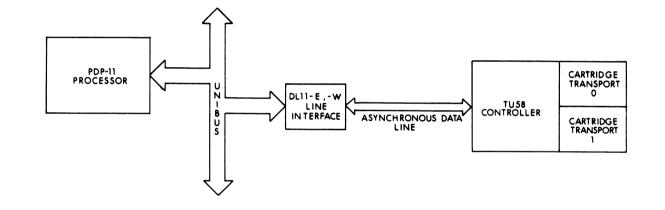

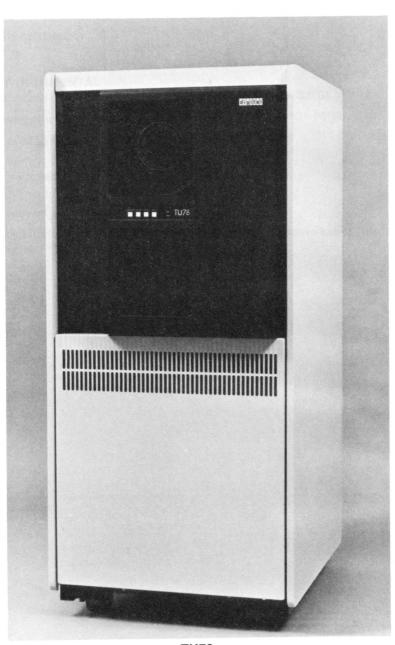

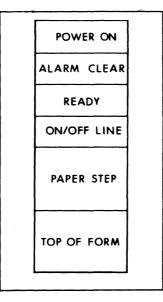

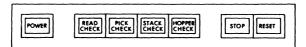

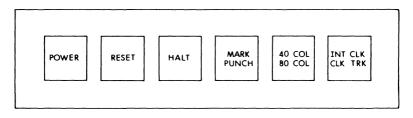

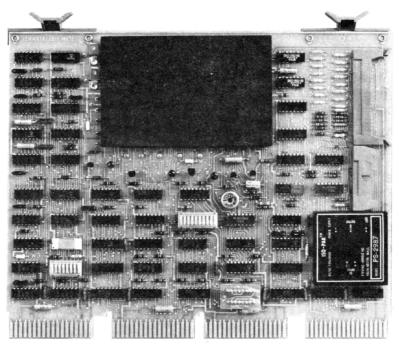

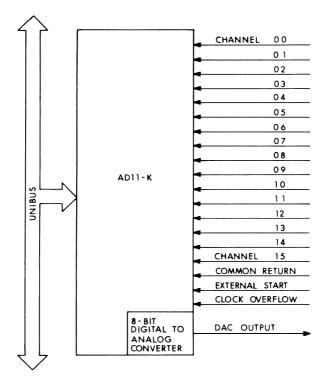

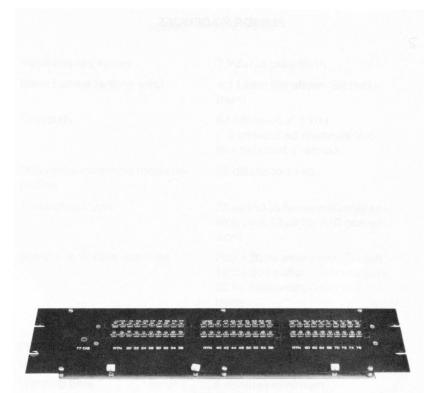

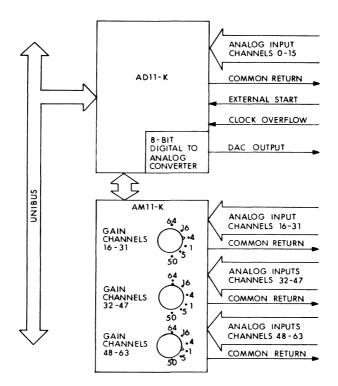

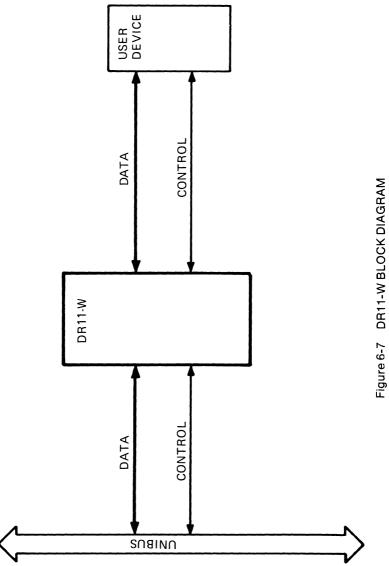

After the MBA virtual address, MBA byte counter, desired cylinder, and desired sector/track address registers have been loaded, the control and status 1 register is loaded with the READ or WRITE command from the processor. The command is then executed. If the heads are not currently positioned at the specified cylinder, the drive will do an implied SEEK, which moves the heads to the correct cylinder. The read/write data heads then read the headers on the specified track to locate the specified sector. During a READ operation, data bits serially read from the disk are assembled into 16-bit parallel words and a parity bit is generated for each 16-bit word. Every 16-bit word plus parity is then transferred to the MBA. The MBA combines two 16-bit words into a 32-bit memory word and generates a parity bit for each 32-bit word. Every 32-bit word plus parity is then transferred into the memory location specified. This process continues until the byte count in the MBA virtual address register is reached. When the READ operation is completed, an interrupt is set to alert the processor that the data has been read off the disk and stored in the specified memory location.