# MAGNETIC TAPE EQUIPMENT TYPES 50/51/52

Copyright 1963 by Digital Equipment Corporation

# TABLE OF CONTENTS

## CHAPTER 1

# INTRODUCTION

|     |                   | Page |

|-----|-------------------|------|

| 1-1 | Purpose and Scope | 1-1  |

| 1-2 | Chapter Subjects  | 1-1  |

| 1–3 | Figures           | 1-2  |

## CHAPTER 2

## GENERAL DESCRIPTION

| 2-2 | Purpose of System                         | 2-1 |

|-----|-------------------------------------------|-----|

| 2-2 | System Components                         | 2-1 |

| 2-3 | System Operation Specifications           | 2-3 |

| 2-4 | Physical Characteristics                  | 2-4 |

| 2-5 | Power Requirements                        | 2–5 |

| 2-6 | Equipment List                            | 2-5 |

|     | <u>a</u> Logic panels and power equipment | 2–5 |

|     | b Module list                             | 2-7 |

## CHAPTER 3

## INSTALLATION

| 3-1 | Site Selection                  | 3-1 |

|-----|---------------------------------|-----|

| 3-2 | Installation                    | 3-1 |

|     | <u>a</u> Unpacking              | 3-2 |

|     | b Installation of subassemblies | 3-2 |

|     | <u>c</u> Bus connections        | 3–3 |

| 3–3 | Inspection and Checkout         | 3-4 |

|     | <u>a</u> Inspection             | 3-4 |

|     | b Preoperational checkout       | 3-4 |

# SYSTEM FUNCTION

|     |                                  | Page |

|-----|----------------------------------|------|

| 4-1 | Logical Organization             | 4-1  |

| 4-2 | Tape Format                      | 4-3  |

| 4-3 | Tape Write and Read Signal Flow  | 4-5  |

| 4-4 | Type 52 Tape Instructions        | 4-7  |

| 4-5 | Type 52 System Logic             | 4-15 |

|     | <u>a</u> Command logic           | 4-18 |

|     | b Address logic                  | 4-18 |

|     | <u>c</u> Data transfer registers | 4-18 |

|     | <u>d</u> In-out control          | 4-19 |

|     | e_ Format control                | 4-20 |

|     | <u>f</u> Tape unit control       | 4-21 |

| 4-6 | Type 51 Tape Instructions        | 4-22 |

| 4-7 | Type 51 System Logic             | 4-24 |

# CHAPTER 5

# OPERATING PROCEDURES

| 5-1          | General                              | 5-1          |

|--------------|--------------------------------------|--------------|

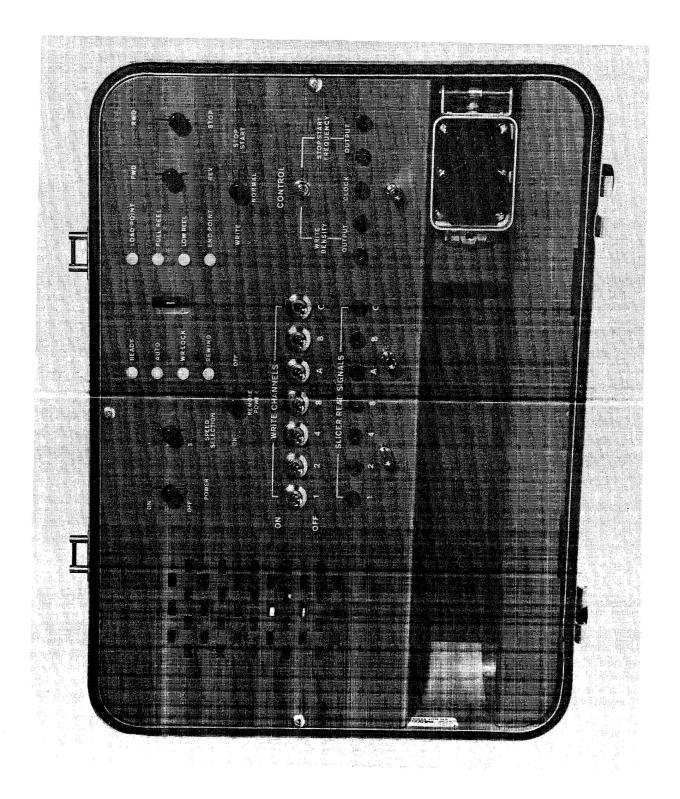

| 5-2          | Tape Unit Switches and Indicators    | 5-1          |

|              | a Manual control panel               | 5-1          |

|              | b Gain, slice and test point panel   | 5-3          |

|              | <u>c</u> Miscellaneous controls      | 5 <b>-</b> 4 |

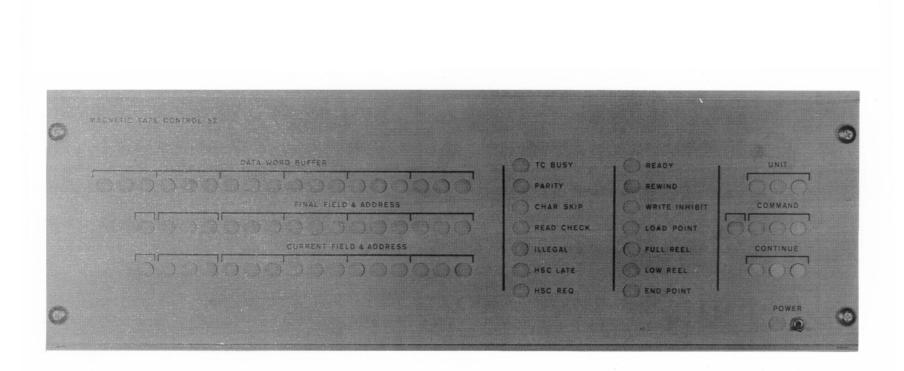

| 5-3          | Tape Control Switches and Indicators | 5-4          |

|              | a_Indicator panel                    | 5-5          |

|              | b Power controls                     | 5-7          |

| 5 <b>-</b> 4 | Tape Loading                         | 5-8          |

| 5 <b>-</b> 5 | Manual Control                       | 5-9          |

| 5-6          | Operator's Checklist                 | 5-10         |

# TAPE SYSTEM LOGIC

|                                                             | Page              |

|-------------------------------------------------------------|-------------------|

| General                                                     | 6-1               |

| System operations                                           | 6-2               |

| a_Type 52 system                                            | 6-2               |

| <u>b</u> Type 51 system                                     | 6-3               |

| PDP-1 Control                                               | 6-4               |

| a_ Type 52 system                                           | 6-4               |

| b Type 51 system                                            | 6-4               |

| <u>c</u> Signal connections between PDP-1 and tape system . | 6 <b>-</b> 5      |

| Command Logic                                               | 6 <b>-</b> 5      |

| a Command register                                          | 6-6               |

| b Command decoders                                          | 6-7               |

| Address Logic                                               | 6-8               |

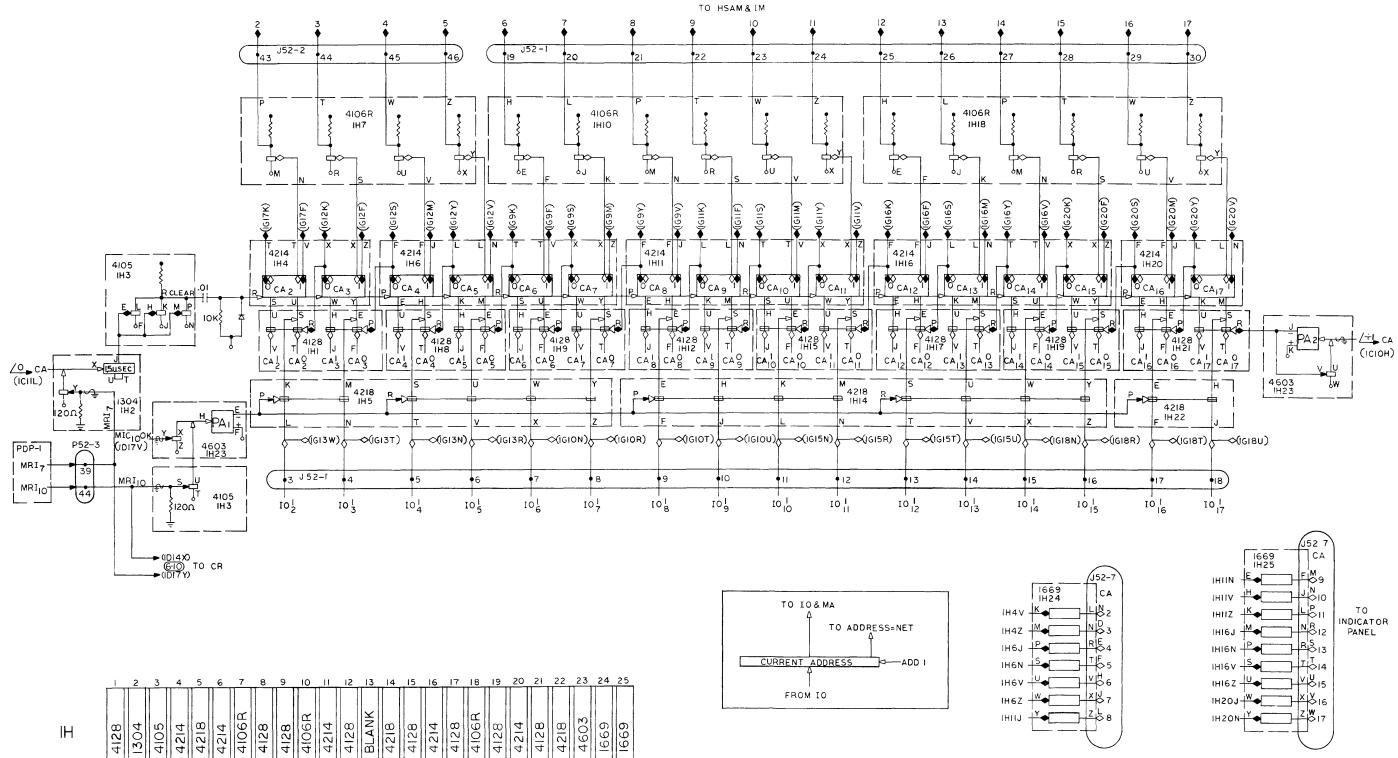

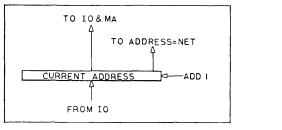

| <u>a</u> Current address                                    | 6-8               |

| b Unit address                                              | 6-9               |

| <u>c</u> Final address                                      | 6-10              |

| d Address equal                                             | 6-10              |

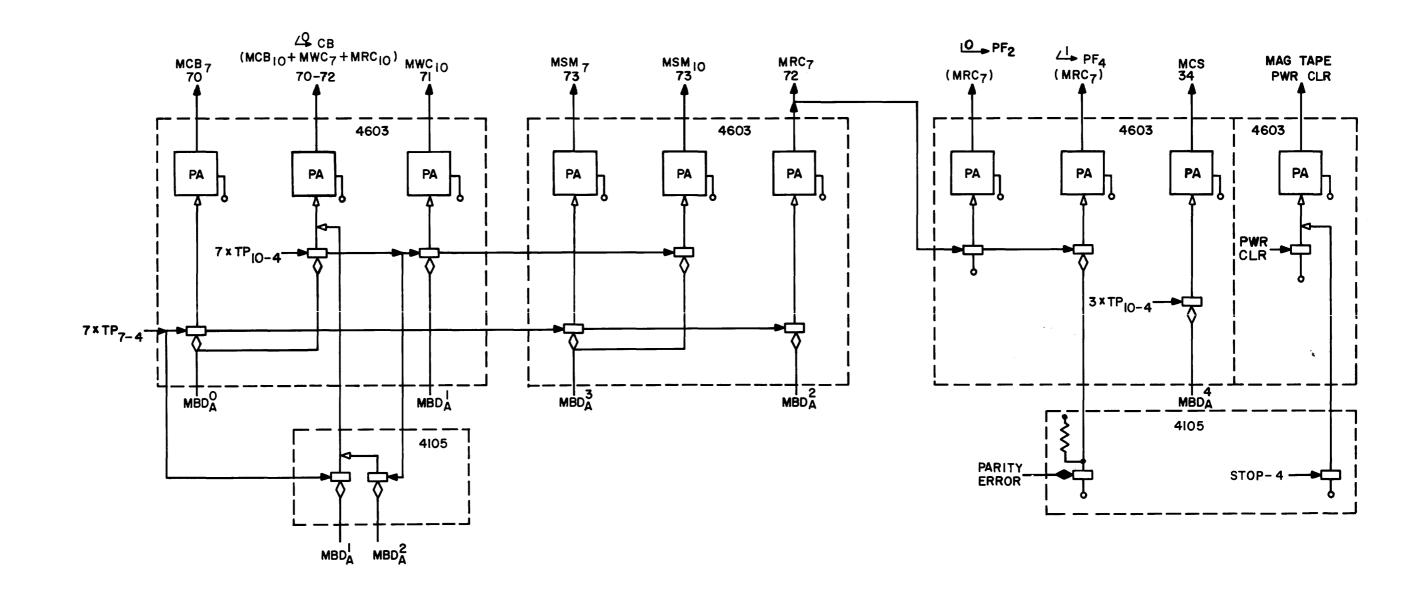

| Data Word Buffer                                            | 6-11              |

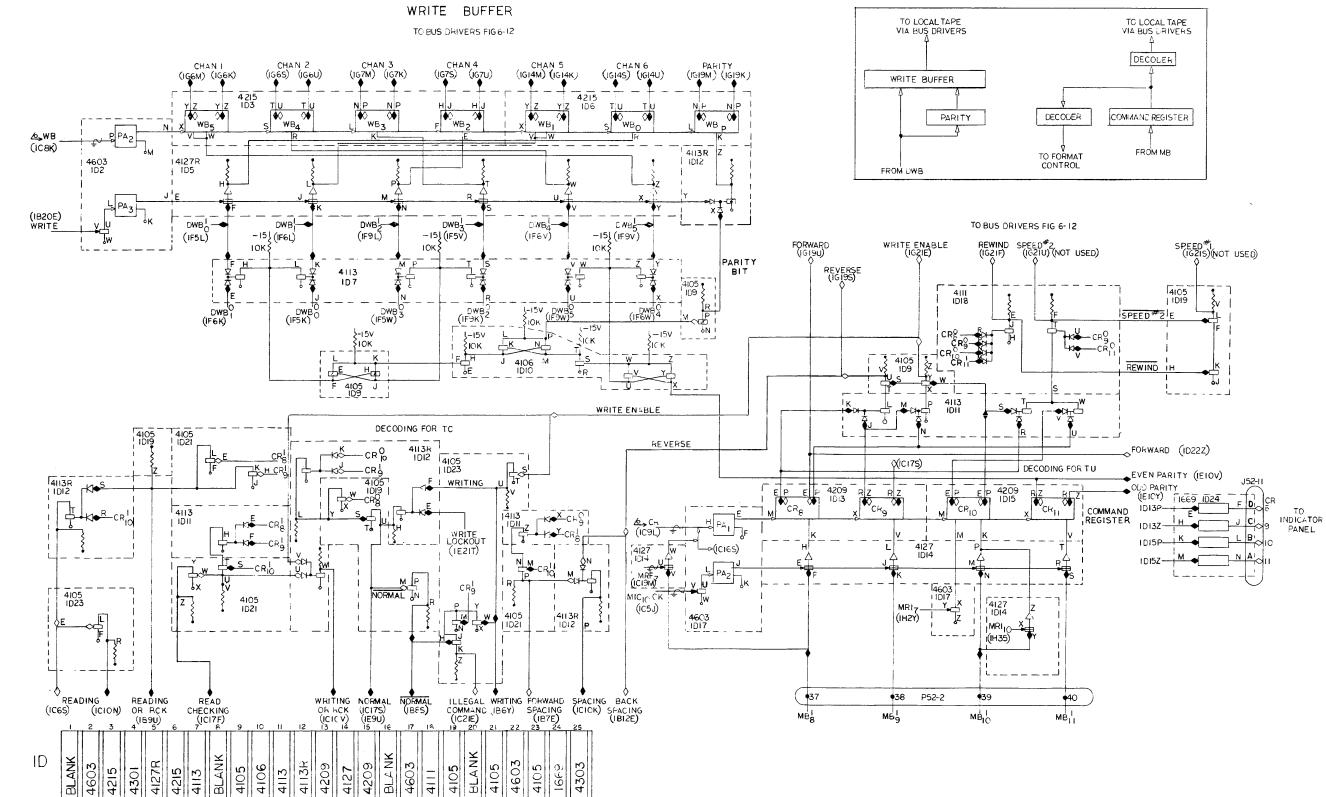

| Write Buffer                                                | 6-12              |

| Read Buffer                                                 | 6-13              |

| In-out Control                                              | 6-15              |

| a_Clear logic                                               | 6 <b>-</b> 15     |

| b System status                                             | 6-15              |

| <u>c</u> Instruction execution                              | 6-17              |

| <u>d</u> HSC transfers                                      | 6-20              |

| <u>e</u> Register control                                   | 6-21              |

| Format Control                                              | 6-21              |

| a Character counting                                        | 6-21              |

| b Write sequence                                            | 6-22              |

|                                                             | System operations |

|      |                                 | Page |

|------|---------------------------------|------|

|      | <u>c</u> Read sequence          | 6-23 |

|      | <u>d</u> HSC requests           | 6-25 |

|      | e Terminating sequence          | 6-26 |

| 6-11 | Programmed Tape Control Type 51 | 6-27 |

|      | a_Command logic                 | 6-28 |

|      | b Write logic                   | 6-29 |

|      | <u>c</u> Read logic             | 6-30 |

|      | <u>d</u> Parity logic           | 6-31 |

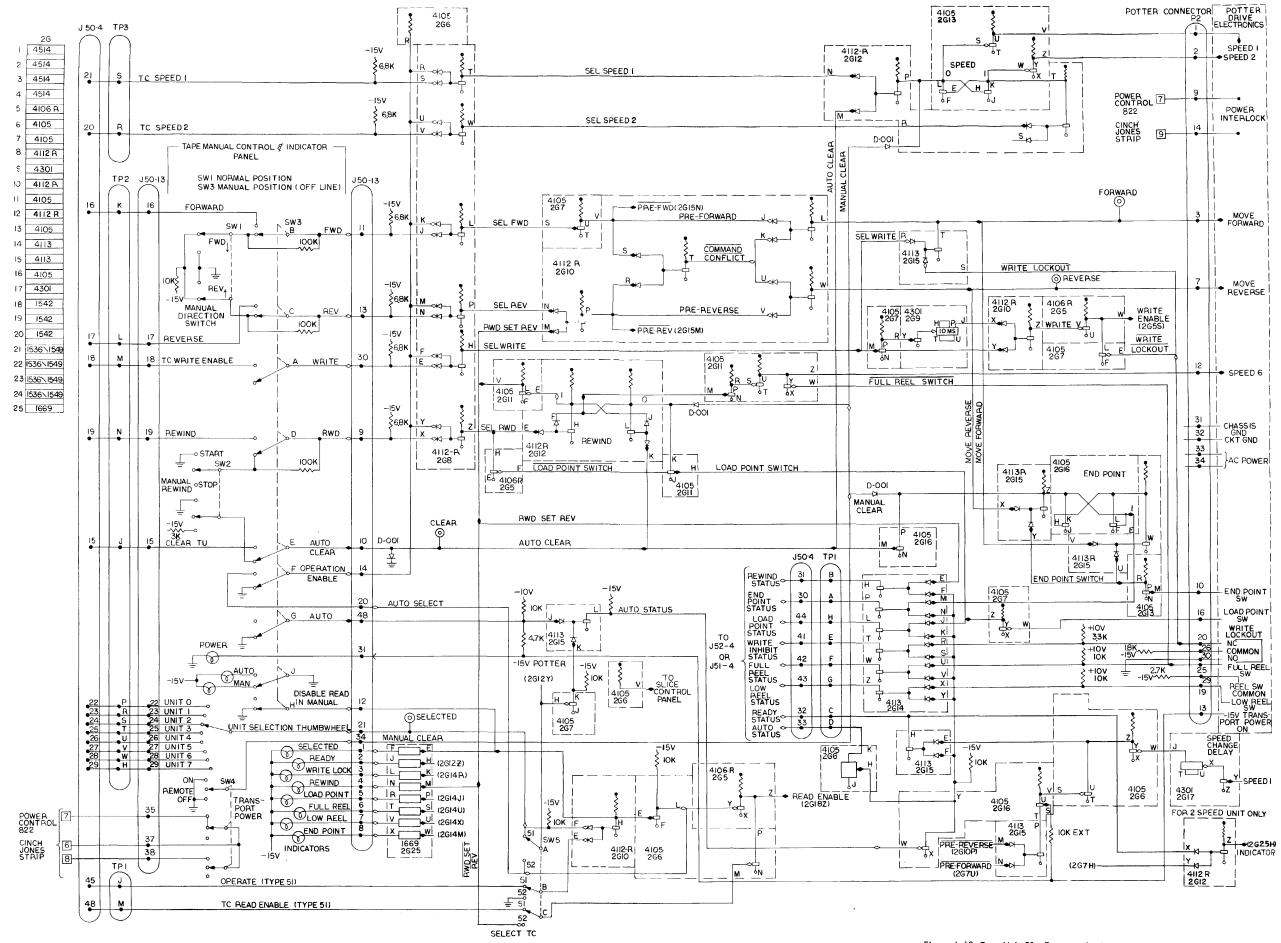

| 6-12 | Local Tape Control Type 50      | 6-31 |

|      | a_ Transport logic              | 6-32 |

|      | b Tape writing and sensing      | 6-35 |

# CIRCUIT DESCRIPTION

| 7-1           |

|---------------|

| 7-1           |

| 7-2           |

| 7-3           |

| 7-4           |

| 7-5           |

| 7-7           |

| 7-8           |

| 7 <b>-</b> 8  |

| 7-9           |

| 7-12          |

| 7-14          |

| 7-16          |

| 7 <b>-</b> 17 |

| 7-18          |

| 7-19          |

|               |

# MAINTENANCE

|                                      | Page                        |

|--------------------------------------|-----------------------------|

| Special Tools and Test Equipment     | 8-1                         |

| Equipment Layout and Wiring,         | 8-3                         |

| Recommended Spare Parts              | 8-4                         |

| a Module spares                      | 8-5                         |

| _<br>b Tape transport spares         | 8-6                         |

|                                      | 8-6                         |

| Adjustment and Calibration           | 8-7                         |

| a Tape sensing circuits              | 8-7                         |

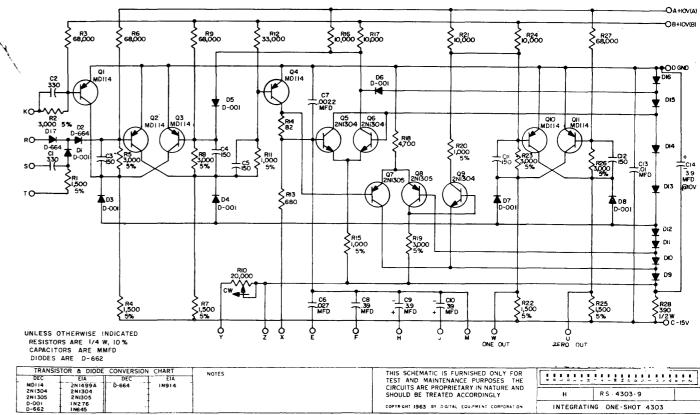

| –<br>b Integrating delay 4303        | 8-10                        |

| –<br>Preventive Maintenance          | 8-11                        |

| Maintenance Programs                 | 8-15                        |

| a General programming considerations | 8-16                        |

| –<br>b Type 52 test word program     | 8-34                        |

| <br>с_ MAINDEC 20 for Туре 51        | 8-45                        |

| Potter Transport                     | 8-45                        |

| a Pinch roller bounce                | 8-46                        |

| _<br>b Write-Read Coupling           | 8-48                        |

|                                      | Equipment Layout and Wiring |

# LIST OF ILLUSTRATIONS

| Figure |                                                     | Page |

|--------|-----------------------------------------------------|------|

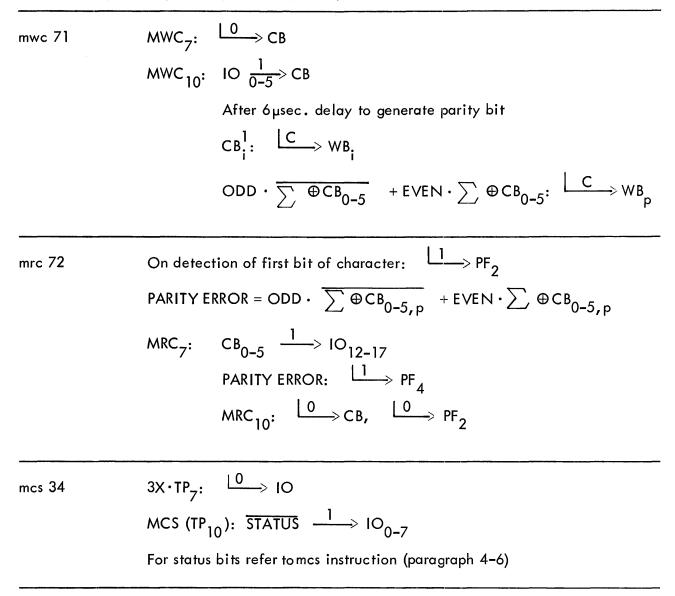

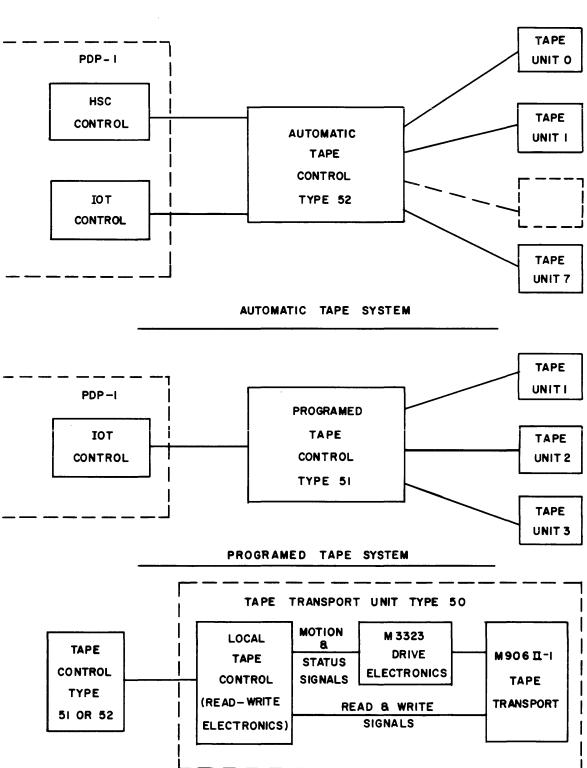

| 2-1    | Tape System Configuration Diagram                   | A-2  |

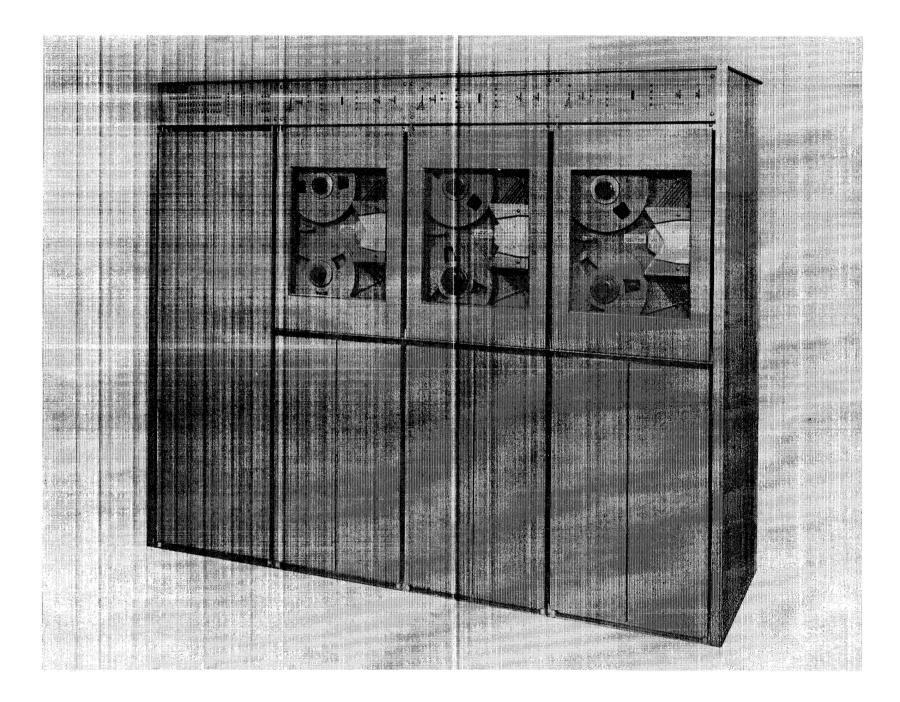

| 2-2    | Typical Installation, Type 52 Automatic Tape System | A-4  |

| 2-3    | Layout Diagram, Tape Control 52                     | A-6  |

| 2-4    | Layout Diagram, Tape Unit 50                        | A-10 |

| 2-5    | Tape Unit                                           | A-14 |

| 3-1    | Tape Unit Bus Socket and Taper Pin Panel            | A-16 |

| 3-2    | Type 52 System Bus Connections                      | A-18 |

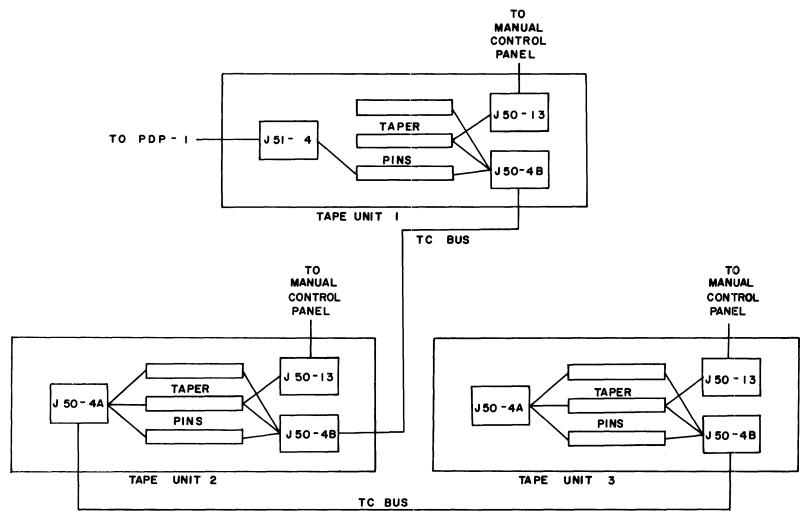

| 3-3    | Type 51 System Bus Connections                      | A-20 |

| Figure       |                                                               | Page           |

|--------------|---------------------------------------------------------------|----------------|

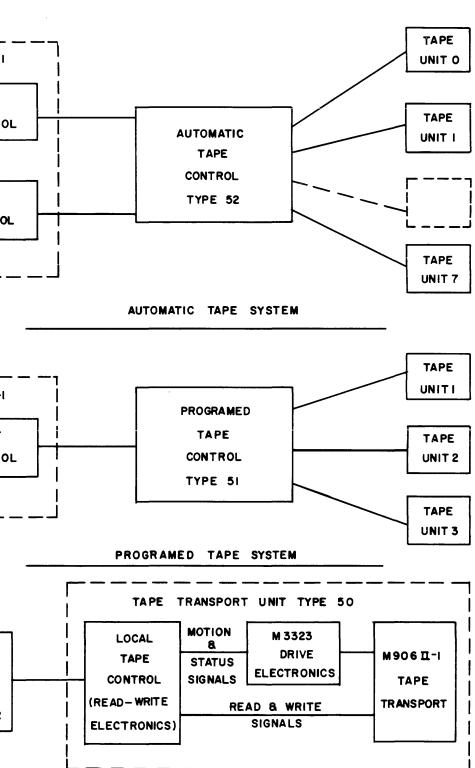

| 4-1          | Automatic Tape System Block Diagram                           | A-22           |

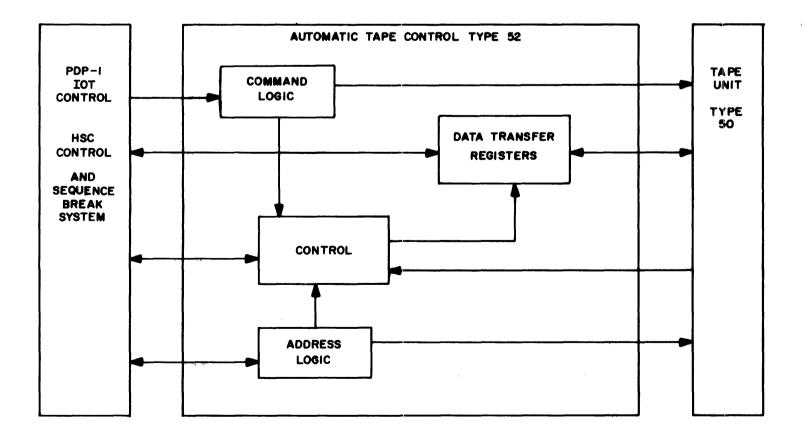

| 4-2          | Tape Format                                                   | A-24           |

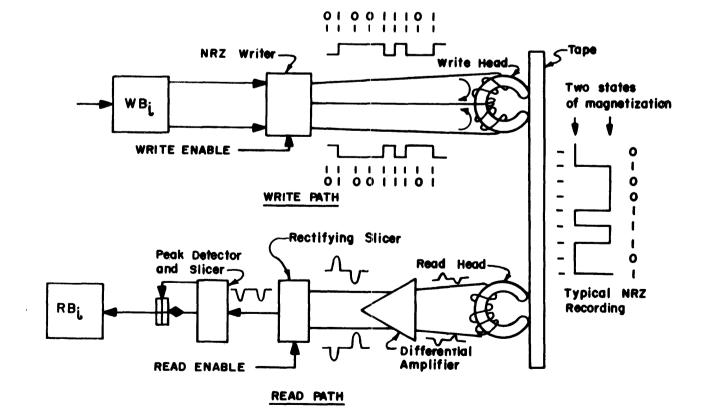

| 4-3          | Tape Write and Read Signal Flow                               | A-26           |

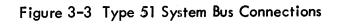

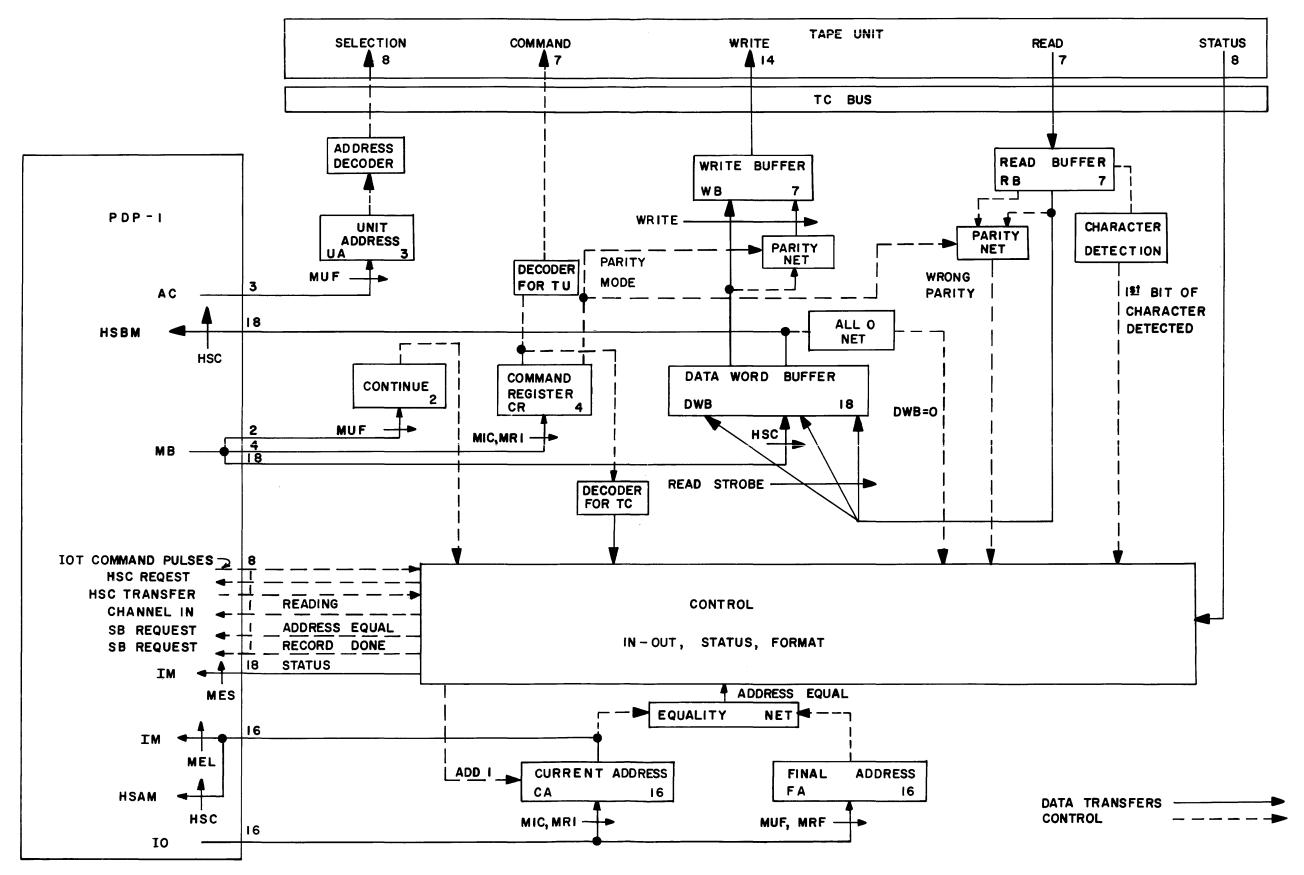

| 4-4          | Automatic Tape Control 52 Block Diagram                       | A-28           |

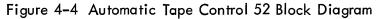

| 4–5          | Tape Unit 50 Block Diagram                                    | A-32           |

| 4-6          | Read Timing for Type 51 Programmed Tape System                | A-34           |

| 4-7          | Programmed Tape Control 51 Block Diagram                      | A-36           |

| 5-1          | Manual Control Panel                                          | A-38           |

| 5-2          | Gain, Slice and Test Point Panel                              | A-40           |

| 5-3          | Indicator Panel                                               | A-42           |

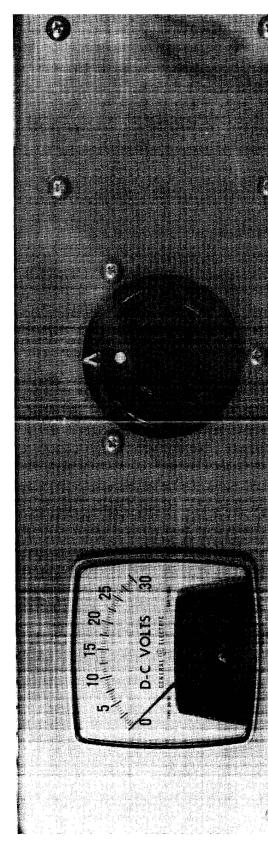

| 5-4          | Variable Power Supply 734                                     | A-44           |

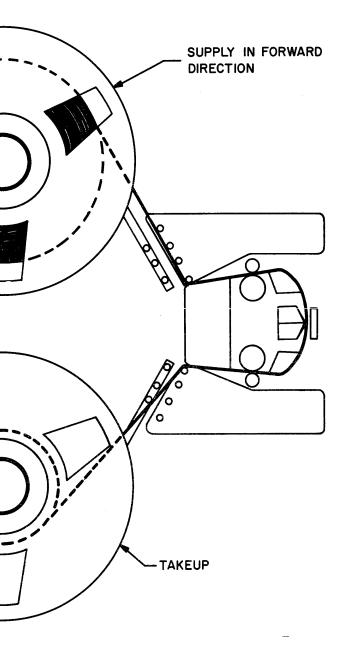

| 5 <b>-</b> 5 | Tape Threading                                                | A <b>-</b> 46  |

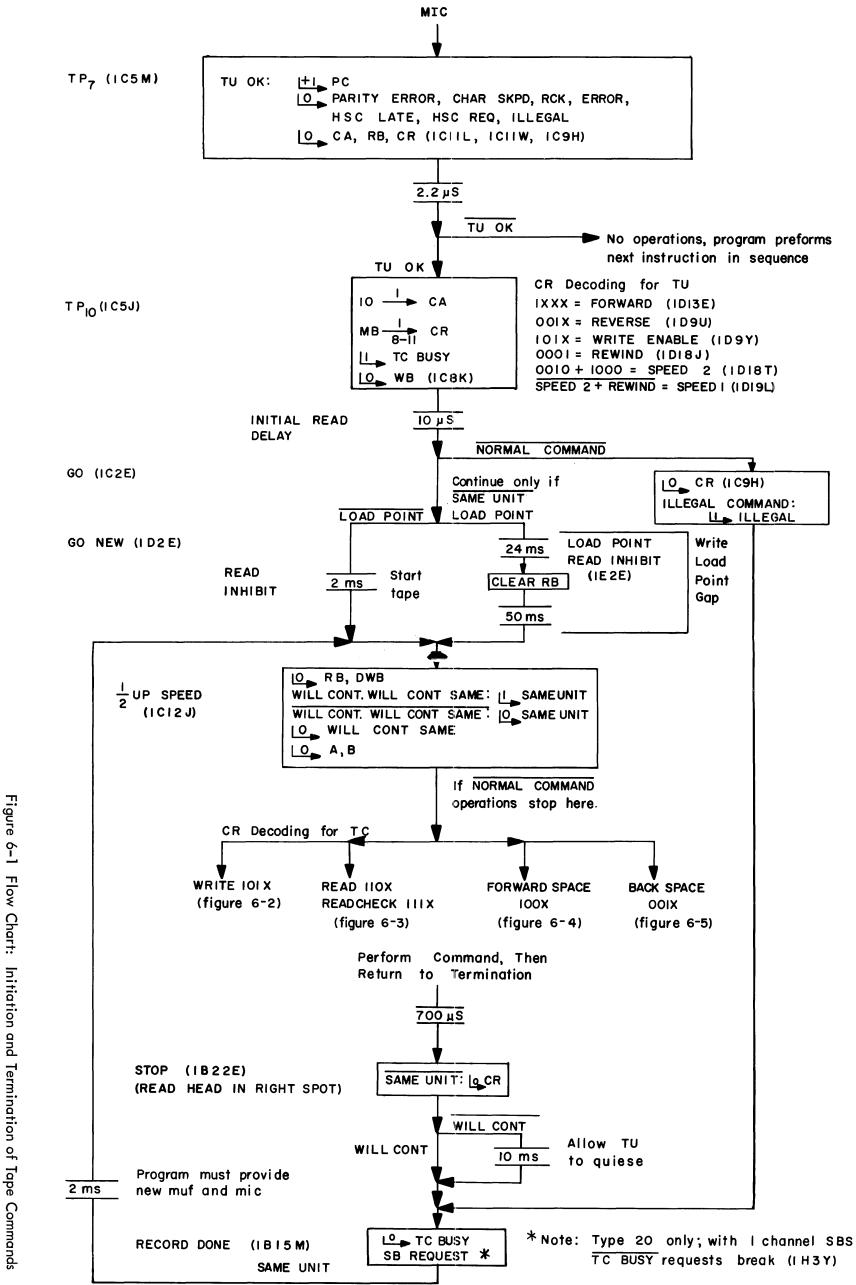

| 6-1          | Flow Chart: Initiation and Termination of Tape Commands .     | A-48           |

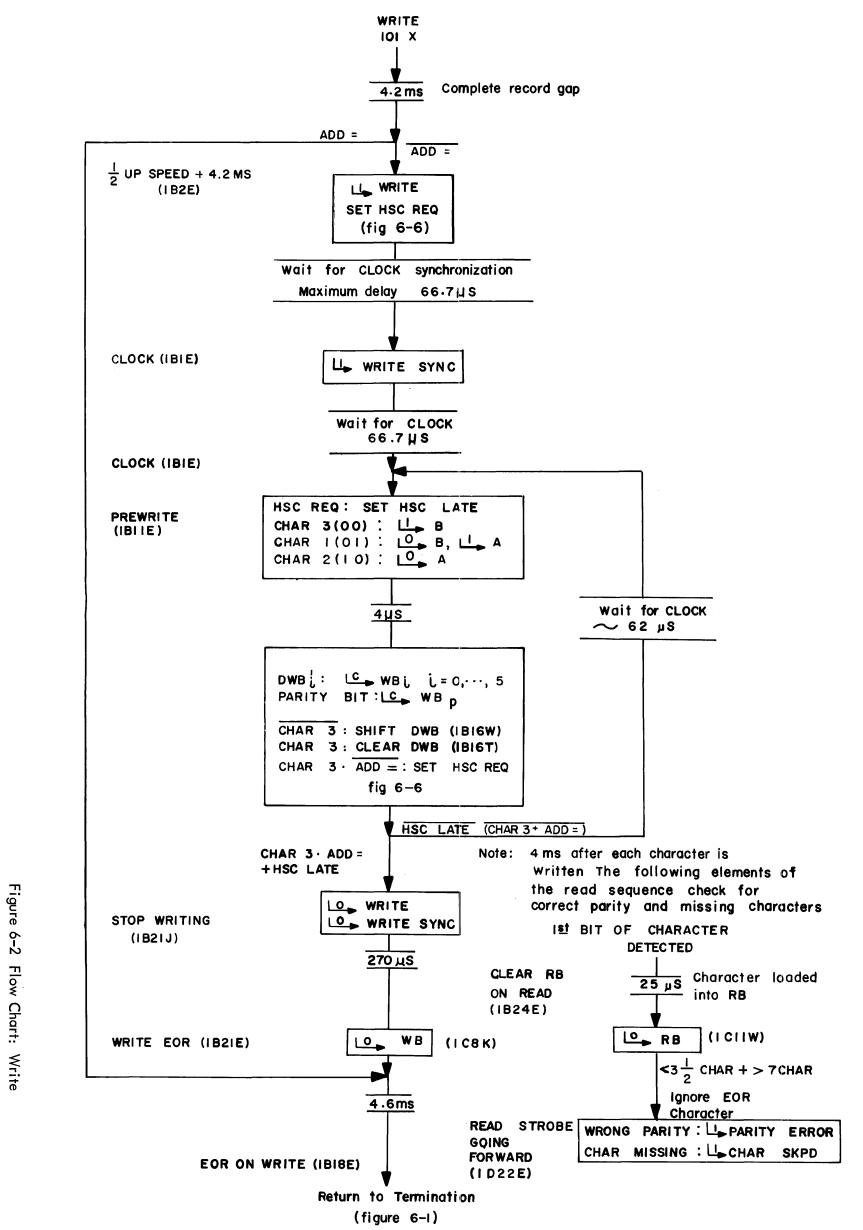

| 6-2          | Flow Chart: Write                                             | A <b>-</b> 52  |

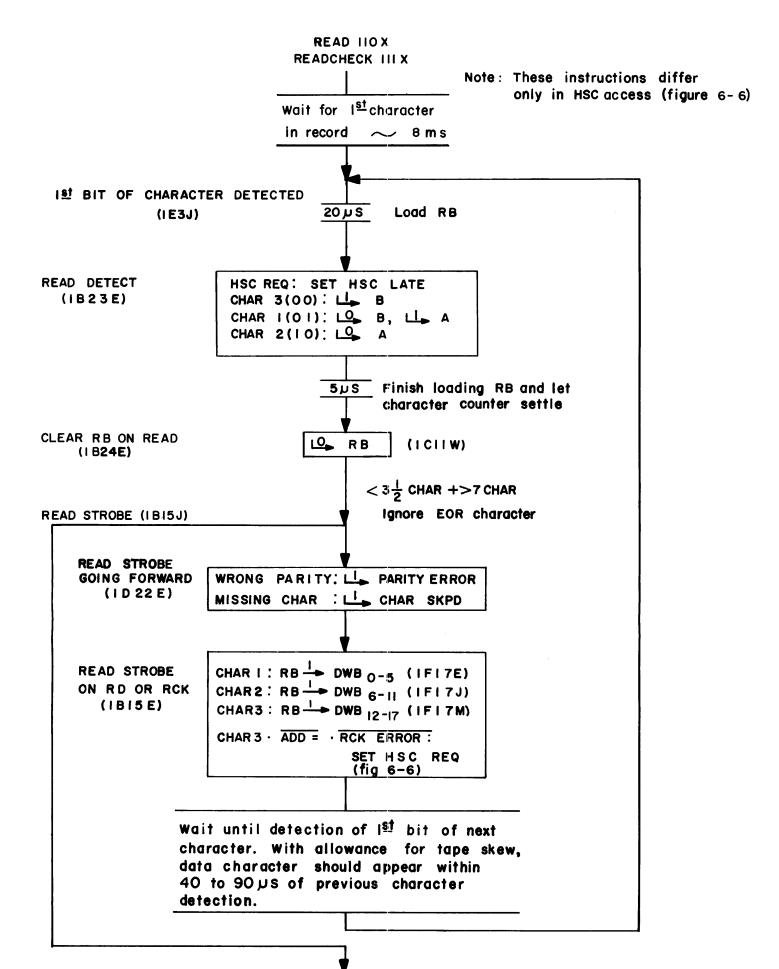

| 6-3          | Flow Chart: Read and Readcheck                                | A <b>-</b> 56  |

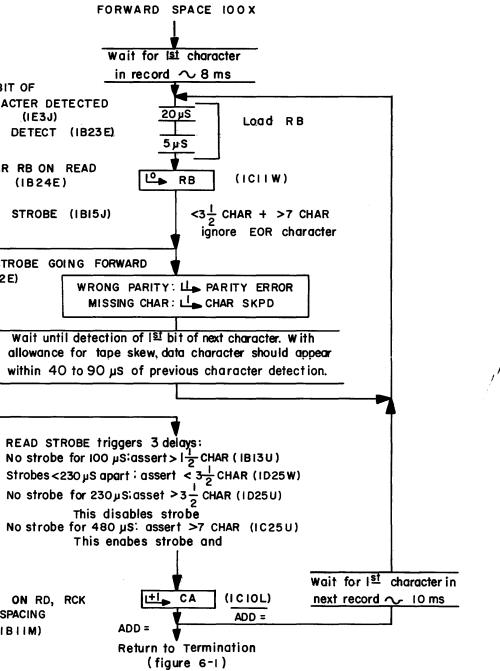

| 6-4          | Flow Chart: Forward Space                                     | A-60           |

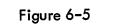

| 6-5          | Flow Chart: Backspace                                         | A-62           |

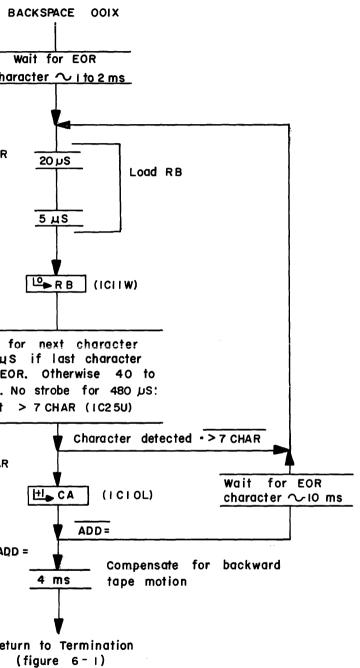

| 6-6          | Flow Chart: High Speed Channel Access                         | A <b>-</b> 64  |

| 6-7          | IOT Control for Type 52 Tape System                           | A-66           |

| 6-8          | IOT Control for Type 51 Tape System                           | A-70           |

| 6-9          | Signal Connections: PDP-1 to Magnetic Tape System             | A <b>-</b> 74  |

| 6-10         | Command Register, Command Decoders, Write Buffer              | A-78           |

| 6-11         | Current Address                                               | A-82           |

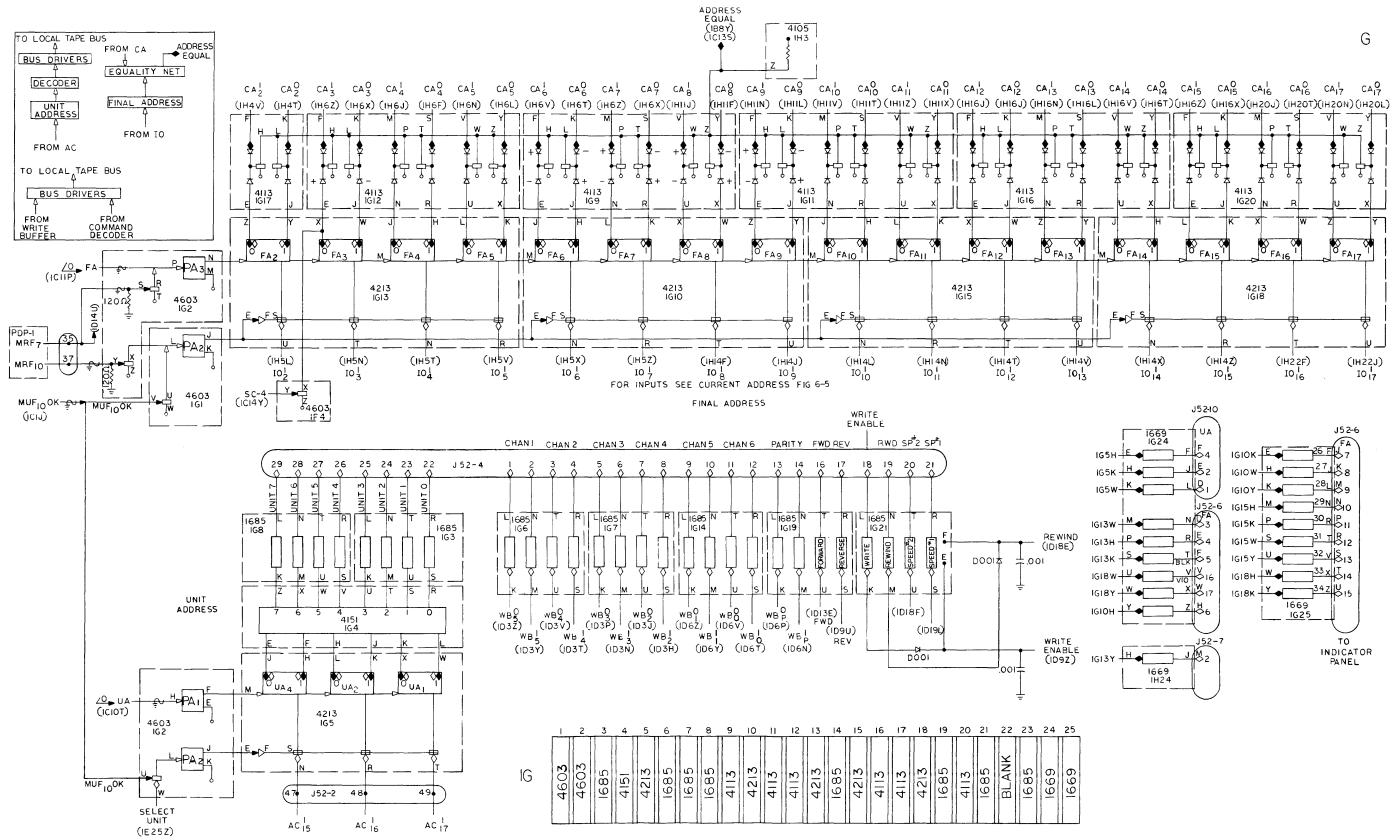

| 6-12         | Unit, Final Address, Address Equal                            | A-86           |

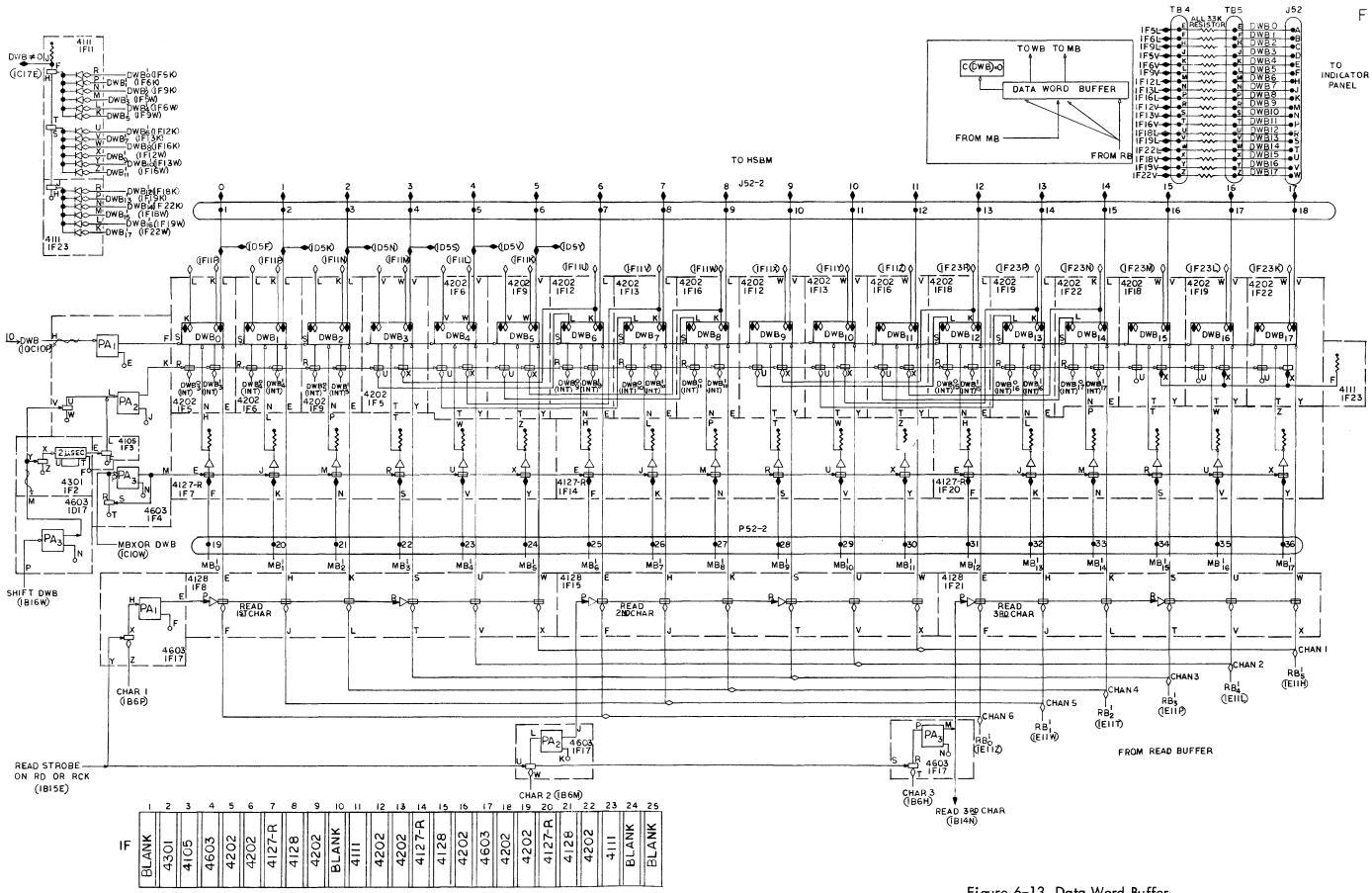

| 6-13         | Data Word Buffer                                              | A-90           |

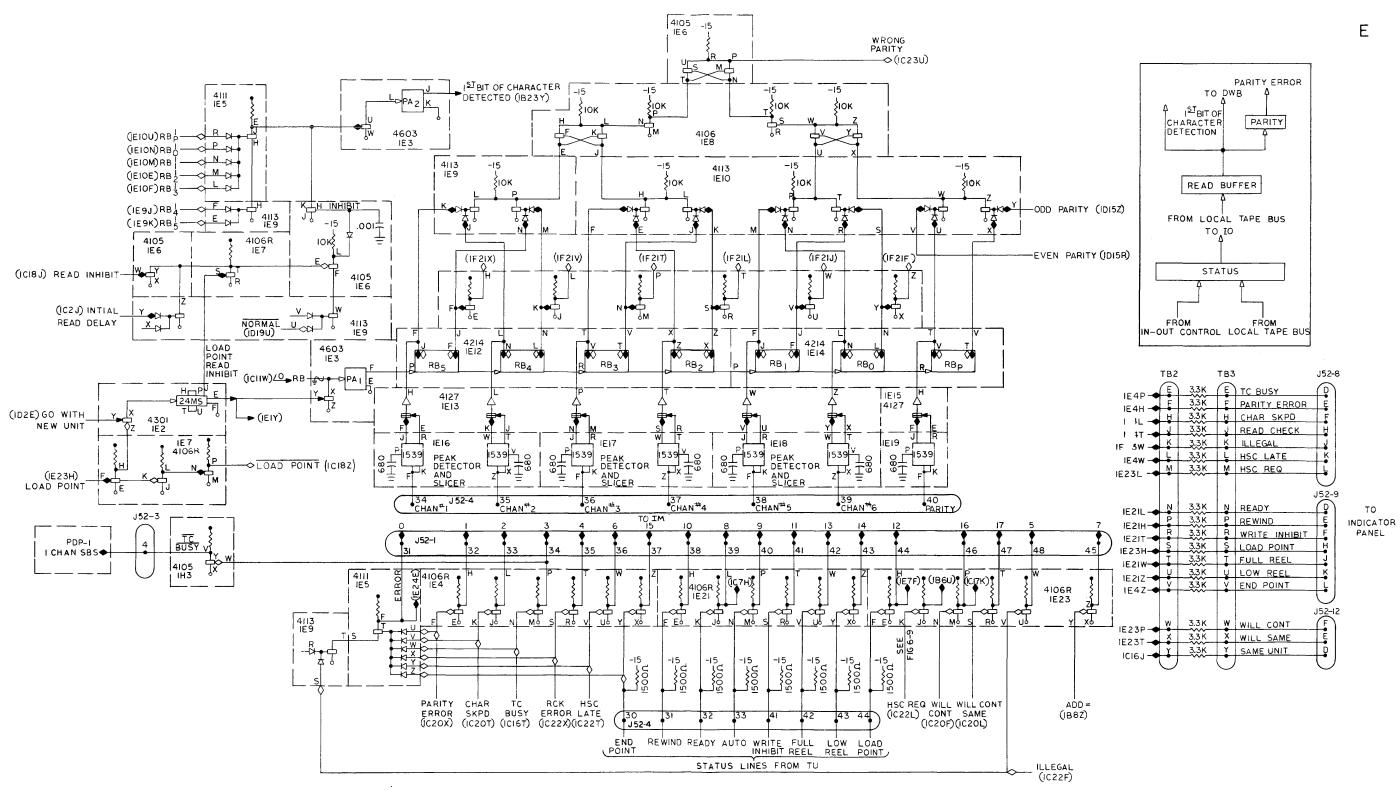

| 6-14         | Read Buffer, Status                                           | A-94           |

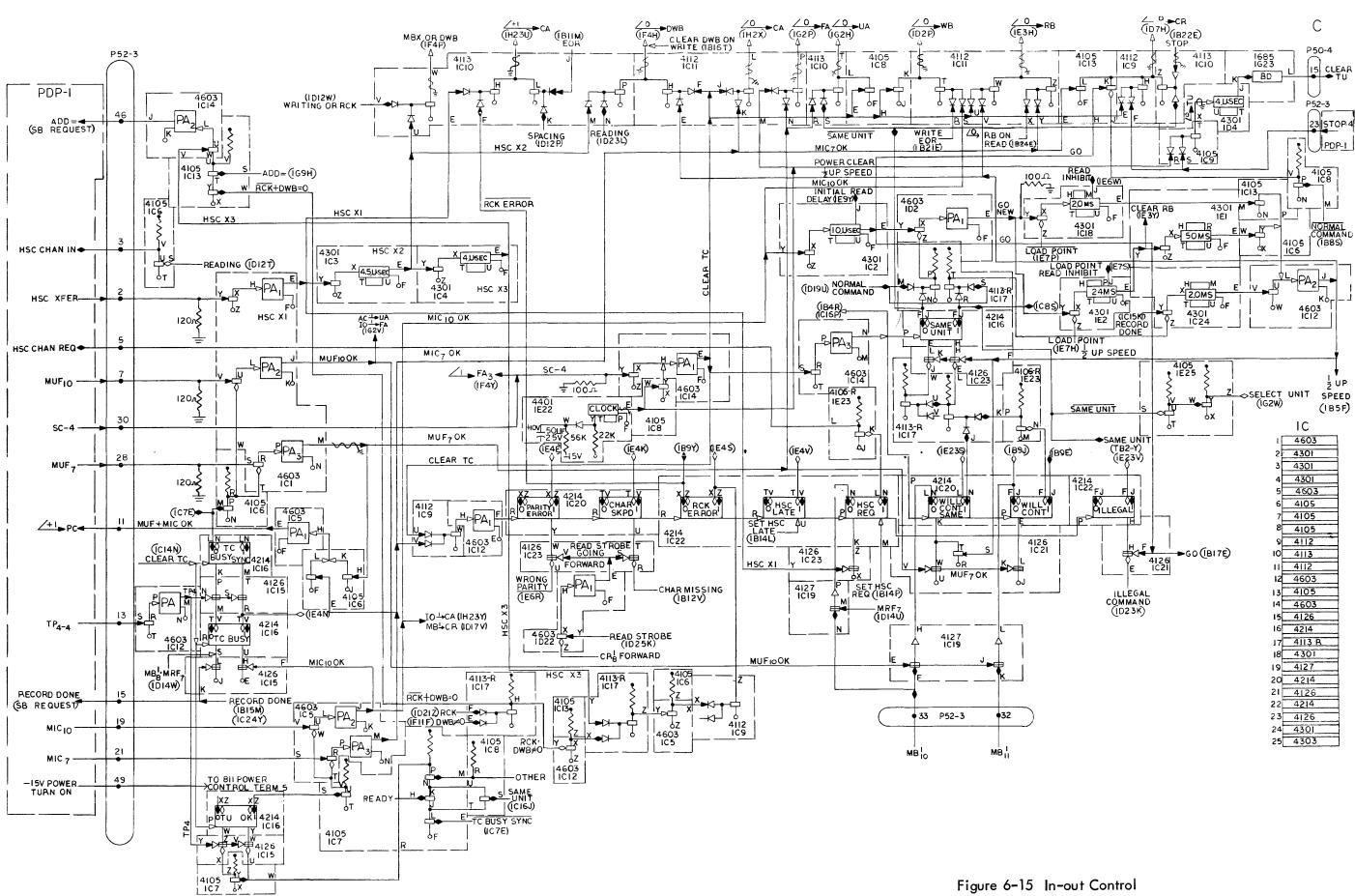

| 6-15         | In-out Control                                                | A-98           |

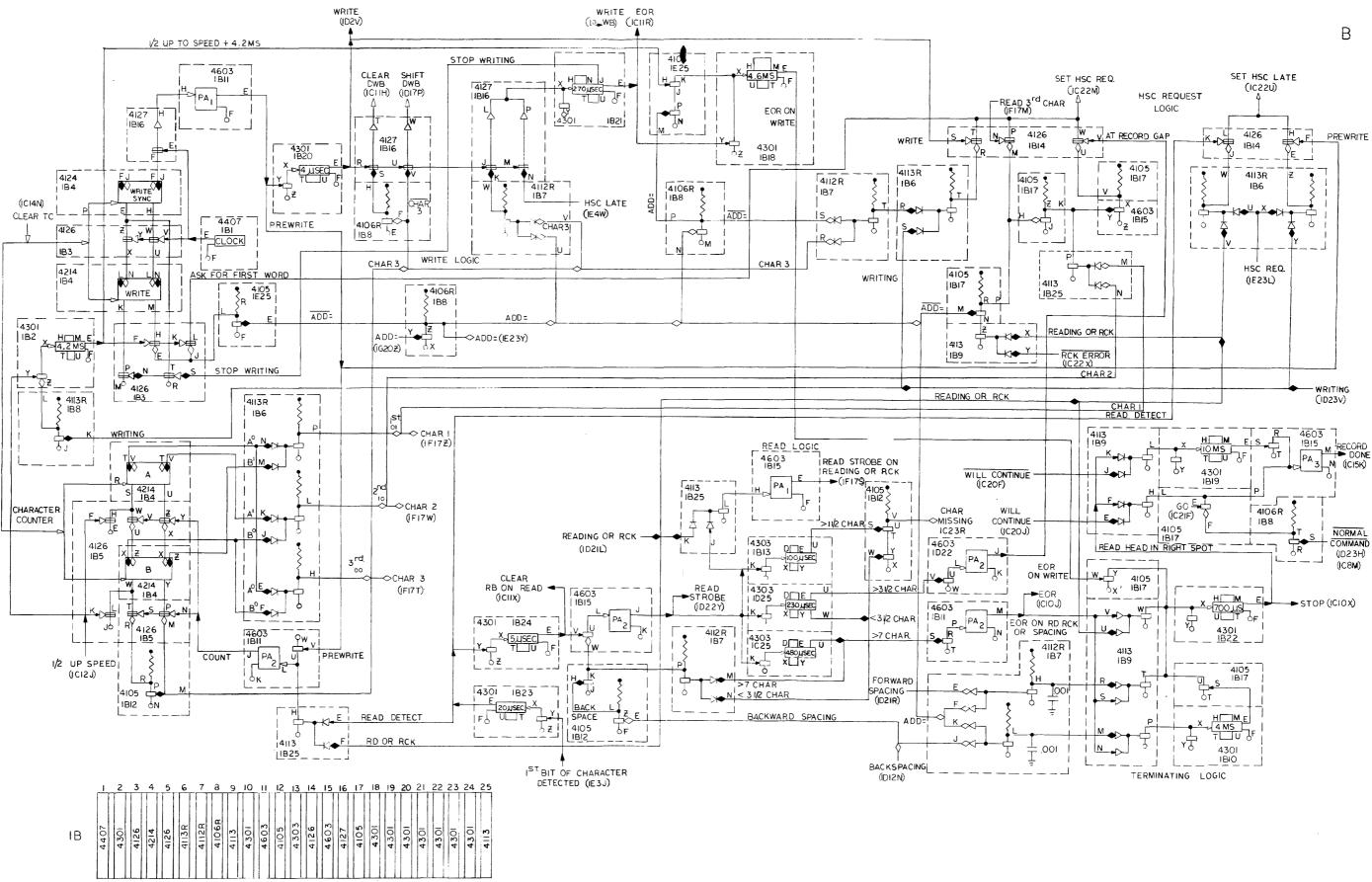

| 6-16         | Format Control                                                | A-102          |

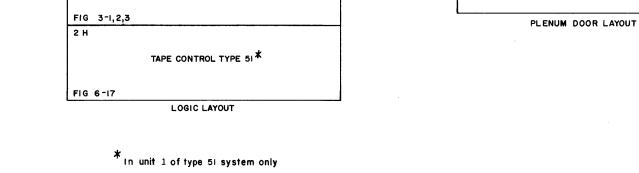

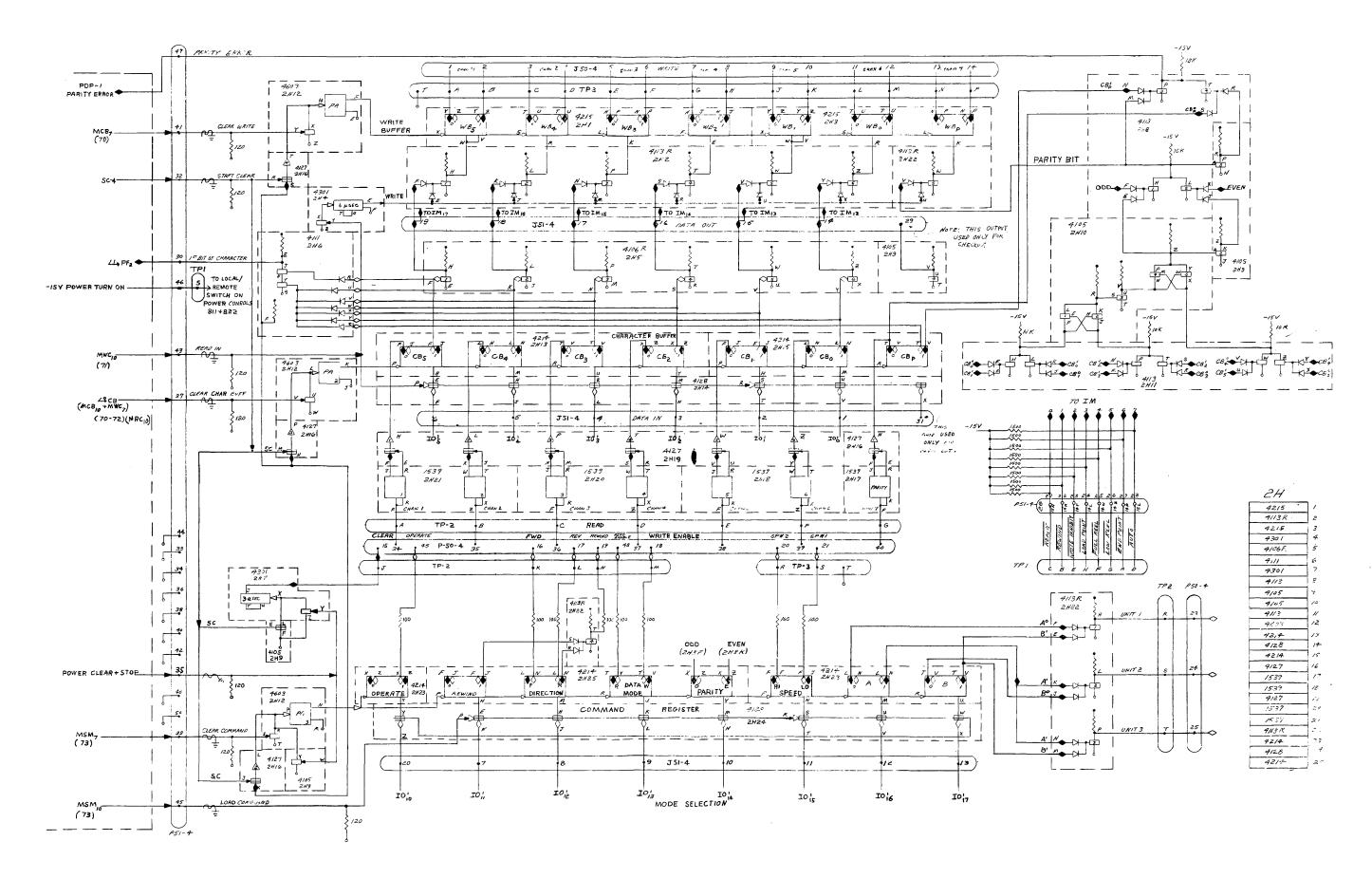

| 6-17         | Programmed Tape Control Type 51                               | A-106          |

| 6-18         | Tape Unit 50:         Transport Logic         Transport Logic | A-112          |

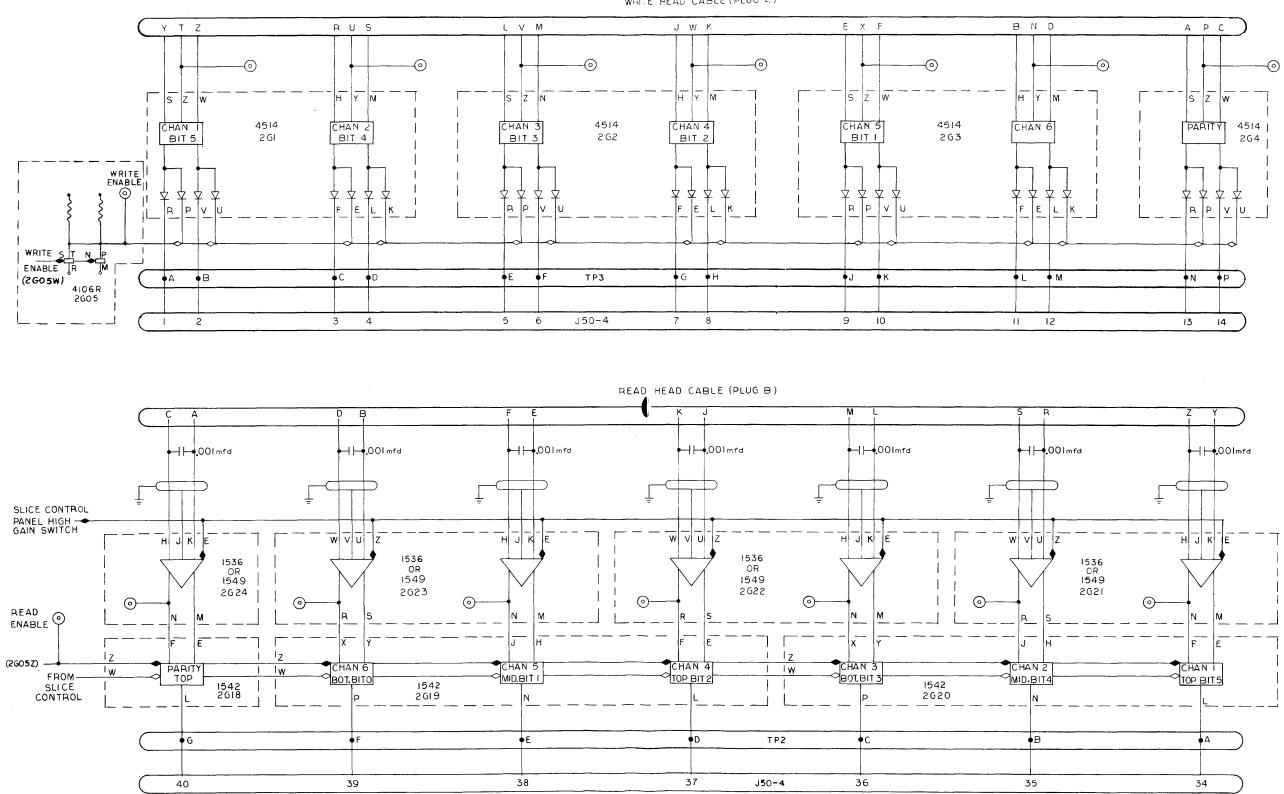

| 6-19         | Tape Unit 50: Read-Write Circuits                             | A <b>-</b> 116 |

| Figure |                                                              | Page  |

|--------|--------------------------------------------------------------|-------|

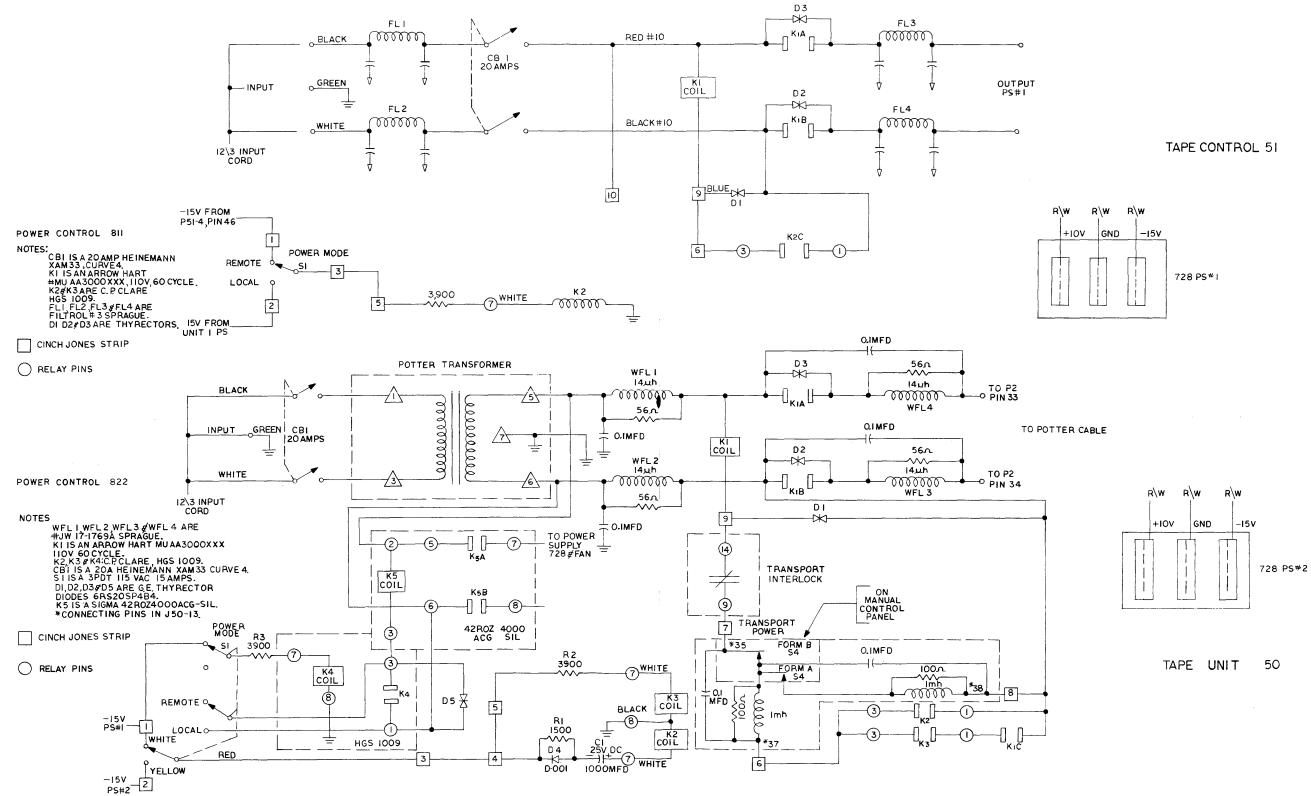

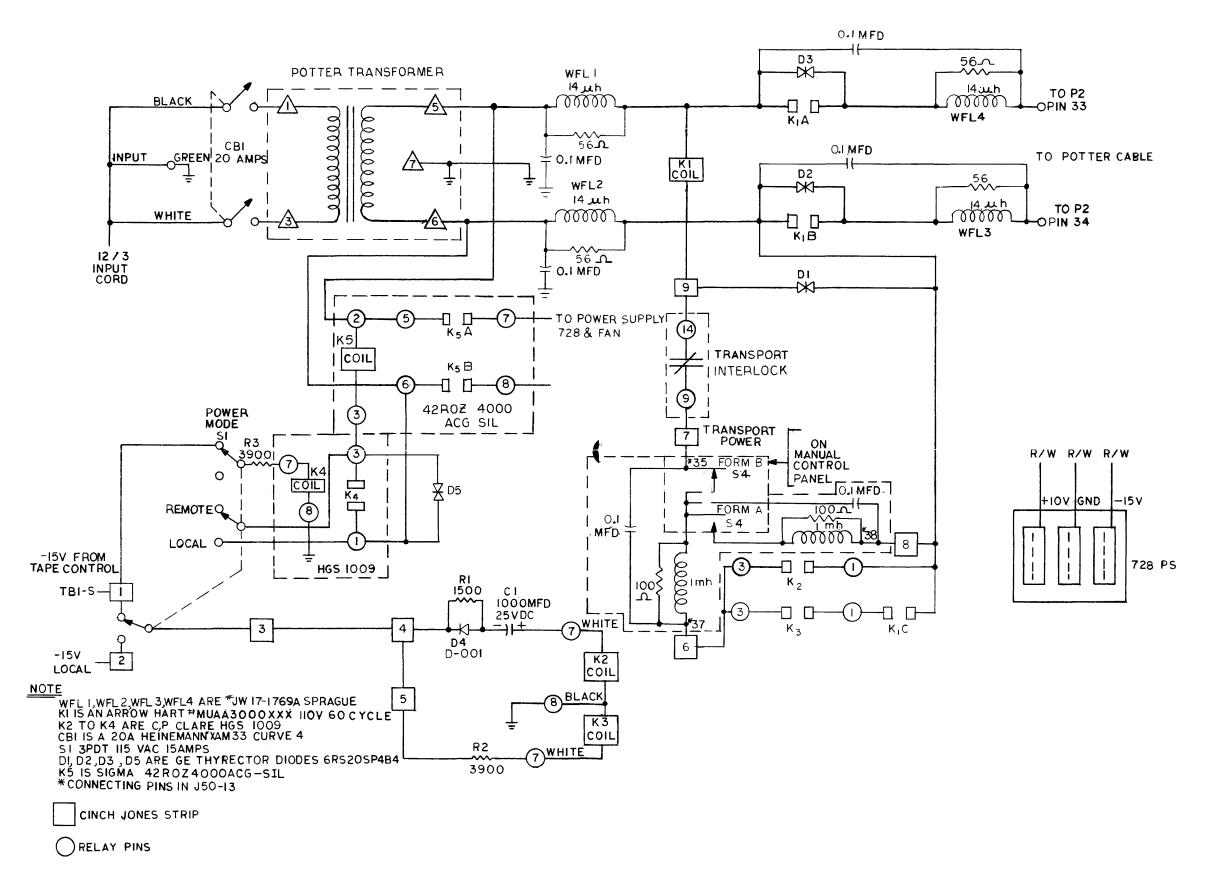

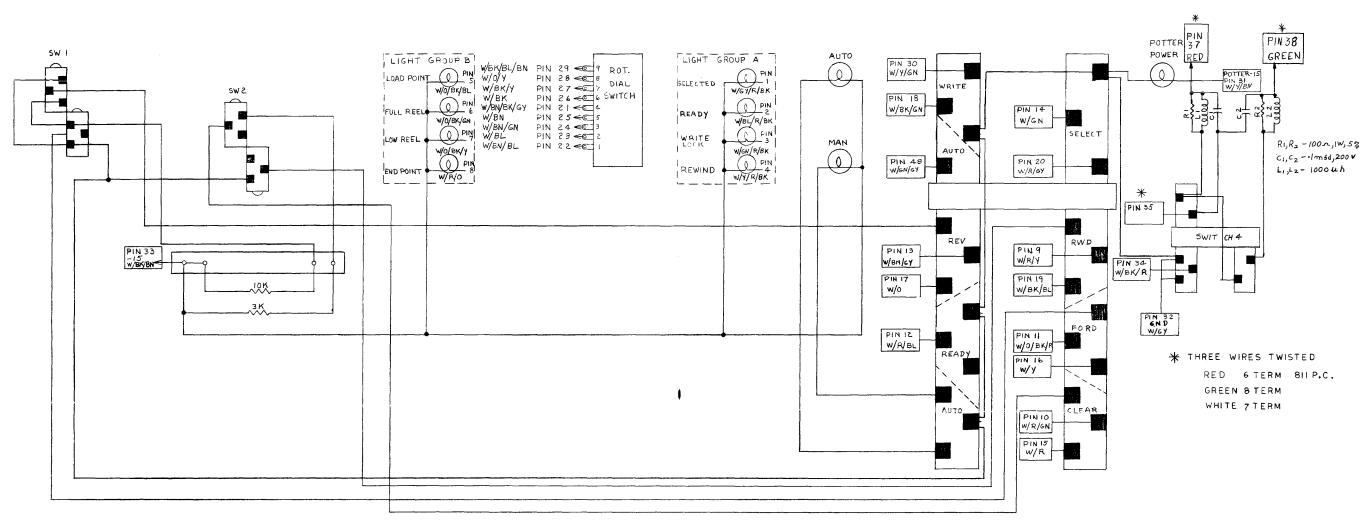

| 7-1    | Power Control Wiring for Types 50 and 51 Combination         | A-120 |

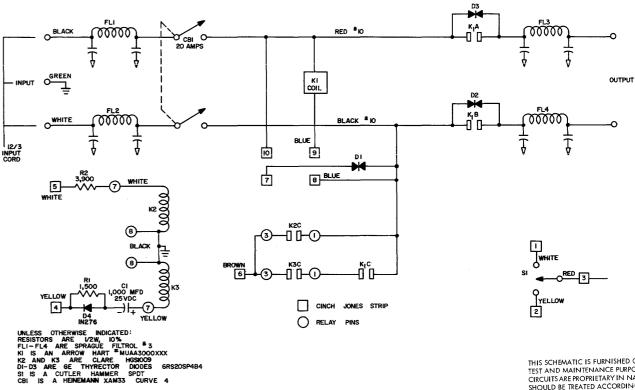

| 7-2    | Power Control Wiring for Tape Control 52                     | A-124 |

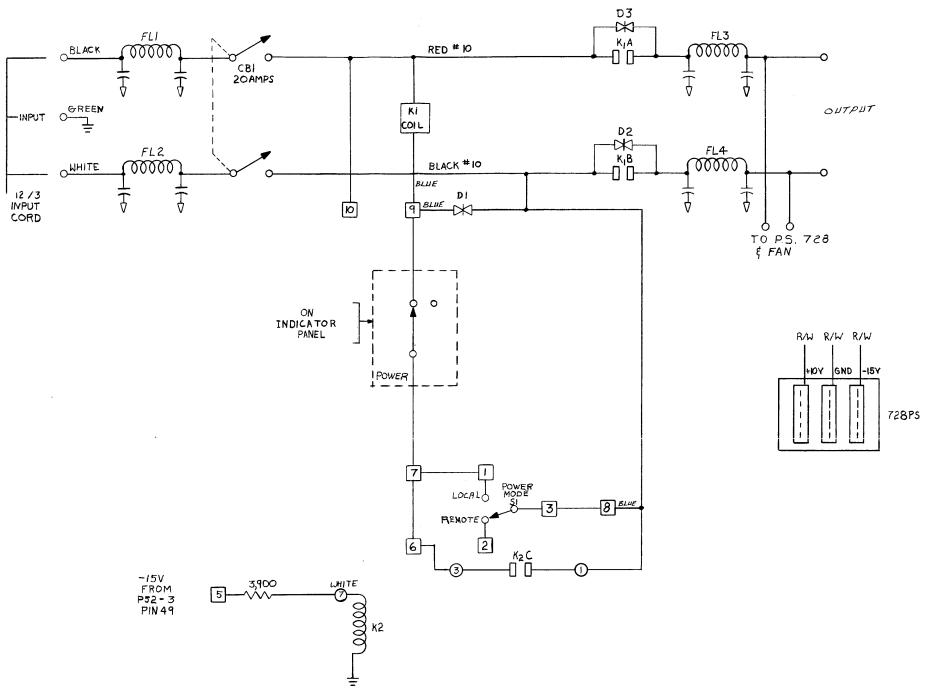

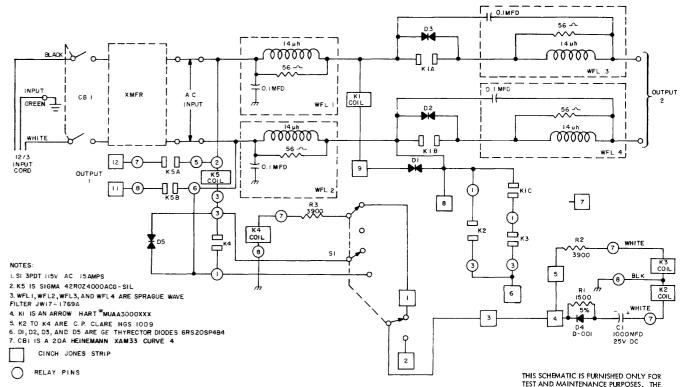

| 7-3    | Power Control Wiring for Tape Unit 50                        | A-128 |

|        | Power Control 811<br>Power Control 822                       | A-132 |

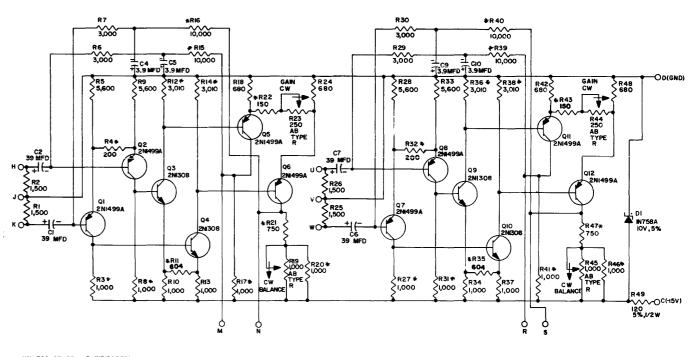

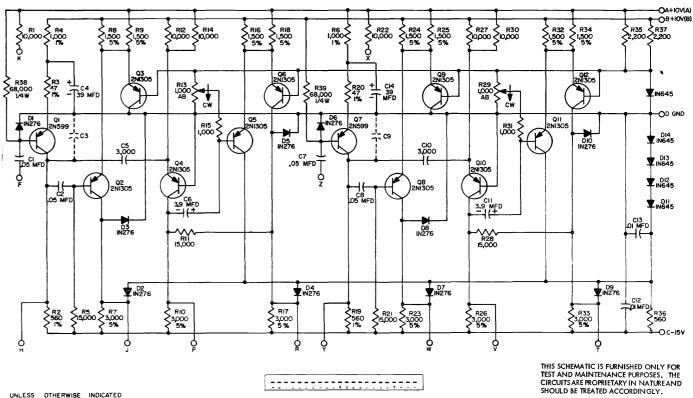

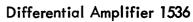

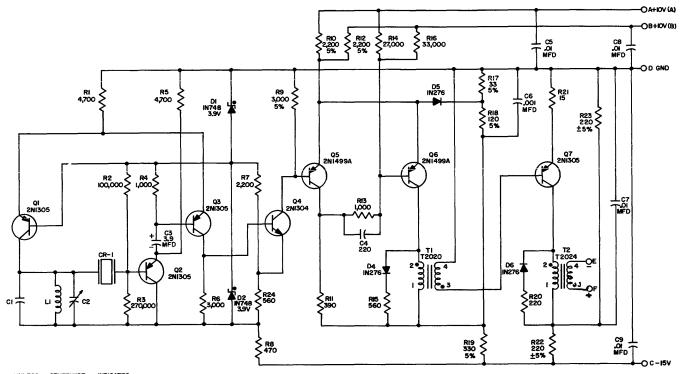

|        | Differential Amplifier 1536<br>Peak Detector and Slicer 1539 | A-134 |

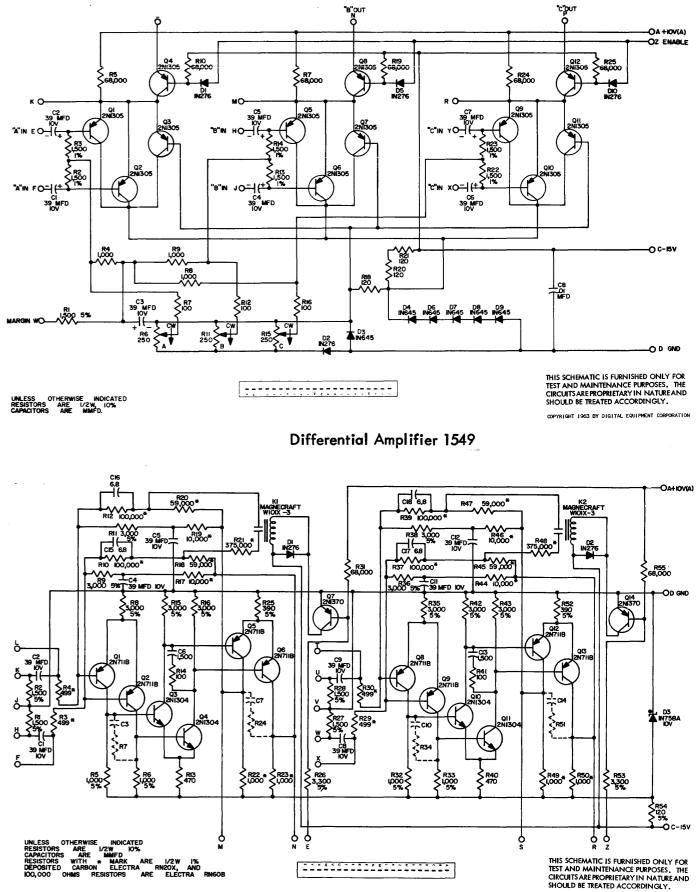

|        | Rectifying Slicer 1542<br>Differential Amplifier 1549        | A-136 |

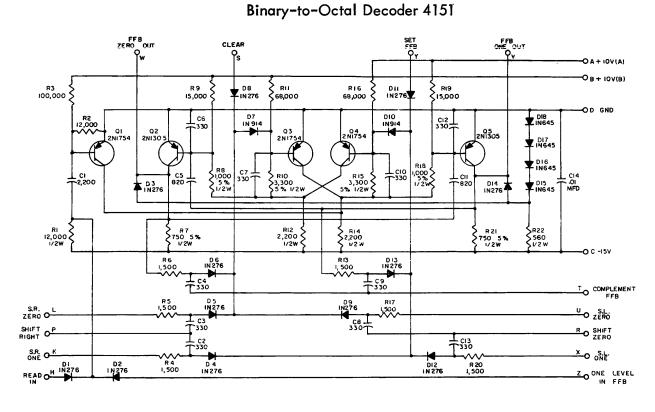

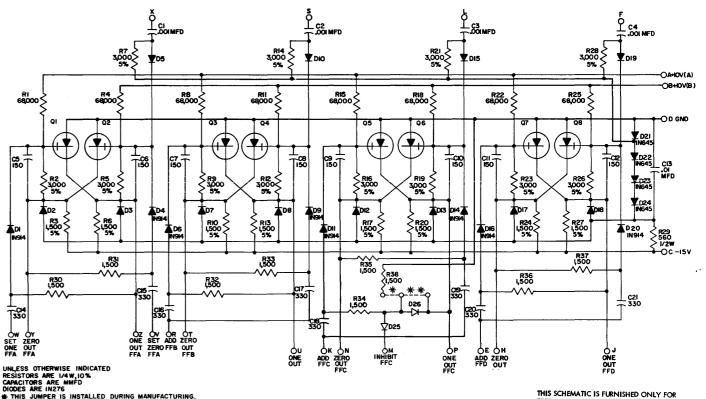

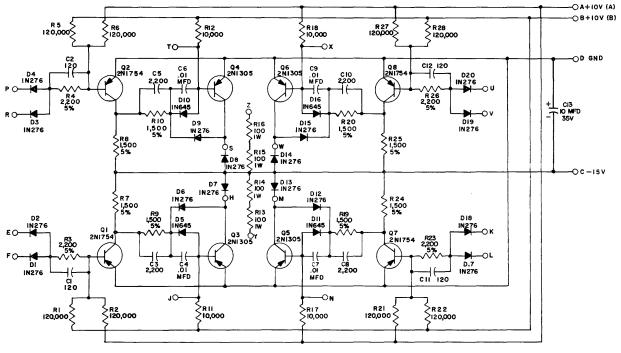

|        | Binary-to-Octal Decoder 4151<br>Dual Flip-flop 4202          | A-138 |

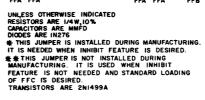

|        | Four-bit Counter 4215<br>Integrating Delay 4303              | A-140 |

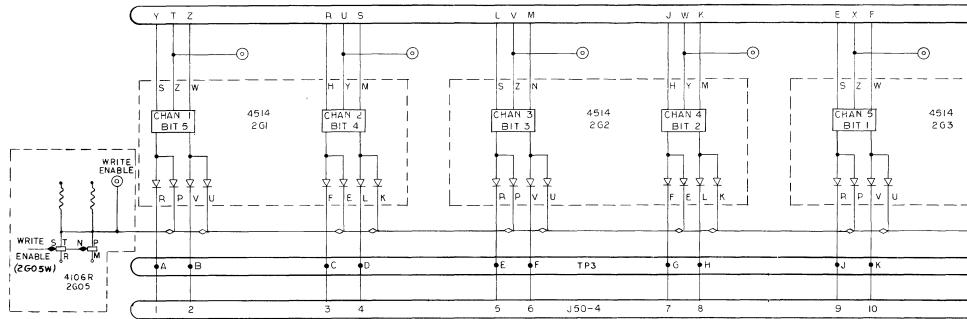

|        | Crystal Clock 4407<br>NRZ Writer 4514                        | A-142 |

| 8-1    | Magnetic Tape Unit Calibrator                                | A-144 |

| 8-2    | Unit Calibrator Logic                                        | A-146 |

| 8-3    | Calibrator Timing Chart                                      | A-150 |

| 8-4    | Tape System Module Layout, Types 50, 51 and 52               | A-152 |

| 8-5    | Bus Panel Taper Pin Layout for Type 50 Alone                 | A-156 |

| 8-6    | Bus Panel Taper Pin Layout for Types 50 and 51 Combination.  | A-160 |

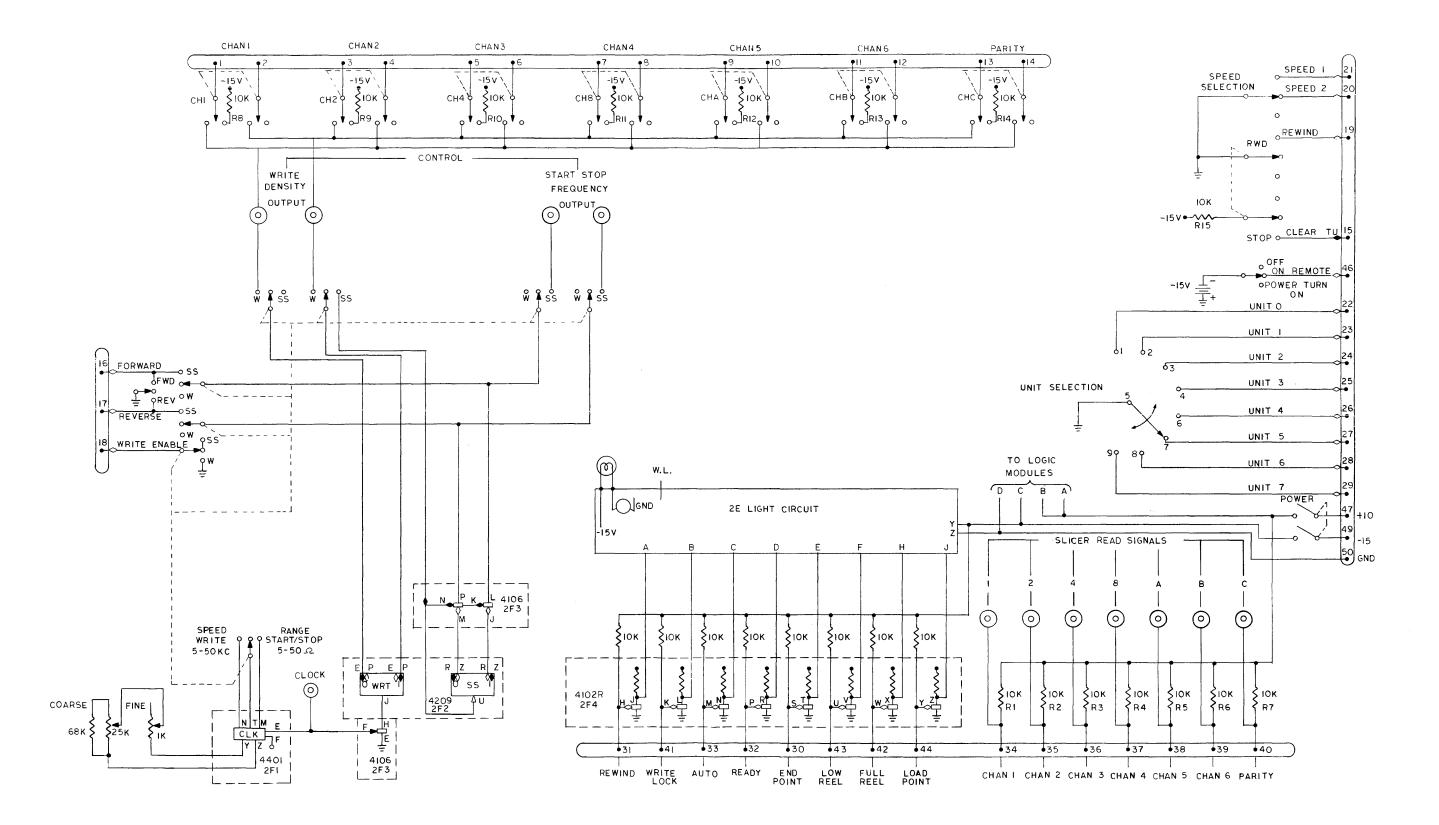

| 8-7    | Manual Control Panel Wiring                                  | A-164 |

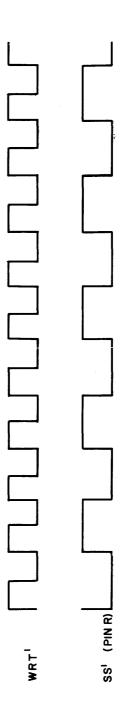

| 8-8    | Typical Waveforms                                            | A-168 |

|        |                                                              |       |

# LIST OF TABLES

| 4-1 | Type 52 Tape System Status                   | 4-16 |

|-----|----------------------------------------------|------|

| 6-1 | Type 52 System, General Functions            | 6-36 |

| 6-2 | Type 52 System, IOT Command Pulse Operations | 6-37 |

| 6-3 | Type 52 Tape Control Logic Levels            | 6-39 |

| 6-4 | Tape Unit Logic Functions                    | 6-40 |

| 6-5 | Type 51 System Operations                    | 6-43 |

Table

## INTRODUCTION

#### 1-1 PURPOSE AND SCOPE

The purpose of this instruction manual is to aid personnel in the installation, operation and maintenance of two magnetic tape systems used with the DEC Programmed Data Processor-1. This manual, a supplement to the basic PDP-1 Maintenance Manual, describes the Automatic Tape Control Unit, Type 52; the Programmed Tape Control Unit, Type 51; and the DEC-designed Local Tape Control, which is mounted in each Type 50 Tape Transport Unit. A separate manufacturer's manual for the tape transport is furnished with the tape system.

Throughout this manual an automatic tape system comprising a Type 52 Automatic Tape Control and one or more Type 50 Tape Units is referred to as a Type 52 System. A programmed tape system comprising a Type 51 Programmed Tape Control and one or more Type 50 Tape Units is referred to as a Type 51 System.

#### 1-2 CHAPTER SUBJECTS

A brief summary of system use and application is presented in Chapter 2, General Description. This chapter also lists system specifications and physical characteristics.

Chapter 3, Installation, provides instructions for initial installation and setup of the system.

Chapter 4, System Function, provides a full general description of all system operations. At block diagram level, Chapter 4 explains what the system does rather than describing the specific hardware and connections involved in the various functions. Also included in this chapter are descriptions of tape format, write and read signal flow and all magnetic tape instructions.

Chapter 5, Operating Procedures, explains the use of all controls and indicators on the tape system control panels, as well as the basic operating procedures for normal functions.

Chapter 6, Tape System Logic, presents a complete and detailed description of the logic in both tape control units and of the DEC-designed logic in the tape transport unit. This chapter also includes flow charts of all system operations. Chapter 7, Circuit Description, describes the function, specifications and circuit theory of all DEC System Modules not described in the basic PDP-1 manual.

Chapter 8, Maintenance, contains information useful in adjustment, calibration, troubleshooting and repair of the tape equipment. This chapter also describes the function and use of the DEC Tape Unit Calibrator.

## 1-3 FIGURES

This manual includes three general classes of figures: logic diagrams, circuit schematics, and miscellaneous figures such as photographs, flow charts, block diagrams and layout drawings. Complete system logic is shown in logic drawings for Chapter 6. This chapter also includes the flow charts. Circuit schematics accompany Chapter 7. Block diagrams, photographs and layout drawings illustrate the other chapters. Chapters 7 and 8 also include various cable and wiring diagrams.

Allfigures are assembled in numerical order at the back of the manual. References to all figures except circuit schematics are of the form "Figure 5-1" (i.e. the first figure of Chapter 5.) Circuit schematics are arranged in order by circuit type designation.

## GENERAL DESCRIPTION

## 2-1. PURPOSE OF SYSTEM

One of the many PDP-1 options is the magnetic tape system. This system provides computer input-output at a much faster rate than other peripheral devices, and may also be used as high capacity, slow access storage to augment core memory. Two kinds of tape option are available: automatic systems and programmed system. This manual describes one system of each kind.

The Type 52 Automatic Tape System transfers blocks of characters between computer memory and tape. By using the high speed channels it allows computation to continue while the transfer is in process. Special features include scatter read and gather write automatic bit-by-bit read-compare with core memory automatic lateral parity error detection while reading and writing and rapid tape search by skipping a preselected number of records. Tape format is standard IBM with choice of odd or even parity. Each automatic tape control can handle up to eight tape units. A maximum of three tape controls (for capability of 24 tape units) can be added to the PDP-1.

The Type 51 Programmed Tape System transfers information between computer and tape one character at a time. All transfer operations including error checking and assembly of characters into computer words must be performed by subroutines. Some choice of tape format is allowed including standard IBM. The programmed tape control can handle up to three tape units.

All tape system components are housed in standard DEC equipment frames and run on ordinary 60 cycle, 117 volt current. The control unit of the automatic system contains built-in marginal checking to facilitate preventive maintenance. No special wiring, subflooring or air conditioning is required.

## 2-2 SYSTEM COMPONENTS

Equipment comprising two of the PDP-1 tape systems is shown in Figure 2-1. Both systems include a tape control, the Programmed Tape Control Type 51, or the Automatic Tape Control Type 52. Each Type 50 Tape Transport Unit includes the DEC-designed Local Tape Control (read-write electronics) and two components designed by Potter Instrument Company: the M906II-1 Tape Transport, and the M3323 Drive Electronics Unit. The Type 51 or 52 Tape Control governs the tape unit through the local control. All motion and status signals between local control and the transport pass through the Potter drive electronics. Data signals, however, go directly between the read-write electronics and the read and write heads.

Both tape systems are governed from the in-out transfer control section of PDP-1. For the Type 52 Automatic System, six iot instructions are added to the computer repertoire. These instructions specify a tape unit, initial and final addresses, and a tape command. The Type 52 Control then selects the specified tape unit and executes the command automatically. This process is independent of further computer operations, so the computer may continue with the program. All required tape operations are executed by the Type 52 hardware. Each time the Type 52 Control has finished writing a word on tape or reading a word from tape, it gains direct access to memory through a high speed channel. Data transfers are made to or from consecutive memory locations, starting with the initial address and ending with the final address. Since the high speed channel control includes three channels, up to three Type 52 Controls (and hence 24 tape units) may be added to the computer.

The Type 51 Programmed Tape System, like the Type 52 System, is governed from iot control. However, all data transfers are made through the in-out register one character at a time. The five iot instructions added to the computer repertoire select the tape unit and its operating mode (read or write, odd or even parity, etc.) and initiate the individual character transfers. The write instruction transfers a character from the in-out register to the tape control to be written on tape; each character read from tape must be detected by the program and transferred to the in-out register by a read instruction. The program must also assemble the characters into words and deposit them in memory.

A typical automatic tape system including a Type 52 Tape Control and three tape units is shown in Figure 2-2. The tape control requires an entire bay and each tape unit, including a tape transport, is mounted in an additional bay. In a programmed system the tape units also require one bay each, but the Type 51 Control is mounted in the bottom of one of the tape unit bays.

## 2-3 SYSTEM OPERATING SPECIFICATIONS

SYSTEM PARAMETERS

Characters

Parity

Lateral

Longitudinal

Transfer rate

Density

Minimum record length (excluding longitudinal parity character)

Type 52 System

Type 51 System

Load point gap

Longitudinal parity character spacing

Inter-record gap

Recording

Errors detected

Type 52 System

Type 51 System

## TRANSPORT PARAMETERS

Tape

Speed Start time Start distance Stop distance Single unit stop-start interval Read-write heads Data protection Detected conditions 7 bits: 6 data, 1 parity

Odd or even Even 15,000 characters/second 200 characters/inch

3 characters 1 character 6" 0.020" 0.023" (4 character spaces) 3/4" NRZ

Parity, skipped character, readcompare, illegal command, late HSC access

Parity

1.5 mil polyester, 2400' long, 1/2" wide

75 ips

3 ms

0.15"

0.10"

10 ms

7 channel

Write enable ring

| Load point                         | 10' from physical beginning of tape |

|------------------------------------|-------------------------------------|

| Full reel                          | <100' of tape on takeup reel        |

| Low reel                           | <100' of tape on supply reel        |

| End point                          | 14' from physical end of tape       |

| Load point and end point detection | Photoelectric                       |

| Rewind speed                       | 300 ips                             |

| Rewind time                        | 1 3/4 minutes, full reel            |

| Reel diameter                      | 10 1/2"                             |

## 2-4 PHYSICAL CHARACTERISTICS

#### CONSTRUCTION

All magnetic tape equipment is housed in Standard DEC Bays (all steel construction). Control panels are aluminum.

## MODULES

Standard DEC System Plug-in units, series 1000 and series 4000.

## POWER EQUIPMENT

Power supplies series 700; power controls series 800.

## LOGIC

Solid state. Transistors and crystal diodes operating on static logic levels (0 vdc and -3vdc).

#### DIMENSIONS

Each DEC bay has the following dimensions:

1. . . •

Height 69 1/2 inches Width 22 inches Depth 26 inches

Usually, however, several units are bolted together — the overall length then being 20" per unit plus 2" for the end panels. For example, if a Tape Control Type 52 and three tape units are bolted together, total length is 82".

#### UNIT WEIGHTS

Tape Unit Type 50 (including transport and logic) 600 pounds

Tape Control Type 51 65 pounds

Tape Control Type 52 500 pounds

Each pair of unused end panels reduces system weight by 90 pounds.

2-5 POWER REQUIREMENTS

LINE VOLTAGE INPUT

105 to 125 volts, 60 cycle, single phase

CURRENT CONSUMPTION Tape Unit Type 50

7.5 amperes average, 740 watts. However, under heavy operating conditions, the tape unit may draw 20-ampere peaks.

Tape Control Type 51 Tape Control Type 52

2-6 EQUIPMENT LIST

4 amperes (6-ampere peaks), 410 watts

0.5 ampere, 60 watts

All PDP-1 tape equipment is housed in Standard DEC Bays. The front of each bay can accommodate up to 12 horizontal 19-inch mounting panels (DEC Type 1914). Each panel can hold 25S tandard DEC Plug-in Logic Modules. Inside the double doors at the back of each bay is an inner plenum door supporting the required power supplies and power controls.

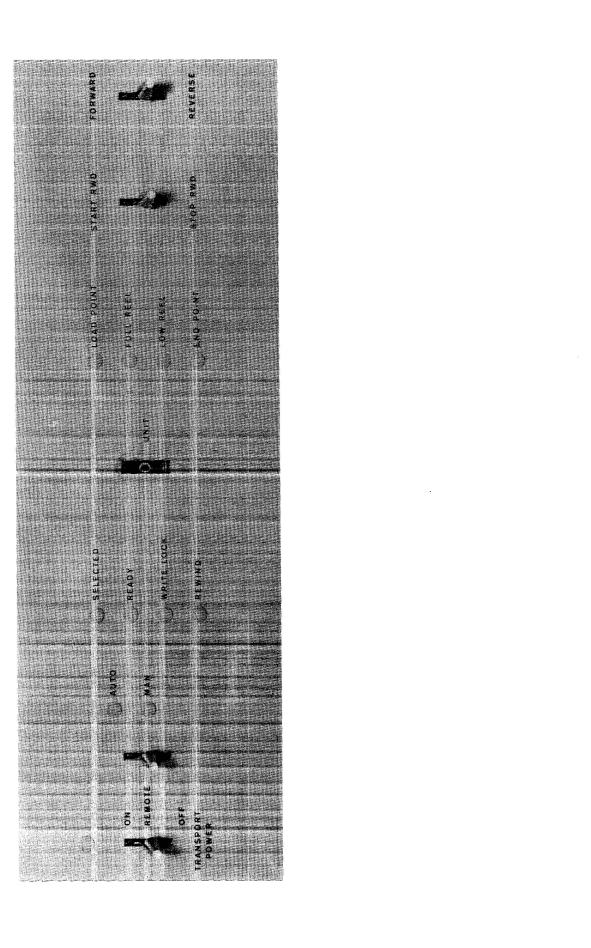

A typical automatic tape installation is shown in Figure 2-2. The Type 52 Tape Control (left) is bay 1. All tape units of a system are designated bay 2 for purposes of module location. The tape transport is behind the glass door on the front of the tape unit. The transport and the manual control panel together take up the upper half of the unit. Behind the double doors in the lower half are the logic, the drive electronics, a test panel and a bus socket panel.

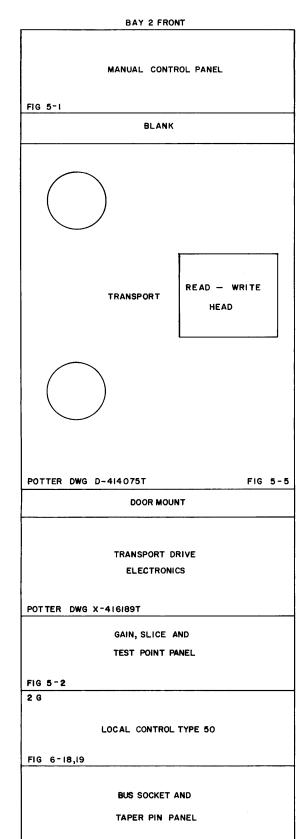

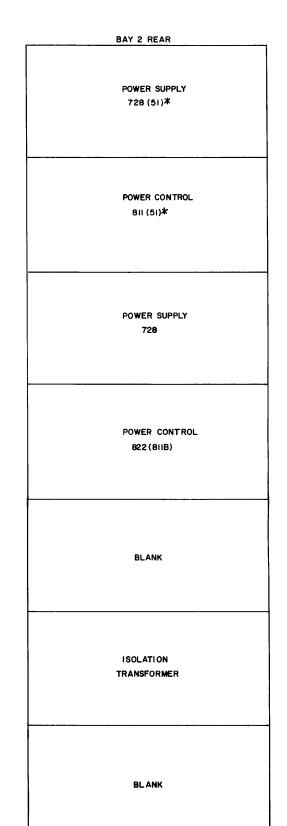

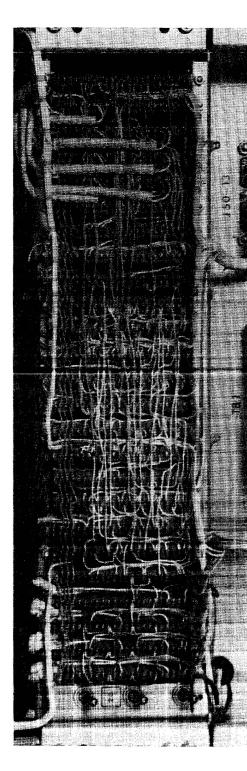

<u>a</u> LOGIC PANELS AND POWER EQUIPMENT - Complete front and back layouts of tape system bays 1 and 2 are shown in Figures 2-3 and 2-4. The front of bay 1 (Type 52 includes an indicator panel and seven mounting panels of logic. In general each mounting

panel contains a complete subsection of logic and is shown in a single logic drawing in Chapter 6. The figure number is at the lower left of each panel. On the back of bay 1 are a power control, the logic power supplies and a variable power supply for marginal checking.

The upper half of bay 2 (tape unit) contains the tape transport and the manual control panel. The components listed in the layout drawing (Figure 2-4) are also shown in Figure 2-5, a photograph of the tape unit with the double doors open. Below the transport is the drive electronics: test points and fuses on the left, plug-in modules on the right. The DEC tape unit equipment, below the drive electronics, includes the gain, slice and test ponit panel, the logic for local tape control and the bus socket and taper pin panel for cable connections between tape control and tape unit. The unit shown in Figure 2-5 is unit 1 of a programmed tape system. Below the bus socket panel is the logic for the Programmed Tape Control Type 51. In all units of a Type 52 System and in units 2 and 3 of a Type 51 System, this logic is replaced by a blank panel.

The back of the tape unit (Figure 2-4) includes an isolating transformer, a power control and a power supply for the Type 50 Logic. However, in unit 1 of the Type 51 System, an additional power control and power supply for the Type 51 Logic are mounted at the top of the plenum door.

The following table lists the mounting panel and power equipment requirements for the three tape system components described in this manual.

Tape Transport Unit Type 50 (Figure 2-4)Space requirement1 bayLogic1 mounting panel (2G)Power equipment1 power supply 7281 power control 822 (811B)1 isolation transformerProgrammed Tape Control Type 51 (Figure 2-4)Logic1 mounting panel (2H)Power equipment1 power supply 7281 power supply 7281 power control 811

## Automatic Tape Control Type 52 (Figure 2-3)

| Space requirement | 1 bay                        |  |

|-------------------|------------------------------|--|

| Logic             | 7 mounting panels (1A to 1H) |  |

| Power equipment   | 3 power supplies 728         |  |

|                   | 1 variable power supply 734  |  |

|                   | 1 power control 811          |  |

<u>b</u> MODULE LIST - The following list includes all plug-in modules required by local tape control in the Type 50, Programmed Tape Control Type 51 and Automatic Tape Control Type 52. Circuits indicated by an asterisk (\*) are described in Chapter 7 of this manual. All other circuits are described in Chapter 10 of the basic PDP-1 manual.

Local Tape Control

| Туре                                     | Quantity   |

|------------------------------------------|------------|

| Differential Amplifier 1536*<br>or 1549* | 4          |

| RectifyingSlicer 1542*                   | a <b>3</b> |

| Indicator Driver 1669                    | 1          |

| Inverter 4105                            | 5          |

| Inverter 4106R                           | 1          |

| Diode 4112R                              | . 3        |

| Diode 4113                               | 2          |

| Delay 4301                               | 1          |

| NRZWriter 4514*                          | 4          |

Programmed Tape Control Type 51 and Automatic Tape Control Type 52 – Numbers in parentheses indicate modules that must be added to PDP-1 iot control to govern the tape system.

|                                | Quantity |         |  |

|--------------------------------|----------|---------|--|

| Туре                           | Type 51  | Туре 52 |  |

| Delay 1304                     |          | 1       |  |

| Peak Detector and Slicer 1539* | 4        | 4       |  |

| Indicator Driver 1669          |          | 5       |  |

| Bus Driver 1685                |          | 8 (1)   |  |

|                               | Quan    | tity    |

|-------------------------------|---------|---------|

| Туре                          | Type 51 | Type 52 |

| Inverter 4105                 | 2 (1)   | 14      |

| Inverter 4106                 |         | 2       |

| Inverter 4106R                | 1       | 9       |

| Diode 4111                    | 1       | 4       |

| Diode 4112                    |         | 2       |

| Diode 4112R                   |         | 1       |

| Diode 4113                    | 2       | 13      |

| Diode 4113R                   | 2       | 3       |

| Capacitor–Diode 4126          |         | 6       |

| Capacitor–Diode 4127          | 2       | 5       |

| Capacitor–Diode 4127R         |         | 4       |

| Capacitor–Diode 4128          | 2       | 14      |

| Binary-to-Octal Decoder 4151* |         | 1       |

| Dual Flip-Flop 4202*          |         | 9       |

| Dual Flip-Flop 4209           |         | 2       |

| Quadruple Flip-Flop 4213      |         | 5       |

| Quadruple Flip-Flop 4214      | 4       | 11      |

| 4–Bit Counter 4215*           | 2       | 2       |

| Delay 4301                    | 2       | 17      |

| Integrating Delay 4303*       |         | 3       |

| Clock 4401                    |         | 1       |

| Clock 4407*                   |         | 1       |

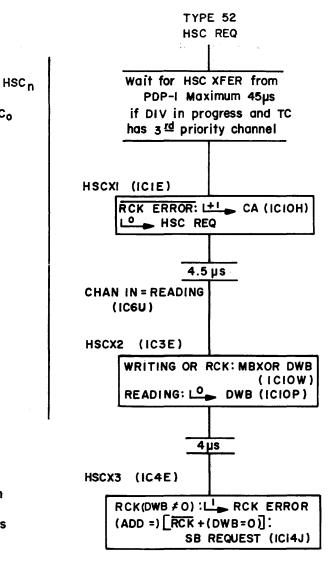

| Pulse Amplifier 4603          | 1 (4)   | 15 (4)  |

|                               |         |         |

## INSTALLATION

## 3-1 SITE SELECTION

Before installing a magnetic tape system, select a suitable location near the PDP-1 computer. The Tape Control Type 52 must be installed within 25 feet of the computer. Furthermore, the tape units must be within 25 feet of the tape control. In the programmed system the Type 51 Tape Control is mounted in tape unit 1 so the entire system must be within 25 feet of the computer.

All system equipment frames are 69 1/2" high. The floor area occupied by the system depends upon the number of tape units that are included (equipment dimensions are given in paragraph 2-4). Usually the equipment frames are bolted together in groups. At least 3 feet of clearance should be allowed on all sides of the equipment for access during maintenance.

A level floor is required because the equipment frames are mounted on casters. The floor should be capable of supporting 150 psf.

The system is designed to operate efficiently from 50° to 100°F. The plug-in modules are cooled by blowing air out the front of the bays. Intake fans are factory-installed in the floor of all DEC bays, and in the top of each tape unit bay as well. No additional cooling equipment is required.

All units run on ordinary 115 volt, 60 cycle current. Since each bay has its own ac line, a separate outlet must be provided for every unit. Tape units should each be connected to a 20 ampere line. A 10 ampere line is sufficient for the Type 52 Tape Control. All cables are equipped with Miller Electric Type 034-2 Connectors.

## 3-2 INSTALLATION

The bays containing the tape control and the tape units are usually bolted together into one or two large equipment frames. However, the drive electronics and the isolation transformer for each tape unit are packed separately and must be installed before the system is ready for use. All cabling within a single equipment frame is installed at the factory. All cables necessary to connect the different frames are packed in a single separate container. Thus a tape system including one Type 52 Control and three tape units would be shipped as a single large equipment frame and seven additional containers: three contain drive electronics units, three contain isolation transformers, and one contains the necessary cables.

<u>a</u> UNPACKING – Each equipment frame is shipped on a skid. The frame is wrapped in plastic, a wooden cover is placed on the top, and the entire package is held on the skid with metal straps. The tape unit subassemblies and cables are shipped separately in ordinary packing containers.

(1) Carefully remove the metal straps, wooden cover and plastic from the equipment frame. Remove the frame from the skid and place as desired near the PDP-1.

(2) The plenum doors at the rear of the bays have spring catches. To reinforce these doors during shipment two screws are used to hold each door shut. Remove these screws and store them in the plastic loops provided.

(3) Remove any packing material, shipping blocks, etc., from the inside of the frame.

(4) The plug-in modules are taped into the logic panels to prevent damage in shipment. Remove the tape.

(5) Unpack the cables, transformers and drive electronics units.

NOTE: If the user plans to reship the equipment (or move it more than a short distance) in the near future, special packing materials should be saved for reuse. The containers for drive electronics units and transformers, in particular, are designed especially to accommodate the equipment and are the safest means of packing it for reshipment.

<u>b</u> INSTALLATION OF SUBASSEMBLIES – The user must install a drive electronics unit and an isolation transformer in each tape unit. Mount the drive electronics just below the tape transport with the fuses at the left end of the unit (see Figure 2-4). The mounting bolts are already in place at the sides of the bay front, behind the double doors. Correct mounting of the unit is shown in Figure 2-4 of the Potter Handbook.

Two cables connect the drive electronics to the rest of the tape unit. The cable from the Type 50 Logic is coiled and taped to the bay floor. Remove the tape and plug this cable

into the smaller receptacle at the back of the drive electronics. The cable from the tape transport is coiled and taped around the transport motors. Remove the tape and plug this cable into the larger receptacle at the back of the drive electronics.

The isolation transformer must be mounted on the second panel from the bottom on the inside of the plenum door at the rear of the bay (see Figure 2-4). The mounting bolts and connecting cables for the transformer are already in place. Each cable is marked by a numbered tag. On the front of the transformer are two sets of terminals covered with plastic plates. On the plastic are strips of tape bearing corresponding terminal numbers. Connect the cables to the matching transformer terminals.

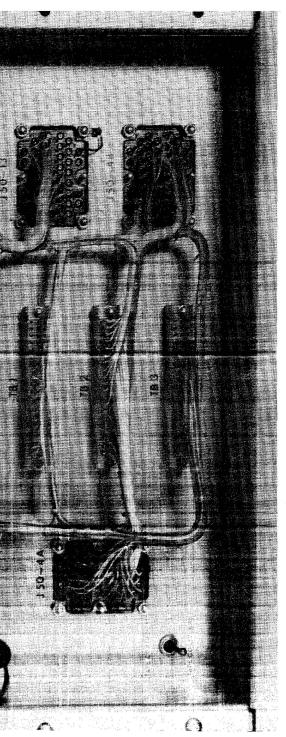

<u>c</u> BUS CONNECTIONS - At the bottom of each tape unit is a bus socket and taper pin panel (Figure 3-1). The socket in the upper right provides connection to the manual control panel at the top of the unit. The other two sockets are for the tape control bus (TC bus).

All tape units are connected to a single bus from the tape control. The TC bus enters each tape unit at the left of the socket panel and leaves at the lower right. Connections between the two sockets are made through the taper pins in the center of the panel. There are three taper pin blocks, each containing three horizontal rows of pins. In all three blocks, connections from the in-bus are made to the center row, while connections to the out-bus are made from the bottom row. Connections to the Type 50 Logic and to the socket for the control panel connector are made from the top row.

All cables within a single equipment frame are installed at the factory. However, bus connections between the tape system and the computer, and between separate equipment frames within the system, must be made at the site.

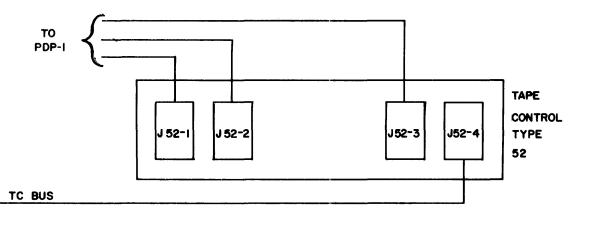

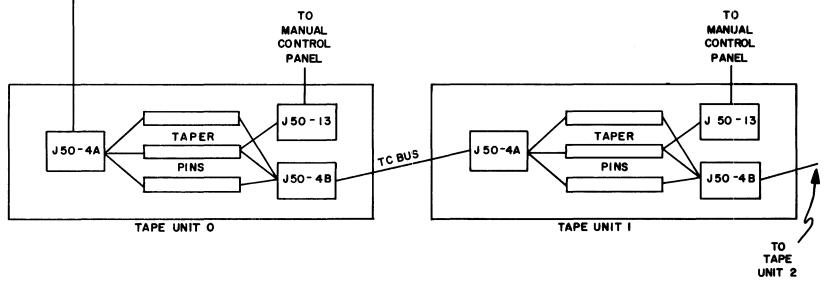

Bus connections for the Type 52 Tape System are shown in Figure 3-2. A panel containing four bus sockets is located at the bottom of the Type 52 Control. Three cables connect the tape system to the in-out transfer control section of the PDP-1. The in-out plugs at the computer are labelled to correspond to the bus sockets at the tape control: J52-1, -2 and -3. The TC bus socket, J52-4, is equivalent to J50-4A and J50-4B in all tape units. If the system is divided between two equipment frames, J50-4B in the last unit of the first frame must be connected to J50-4A in the first unit of the second frame. The bus connections for the Type 51 Tape System are shown in Figure 3-3. Since the Programmed Tape Control Type 51 is mounted in tape unit 1, and all three units are bolted into a single frame, only one bus need be installed. This connects the computer to J51-4 at the left of the unit 1 socket panel. Connections to the Type 51 Control are made directly from J51-4. Connections between the Type 51 and the rest of the tape system are then made through the taper pins. Note, however, that the bus connections in tape units 2 and 3 are just the opposite of those in the units of the Type 52 System. The bus connections are reversed in order that all tape units except unit 1 of the Type 51 System will have the same taper pin wiring. The unit that contains the Type 51 Logic must provide voltage to the unit calibrator through the out-bus. Reversing the bus connections prevents the mixing of logic voltages between two adjacent units.

## 3-3 INSPECTION AND CHECKOUT

The tape system is thoroughly tested and checked before it leaves the factory. However, it should be inspected and checked again after installation to make sure that no damage has occurred during shipment.

<u>a</u> INSPECTION - After the tape equipment has been unpacked and installed, the system should be inspected visually. Check the following:

(1) Have a drive electronics unit and an isolation transformer been installed in every tape unit?

(2) Have all bus connections between computer and tape system been made properly?

(3) Have all shipping blocks, packing materials, tape, etc. been removed? A coiled ac power line is taped to the fan at the bottom of each bay. Remove the tape but do not plug in the power lines.

(4) Are all plug-in units inserted firmly in position?

(5) Are there any loose nuts or bolts?

(6) Are there any loose or broken wires?

<u>b</u> PREOPERATIONAL CHECKOUT - Before using the tape system make sure that the entire system turns on and off properly and that the tape transport functions correctly. The checkout

procedure makes use of the following switches:

The POWER switch and indicator located at the lower right of the Type 52 Indicator Panel;

The TRANSPORT POWER switch and indicator located at the left end of the tape unit manual control panel;

The circuit breakers and LOCAL/REMOTE switch on each Type 811 and 822 (811B) Power Control.

All switches and indicators in the tape system are described in detail in paragraphs 5-2 and 5-3. The following checkout procedure is complete for both the Type 52 and Type 51 Tape Systems. For either system merely ignore those steps that refer only to the other. All steps that refer to the tape unit should be performed on all tape units.

(1) Make sure computer power is off.

(2) Turn OFF the TRANSPORT POWER switch on the manual control panel. Turn off (down) the Type 52 POWER switch.

(3) Load a tape into the tape unit. Complete tape loading procedure is described in paragraph 5-4.

(4) Switch the 811 and 822 power controls to REMOTE.

(5) Plug in the ac lines and make sure all 811 and 822 circuit breakers are closed. All units should remain off.

(6) Switch the 822 power control to LOCAL. This applies power to the Type 50 Logic.

(7) Set TRANSPORT POWER to REMOTE. Nothing should happen.

(8) Push TRANSPORT POWER to the momentary contact ON position. The transport should go on, lighting the associated indicator. When the switch is returned to RE-MOTE, power remains on.

(9) Switch the 882 power control to REMOTE. All tape unit power including the transport goes off.

(10) Turn on (up) the Type 52 POWER switch.

(11) Switch the 811 power control into LOCAL. With Type 52 this turns on the power indicator and applies power to the entire tape system. With the Type 51, both the 811 and the unit 1 822 power controls must be switched to LOCAL. This turns on only the Type 51 Logic and unit 1. (To turn on the entire system, switch all power controls to LOCAL.)

(12) Switch the 811 power control to REMOTE. With the Type 52, the entire tape system should go off. With the Type 51 all power controls must be returned to REMOTE to turn off the entire system.

- (13) Turn on the computer. The entire tape system should go on with the computer.

- (14) Turn off the computer. The entire tape system should go off.

- (15) Check the operation of the tape transport as described in paragraph 5-5.

## SYSTEM FUNCTION

## 4-1 LOGICAL ORGANIZATION

The logical configuration of the PDP-1 Type 52 Automatic Magnetic Tape System is shown in Figure 4-1. The Tape Control Type 52 functions as an automatic buffer between the computer and the tape units. Program iot instructions govern the entire tape system by providing addresses and commands to the tape control. The tape control then goes into automatic operation, regulating both its own operations and those of the addressed tape unit. All data transfers between tape system and computer are made directly to memory through a high speed channel.

To place the tape system in operation the program must provide three types of information:

- 1. It must select a tape unit by providing a unit address.

- 2. It must specify the quantity of data to be processed by providing a pair of memory addresses. These addresses define a range of memory locations for retrieval or storage of data through a high speed channel.

- 3. It must tell the system what to do with the data by providing a tape command.

The program performs the first two functions through the address logic, the third through the command logic.

The address logic contains three registers and an equality net. The program provides these three registers with tape unit, initial and final addresses. For each tape operation the tape control selects a tape unit according to the unit address (UA). The first HSC access to memory is made according to the initial address. Subsequently, the initial address becomes the current address (CA). The tape control keeps count of data transfers by incrementing this current address by 1 on each HSC access. When the current address becomes equal to the final address (FA), the equality net indicates that the operation is complete. This equal address condition produces a sequence break in the computer. If the program then resets the initial and final addresses before termination takes place, the operation continues.

Besides providing addresses to the tape control, the program must also provide a tape command to the command register (CR). The command is decoded to govern the operation of both the tape control and the selected tape unit. The control portion of the Type 52 contains two parts: in-out control and format control. Basically, in-out control governs the transfer of information between computer and tape control, while format control governs transfers between tape control and tape unit. In-out control governs program initiation of all tape operations, transfers of data through a high speed channel and requesting of sequence breaks. All status levels for both tape control and tape unit are also provided to the computer by in-out control.

Format control includes logic for the sequences of operations that produce the correct tape format in writing and that respond properly to the same format in reading. Format control also generates high speed channel requests whenever a full computer word has been read or written; it provides timing for the termination of a tape operation in order to produce the correct record gap; it positions the tape properly with respect to the read and write heads.

Data is transferred between computer memory and tape through a set of three data transfer registers. All transfers between computer and tape system are full-word transfers between the memory buffer and the 18-bit data word buffer (DWB). In writing, format control divides the word in DWB into three characters which are made available to the tape through the single-character write buffer (WB). In reading, format control assembles three consecutive characters from the single-character read buffer (RB) into a full word in DWB.

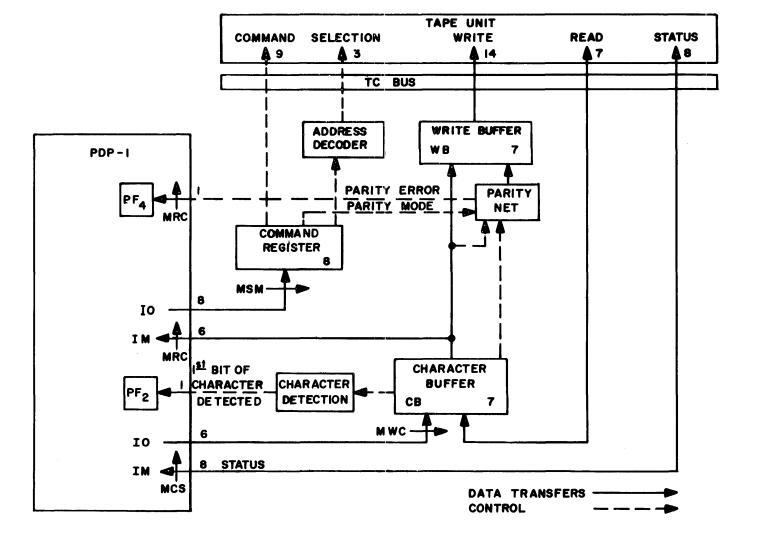

In the programmed tape system, the Type 52 Control is replaced by a Type 51 and no use is made of high speed channels or sequence break system. All command information and data are transferred through the in-out register and most control and address functions must be provided by the computer. The Type 51 Control includes only a pair of single-character buffers for data transfer and a command register which includes bits for tape unit selection. All data transfers are single-character transfers, made completely under program control. In writing, the program must transfer each character to the character buffer (CB); it is then made available to the tape through the write buffer (WB). In reading, the character buffer doubles as a read buffer, and the program must transfer each character to the in-out register. The command register specifies the tape unit operating mode but governs no functions in the tape control except parity mode.

#### 4-2 TAPE FORMAT

PDP-1 magnetic tape units use 1/2" wide tape containing 7 information channels. The tape format produced by the Type 52 Automatic Tape Control is shown in Figure 4-2. With the Type 51 Programmed Tape Control the computer may provide the necessary timing to duplicate this format or may write the tape in some other format if desired.

The left part of Figure 4-2 shows the tape in relation to the read and write heads. The tape moves by the heads vertically — forward direction being downward. The tape is composed of a mylar base coated on one side with an iron oxide composition. The oxide or dull side of the tape faces the heads, with the left edge toward the transport drive plate. The recording rate of 15,000 characters/second means that one character is written every 66.67 microseconds. Since the tape moves at 75 ips, there are 200 characters/inch, and the characters are spaced 0.005 inches apart.

The method of recording used is nonreturn-to-zero (NRZ). Although the tape has two basic states of remanent magnetization, the remanent magnetic state of the tape at a given bit position does not determine the value of that bit. A logical 1 is represented by a change from one state of magnetization to the other, in either direction. A logical 0 is represented by a constant state of magnetization. Thus, writing a character containing all 0s is equivalent to producing blank tape. Each time a character is transferred into the write buffer, the NRZ writers produce an equivalent character on the tape. Because of the NRZ type of recording however, a transfer into the buffer is not a normal 1 transfer. Instead, whenever a 1 is to be written in a given tape channel, the corresponding bit of the buffer is complemented, producing a change in tape magnetization.

The structure and spacing of the individual tape characters are shown at the right in Figure 4-2. Each 18-bit computer word is divided into three 6-bit characters in DWB. The write buffer, however, contains seven flip-flops corresponding to the seven tape channels. A parity bit is transferred into the buffer with each 6-bit data character, producing a tape character of six data bits and a lateral parity bit. Channel 1 contains the least significant data bit; channel 6, the most significant. The parity of the character may be either odd or even, as specified by the program.

In reading the tape, only 1s are detected. If odd parity is used, there must be a 1 in at least

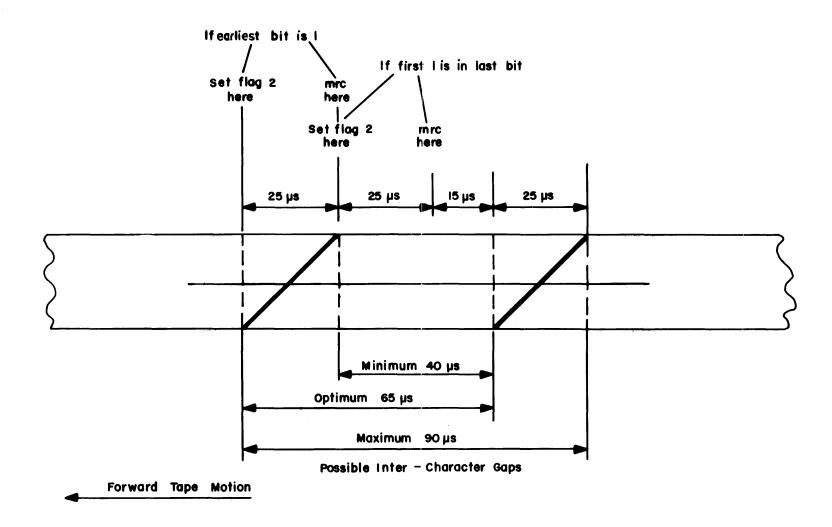

one channel of every character so that all characters will be detected. However, if six 0 data bits are written with even parity, a character containing all 0s is produced. This is equivalent to a character space and is interpreted by the system as a missing character error. After the first 1 bit of a character is detected, the tape control waits 25 microseconds for the read buffer to receive all the bits in the character. This procedure allows a tape skew of up to 0.0018" without loss of information.

The smallest unit of information that can be written on the tape is a record. Since each word is divided into three characters, a record contains 3n data characters, where n is the number of words provided by the computer for a given write operation. After the last data character is written, the tape control writes 0.020" of blank tape (270 microseconds at 75 ips), and then clears the write buffer to produce an end-of-record character (EOR). A complete record therefore contains 3n+1 characters, that is, 3n data characters and the EOR character. Since the write buffer flip-flops always begin a record in the 0 state, returning the buffer to its initial state at the end of the record produces even longitudinal parity in all tape channels.

The smallest unit of information that can be read by the tape control is also an entire record. This does not mean, however, that the entire record must be deposited in computer memory. In a read operation, the program specifies initial and final addresses for transfer of information to memory. If, when the addresses become equal, they are reset within 100 microseconds, the operation continues. If the addresses remain equal for longer than the allowed time, all high speed channel transfers to memory cease, but the tape control continues reading until the end of record is reached. If the address range specified by the program is greater than the number of words in the record, the tape stops at the end of the record even though the addresses have not become equal.

In all normal tape operations, therefore, the tape always stops so that both the read head and the write head are within the record gap. The distance that the EOR character moves beyond the read head, in combination with the delay before writing is allowed, always produces at least 3/4" of blank tape between records. Since only 1s are written on the tape (the failure to detect a 1 during the reading of a character is interpreted as a 0) the absence of write signals during a write operation erases the tape, i.e. produces blank tape. The actual position of the heads within the gap depends upon the type of operation just completed. The EOR character always moves slightly further beyond the heads in writing than in reading. This prevents

generation of inter-record trash, which can be produced by failing to erase the entire record gap when writing on a previously recorded tape.

Since the spacing between the read and write heads is 0.30", every character passes the read head 4 milliseconds after it is written. Thus in a write operation the characters are read in order to check for parity or missing character errors, but no transfers beyond the read buffer occur.

Besides detecting changes in magnetization through the read head, the tape unit also includes a photoelectric system for sensing beginning and end of tape and a mechanical system for detecting low tape supply. The low reel condition (less than 100 feet of tape on the supply reel) is provided to the tape control as a status condition but is not used within the tape unit. In the rewind operation, the full reel condition (less than 100 feet of tape on the takeup reel) returns the tape unit to normal speed for the remainder of the rewind and the tape finally halts at load point. The load point and end point of the tape are marked by reflective strips mounted on the side of the tape away from the heads. These strips are detected by photodiodes which sense light reflected from them. In writing on a newly mounted or rewound tape, a gap of 6" is left from the load point before writing can begin. If the tape should run to the end point in any operation the tape unit stops automatically.

## 4-3 TAPE WRITE AND READ SIGNAL FLOW

Figure 4-3 is a block diagram of the tape system write and read paths for a single channel. The write path begins at the write buffer in the tape control and ends at the tape, while the read path begins at the tape and ends at the tape control read buffer. Most of the equipment shown in the figure is located physically in the read-write electronics of the tape unit.

In the write path, both outputs of a WB flip-flop are connected to an NRZ writer whose three outputs are in turn connected to the two ends and centertap of a write head inductor. The NRZ writer contains a pair of semiconductor switches. If the write enable level is not asserted, both switches are off and no current flows in the inductor. However, if write enable is asserted, one (and only one) switch must be on because the two switches are controlled by complementary outputs of a WB flip-flop. If the upper switch is closed, current flows through the upper coil in the direction shown by the arrow. If the lower switch closes, current flows through the low-er coil.

The tape control writes information on the tape by complementing the WB bit. So long as a given WB bit remains in the same state, the corresponding writer switch remains closed, and current still flows through the same half of the write head coil. This is equivalent to writing 0s on the tape every 66.7 microseconds. Whenever a 1 is to be written on the tape, the WB bit is complemented; this reverses the states of the two writer switches, causing current to flow in the other half of the coil. This, in turn, changes the direction of magnetization in the tape channel. Current flow through the two halves of the coil for writing a typical tape message is shown by the graphs above and below the current lines. A similar graph represents the direction of tape magnetization for the same message as shown at the right.

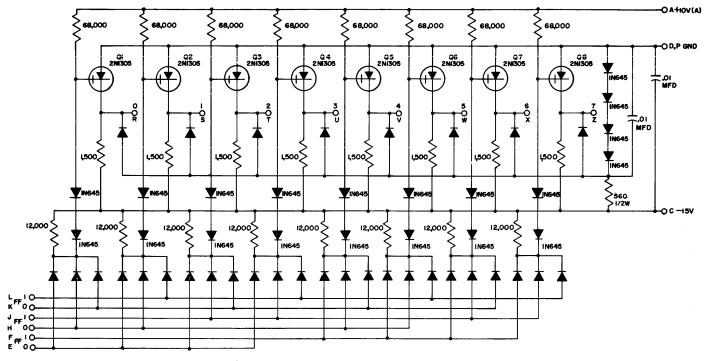

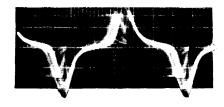

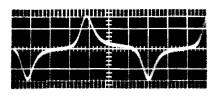

A tape passes the read head 4 milliseconds after passing the write head. So long as the direction of tape magnetization remains the same, no current flows in the read head coil. However, when the read head encounters a change in the direction of magnetization, current flows through the coil. Each change causes current flow in the opposite direction from the preceding change. Typical current flow for two consecutive tape 1s is shown by the waveforms above the connecting lines from the coil to the differential amplifier.

The differential amplifier provides considerable amplification for difference signals but only fractional amplification for common mode signals. Amplifier waveforms are shown to the left. The amplifier also includes a balance potentiometer to assure that the output signals are the same amplitude regardless of polarity.

The output of the differential amplifier is applied to a rectifying slicer. No slicer output can be generated unless the read enable level is asserted. This prevents the sending of read signals to the tape control when tape is in motion but is not being read as, for example, in the rewind operation. The rectifying slicer generates a negative output pulse for an input pulse of either polarity from the differential amplifier. However, no slicer output is generated unless the input exceeds a threshold level. Thus a low level noise input cannot generate an output pulse.

The rectifying slicer output feeds a peak detector and slicer in the tape control. The pulse produced through the read path from the read head is long compared to the duration of most logic levels within the tape control. Therefore, for the time during which the input pulse exceeds a preset threshold level, the slicer portion of the peak detector and slicer produces a logic level output. Further, the peak detector produces a logic pulse output at the peak of the input pulse. The two outputs — a logic level and a pulse — are applied to a capacitor-diode gate to set a flip-flop in the read buffer.

#### 4-4 TYPE 52 TAPE INSTRUCTIONS

With the installation of a Type 52 Automatic Tape System, eight in-out transfer instructions are added to the PDP-1 repertoire. Each of these instructions is executed in a single computer memory cycle of 5 microseconds. In order to place the tape system in operation, the program must execute the two initiating instructions. These provide the necessary addresses and tape commands. The tape system then executes the command automatically. When the addressequal condition occurs during a tape operation, the program may provide new initial and final addresses through the two reset instructions without stopping the tape operation in process. The automatic tape instructions also include a pair of examine instructions (through which the program may check the condition of the tape system) and a pair of maintenance instructions. The entire set of eight instructions uses the iot primary operation code and six of the secondary operation codes (both maintenance instructions use the same second code as one of the reset instructions). Furthermore, one of the initiating instructions has a third 4-bit operation code. This third code is the tape command which is executed by the tape control.

In all magnetic tape instructions, bits 6 and 7 of the instruction word (denoted by 'ab' in the instruction code) select the tape control. The three tape controls are addressed at 00, 01 and 10. If there is only one tape control these bits are ignored. In the following list the instruction codes are given in octal with capital letters representing variable octal digits. Whenever binary digits are necessary, they are given as 1s and 0s in parentheses or are represented by lower case letters. For convenience, the tape control is often referred to as the TC, while the tape unit is referred to as the TU. In some instructions, reference is made to various status bits. These correspond to the tape status conditions and are described under the instruction mes. Each status bit number corresponds to its position in the in-out register when tape status is examined by mes.

#### Initiating Instructions:

## Magnetic Tape Unit and Final Address .....

.....muf Instruction Code 72abxC76

The  $C(AC_{15-17})$  replace C(UA);  $C(IO_{2-17})$  replace C(FA). The unit address transferred to UA selects that TU whose unit selector is set to the same address. If the program is about to initiate a read or write command, the memory address transferred to FA must be 1

greater than the desired final address to which high speed channel access is to be made during execution of the command. However, if the program is about to initiate a space command, the number transferred to FA must be 1 less than the total number of records to be spaced over.

If the selected TC is not busy, muf is properly executed and the computer skips the next instruction in sequence. If TC is busy, muf is performed as a nop and the computer goes on to the next instruction in sequence. In either event, C(IO) and C(AC) remain unchanged.

Bits 5, 8 and 9 of the instruction are ignored. Bits 10 and 11 (octal digit C) adjust the states of the continue flip-flops in order to select one of three possible end-of-record actions. When the end of a record is reached, the tape control clears the busy flip-flop (status bit 3) and returns a completion pulse to the computer. If the sequence break system is on, the TC requests a break. The three end-of-record actions are as follows:

(1) Normal Completion and Stop, C=0. Upon reaching the end-of-record, the tape stops with the head at the appropriate distance past the EOR character. The tape control waits 10 milliseconds to allow the pinch rollers to settle down and then returns the completion pulse.

(2) Early Completion and Stop, C=1. Upon reaching the end-of-record, TC returns the completion pulse immediately. Thus the programmer can use the same TC to initiate a tape command on a different TU while the previously selected TU is stopping. This saves 10 milliseconds of program time.

(3) Early Completion and Continue, C=3. Upon reaching the end-of-record, TC returns the completion pulse immediately, and the previously selected TU continues in operation. During a 2 millisecond interval following the completion pulse, the program must provide new initiating instructions. In this manner many records can be processed without stopping the tape. If new instructions are not given within the allotted time, TC repeats the previous command with Early Completion and Stop, producing the following results:

(a) If the previous command was Write, the tape control writes a complete record gap and then stops with the heads at the appropriate distance in a second gap.

(b) If the previous command was Read or Readcheck, the tape control processes

the next record. HSC transfers continue until the addresses become equal, but the tape control reads to the end-of-record in the normal manner. Since the completion pulse at the end of the first record clears the busy flip-flop, the processing of the second record can be interrupted by a new muf instruction. Use of this procedure to read two records with a single pair of initiating instructions is therefore not recommended.

(c) If the previous command was Forward Space or Backspace, the tape control spaces the tape to the end of the reel. Since any number of records can be spaced with a single tape command, Early Completion and Continue should not be specified with a space command unless the command is definitely intended to be changed.

## Magnetic Tape Initial Address and Command .....

.....mic Instruction Code 72abnN75

Bits 8 through 11 of the mic instruction ( $MB_{8-11}$ ) replace C(CR); C( $IO_{2-17}$ ) replace C(CA). This instruction also sets the TC busy flip-flop, clears the HSC request flip-flop and clears the status flip-flops which indicate tape system errors. The mic instruction contains a third operation code nN which specifies the tape command that the system is to perform. As soon as nN is transferred into the command register, the tape control begins automatic operations and places in operation the tape unit selected by the previous muf. The memory address for initial high speed channel access is provided from IO to the current address register. As each word is processed the current address is incremented by 1 so that the next HSC access will be made to the next consecutive memory location. For space commands, IO should contain zero.

Bit 5 of mic is ignored. If the selected TC is not busy and the TU selected by the previous muf is ready, mic is properly executed, and the computer skips the next instruction in sequence. If either TC or TU are not available, mic is performed as a nop and the computer goes on to the next instruction in sequence. In either event, C(IO) remain unchanged.

The following table lists the tape commands with their mnemonic codes and octal codes. The octal code is given as the center pair of octal digits in the instruction word when tape control 0 is selected. That is, the code represents abnN with a and b both 0. To provide a tape command to TC 1, add 20 to the code as given; to provide a command to TC 2, add 40. All

commands that generate or check parity have two codes: even code for even parity, odd for odd parity.

| Command                         | Mnemonic Code | Octal Code |

|---------------------------------|---------------|------------|

| Stop                            | mst           | 00         |

| Rewind                          | mrw           | 01         |

| Backspace                       | mbs           | 02, 03     |

| Forward Space Check Even Parity | mfe           | 10         |

| Forward Space Check Odd Parity  | mfo           | 11         |

| Write Even Parity               | mwe           | 12         |

| Write Odd Parity                | mwo           | 13         |

| Read and Compare Even Parity    | mce           | 14         |

| Read and Compare Odd Parity     | mco           | 15         |

| Read Even Parity                | mre           | 16         |

| Read Odd Parity                 | mro           | 17         |

<u>Stop</u> - This command should only be used immediately after the return of a completion pulse following a muf instruction that called for early completion and continue with same unit. Stop clears the command register, halting the tape.

<u>Rewind</u> - This command merely initiates the rewind operation — the tape unit then completes it automatically. The tape control returns the completion pulse 10 microseconds after Rewind is given. The program may then use the same tape control to operate another unit while the previously selected unit is rewinding.

<u>Space</u> - For Backspace and Forward Space commands, the number of records spaced (i.e. skipped over) is equal to C(FA) - C(CA) + 1. To space five records, for example, load 4 into FA and 0 into CA. Besides spacing, Forward Space checks for parity errors and missing characters. Any errors discovered are indicated by status bits 1 and 2 respectively.

<u>Write</u> - Normally the tape control writes the first word of the record 6 milliseconds after tape motion begins. However, if the tape is at load point, TC waits 78 milliseconds to produce the load point gap before starting the first

record. Writing then continues at the rate of one word every 200 microseconds until the current and final addresses become equal. When the address-equal condition occurs, status bit 7 is set, and a sequence break is requested if the sequence break system in on. The address of the last word taken from memory is C(FA) - 1.

The tape continues in motion in order to write the three characters of the final word. If the addresses are changed by reset instructions within 100 microseconds after the address-equal condition occurs, the write operation continues. This process is called "gather write." That is, information contained in scattered areas of memory can be gathered and written on tape as a single continuous record. If the address-equal condition still exists when the third character of the final word is written, the tape control automatically writes 0.020" of blank tape and an EOR character.

If Write is executed with the addresses equal initially, one record gap is written and one of the end-of-record actions is taken. Controlled lengths of blank tape can be written in this manner by using Early Completion and Continue.

Since the tape passes the read head after passing the write, head every character is read and checked 4 milliseconds after it is written. If a parity error or missing character error occurs, it is indicated by the appropriate status bit. Writing a character composed of seven 0s is equivalent to writing blank tape; it produces a missing character error. In PDP-1 Concise Code, such a 0 character can be generated by writing a space or tape feed character with even parity.

<u>Read</u> - Normally the tape control retrieves the first word of a record approximately 10 milliseconds after tape motion begins. However, if the read operation begins at load point,TC must wait approximately 82 milliseconds while the load point gap passes by the read head. After the first character is detected the record is processed at the rate of one word every 200 microseconds. As soon as the third character of each word is read, the system requests high speed channel access to memory in order to deposit the word. HSC access must be granted before the next character is encountered or an HSC Late error occurs. Reading continues until the addresses become equal or the end-of-record is encountered.

When the address-equal condition occurs, status bit 7 is set and a sequence break is requested if the sequence break system is on. At this time the address of the last word stored in memory is C(FA) - 1. Tape motion continues and the tape control retrieves the next word from the record. If the program resets the addresses within 100 microseconds after address-equal occurs (i.e. before the system finishes retrieving the next complete word), the normal read operation continues. This process is called "scatter read." That is, information read from a single continuous record can be stored in scattered areas of memory.

If the addresses are not reset, HSC transfers to memory cease, but the tape continues to the end-of-record. If the address reset is delayed beyond the allotted time, the normal read operation restarts, but information retrieved from the tape during the delay is lost. In any event, whether or not the addresses become equal beforehand, Read terminates at the end of the record.

When the end-of-record is encountered, the system returns a completion pulse either at the normal time or earlier, depending upon the previously selected end-of-record action. The completion pulse clears status bit 3 (indicating that the TC is no longer busy) and requests a sequence break if the sequence break system is on. If the end-of-record action specifies that system operation will continue with the same tape unit, tape motion continues at normal speed into the next record. The address of the last word stored in memory is C(CA) - 1. Note that if the total range of memory locations specified by the initiating and reset instructions is greater than the number of words in the record, CA and FA will not be equal when Read ends.

Parity errors or missing character errors detected while reading a record are indicated by the appropriate status bits. The read operation is not affected by the discovery of errors. However, if a character is skipped, all subsequent words transferred to memory are offset by one character, i.e. all characters retrieved from the tape are packed sequentially in memory. If the system is not at the third character of a word when the end-of-record is encountered, HSC access is requested, and the final partial word is deposited in memory, left justified.

<u>Read and Compare (Readcheck)</u> - This operation retrieves information from tape in exactly the same manner as Read. All timing, address reset operations, termination by address-equal or end-of-record conditions, end-of-record actions taken, etc. are exactly the same as for Read. However, in readchecking, each time a complete word is assembled in the data word buffer it is not transferred to the computer. Instead the HSC access is used to retrieve a word from the currently addressed memory location. The two words are then compared bit by bit by producing their exclusive OR function in DWB. If DWB does not contain zero after the comparison, a readcheck error is indicated.

When a readcheck error occurs, status bit 4 is set and the Readcheck ceases, but tape motion continues until the end-of-record is encountered. The address of the last word taken from memory which correctly compared with the corresponding word retrieved from tape is C(CA) - 1.

Reset Instructions:

Magnetic Tape Reset Final Address .....

....mrf Instruction Code 72ab(0)067

The  $C(IO_{2-17})$  replace C(FA); C(IO) remain unchanged. This instruction resets the final address to allow HSC transfers to proceed for gather write, scatter read or gather readcheck. In all other respects the operation specified by the initiating instructions continues. To be effective, mrf must be given within 100 microseconds after the address-equal condition occurs. Usually both reset instructions are used together, in which case both must be given within the 100-microsecond interval.

Bits 5, 9 and 11 of mrf are ignored. However, bits 8 and 10 must be 0. If either of these bits is 1, a maintenance instruction results.

Magnetic Tape Reset Initial Address .....

....mri Instruction Code 72abxxcx66

The  $C(IO_{2-17})$  replace C(CA); C(IO) remain unchanged. Furthermore, bit 10 of the mri instruction (represented by 'c' in the instruction code) replaces  $C(CR_{10})$  in the command register. This instruction provides a new initial address to allow further HSC transfers for gather write,

scatter read and gather readcheck. Moreover, by adjusting the state of CR<sub>10</sub>, the instruction also allows the programmer to change the current command from Read to Readcheck, or vice versa.

Since mri clears CR<sub>10</sub> before transferring bit 10 into it, the program must also provide the appropriate bit if continuation of the original operation is desired. To read or write after the address reset, bit 10 must be 1; to readcheck, it must be 0.

The mri instruction must be given within 100 microseconds after the address-equal condition occurs. Usually both reset instructions are used, in which case both must be given within the 100-microsecond interval.

### Examine Instructions:

### Magnetic Tape Examine Status...mes Instruction Code 72abxX35

The various status bits replace C(IO). The status bits are unaffected by the instruction. Bits 5 and 8 to 11 of mes are ignored. Following transfer of status information to IO, the program can determine the status of the selected TC and selected TU by checking the states of the 18 IO bits.

The 18 status bits are listed and described in Table 4-1. The left column lists the IO bits; the center column lists the status condition that causes the corresponding IO bit to be set by mes. The status condition may be either a flip-flop or a logic level; flip-flops are indicated by an 'f' in parentheses. The last column lists the meaning of the status condition. Conditions examined are those for the TC selected by mes and the TU specified by the unit address provided by the last muf.

### Magnetic Tape Examine Location...mel Instruction Code 72abxX36

The C(CA) replace  $C(IO_{2-17})$ ;  $IO_{0,1}$  are cleared. The address of the last HSC access to memory is 1 less than the address transferred into IO by this instruction.

Bits 5 and 8 to 11 of mel are ignored. To examine the current address while a record is being processed, execute two mel instructions and accept the results only if they are identical. This procedure prevents the program from accepting an erroneous address should the transfer occur while CA is in a dynamic state.

# Maintenance Instructions:

Two special instructions are available for maintenance and diagnostic operations. These instructions bypass all interlocks in the tape control. Both instructions use the same second op code (67) as mrf, and they therefore reset the final address according to C(IO) at the same time that they perform their maintenance functions.

# Initiate HSC Request.....inr Instruction Code 72ab(0)267

This instruction sets flip-flop HSC REQ, causing TC to request high speed channel access. Use made of such access depends upon the tape operation currently being performed.

#### Clear Command Register.....cr Instruction Code 72ab(1)067

This instruction halts the tape by clearing the command register. This procedure is the only way, under program control, to halt tape motion while a record is being processed. The ccr instruction is particularly useful for adjusting the transport start-stop characteristics.

### 4-5 TYPE 52 SYSTEM LOGIC

Figure 4-4 is a detailed block diagram of the Type 52 Automatic Tape Control. This figure shows the registers and many of the logic nets in the Type 52 as well as the connections from the tape control to the computer and the tape units. The number of physical lines required for each connection is indicated by a number written on the line in the figure. For example, transfer of information from data word buffer to memory buffer requires 18 lines. A pulse that gates information into a register (usually an iot command pulse) is shown as an arrow drawn across the transfer line into the register. The name of the pulse, or pulses, is written at the base of the arrow. Solid lines represent data transfers; dotted lines represent control.