# Digital Equipment Corporation Maynard, Massachusetts

RT02-A 30 character keyboard remote terminal maintenance manual

DEC-00-HRT2A-C-D

RT02-A 30 character keyboard remote terminal maintenance manual

digital equipment corporation · maynard, massachusetts

.

1st Edition, November 1972 2nd Printing (Rev) May 1973 2nd Edition December 1973

-

ä.,

# Copyright © 1972, 1973 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DEC       | PDP          |

|-----------|--------------|

| FLIP CHIP | FOCAL        |

| DIGITAL   | COMPUTER LAB |

# CONTENTS

-

.

-

| CHAPTER 1                                                                                                                                                                            | INTRODUCTION AND DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1                                                                                                                                                                                  | PURPOSE AND SCOPE                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1.1.1                                                                                                                                                                                | Related Documentation 1-1                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1.2                                                                                                                                                                                  | BASIC DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1.2.1                                                                                                                                                                                | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1.2.2                                                                                                                                                                                | Physical Description                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1.3                                                                                                                                                                                  | EQUIPMENT SPECIFICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1.4                                                                                                                                                                                  | REFERENCING CONVENTIONS AND TERMINOLOGY                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CHAPTER 2                                                                                                                                                                            | INSTALLATION                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.1                                                                                                                                                                                  | SITE PLANNING                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.2                                                                                                                                                                                  | INSTALLATION                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.2.1                                                                                                                                                                                | Unpacking                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.2.2                                                                                                                                                                                | Primary AC Power                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2.2.3                                                                                                                                                                                | RT02-A Power Connections 2-2                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.2.4                                                                                                                                                                                | Interface Cabling                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.2.4.1                                                                                                                                                                              | Teletypewriter Interface                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.2.4.2                                                                                                                                                                              | EIA Interface                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.2.5                                                                                                                                                                                | Communications Module Interconnection                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2.3                                                                                                                                                                                  | INITIAL CHECKS                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2.3.1                                                                                                                                                                                | Preparation for the Off-Line Display Check                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                      | • •                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.3.2<br>2.3.3                                                                                                                                                                       | RT02-A Off-Line Display Check                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.3.3                                                                                                                                                                                | RT02-A On-Line Transmit and Receive Display Check                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CHAPTER 3                                                                                                                                                                            | OPERATION AND PROGRAMMING                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3.1                                                                                                                                                                                  | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.1                                                                                                                                                                                  | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3.1<br>3.2                                                                                                                                                                           | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3.1<br>3.2<br>CHAPTER 4                                                                                                                                                              | INTRODUCTION       3-1         RT02-A OPERATION       3-1         PRINCIPLES OF OPERATION       3-1                                                                                                                                                                                                                                                                                                                                                |

| 3.1<br>3.2<br>CHAPTER 4<br>4.1                                                                                                                                                       | INTRODUCTION       3-1         RT02-A OPERATION       3-1         PRINCIPLES OF OPERATION       4-1                                                                                                                                                                                                                                                                                                                                                |

| <ul> <li>3.1</li> <li>3.2</li> <li>CHAPTER 4</li> <li>4.1</li> <li>4.2</li> </ul>                                                                                                    | INTRODUCTION3-1RT02-A OPERATION3-1PRINCIPLES OF OPERATION3-1TERMINAL ORGANIZATION4-1TERMINAL INTERFACING4-1MODULE OPERATIONAL DESCRIPTIONS4-2                                                                                                                                                                                                                                                                                                      |

| 3.1<br>3.2<br>CHAPTER 4<br>4.1<br>4.2<br>4.3                                                                                                                                         | INTRODUCTION3-1RT02-A OPERATION3-1PRINCIPLES OF OPERATION3-1TERMINAL ORGANIZATION4-1TERMINAL INTERFACING4-1MODULE OPERATIONAL DESCRIPTIONS4-2Keyboard and Keyboard Encoder4-2                                                                                                                                                                                                                                                                      |

| <ul> <li>3.1</li> <li>3.2</li> <li>CHAPTER 4</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.3.1</li> <li>4.3.1.1</li> </ul>                                                       | INTRODUCTION3-1RT02-A OPERATION3-1PRINCIPLES OF OPERATION3-1TERMINAL ORGANIZATION4-1TERMINAL INTERFACING4-1MODULE OPERATIONAL DESCRIPTIONS4-2Keyboard and Keyboard Encoder4-2Transmit Mode Sequence4-7                                                                                                                                                                                                                                             |

| 3.1<br>3.2<br>CHAPTER 4<br>4.1<br>4.2<br>4.3<br>4.3.1<br>4.3.1.1<br>4.3.2                                                                                                            | INTRODUCTION3-1RT02-A OPERATION3-1PRINCIPLES OF OPERATION3-1TERMINAL ORGANIZATION4-1TERMINAL INTERFACING4-1MODULE OPERATIONAL DESCRIPTIONS4-2Keyboard and Keyboard Encoder4-2Transmit Mode Sequence4-7                                                                                                                                                                                                                                             |

| 3.1<br>3.2<br>CHAPTER 4<br>4.1<br>4.2<br>4.3<br>4.3.1<br>4.3.1.1<br>4.3.2<br>4.3.2.1                                                                                                 | INTRODUCTION3-1RT02-A OPERATION3-1PRINCIPLES OF OPERATION4-1TERMINAL ORGANIZATION4-1TERMINAL INTERFACING4-1MODULE OPERATIONAL DESCRIPTIONS4-2Keyboard and Keyboard Encoder4-2Transmit Mode Sequence4-7Communications Module4-8Transmit Mode4-10                                                                                                                                                                                                    |

| 3.1<br>3.2<br>CHAPTER 4<br>4.1<br>4.2<br>4.3<br>4.3.1<br>4.3.1<br>4.3.1.1<br>4.3.2<br>4.3.2.1<br>4.3.2.2                                                                             | INTRODUCTION3-1RT02-A OPERATION3-1PRINCIPLES OF OPERATION4-1TERMINAL ORGANIZATION4-1TERMINAL INTERFACING4-1MODULE OPERATIONAL DESCRIPTIONS4-2Keyboard and Keyboard Encoder4-2Transmit Mode Sequence4-7Communications Module4-8Transmit Mode4-10Receive Mode4-12                                                                                                                                                                                    |

| 3.1<br>3.2<br>CHAPTER 4<br>4.1<br>4.2<br>4.3<br>4.3.1<br>4.3.1<br>4.3.2<br>4.3.2.1<br>4.3.2.2<br>4.3.2.3                                                                             | INTRODUCTION3-1RT02-A OPERATION3-1PRINCIPLES OF OPERATION3-1TERMINAL ORGANIZATION4-1TERMINAL INTERFACING4-1MODULE OPERATIONAL DESCRIPTIONS4-2Keyboard and Keyboard Encoder4-2Transmit Mode Sequence4-7Communications Module4-8Transmit Mode4-10Receive Mode4-12TTY and EIA Input and Output Converters4-13                                                                                                                                         |

| 3.1<br>3.2<br>CHAPTER 4<br>4.1<br>4.2<br>4.3<br>4.3.1<br>4.3.1<br>4.3.2<br>4.3.2.1<br>4.3.2.2<br>4.3.2.2<br>4.3.2.3<br>4.3.2.4                                                       | INTRODUCTION3-1RT02-A OPERATION3-1PRINCIPLES OF OPERATION3-1TERMINAL ORGANIZATION4-1TERMINAL INTERFACING4-1MODULE OPERATIONAL DESCRIPTIONS4-2Keyboard and Keyboard Encoder4-2Transmit Mode Sequence4-7Communications Module4-8Transmit Mode4-10Receive Mode4-12TTY and EIA Input and Output Converters4-13Clock and Frequency Divider4-15                                                                                                          |

| 3.1<br>3.2<br>CHAPTER 4<br>4.1<br>4.2<br>4.3<br>4.3.1<br>4.3.1.1<br>4.3.2<br>4.3.2.1<br>4.3.2.2<br>4.3.2.3<br>4.3.2.3<br>4.3.2.4<br>4.3.3                                            | INTRODUCTION3-1RT02-A OPERATION3-1PRINCIPLES OF OPERATION4-1TERMINAL ORGANIZATION4-1TERMINAL INTERFACING4-1MODULE OPERATIONAL DESCRIPTIONS4-2Keyboard and Keyboard Encoder4-2Transmit Mode Sequence4-7Communications Module4-8Transmit Mode4-10Receive Mode4-12TTY and EIA Input and Output Converters4-13Clock and Frequency Divider4-16                                                                                                          |

| 3.1<br>3.2<br>CHAPTER 4<br>4.1<br>4.2<br>4.3<br>4.3.1<br>4.3.1<br>4.3.2<br>4.3.2.1<br>4.3.2.2<br>4.3.2.2<br>4.3.2.3<br>4.3.2.4                                                       | INTRODUCTION3-1RT02-A OPERATION3-1PRINCIPLES OF OPERATION3-1TERMINAL ORGANIZATION4-1TERMINAL INTERFACING4-1MODULE OPERATIONAL DESCRIPTIONS4-2Keyboard and Keyboard Encoder4-2Transmit Mode Sequence4-7Communications Module4-8Transmit Mode4-10Receive Mode4-12TTY and EIA Input and Output Converters4-13Clock and Frequency Divider4-15                                                                                                          |

| 3.1<br>3.2<br>CHAPTER 4<br>4.1<br>4.2<br>4.3<br>4.3.1<br>4.3.1.1<br>4.3.2<br>4.3.2.1<br>4.3.2.2<br>4.3.2.2<br>4.3.2.3<br>4.3.2.4<br>4.3.3<br>4.3.4                                   | INTRODUCTION3-1RT02-A OPERATION3-1PRINCIPLES OF OPERATION4-1TERMINAL ORGANIZATION4-1TERMINAL INTERFACING4-1MODULE OPERATIONAL DESCRIPTIONS4-2Keyboard and Keyboard Encoder4-2Transmit Mode Sequence4-7Communications Module4-8Transmit Mode4-10Receive Mode4-12TTY and EIA Input and Output Converters4-13Clock and Frequency Divider4-16Self-Scan Panel Display4-18                                                                               |

| 3.1<br>3.2<br>CHAPTER 4<br>4.1<br>4.2<br>4.3<br>4.3.1<br>4.3.1.1<br>4.3.2<br>4.3.2.1<br>4.3.2.2<br>4.3.2.3<br>4.3.2.3<br>4.3.2.4<br>4.3.3<br>4.3.4<br>4.3.4<br>1<br>CHAPTER 5        | INTRODUCTION3-1RT02-A OPERATION3-1PRINCIPLES OF OPERATION4-1TERMINAL ORGANIZATION4-1TERMINAL INTERFACING4-1MODULE OPERATIONAL DESCRIPTIONS4-2Keyboard and Keyboard Encoder4-2Transmit Mode Sequence4-7Communications Module4-8Transmit Mode4-10Receive Mode4-12TTY and EIA Input and Output Converters4-13Clock and Frequency Divider4-16Self-Scan Panel Display4-18Gas Discharge Tube Operation4-19MAINTENANCE                                    |

| 3.1<br>3.2<br>CHAPTER 4<br>4.1<br>4.2<br>4.3<br>4.3.1<br>4.3.1.1<br>4.3.2<br>4.3.2.1<br>4.3.2.2<br>4.3.2.2<br>4.3.2.3<br>4.3.2.4<br>4.3.3<br>4.3.4<br>4.3.4<br>1<br>CHAPTER 5<br>5.1 | INTRODUCTION3-1RT02-A OPERATION3-1PRINCIPLES OF OPERATION4-1TERMINAL ORGANIZATION4-1TERMINAL INTERFACING4-1MODULE OPERATIONAL DESCRIPTIONS4-2Keyboard and Keyboard Encoder4-2Transmit Mode Sequence4-7Communications Module4-8Transmit Mode4-10Receive Mode4-12TTY and EIA Input and Output Converters4-13Clock and Frequency Divider4-15M7395 Display Control Module4-16Self-Scan Panel Display4-18Gas Discharge Tube Operation4-19MAINTENANCE5-1 |

| 3.1<br>3.2<br>CHAPTER 4<br>4.1<br>4.2<br>4.3<br>4.3.1<br>4.3.1<br>4.3.2<br>4.3.2.1<br>4.3.2.2<br>4.3.2.3<br>4.3.2.3<br>4.3.2.4<br>4.3.3<br>4.3.4<br>4.3.4<br>1<br>CHAPTER 5          | INTRODUCTION3-1RT02-A OPERATION3-1PRINCIPLES OF OPERATION4-1TERMINAL ORGANIZATION4-1TERMINAL INTERFACING4-1MODULE OPERATIONAL DESCRIPTIONS4-2Keyboard and Keyboard Encoder4-2Transmit Mode Sequence4-7Communications Module4-8Transmit Mode4-10Receive Mode4-12TTY and EIA Input and Output Converters4-13Clock and Frequency Divider4-16Self-Scan Panel Display4-18Gas Discharge Tube Operation4-19MAINTENANCE                                    |

# **CONTENTS** (Cont)

Page

.

| 5.2.2     | RT02-A Diagnostic Programs for the PDP-11 5-6 |

|-----------|-----------------------------------------------|

| 5.2.3     | RT02-A System Exercising 5-6                  |

| 5.2.3.1   | PDP-8 Systems Exerciser DEC/X8                |

| 5.2.3.2   | PDP-11 System Exercising 5-7                  |

| 5.3       | PREVENTIVE MAINTENANCE 5-7                    |

| 5.3.1     | Mechanical Checks                             |

| 5.3.2     | Electrical Checks                             |

| 5.4       | CHECKS AND ADJUSTMENTS 5-8                    |

| 5.4.1     | Basic Operational Check 5-8                   |

| 5.4.2     | Keyboard Check                                |

| 5.4.3     | Keyboard Encoder Check 5-9                    |

| 5.4.4     | M7390 Communications Module Checks            |

| 5.4.4.1   | Parallel Input Check                          |

| 5.4.4.2   | M7390 Module Serial Output Check              |

| 5.4.4.3   | M7390 Module Serial Input Check               |

| 5.4.4.4   | EIA Serial Input Circuitry Check              |

| 5.4.4.5   | TTY Serial Input Circuitry Check              |

| 5.4.4.6   | Data Available Output Check                   |

| 5.4.4.7   | Parallel Data Output Check                    |

| 5.4.4.8   | RT02-A Basic Timing Check                     |

| 5.4.5     | Display Control Module Checks                 |

| 5.4.5.1   | Transmit/Receive Clock Checks                 |

| 5.4.5.2   | Control Signal Checks                         |

| 5.4.6     | Self-Scan Checks                              |

| 5.5       | ASSEMBLY/DISASSEMBLY                          |

| 5.5.1     | Module Handling                               |

| 5.5.2     | MOS Device Handling                           |

| 5.5.3     | Cover Removal                                 |

| 5.5.4     | Front Panel Removal                           |

| 5.5.5     | Keyboard Removal                              |

| 5.5.6     | ON/OFF Indicator (LED-1) Removal              |

| 5.5.7     | Display Panel (Self-Scan) Removal 5-25        |

| 5.5.8     | Plug-In Module Removal                        |

| 5.5.9     | Logic Module Assembly (Vertical Adjustment)   |

| 5.5.10    | Power Supply Removal                          |

| 5.6       | RECOMMENDED SPARE MODULES AND COMPONENTS      |

| CHAPTER 6 | RT02-A ENGINEERING DRAWINGS                   |

| 6.1       | APPLICABLE ENGINEERING DRAWINGS               |

| 6.2       | DRAWING CODE                                  |

| 6.3       | RT02-A ENGINEERING DRAWINGS                   |

| 0.0       |                                               |

# **ILLUSTRATIONS**

| Figure No. | Title                                                                          |       | Page |

|------------|--------------------------------------------------------------------------------|-------|------|

| 1-1        | RT02-A 30 Character Keyboard Remote Terminal                                   |       | 1-2  |

| 1-2        | RT02-A Block Diagram                                                           |       | 1-3  |

| 1-3        | Keyboard Layout                                                                |       | 1-3  |

| 1-4        | 110 and 300 Baud Rate, Serial Output Examples<br>(M7390 Communications Module) |       | 1-5  |

| 1-5        | Character Format                                                               |       |      |

| 2-1        | RT02-A Power Supply (H753) Input and Output<br>Connections (115 and 230 Vac)   |       |      |

| 2-2        | RT02-A Rear Panel and Connector Cables                                         |       |      |

| 2-3        | Typical RT02-A Interface Configuration - Local (TTY) Installation              |       |      |

| 2-4        | Typical RT02-A EIA Interface Configuration - Remote Installation               |       |      |

| 2-5        | Output Connector Cable Assembly 7008983                                        |       |      |

| 2-6        | EIA Connector Pin Assignments                                                  |       |      |

| 4-1        | Keyboard Encoder (M7396)                                                       |       |      |

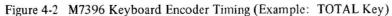

| 4-2        | M7396 Keyboard Encoder Timing (Example: TOTAL Key)                             |       |      |

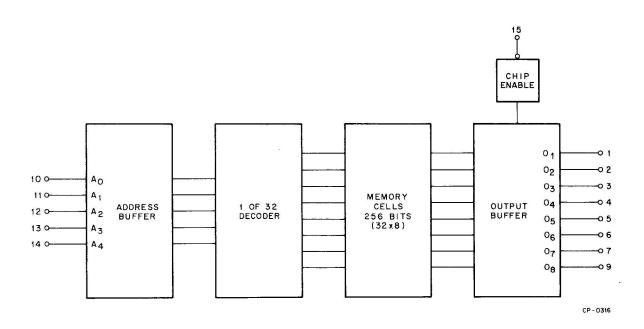

| 4-3        | Programmable Read-Only Memory (PROM), Block Diagram                            |       |      |

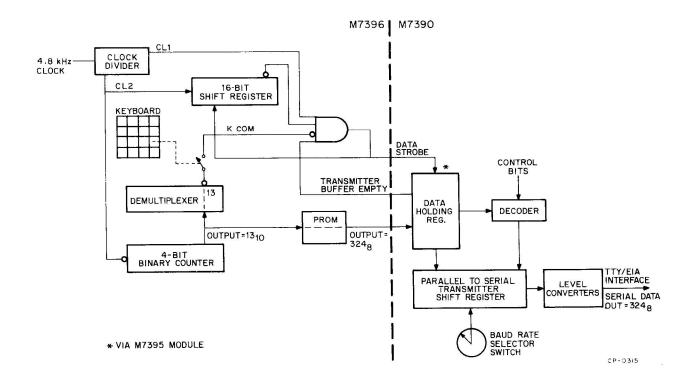

| 4-4        | Transmit Mode Block Diagram (Example: TOTAL Key)                               |       |      |

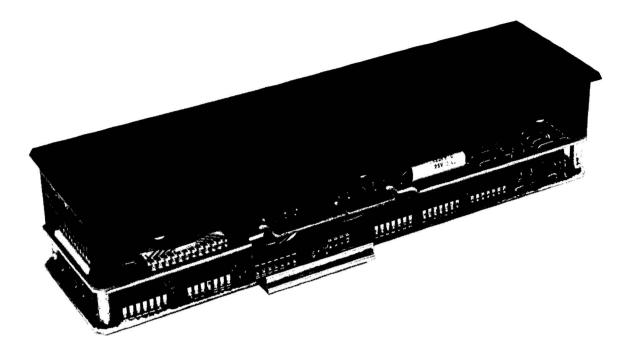

| 4-5        | M7390 Communications Module                                                    |       | 4-9  |

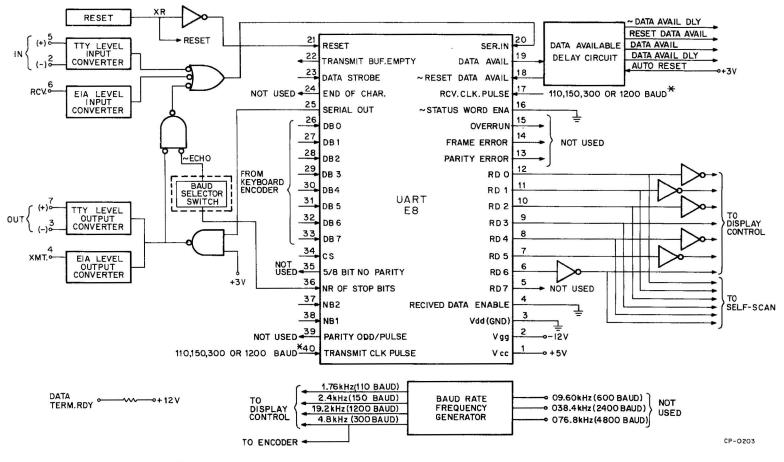

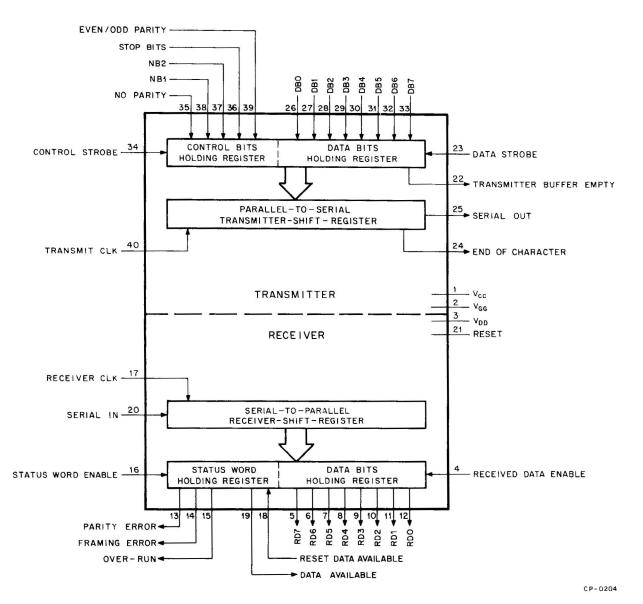

| 4-6        | Universal Asynchronous Receiver/Transmitter (UART)                             |       | 4-10 |

| 4-7        | Receive Data Format                                                            | • •   | 4-13 |

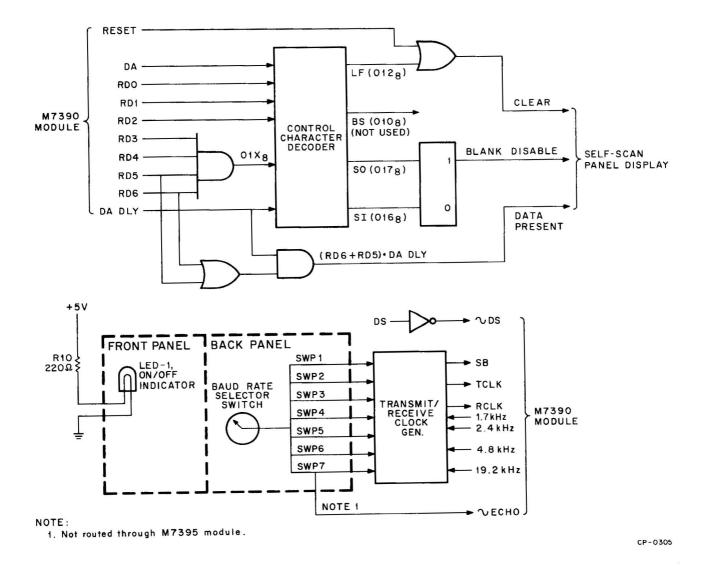

| 4-8        | M7395 Display Control Module, Block Diagram                                    |       | 4-16 |

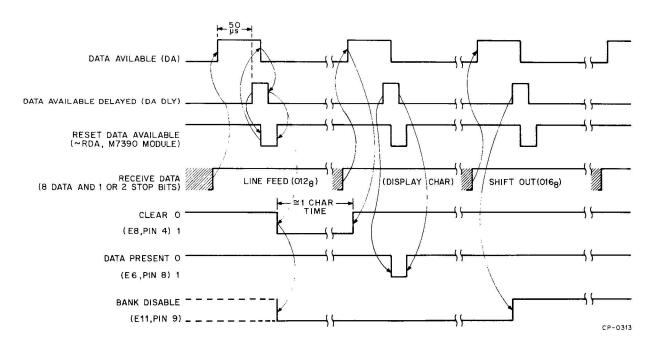

| 4-9        | Control Signal Timing, M7395 Display Control Module                            |       | 4-17 |

| 4-10       | Display Panel, Block Diagram                                                   |       | 4-18 |

| 4-11       | Display Panel, Outline Drawing                                                 | • •   | 4-18 |

| 4-12       | Display Panel Timing                                                           |       |      |

| 4-13       | Construction of Self-Scan Panel Display                                        |       |      |

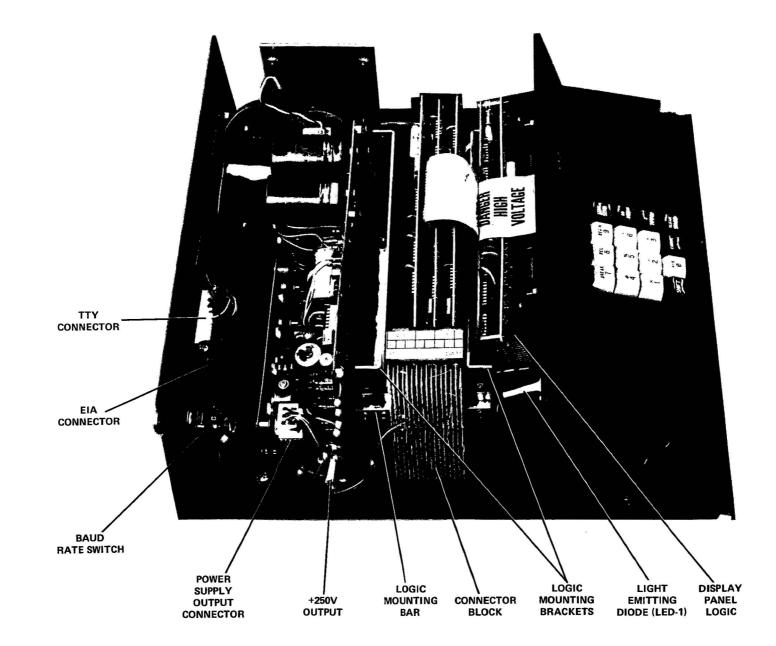

| 5-1        | RT02-A Interior View, Left                                                     |       |      |

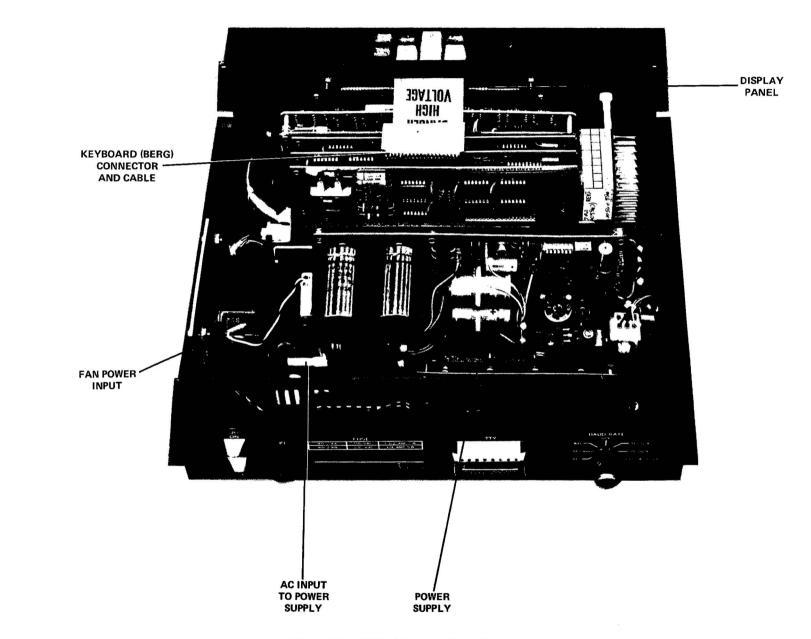

| 5-2        | RT02-A Interior View, Rear                                                     |       |      |

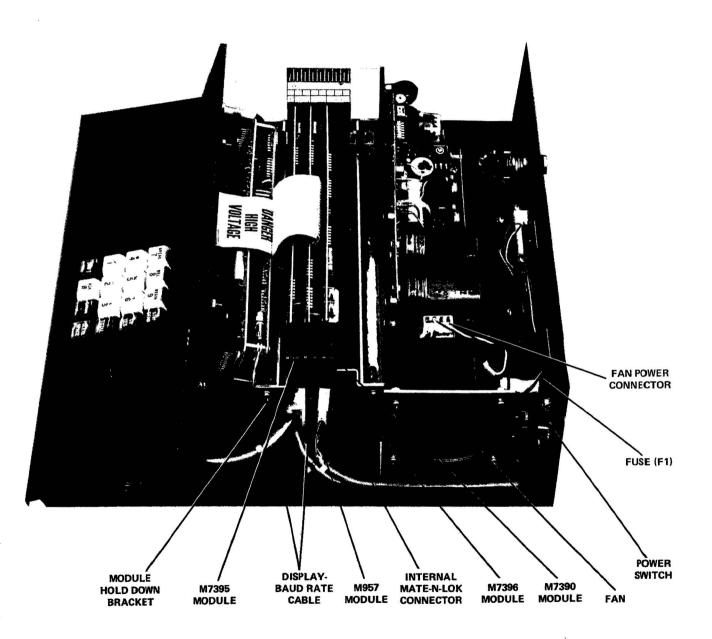

| 5-3        | RT02-A Interior View, Right                                                    |       |      |

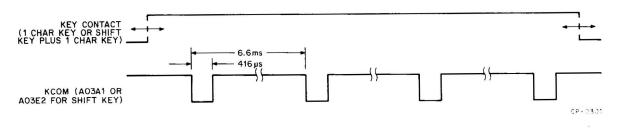

| 5-4        | Keyboard Timing                                                                |       | 5-9  |

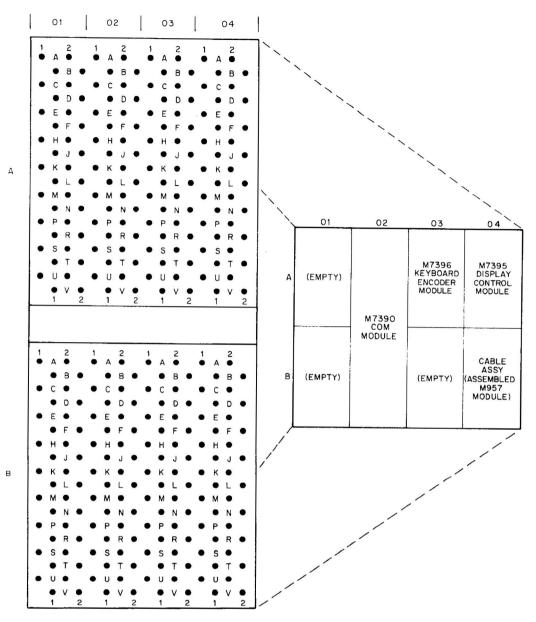

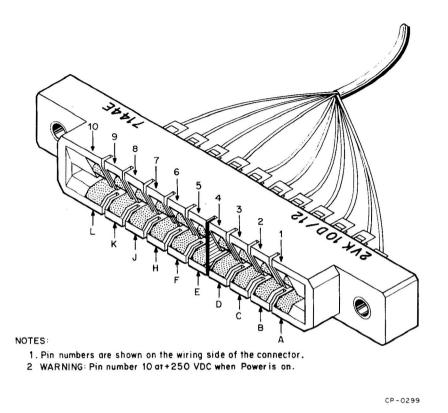

| 5-5        | RT02-A Module Connector Block (Wiring Side)                                    |       | 5-10 |

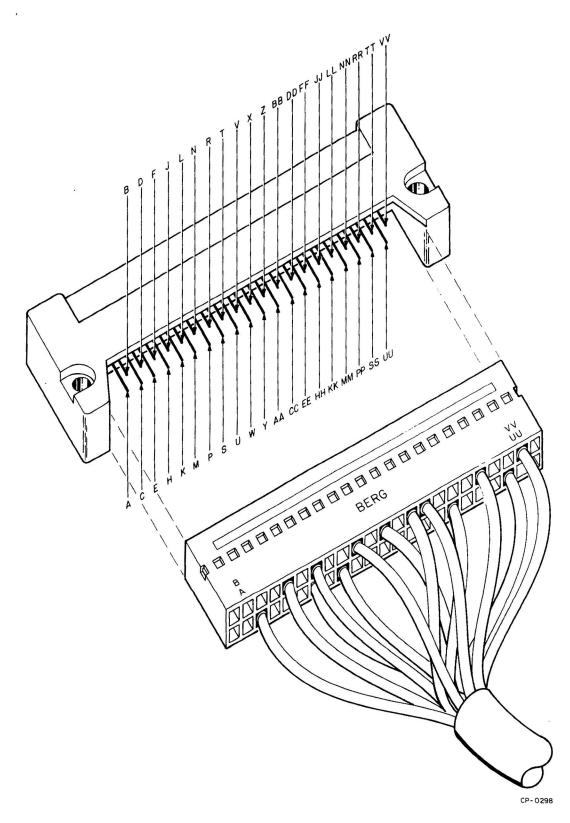

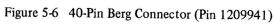

| 5-6        | 40-Pin Berg Connector (Pin 1209941)                                            | • • • | 5-12 |

| 5-7        | M7390 Module Serial Output Example Format                                      | • • • | 5-15 |

| 5-8        | 20-Pin Self-Scan Connector                                                     |       |      |

| 5-9        | Display Panel with Shorting Clip                                               | • • • | 5-26 |

# TABLES

# Table No.

# Title

# Page

Ξ.

| 1-1 | RT02-A Keyboard Transmit Code (ASCII)                     | 1-4        |

|-----|-----------------------------------------------------------|------------|

| 1-2 | RT02-A Receive Code (Modified ASCII)                      | 1-6        |

| 1-3 | Transmit/Receive Frequencies and Baud Rates               | 1-6        |

| 2-1 | Power Cable Line Identification                           | 2-2        |

| 2-2 | Power Wiring Jumper Table                                 | 2-2        |

| 2-3 | I/O Port Pin No./Signal Assignments                       | 2-6        |

| 2-4 | Typical 4-Wire Twisted Pair Cable Lengths and Recommended | MART IN IT |

|     | Wire Sizes for 110 Baud                                   | 2-7        |

v

:

-

----

# TABLES (Cont)

| Table No. | Title                                                         | Page   |

|-----------|---------------------------------------------------------------|--------|

| 2-5       | Typical TTY Interface Configurations (RT02-A to DEC Computer) | 2-8    |

| 2-6       | EIA Connector Pin Assignments                                 |        |

| 2-7       | Typical EIA Interface Configurations (RT02-A to DEC Computer) | . 2-9  |

| 2-8       | Communications Module Connector (P1) Pin Assignments          | . 2-10 |

| 3-1       | RT02-A Transmit Codes (ASCII)                                 | . 3-2  |

| 3-2       | RT02-A Receive Display Codes (ASCII)                          |        |

| 3-3       | Receive Control Codes                                         | . 3-3  |

| 4-1       | 4-Bit Binary Counter Truth Table                              | . 4-5  |

| 4-2       | Demultiplexer Truth Table                                     | . 4-5  |

| 4-3       | Programmable Read-Only Memory (PROM)                          | . 4-6  |

| 4-4       | UART Input/Output Pins, Signals, and Functions                |        |

| 4-5       | Baud Rates and Operating Frequencies                          | . 4-15 |

| 4-6       | Frequency Divider Counter Inputs and Outputs                  | . 4-15 |

| 4-7       | Input/Output Signal Pin Connections                           | . 4-20 |

| 4-8       | Common Terms of Gas Discharge Devices                         | . 4-22 |

| 5-1       | Equipment Required                                            | . 5-1  |

| 5-2       | RT02-A MAINDEC Diagnostic Tests                               | . 5-5  |

| 5-3       | Power Supply Output Checks                                    | . 5-8  |

| 5-4       | Keyboard Output Assignments                                   |        |

| 5-5       | PROM Outputs                                                  | . 5-13 |

| 5-6       | M7390 Module Input Pin Cross-Reference                        |        |

| 5-7       | RT02-A Derived Frequencies and Corresponding Test Points      |        |

| 5-8       | Transmit and Receive Clock Measurements                       | . 5-19 |

| 5-9       | BAUD RATE Switch Inputs                                       | . 5-20 |

| 5-10      | M7395 Module Control Signal (Decode and Generate)             | . 5-21 |

| 5-11      | Self-Scan Inputs (Continuity Check)                           | . 5-23 |

| 5-12      | Recommended Spares List, Level 1                              | . 5-27 |

| 5-13      | Recommended Spares List, Level 2                              | . 5-27 |

| 6-1       | RT02-A Engineering Drawings                                   | . 6-1  |

# CHAPTER 1 INTRODUCTION AND DESCRIPTION

## 1.1 PURPOSE AND SCOPE

This manual describes the purpose and use of the RT02-A 30 Character Keyboard Remote Terminal. The following information is also included: installation, theory of operation, programming, and maintenance information and procedures.

#### 1.1.1 Related Documentation

The reader must have access to the applicable engineering drawings listed in Chapter 6 of this manual. The RT02 cabling brochure, *How to Mate RT02's*, should also be available for reference. This publication contains a more detailed description of possible RT02-to-modem or computer configurations than is provided in this manual (Chapter 2).

## **1.2 BASIC DESCRIPTION**

The RT02-A is a compact, light weight, self-contained alphanumeric display terminal (Figure 1-1) designed to provide interactive communications with a computer in configurations where source data is primarily numeric and a limited alphanumeric display storage capability is required. The RT02-A receives, stores, and displays 32 alphanumeric characters on a single-line gas discharge type readout panel from a 64-character repertoire (modified ASCII). Data entry is by means of a 16-pad keyboard that includes a shift key to furnish a 30-character input to the computer; input information may be treated by the monitoring computer as either numeric data or control functions. Terminal-to-computer interfacing is via standard teletype line units (full duplex, 4-wire interface cable) that are available for the PDP-8 and PDP-11 families, DECsystem-10, PDP-12, PDP-15, and PDP-16 computers. The RT02-A also receives and transmits modem interface signals that comply with Electronic Industries Association (EIA) RS-232-C specifications. Either teletype or EIA signals are exchanged with data communications devices by means of separate connectors provided as standard equipment on the RT02-A.

Two RT02-A models are available: the RT02-AA for 115-Vac facilities, and the RT02-AB for 230-Vac facilities.

#### 1.2.1 Functional Description

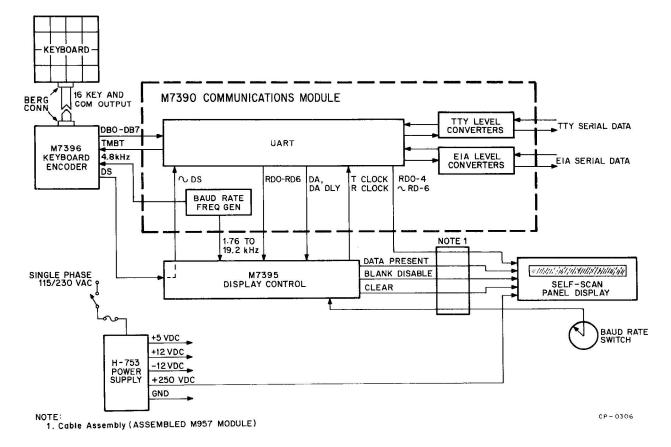

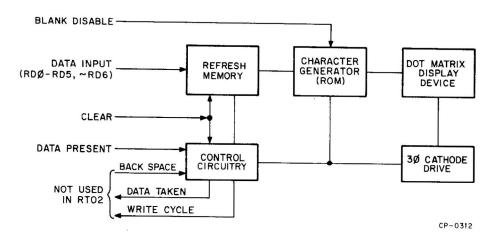

The basic RT02-A (Figure 1-2) consists of a 16-key, 30-character keyboard and keyboard encoder module, a communications module, a display control module, a 32-character alphanumeric display panel, and an H753 Power Supply. The RT02-A is hardware compatible with existing DEC computers and computer teletypewriter interface units. A detailed description of various terminal-computer configurations is contained in Paragraph 2.2.4. The required signals and interface hardware for data communications via modems are provided in accordance with EIA Standard RS-232-C and European International Telegraph Consultative Committee (CCIT) standards. The RT02-A may also be connected with any 20-mA asynchronous current loop (TTY). A more detailed description of input/output signals and the interface connectors used with the RT02-A may be found in Paragraph 2.2.4.

Figure 1-1 RT02-A 30 Character Keyboard Remote Terminal

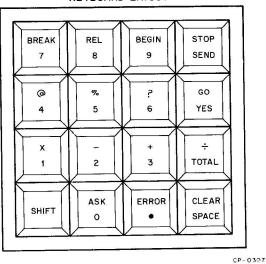

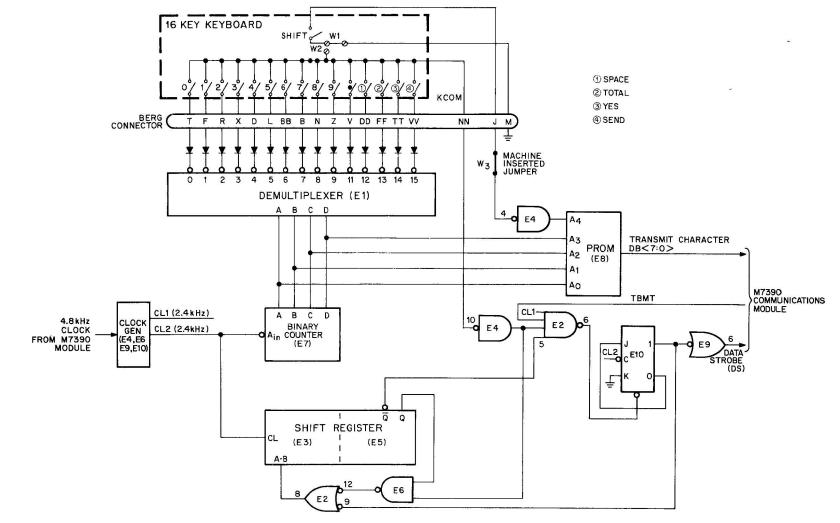

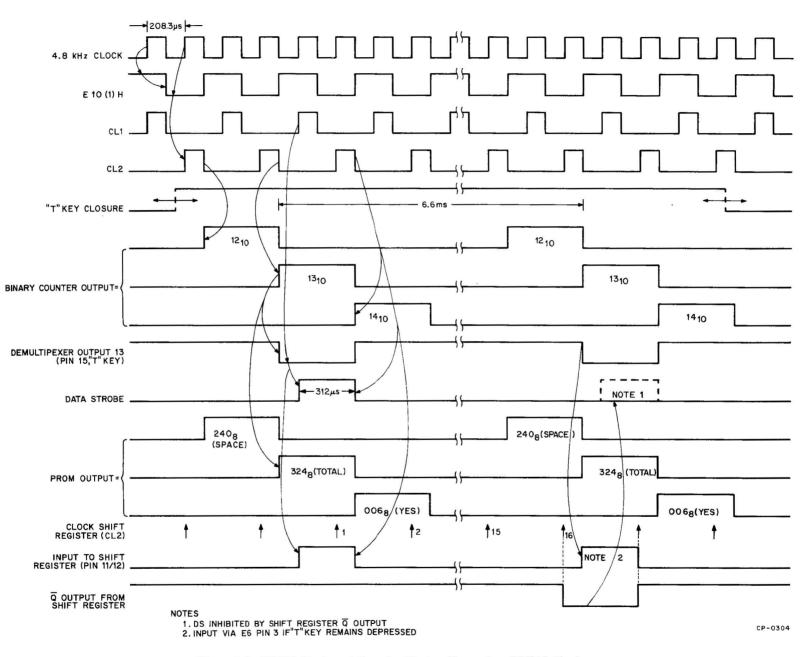

A 16-key keyboard (Figure 1-3) provides the RT02-A with a transmission capability. The keyboard is an unencoded 4 X 4 pad with switch-closure outputs to a common reference. A 40-pin Berg connector delivers the 16 outputs, plus the common reference, to an M7396 Keyboard Encoder Module. With one of the 16 keys dedicated as a SHIFT key, the key pad can generate a total of 30 discrete characters. The M7396 Keyboard Encoder continually scans the keyboard to ascertain new key contact closures. A programmable read-only memory (PROM) in the encoder module is synchronized to this scan. When the encoder circuit finds a new key closure, an 8-bit ASCII character, designated DB0 through DB7, is sent (in parallel) with a data strobe (DS) to the M7390 Communications Module.

An additional design feature allows N-key rollover operation of the keyboard. Two or more keys can be depressed in sequence, without being released, and encoded characters will be generated for each key in the proper sequence. The absence of any interaction between keys, except when the SHIFT key and one of the other fifteen keys are depressed simultaneously, results in independent key outputs. Consequently, data transmission at burst rate speeds is possible.

Necessary timing, control logic, and interface circuits required for RT02-A operation are provided by the M7390 Communications Module. This module comprises a 40-pin MOS IC that is a Universal Asynchronous Receiver/Transmitter (UART), a crystal-controlled clock with frequency divider circuitry, and 10 to 60-mA teletype and EIA input/output interface circuitry. The M7390 receives binary data from the keyboard encoder module (bit-parallel) and the EIA/TTY communications lines (bit-serial). These lines provide the interface with a computer or a modem. Output from the M7390 module is serial binary data transmitted via the EIA or TTY communications lines (Table 1-1), or parallel binary data (designated RD0-RD6) to the display control module and the display panel. Data on the RD0-RD6 lines is decoded in the display control module as displayable data or display control data.

KEYBOARD LAYOUT

Figure 1-3 Keyboard Layout

| · ·     | <br>B-5<br>DB-4 |         |         | -><br>> | -• | 0<br>0<br>0 | 0<br>0<br>1 | 0<br>1<br>0 | 0<br>1<br>1 | 1<br>0<br>0 | 1<br>0<br>1 | 1<br>1<br>0 | 1<br>1<br>1 |

|---------|-----------------|---------|---------|---------|----|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| s       | DB<br>3         | DB<br>2 | DB<br>1 | DB<br>0 |    | ł           | Ļ           | Ļ           | ł           | Ļ           | ł           | Ļ           | ł           |

| <b></b> | 0               | 0       | 0       | 0       | -  | NUL         |             | SP          | 0           | @           |             |             |             |

|         | 0               | 0       | 0       | 1       |    |             |             |             | 1           |             |             |             |             |

|         | 0               | 0       | 1       | 0       |    | STX         |             |             | 2           |             |             |             |             |

|         | 0               | 0       | 1       | 1       | +  | ETX         |             |             | 3           |             |             |             |             |

| -       | 0               | 1       | 0       | 0       | >  |             |             |             | 4           | D           | Т           |             |             |

|         | 0               | 1       | 0       | 1       | >  |             |             | %           | 5           |             |             |             |             |

|         | 0               | 1       | _1      | 0       | >  | ACK         |             |             | 6           |             |             |             |             |

|         | 0               | _1      | 1       | 1       |    |             |             |             | 7           | G           |             |             |             |

|         | 1               | 0       | 0       | 0       | >  |             |             |             | 8           |             |             |             |             |

|         | 1               | 0       | 0       | 1       |    |             |             |             | 9           |             |             |             |             |

|         | 1               | 0       | 1       | 0       | >  | LF          |             | *           |             |             |             |             |             |

|         | 1               | 0       | 1       | 1       |    |             | ESC         | +           |             |             |             |             |             |

|         | 1               | 1       | 0       | 0       |    |             |             |             |             |             |             |             |             |

|         | 1               | 1       | 0       | 1       |    | CR          |             | -           |             |             |             |             |             |

|         | 1               | 1       | 1       | 0       | >  |             |             | <u> </u>    |             |             |             |             |             |

|         | 1               | 1       | 1       | 1       |    |             |             | /           | ?           |             |             |             | DEL         |

Table 1-1

RT02-A Keyboard Transmit Code (ASCII)

Note: Refer to Table 3-1 for keyboard names.

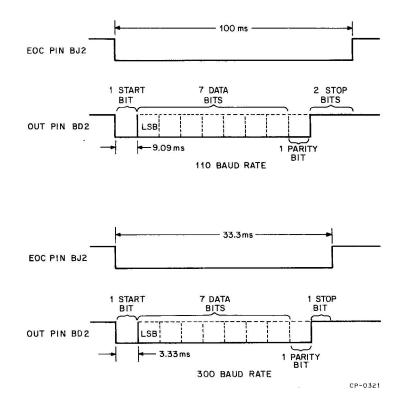

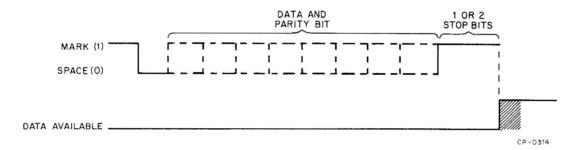

The EIA/TTY interface circuitry is used by both the transmit data originating in the keyboard encoder, and the receive data from an external source (computer or modem). Signal level conversion occurs at this point in the data path. Both input and output data is 8-level asynchronous serial ASCII with bit 8 designated as the parity (even) bit (Figure 1-4). The receive (input) data is not checked for correct parity. The least significant bit (LSB) is transmitted/received first.

As indicated in Table 1-1, 30 different ASCII characters may be transmitted by the RT02-A. However, 64 receive characters are recognized as displayable by the RT02-A. These are a modified subset of standard ASCII codes (040<sub>8</sub> through 137<sub>8</sub>) consisting of 10 numeric, 26 alphabetic, and 28 graphic characters (Table 1-2). If any code from 140<sub>8</sub> through 177<sub>8</sub> is received, it is displayed as the corresponding character in the 100<sub>8</sub> through 137<sub>8</sub> range. Therefore all lower case alphabetic characters received (codes 141<sub>8</sub> through 172<sub>8</sub>) are converted and displayed as upper case alphabetic characters (codes 101<sub>8</sub> through 132<sub>8</sub>). The only recognized control characters are LF (012<sub>8</sub>), SO (016<sub>8</sub>), and SI (017<sub>8</sub>).

The crystal-controlled clock and frequency divider in the M7390 module outputs signals from 1.76 to 76.8 kHz. The BAUD RATE selector switch, located on the rear panel, controls the receive and transmit rates by selecting one of four frequencies (1.76 to 19.2 kHz) from the frequency divider. All the Baud rate transmit/receive combinations used by the RT02-A are listed in Table 1-3. Note that the selected clock frequencies are 16 times the actual transmit and receive Baud rates.

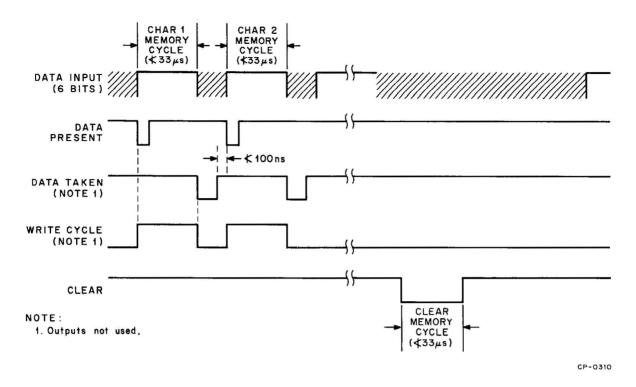

The M7395 Display Control Module contains control logic for the display panel. Inputs are the 7-bit ASCII receive word (RD0 through RD6) and the strobe pulses (DA, DA DLY) from the M7390 module. Examination of the ASCII character determines if it is a display control character or a character to be actually displayed. If a control character is decoded, one of three command signals is directed to the display panel: CLEAR, BLANK DISABLE, or BLANK DISABLE (the last two signals are commonly known as "blank" and "unblank"). A fourth control signal,

Backspace, is also decoded; it is not used by the display panel model currently installed in the RT02-A. Decoding one of 64 displayable characters results in a strobe pulse (DATA PRESENT) being sent to the display panel. This signal gates the 6-bit display word (RD0 through RD4 and  $\sim$ RD6) from the M7390 Communications Module into the display panel memory for subsequent presentation.

The output of the BAUD RATE selector switch is also input to the M7395 module. Switch outputs are employed in generating the transmitter and receiver clock pulses (TCLK and RCLK) that are gated back to the M7390 module to control the serial transmit and receive rate (Table 1-3).

A fourth module, the Display Baud Rate Cable Assembly (7008991), is positioned in the data/signal path to the panel display and the BAUD RATE selector switch. This is an assembled M957 module used as a tie point for data and control signals to the display panel and the BAUD RATE selector switch outputs to the M7395 module. The cable assembly module does not contain any logic circuits and therefore can not alter the signals that are routed through it.

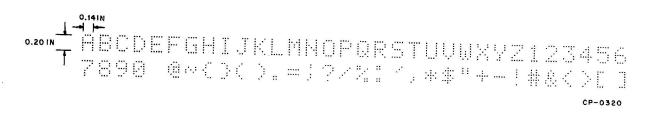

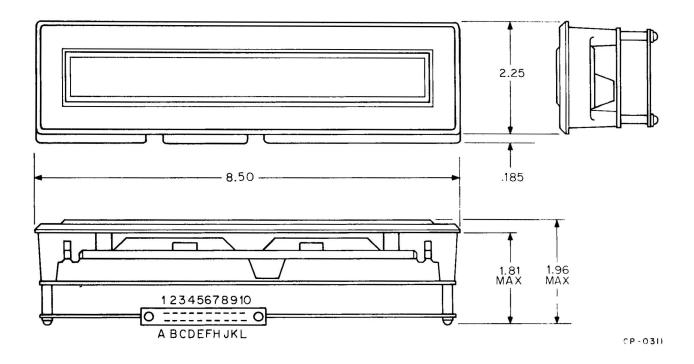

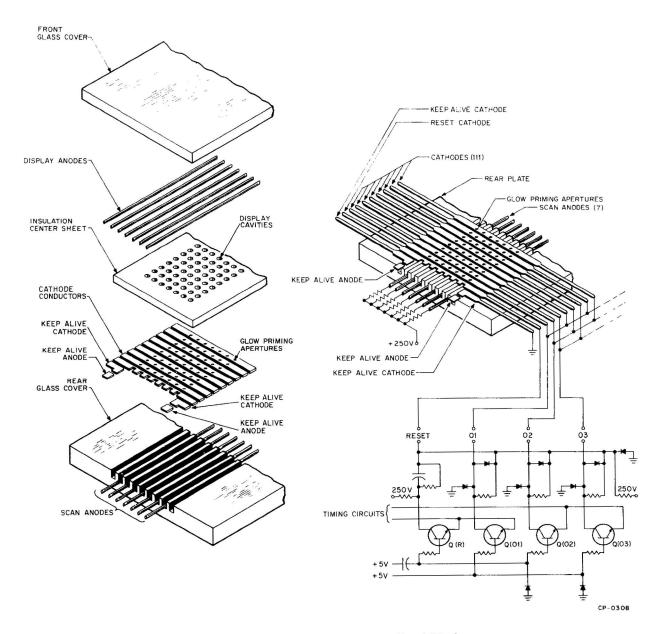

The display device is a Self-Scan M Panel Display, Model No. SS0132-0040, or equivalent. This vendor-supplied unit is a single-row 32-position alphanumeric display with self-contained control logic, drive electronics, refresh memory, and character generator. From a repertoire of 64 ASCII characters (modified), the characters are displayed in a 5  $\times$  7 dot matrix format (Figure 1-5) on a gas discharge type display screen. Each character is defined by a positive logic 6-bit code, RD0 through RD4 and ~RD6. The display operates in a sequential mode, entering characters from left to right, until a total of 32 characters is displayed. Character number 33 will be displayed in the left-most position, replacing the first character. Characters are 0.2 inch high and are readable up to a viewing distance of 10 feet. The display may be cleared at any time during the 32-character cycle on receipt of the CLEAR signal from the M7395 Display Control Module. All Self-Scan components are packaged in a molded housing that has an integral mounting bezel.

Figure 1-4 110 and 300 Baud Rate, Serial Output Examples (M7390 Communications Module)

TM Self-Scan is a trademark of the Burroughs Corporation.

| B RD C<br>i R<br>t | 6<br>D 5<br>RD 4 |    |    | ÷<br>• | • | 0<br>0<br>0 | 0<br>0<br>1 | 0<br>1<br>0 | 0<br>1<br>1 | 1<br>0<br>0 | 1<br>0<br>1 | 1<br>1<br>0 | 1<br>1<br>1 |

|--------------------|------------------|----|----|--------|---|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| s                  | RD               | RD | RD | RD     |   | 1           | 1           | 1           | 1           | 1           |             | 1           | 1           |

|                    | 3                | 2  | 1  | 0      |   |             | •           | T           | T           | T           | 7           | T           | •           |

|                    | 0                | 0  | 0  | 0      |   |             |             | SP          | 0           | @           | P           | @           | P           |

|                    | 0                | 0  | 0  | _1     |   |             |             | !           | 1           | A           | Q           | A           | Q           |

|                    | 0                | 0  | 1  | 0      |   |             |             | "           | 2           | В           | R           | B           | R           |

|                    | 0                | 0  | 1  | 1      | • |             |             | #           | 3           | С           | \$          | С           | S           |

|                    | 0                | 1  | 0  | 0      | > |             |             | \$          | 4           | D           | T           | D           | Т           |

|                    | 0                | 1  | 0  | 1      | + |             |             | %           | 5           | E           | U           | Ē           | U           |

|                    | 0                | 1  | 1  | 0      | • |             |             | &           | 6           | F           | V           | F           | V           |

|                    | 0                | 1  | 1  | 1      | • |             |             | ,           | 7           | G           | W           | G           | W           |

|                    | 1                | 0  | 0  | 0      | ١ |             |             | (           | 8           | H           | X           | Н           | X           |

|                    | 1                | 0  | 0  | 1      |   |             |             |             | 9           | I           | Ŷ           | I           | Y           |

|                    | 1                | 0  | 1  | 0      | • | LF (2)      |             | *           | :           | J           | Z           | J           | Z           |

|                    | 1                | 0  | 1  | 1      |   |             |             | +           | :           | K           | [           | K           | [           |

|                    | 1                | 1  | 0  | 0      | > |             |             | ,           | <           | L           | ~(1)        | L           | ~(1)        |

|                    | 1                | 1  | 0  | 1      |   |             |             | -           | =           | M           | ]           | М           | ]           |

|                    | 1                | 1  | 1  | 0      | > | SO (2)      |             | •           | >           | N           | { (1)       | N           | { (1)       |

|                    | 1                | 1  | 1  | 1      |   | SI (2)      |             | /           | ?           | 0           | } (1)       | 0           | } (1)       |

Table 1-2

RT02-A Receive Code (Modified ASCII)

Notes: (1) Modification of Standard ASCII Coded Symbol

(2) RT02-A Control Characters

64 Character Display Subset

Г

| BAUD RATE       | Tra  | nsmit          | Receive |                |  |

|-----------------|------|----------------|---------|----------------|--|

| Switch Position | BAUD | T CLK<br>(kHz) | BAUD    | R CLK<br>(kHz) |  |

| 10              | 110  | 1.76           | 110     | 1.76           |  |

| 150             | 150  | 2.4            | 150     | 2.4            |  |

| 300             | 300  | 4.8            | 300     | 4.8            |  |

| 1200*           | 1200 | 19.2           | 1200    | 19.2           |  |

| 110/1200*       | 110  | 1.76           | 1200    | 19.2           |  |

| 150/1200*       | 150  | 2.4            | 1200    | 19.2           |  |

| LOCAL COPY**    | 110  | 1.76           | 110     | 1.76           |  |

Table 1-3 Transmit/Receive Frequencies and Baud Rates

\* Use the 1200 Baud switch positions only when the input/output is via the EIA interface.

\*\* ECHO position - not to be used when the RT02-A is connected to a modem or computer.

The H753 Power Supply, also vendor supplied, generates the dc voltages (Paragraph 1.3) required by the RT02-A. A cooling fan is provided and the ON/OFF indicator is a light-emitting diode connected through a resistor to the +5 Vdc output.

# Figure 1-5 Character Format

# 1.2.2 Physical Description

The RT02-A is self-contained in a single cabinet that houses all the necessary components and modules. The cabinet package consists of four pieces: cover, bottom panel assembly, front panel assembly, and rear panel. Cabinet dimensions are described in Paragraph 1.3. Figure 4-11 shows the front and side dimensional views of the RT02.

## **1.3 EQUIPMENT SPECIFICATIONS**

The RT02-A operating requirements and overall physical characteristics are outlined below:

| Operating Temperature Range:                        | 0° to 40°C            |

|-----------------------------------------------------|-----------------------|

| Operating Humidity Range:<br>(without condensation) | 10% to 90% (relative) |

# CAUTION

The RT02-A is not explosion-proof; do not operate in an explosive atmosphere.

| Power Requirements:        | 95-135 or 190-270 Vac, 47-63 Hz Line Voltage                                                                                                                                                    |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Consumption:         | 50 W (maximum)                                                                                                                                                                                  |

| Heat Dissipation:          | 170 BTU/hour                                                                                                                                                                                    |

| Fuses:                     | 1.5A Slo Blo (115 Vac)<br>.75A Slo Blo (230 Vac)                                                                                                                                                |

| Power Supply Outputs:      | +5Vdc (± 2%) @ 3.0A for TTL Logic (Vcc)<br>+12 Vdc (± 2%) @ 0.3A for TTY and EIA<br>-12 Vdc (± 2% @ 0.3A for EIA, MOS, and Self-Scan (V <sub>GG</sub> )<br>+250 Vdc (± 2%) @ 0.03 for Self-Scan |

| Data Rates:<br>(Table 1-3) | 110 to 1200 Baud<br>(10 to 120 characters/sec)                                                                                                                                                  |

#### Data Input:

| Teletype*                            |        |                  |                                   |  |  |  |

|--------------------------------------|--------|------------------|-----------------------------------|--|--|--|

| Line Condition Logic Current Voltage |        |                  |                                   |  |  |  |

| Mark<br>Space                        | 1<br>0 | 10–60 mA<br>0 mA | 1.5 Vdc (min.)<br>35.0 Vdc (max.) |  |  |  |

\*Isolated optical coupler

| EIA            |        |                                        |

|----------------|--------|----------------------------------------|

| Line Condition | Logic  | Voltage                                |

| Mark<br>Space  | 1<br>0 | -3 Vdc to -25 Vdc<br>+3 Vdc to +25 Vdc |

| Open           | 0      | -                                      |

Data Output:

| Teletype*      |        |                  |                                   |

|----------------|--------|------------------|-----------------------------------|

| Line Condition | Logic  | Current          | Voltage                           |

| Mark<br>Space  | 1<br>0 | 10–60 mA<br>0 mA | 0.5 Vdc (min.)<br>35.0 Vdc (max.) |

\*Isolated NPN phototransistor

| E. | г |     |

|----|---|-----|

| Г. | • | HA. |

| EIA            |        |                                            |

|----------------|--------|--------------------------------------------|

| Line Condition | Logic  | Voltage                                    |

| Mark<br>Space  | 1<br>0 | -11.5 Vdc (nominal)<br>+11.5 Vdc (nominal) |

Data Input/Output Format: (Table 1-3, Figure 1-4)

| 110 Baud       | 150, 300, and 1200 Baud |

|----------------|-------------------------|

| 1 Start Bit    | 1 Start Bit             |

| 7 Data Bits    | 7 Data Bits             |

| (LSB first)    | (LSB first)             |

| 1 Parity Bit   | 1 Parity Bit            |

| (Even Parity)* | (Even Parity)*          |

| 2 Stop Bits    | 1 Stop Bit              |

\*RT02-A receive data not checked for correct parity

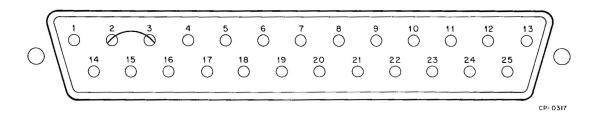

| Interface Connectors:     | TTY – 8-pin Mate-N-Lok (DEC No. 1209340-00)<br>EIA – Cinch DB 19604-432 (DEC No. 1205886)                                          |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Physical Characteristics: | Height $-6.25$ in. (15.87 cm)<br>Width $-14.375$ in. (36.51 cm)<br>Depth $-15.875$ in. (40.31 cm)<br>Weight $-14.0$ lb. (6.342 kg) |

## 1.4 REFERENCING CONVENTIONS AND TERMINOLOGY

The following paragraphs briefly describe the referencing conventions and terminology used in this manual.

- a. Numeric Notations Unless otherwise specified, all number representations are decimal. Number representations other than decimal are so designated; e.g., 18, 0012, etc.

- b. Circuit References All references to logic signals within the module descriptions include the component designator number, and in instances where more than one component has the same designation, the component designator number and input/output pin numbers are given. For example, two NAND gates are both designated E10; the output of the first is designated as pin 3, and the output of the second is designated as pin 6. The two gates are referenced as E10, pin 3 for the first gate, and E10, pin 6 for the second gate.

RT02-A modules are referenced by module number; e.g. the M7390 Communications Transceiver Module is referenced as the M7390 module.

- c. Input/Output Pin References Circuit and component input/output pins normally use numeric designations; e.g. pin 6. Pins used for communication between modules are defined as *module interconnect pins*. These pins are assigned alphanumeric pin designators; e.g. AA1, BA2 (Figure 5-5).

- d. Signal Mnemonics Uncommon mnemonics are explained parenthetically the first time they are mentioned in the discussion.

- e. Illustrations References to in-text illustrations include the chapter prefix number; e.g. Figure 1-5 is the fifth illustration in Chapter 1. References to engineering drawings contained in Volume II will be designated by the drawing number; e.g. (RT02-0-1), indicating drawing number 1 of the RT02 Data Entry Terminal engineering drawing package, or (M7395-0-1), indicating drawing 1 of the M7395 Display Control Module.

- f. **Terminology** Unusual or uncommon terms, functions, methods, etc., are explained or referenced to an explanatory paragraph the first time they are mentioned in the discussion.

• •

# CHAPTER 2 INSTALLATION

This chapter provides installation planning considerations and site preparation recommendations; physical, electrical and environmental requirements; and installation, inspection, and acceptance checkout procedures.

## 2.1 SITE PLANNING

The RT02-A is housed in a compact, self-contained cabinet that can be placed on a table, desk, or bench top.

The customer should determine the location of the RT02-A installation prior to shipment. Items of major importance are: the location of the RT02-A in relation to work flow requirements within the work area, provision for and availability of adequate power, type of system to which the RT02-A will be interfaced, fire and personnel safety precautions, and proper environmental conditions. Operating, environmental, and physical characteristics and system specifications for the RT02-A are provided in Chapter 1 of this manual.

#### 2.2 INSTALLATION

#### 2.2.1 Unpacking

The RT02-A is packed in a specially designed shipping carton to prevent damage during shipment.

#### NOTE

# Any damage to the RT02-A should be noted and reported immediately to the DEC Field Service representative.

Unpack the RT02-A according to the following sequence:

- 1. Remove the RT02-A from the shipping container; save the shipping container.

- 2. Remove the polyethylene cover from the cabinet, if supplied.

- 3. Remove any tape from the RT02-A cabinet.

- 4. Ensure that the RT02-A is clean and free of any foreign materials.

- 5. Place the RT02-A in the location in which it is to be used.

- 6. Perform the initial checks contained in Paragraphs 2.3 through 2.3.3.

# 2.2.2 Primary AC Power

The primary ac power cable is a 3-wire cable that interconnects the site power source to the RT02-A power supply. The 3-wire cable is connected at the factory to the RT02-A power transformer for either 115V or 230V operation.

### CAUTION

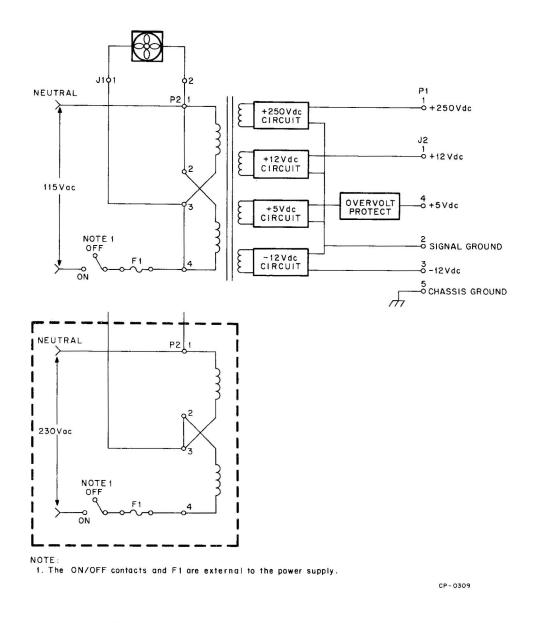

Before proceeding, ensure that the RT02-A power transformer primary windings are correctly connected (for 115V or 230V operation) to correspond to the installation site source power voltage. Refer to the power supply schematic (Drawing A-PS-H753-0-0) for the appropriate connections. Power cable line identification information is provided in Table 2-1. Jumper connection information is provided in Table 2-2 and Figure 2-1.

| Line           | Wire Color |

|----------------|------------|

| Frame Ground   | Green      |

| Neutral/Line 2 | White      |

| Line 1         | Black      |

| Table 2-1                       |  |  |  |

|---------------------------------|--|--|--|

| Power Cable Line Identification |  |  |  |

#### WARNING

The green wire is the cabinet frame ground and does not carry load current; however, it must be connected for personnel safety. It must be securely connected between the cabinet and the primary power source grounding point.

The white (or light gray) wire is the neutral, common, ac return, or cold load and should never be used for cabinet grounding.

| Table 2-2 |              |         |  |

|-----------|--------------|---------|--|

| Power     | Wiring Jumpe | r Table |  |

| Input | From | То   |

|-------|------|------|

| 115V  | P2-1 | P2-2 |

|       | P2-3 | P2-4 |

| 230V  | P2-2 | P2-3 |

# 2.2.3 RT02-A Power Connections

Use the following procedure for the initial power check of the RT02-A:

- 1. If the wall receptacle to be used has not been checked prior to installation, meter the wall receptacle to ensure that the hot, neutral, and ground connections are as required.

- 2. Connect the power cord to the wall receptacle and press the power ON/OFF switch to ON.

- 3. With a multimeter or voltmeter, check the following pins for the specified output voltages:

| From (Common) | То        | Voltage Reading |

|---------------|-----------|-----------------|

| Pin B02C2     | Pin B02A2 | +5 Vdc ±2%      |

| Pin B02C2     | Pin A02V2 | +12 Vdc ±2%     |

| Pin B02C2     | Pin B02R2 | -12 Vdc ±2%     |

Measure the power supply output, P1-1 (+250 Vdc) to J2-2 (ground), for +250 Vdc  $\pm 2\%$ . (Other power supply checks are listed in Paragraph 5.3.2.)

Figure 2-1 RT02-A Power Supply (H753) Input and Output Connections (115 and 230 Vac)

## 2.2.4 Interface Cabling

-

Input/output cabling between the RT02-A and the computer installation is supplied by DEC or the user, depending on the particular system configuration.

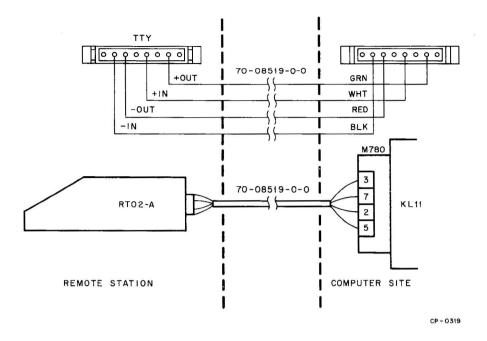

DEC offers standard cables for connecting terminals that are to be used in close proximity to a computer or modem. For those configurations where the RT02-A is situated in a more distant location, cabling must be provided by the user. The RT02 cabling brochure, *How to Mate RT02*'s, lists the part numbers of required cable components in addition to portraying numerous computer-interface combinations.

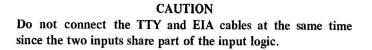

The RT02-A is connected to a computer or modem through either an 8-pin Mate-N-Lok (female) connector for teletype (TTY) interfacing, or a 25-pin (male) data set connector for receiving EIA data input. The connectors are located on the RT02-A rear panel (Figure 2-2).

Figure 2-2 RT02-A Rear Panel and Connector Cables

The RT02-A also provides an I/O port to allow the user to interface other peripheral equipment. With the appropriate peripheral interface, this will accommodate, for example, a strip printer or a card reader. The signals provided to the I/O connector (port) are those that a customer most probably would need for some external peripheral.

The I/O port is located on the logic block in slot B01. Corresponding pins and signal names available are given in Table 2-3.

The interconnecting cable for this option must be ordered separately from the RT02-A. Possible cables and connector modules for this application are as follows:

| BC No.     | DEC Part No. | Function                           |

|------------|--------------|------------------------------------|

|            | M9100        | Berg to Berg<br>(40-Pin Connector) |

| BC08R-XX*  | 91-7578      | I/O Cable                          |

| BC08S-XX   | 91-7578      | I/O Cable                          |

| BC04Z-YY** | 91-7722      | I/O Cable                          |

\* Length expressed as 12 or 18 (feet).

\*\* Length expressed as 01, 06, 10, 15, 25, or 50 (feet).

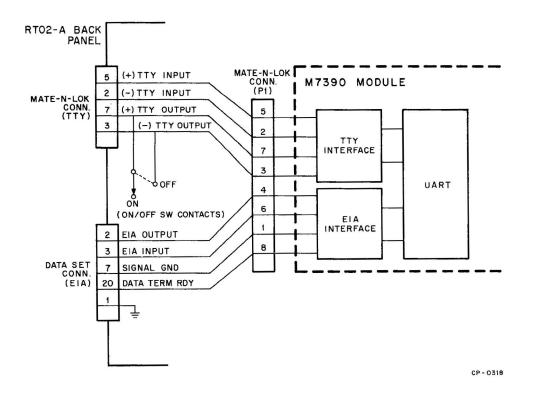

**2.2.4.1** Teletypewriter Interface -- The Mate-N-Lok connector provides the connection to a local 4-wire twisted pair, full duplex line which is the normal means for connecting the DEC computer/teletype interfaces. Connector pin assignments are indicated as follows:

| Pin | Signal   |

|-----|----------|

| 2   | -TTY In  |

| 3   | -TTY Out |

| 5   | +TTY In  |

| 7   | +TTY Out |

Input and output signal parameters are listed in Paragraph 1.3.

#### NOTE

Transistor Q1 (Drawing M7390-0-1) serves as an output switch on the TTY output line. Q1 has a peak inverse rating of 40 Vdc, and the line voltage across Q1 cannot exceed the 40 Vdc rating in the space condition. In the mark condition, the collector-to-emitter voltage (at saturation) will not exceed 0.5 Vdc. The TTY input (current) level converter is a LED with a forward voltage drop of 1.5 Vdc. Both the input and output circuits are protected against reverse polarity connections by two silicon diodes, one per circuit, each with a peak inverse rating of 50 Vdc.

# CAUTION

If the current and/or voltage ratings of any of these devices is exceeded, permanent damage to the terminal may result.

| BO1<br>Pin | Signal<br>Name | Berg (J1)<br>Conn. Pin | Berg (J2)<br>Conn. Pin | Unit<br>Loads | In/Out* |

|------------|----------------|------------------------|------------------------|---------------|---------|

| A1         | PEN            | VV & TT                | A & C                  | 2             | I       |

| B1         | ~XST1          | UU                     | В                      | 1             | I       |

| C1         | ~OUT           | U                      | BB                     | 7             | 0       |

| D1         | ~DS            | SS                     | D                      | 9             | 0       |

| E1         | DB0            | RR                     | E                      | 1             | I       |

| F1         | DB1            | PP                     | F                      | 1             | I       |

| H1         | DB2            | NN                     | Н                      | 1             | I       |

| <b>J</b> 1 | DB3            | ММ                     | J                      | 1             | Ι       |

| K1         | DB4            | LL                     | K                      | 1             | I       |

| L1         | DB5            | KK                     | L                      | 1             | I       |

| M1         | DB6            | JJ                     | М                      | 1             | I       |

| N1         | DB7            | HH                     | N                      | 1             | Ι       |

| P1         | GND            | Z,FF,BB,+DD            | P,S,U,+W               |               |         |

| R1         | TCLK           | EE                     | R                      | 9             | 0       |

| <b>S</b> 1 | 76.8 kHz       | CC                     | Т                      | 8             | 0       |

| <b>V</b> 1 | 1.76 kHz       | AA                     | V                      | 9             | 0       |

| D2         | ~IN            | S                      | DD                     | 1             | Ι       |

| E2         | +5V@1A         | X,R,T,V                | Y,AA,CC,+EE            |               | 0       |

| F2         | RD0            | Р                      | FF                     | 9             | 0       |

| H2         | RD1            | Ν                      | HH                     | 9             | 0       |

| <b>J</b> 2 | RD2            | М                      | JJ                     | 9             | 0       |

| K2         | RD3            | L                      | KK                     | 8             | 0       |

| L2         | RD4            | K                      | LL                     | 9             | 0       |

| M2         | RD5            | J                      | MM                     | 10            | 0       |

| N2         | RD6            | Н                      | NN                     | 10            | 0       |

| P2         | RD7            | F                      | PP                     | 10            | 0       |

| R2         | ~DA DLY        | Е                      | RR                     | 10            | 0       |

| S2         | RESET          | D + B                  | SS + UU                | 5             | 0       |

| T2         | ~ECHO          | С                      | TT                     | 1             | I       |

| U2         | TBMT           | W                      | Z                      | 9             | 0       |

Table 2-3

I/O Port Pin No./Signal Assignments

\*In/Out refers to the RT02-A.

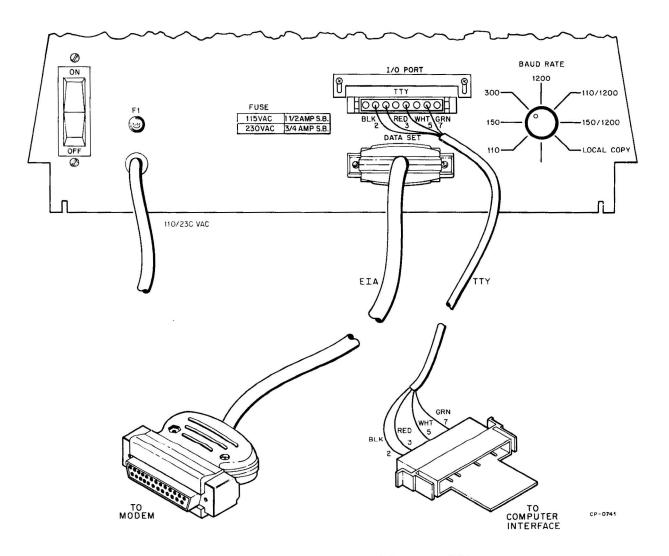

Figure 2-3 shows a typical RT02-A interface configuration using the Mate-N-Lok connector, and a 4-wire twisted pair cable to connect to a DEC KL11 Teletype<sup>®</sup> Interface Control Unit, via an M780 Connector Module.

The maximum distance the RT02-A can be located from the computer depends on the drive capability, Baud rate, and noise immunity of the active line driver, which is usually located at the computer site. Consequently, exact limits cannot be given, however some typical cable lengths and recommended wire sizes for 110 Baud are provided in Table 2-4.

Table 2-5 lists typical TTY interface configurations.

<sup>&</sup>lt;sup>®</sup> Teletype is a registered trademark of Teletype Corporation.

Figure 2-3 Typical RT02-A Interface Configuration - Local (TTY) Installation

| Cable Length<br>(in feet) | Recommended Wire Size |

|---------------------------|-----------------------|

| 1000                      | 22 Gauge              |

| 2000                      | 20 Gauge              |

| 3000                      | 18 Gauge              |