# digital LOGIC HANDBOOK

0.06

## FLIP CHIP" MODULES

# THE LOGIC HANDBOOK FLIP CHIP<sup>®</sup> MODULES 1967 EDITION

FLIP CHIP is a trademark of Digital Equipment Corporation Maynard, Massachusetts.

#### Copyright © 1967 by Digital Equipment Corporation

Digital Equipment Corporation makes no representation that the interconnection of its modular circuits in the manner described herein will notinfringe on existing or future patent rights. Nor do the descriptions contained herein imply the granting of licenses to make, use, or sell equipment constructed in accordance therewith.

FLIP CHIP is a trademark of Digital Equipment Corporation Maynard, Massachusetts.

## PART I: DIGITAL LOGIC PRIMER

## PART II: FLIPCHIP MODULES

# PART III: LOGIC LABORATORY

# PART IV: HARDWARE, OCTAIDS AND PANELAIDS

## PART V: ANALOG - DIGITAL CONVERSION HANDBOOK

PART VI: COMPUTER CATALOG

Hŧ

## PREFACE

### GENERAL PURPOSE MODULES

The first section defines the characteristics of the FLIP-CHIP<sup>™</sup> line of modules which cover the spectrum of application in three series:

- 1. The R series which operates from DC to Two Megahertz.

- 2. The B series which operates from DC to Ten Megahertz.

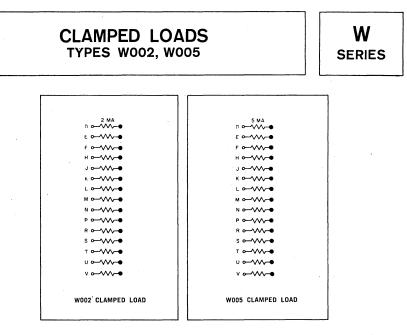

- 3. The W series modules for interfacing with various types of external equipment.

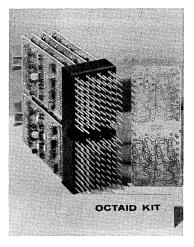

In addition to these various module lines, a totally new approach to subsystem design, OCTAIDS and PANELAIDS are described in detail. These design aids provide the user with a fast, accurate method of assembling such common elements as A to D converters, binary counters, and real time clocks.

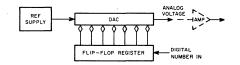

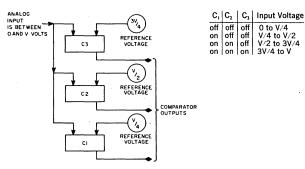

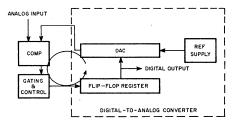

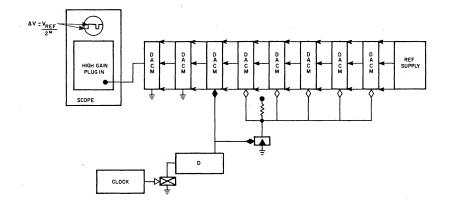

#### ANALOG-DIGITAL CONVERSION

The second section of the Digital Logic Handbook is concerned with Analog-Digital Conversion. A primer on conversion techniques prefaces this section and the complete line of A series modules and A to D converters follow. The system designer is provided with the necessary information to select either a complete A to D converter or the various analog modules. Application notes are included to further aid in the design of special systems.

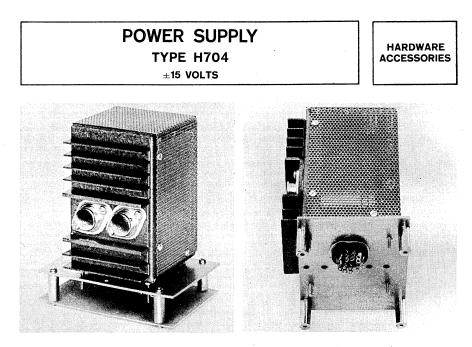

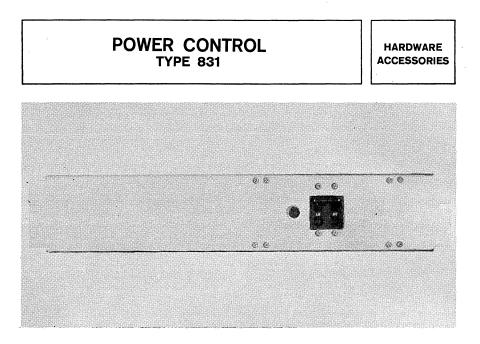

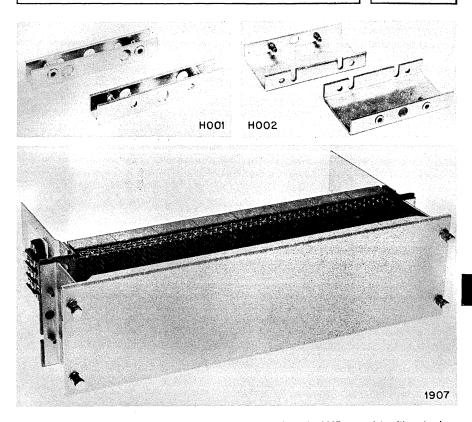

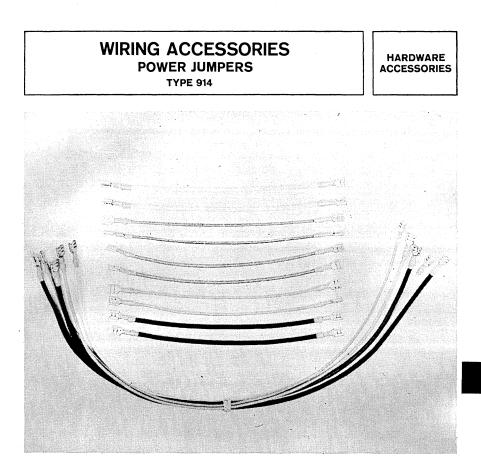

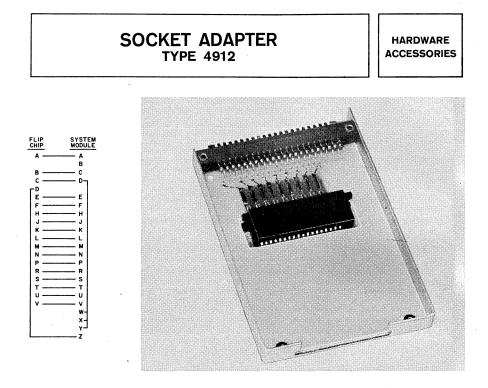

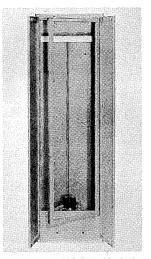

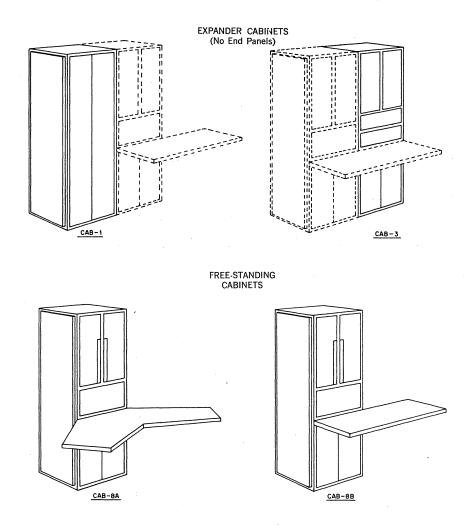

#### HARDWARE

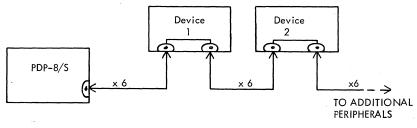

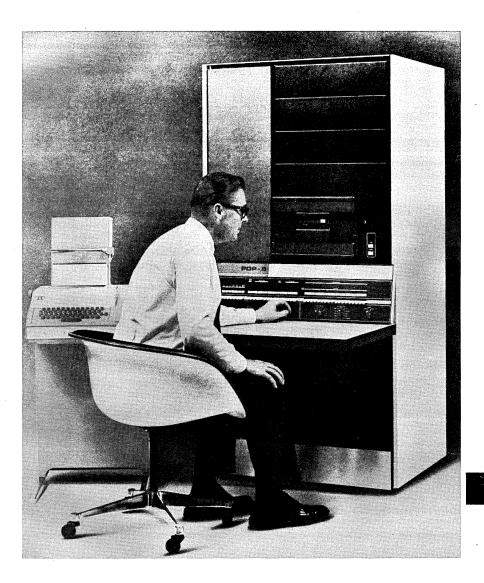

A section which describes Digital's complete line of hardware is included in the Handbook. New in this issue are the 4096 x 13 bit memory and paper tape punch and reader units. All of the hardware necessary for the fabrication of a complete system are included, and each piece of hardware has been field-proven in Digital's PDP series computers.

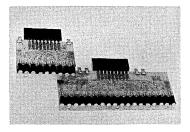

#### MONOLITHIC INTEGRATED CIRCUITS

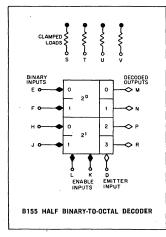

The M series is a completely new line of functional TTL monolithic integrated circuit modules for operation at speeds up to 10 megahertz. These modules are for use where speed is of primary importance and packing density a consideration. Modules are provided which perform the functions of shifting, counting, storage, binary to octal conversion. and gating.

These modules are described in detail in separate literature which can be requested by using the reply form included in this Logic Handbook.

#### INDUSTRIAL CONTROL MODULES

Digital's K Series Industrial Control Modules provide the answer to the problem of using solid state logic in the high noise environment encountered in control systems. All silicon semiconductors and monolithic integrated circuits have been designed into modules providing all necessary functions formerly accomplished by awkward relay devices. K series modules and hardware are designed for installation in standard NEMA enclosures. Connectors for these modules are the field-proven FLIP CHIP<sup>™</sup> connectors which have been used on two generations of Digital's computers and with modules in every conceivable application from steel mills to lathe controls. Connection between terminal strips and electronics are also pluggable, allowing the logic to be installed after field wiring is complete. Standard functions of gating, storage, and counting are provided, plus industrial-oriented AC Input Converter, AC Switch, Timer, Interface Block, and Glow Tube (Indicator) Driver. Sensing and output circuits operate at 115 volts AC for complete electromechanical compatability. Solid state AC switches are fully protected against false triggering, and provisions for interlocking are included.

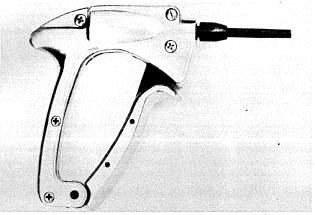

Checkout and trouble shooting are easy with K series modules. Each system input and output has a built-in indicator light and a special test probe provides its own local illumination and built in memory for transient signals as well as steady states.

K series modules provide the solid-state advantages of size reduction, reliability, flexibility, and low cost logic with an added bonus of easy interconnection. For a complete set of specifications and helpful design examples send for the Industrial Controls Handbook by using the reply form attached.

# TABLE OF CONTENTS

| PF     | ·                                                                                                                                                                            | V                              |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| PART I | DIGITAL LOGIC PRIMER                                                                                                                                                         | 1                              |

| N      | UMBER SYSTEM<br>Counting in Different Number Systems<br>Binary Number System<br>Binary-Decimal Conversion<br>Binary-Coded-Decimal Numbers<br>Octal Number System<br>Notation | 2<br>3<br>4<br>5<br>5<br>7     |

| BC     | DOLEAN ALGEBRA         OR Function         AND Function         Identities         Complement         De Morgan's Laws         Boolean Algebra for use with Voltage Levels   | 8<br>9<br>10<br>11<br>11<br>11 |

| BI     | INARY-CODED DECIMAL CODES<br>Four-Bit Codes<br>Arithmetic Operations with the 8421 or Excess 3 Codes<br>Codes Greater than Four Bits                                         | 16<br>16<br>17<br>21           |

| PART I | I FLIP CHIP MODULES                                                                                                                                                          | 23                             |

| R      | SERIES — BASIC LOGIC MODULES (Dc TO 2 MHz)<br>Basic Circuits<br>Logic Configurations<br>Specifications                                                                       | 26<br>38                       |

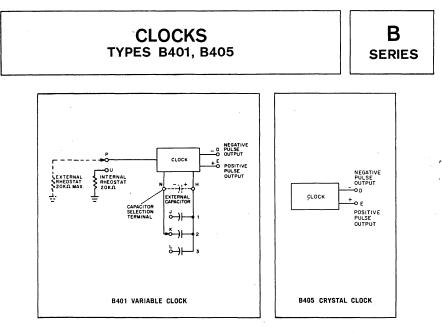

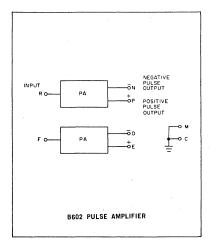

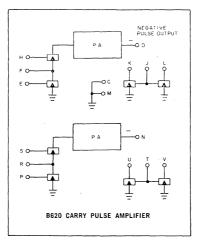

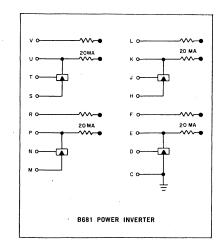

| B      | SERIES — NEGATIVE, HIGH-SPEED LOGIC MODULES (Dc to 10 MHz)<br>Basic Circuits<br>Logic Configurations<br>Specifications                                                       | 84<br>93                       |

| W      | / SERIES — DIGITAL LOGIC INTERFACE MODULES<br>Introduction<br>Specifications                                                                                                 | 130                            |

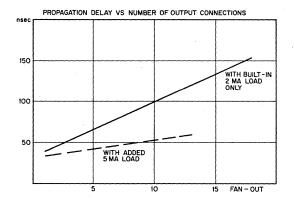

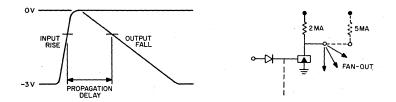

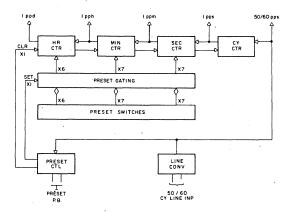

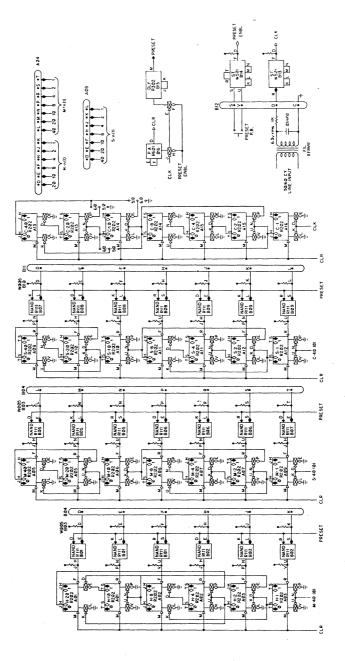

| A      | PPLICATION NOTES<br>Estimating Propagation Delay<br>BCD Counting<br>General Purpose Digital Clocks<br>High-Speed Parallel Adders                                             | 176<br>177<br>184              |

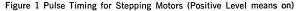

| 32-Position Decoding<br>Stepping Motor Drives (Translators)<br>Generation of Pseudo-Random Sequences | 197  |  |  |  |  |

|------------------------------------------------------------------------------------------------------|------|--|--|--|--|

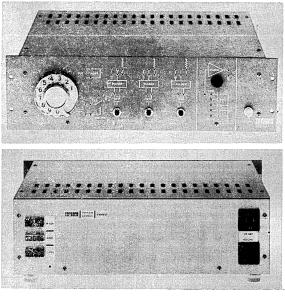

| PART III LOGIC LABORATORY                                                                            | 205  |  |  |  |  |

| Introduction<br>Specification                                                                        |      |  |  |  |  |

| PART IV HARDWARE, OCTAIDS AND PANELAIDS                                                              | 221  |  |  |  |  |

| HARDWARE ACCESSORIES<br>Specifications                                                               |      |  |  |  |  |

| OCTAIDS AND PANELAIDS — PRINTED CIRCUIT BOARD KITS                                                   |      |  |  |  |  |

| Octaid Specifications Panelaid Specifications                                                        |      |  |  |  |  |

| E and F Series — Printed Circuit Boards                                                              |      |  |  |  |  |

| PART V—ANALOG-DIGITAL CONVERSION HANDBOOK                                                            | 275  |  |  |  |  |

| PREFACE                                                                                              | 276  |  |  |  |  |

| CHAPTER I BASIC ELEMENTS OF CONVERSION                                                               | 277  |  |  |  |  |

| CHAPTER II MEASURES OF CONVERTER PERFORMANCE                                                         | 285  |  |  |  |  |

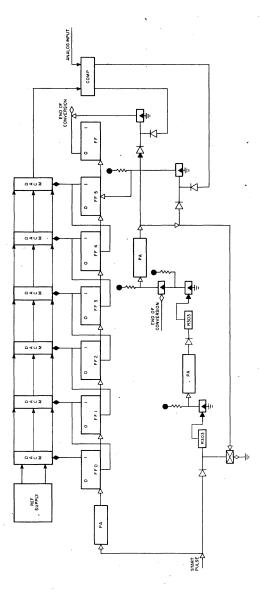

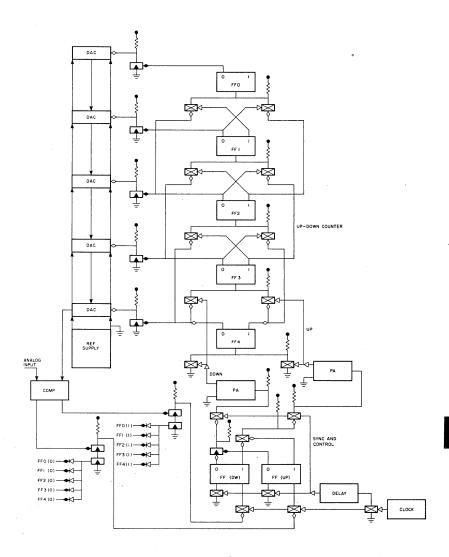

| CHAPTER III SPECIAL ANALOG-TO-DIGITAL CONVERSION TECHNIQUES                                          |      |  |  |  |  |

| CHAPTER IV TYPICAL CONVERTER LOGIC                                                                   |      |  |  |  |  |

| CHAPTER V BASIC CIRCUITS                                                                             |      |  |  |  |  |

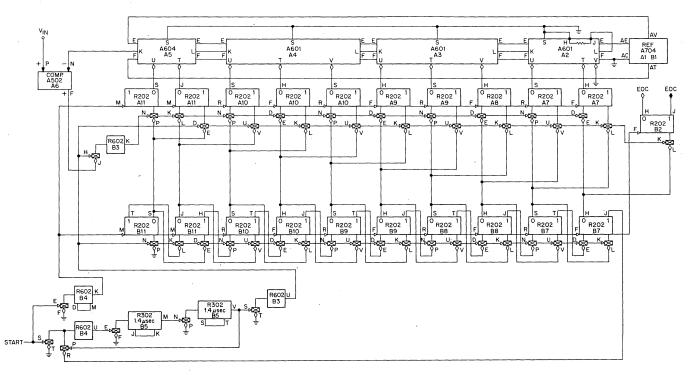

| CHAPTER VI INTERCONNECTION AND CALIBRATION                                                           |      |  |  |  |  |

| CHAPTER VII TESTING AN ANALOG TO DIGITAL CONVERTER                                                   |      |  |  |  |  |

| GENERAL-PURPOSE ANALOG-DIGITAL CONVERTER/MULTIPLEXER                                                 |      |  |  |  |  |

| A SERIES MODULES — ANALOG LOGIC MODULES                                                              | .343 |  |  |  |  |

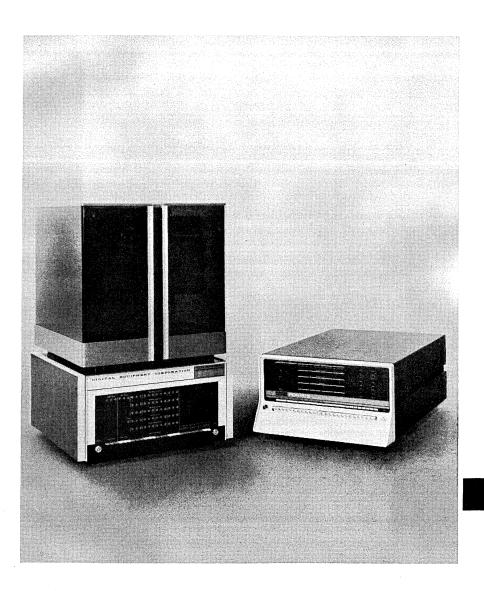

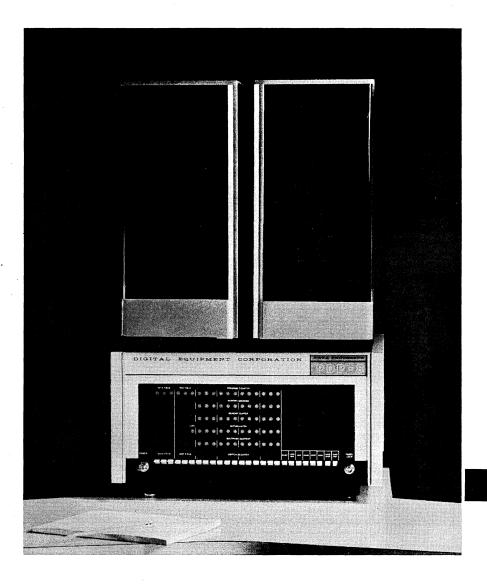

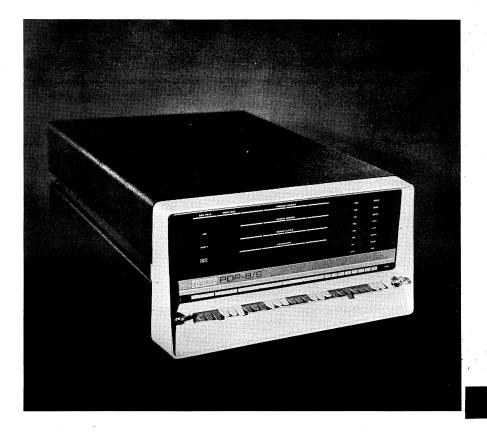

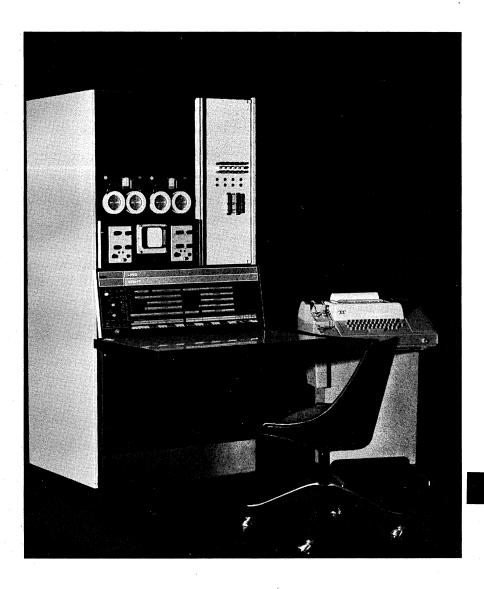

| PART VI COMPUTER CATALOG                                                                             | .357 |  |  |  |  |

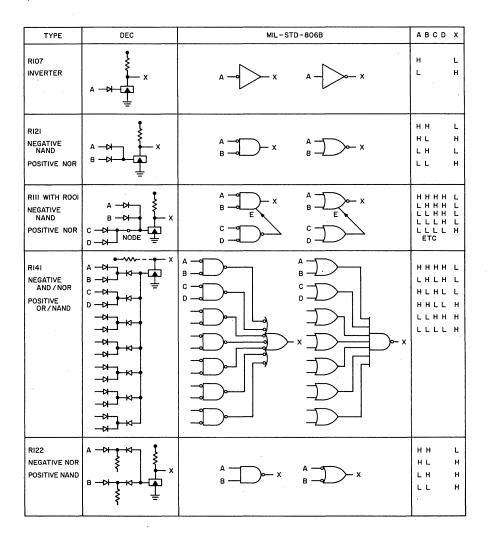

| APPENDIX I MIL — STD. — 806B and DEC Symbol Comparison                                               | .377 |  |  |  |  |

| APPENDIX 2 Powers of Two Table                                                                       | .385 |  |  |  |  |

| APPENDIX 3 Abbreviations                                                                             | .386 |  |  |  |  |

| APPENDIX 4 Definitions                                                                               |      |  |  |  |  |

| APPENDIX 5 Bibliography of Digital Logic                                                             | .388 |  |  |  |  |

| NUMERICAL INDEX                                                                                      |      |  |  |  |  |

| PRICE LIST                                                                                           | .393 |  |  |  |  |

## R AND B SERIES MODULE FEATURES

#### COMPLETENESS OF LINE

A full selection of high-volume standard modules with sufficient types and accessory hardware for building complete systems. 150 items in the current product line with 70 items in stock for immediate delivery.

#### FREQUENCY RANGE

Dc to 10 MHz in two fully compatible series.

#### SIGNAL LEVELS

0 volts and --- 3 volts.

#### FAN-OUT

70 ma from pulse amplifiers 18 ma from diode gates 15 ma from typical flip flops (typical input loads: 1-3 ma)

#### **CLAMPED LOGIC**

Signal voltages are independent of loading. All signals clamped to -3 volts.

#### WIDE TEMPERATURE RANGE

FLIP CHIP silicon modules operate over a temperature range of  $-20^{\circ}$ C to  $+65^{\circ}$ C.

#### GOOD NOISE IMMUNITY

All low speed modules and some high speed modules have diode isolated inputs. Typical noise rejection for diode gates: at 0v - 1.0v

#### LOW POWER DISSIPATION

Typically: 150 mw per flip-flop 40 mw per diode gate

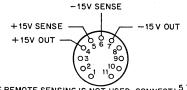

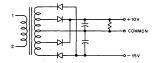

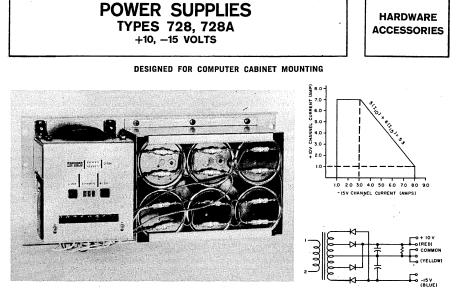

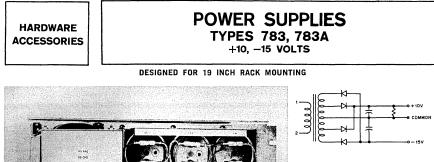

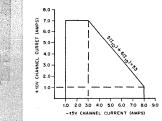

#### SIMPLE POWER REQUIREMENTS

Two supply voltages required: +10v and -15v. All modules have standard power connections. Complete line of power supplies available as standard items.

#### ULTIMATE IN LOGICAL FLEXIBILITY

Extremely flexible flip-flop configuration permits JK, RS, RST, or T memory elements to be constructed without modifying modules.

Gates and power amplifiers may be paralleled for performing positive OR functions. A wide range of interfacing modules are available for converting standard DEC levels to external equipment reuirements.

# GENERAL CHARACTERISTICS - R AND B SERIES MODULES

#### FREQUENCY RANGES

Dc to 2 MHz (R Series) Dc to 10 MHz (B Series)

#### LOGIC LEVELS

0v to -0.3 upper level -3.2 v to -3.9v lower level

#### **HIGH FAN-OUT**

High driving capability for all modules. Typically: 70 ma — pulse amplifiers 18 ma — diode gates

15 ma - flip-flops

#### HIGH FAN-IN

Low input current requirements. Typically 1 ma to 3 ma. Diode gate inputs may be expanded as high as 25 inputs with gate expander modules.

#### ALL LOGIC LEVELS DIODE CLAMPED

Signal voltages are diode clamped at -3v independent of fan-out and independent of other input conditions at the load.

#### LOW POWER DISSIPATION

Typically: 150 mw per JK flip-flop 40 mw per diode gate

#### CONSERVATIVE DESIGN

All circuits can tolerate at least  $\pm 20\%$  variations in power supply voltage.

| NOISE IMMUNITY   | At 0 volts | At —3 volts         |

|------------------|------------|---------------------|

| Diode Gates      | 1.0v       | 1.5v                |

| DCD Gates        | 0.7v       | Totally insensitive |

| 10 MHz Inverters | 0.5v       | 0.5 volts           |

#### TEMPERATURE RANGE

$-20^{\circ}$ C to  $+65^{\circ}$ C on all silicon FLIP CHIP modules. A few W-Series power driving accessory modules include germanium semiconductors as indicated on their data sheets, reducing their upper limit to  $+55^{\circ}$ C.

#### COMPATIBILITY

Many specialized interface modules available providing:

- --- Input voltage compatibility between  $\pm 30v$ .

- Output voltage compatibility between ±135v.

- ---- Output currents as high as 10 amperes.

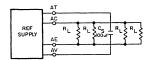

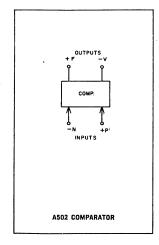

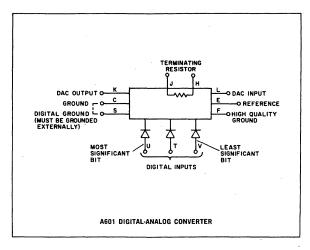

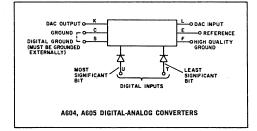

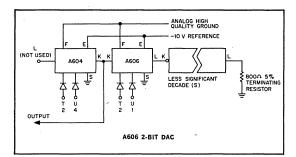

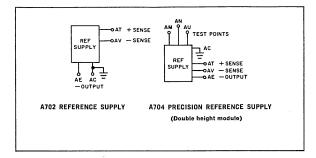

#### ANALOG-DIGITAL CONVERSION

Complete selection of interface modules for building hybrid configurations including: Comparators

D to A converter modules

Analog switch modules

Reference supplies

#### POWER REQUIREMENTS

+10v nominal, module pin A -15v nominal, module pin B ground, module pin C

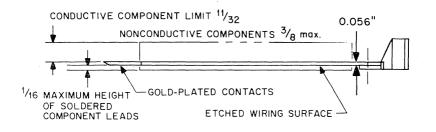

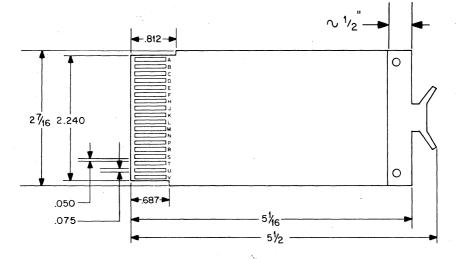

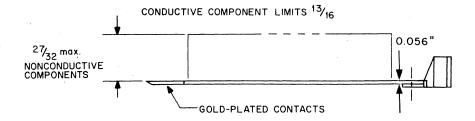

#### BOARD SPECIFICATIONS

$\begin{array}{l} \mbox{Material} \longrightarrow G10 \mbox{ FR4 Glass Epoxy} & \begin{tabular}{l} & \end{tabular} \\ \mbox{Copper Coating} \longrightarrow 2 \mbox{ oz. (0.0028 inches)} \\ \mbox{Thickness} \longrightarrow 0.055 \pm .003 \mbox{ inches overall} \\ \mbox{Gold Plated Contacts} \longrightarrow 0.00015 \mbox{ inch gold on copper} \end{array}$

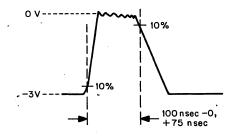

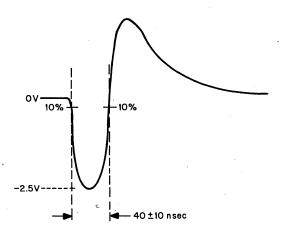

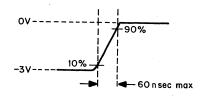

#### STANDARD FLIP CHIP WAVEFORM DEFINITIONS

**R** Series

STANDARD PULSE

Edge Requirements for activation of R Series DCD pulse inputs

XII

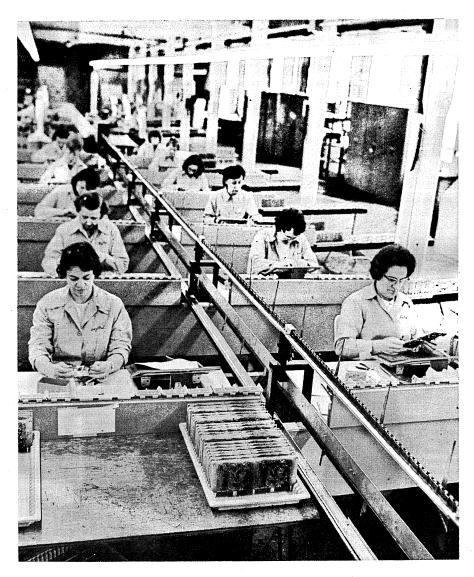

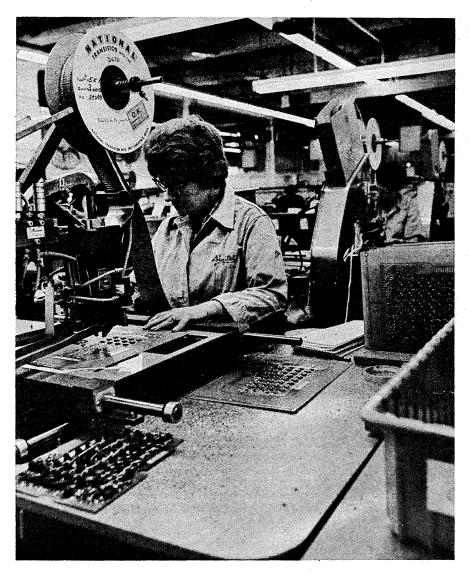

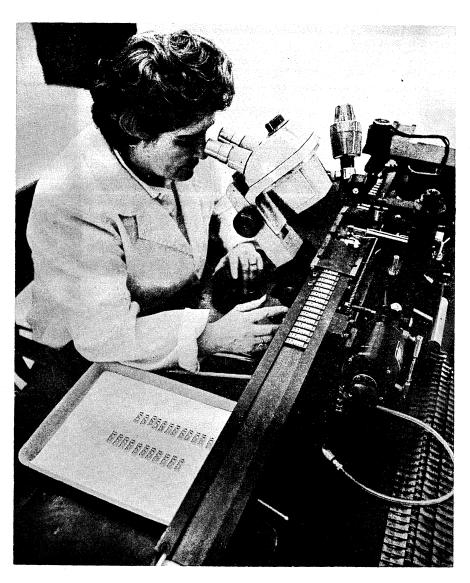

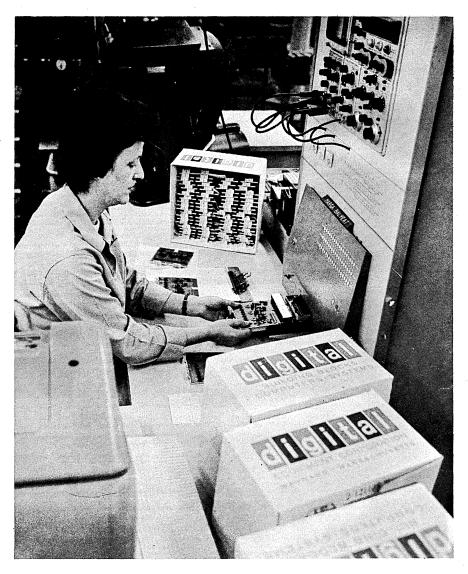

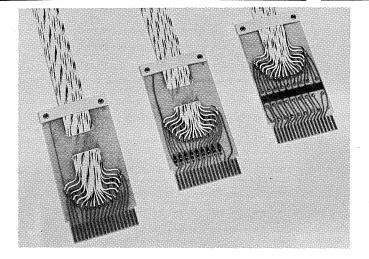

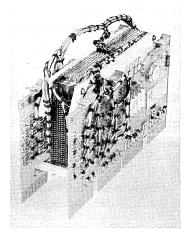

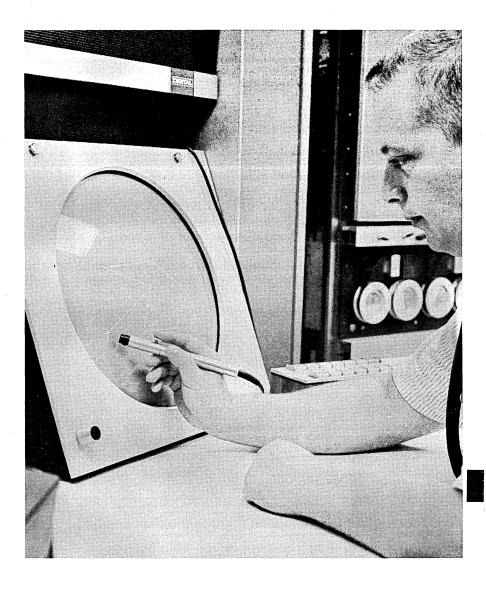

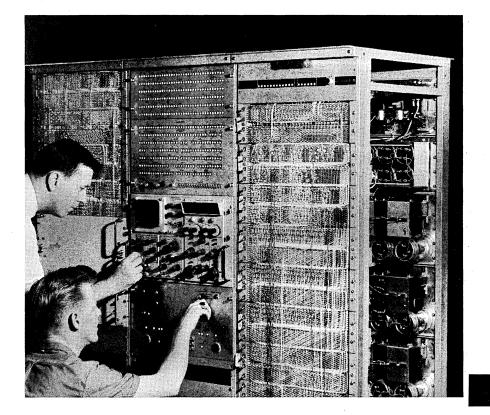

FLIP CHIP assembly line combines automated manufacturing steps with computer controlled checkout for lower cost, more reliable circuits.

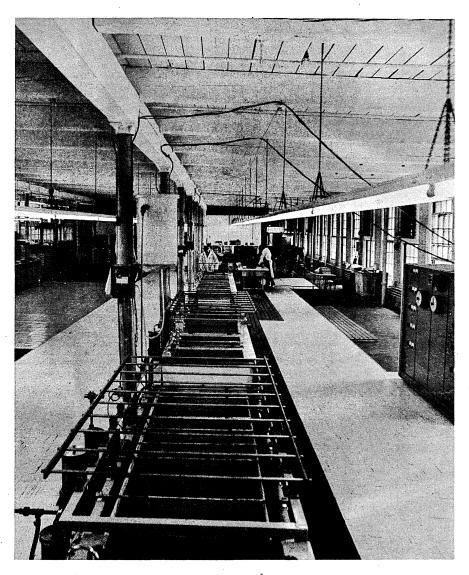

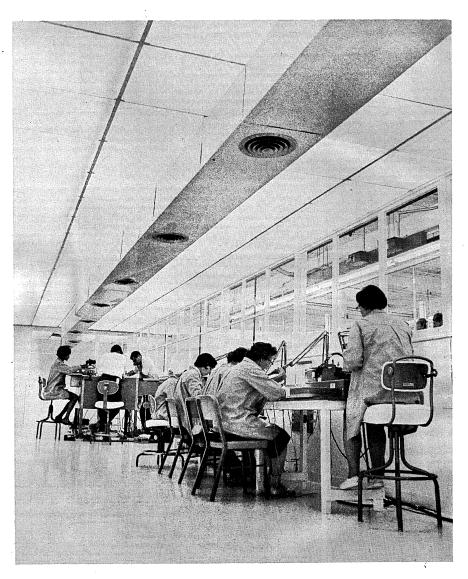

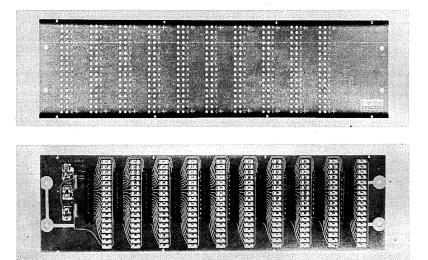

Printed circuits on FLIP CHIP boards are produced in an etching-plating line which includes an 18-step process to gold-plate the plug-in contacts.

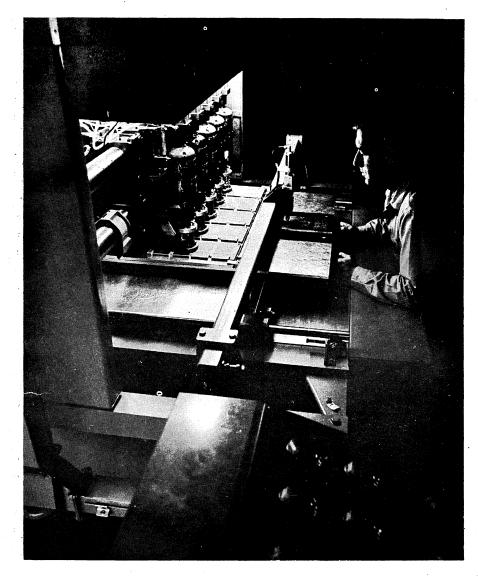

Ten spindle automatic machine drills 40 boards simultaneously, provides precision component layout.

Discrete components are positioned and crimped in place at rates up to 30  $\,\rm per$  minute on pantograph controlled inserting machine.

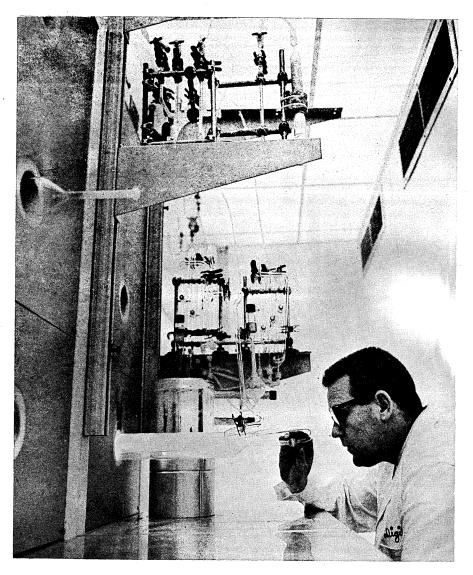

High quality diffusion furnaces used for the generation of semiconductor junctions.

Substrate screening and semiconductor mounting operations are performed under clean room conditions.

Thermal compression bonding ties semiconductors into hybrid networks.

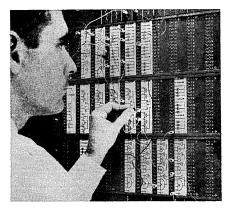

To insure reliability, a wide variety of dynamic tests are performed on-line by a computer controlled system.

# PART I: DIGITAL LOGIC PRIMER

1

# NUMBER SYSTEMS

Early number systems were crude and awkward to use. A simple system, using a mark for each unit, cannot be used to express large quantities such as a thousand. Later systems, such as Roman numerals, were a great improvement, but still extremely difficult to manipulate in ordinary arithmetic. With the Arabic, or decimal, number system, common arithmetic operations, which correspond to true to life operations, can be defined and easily used.

The decimal number system uses ten symbols representing the quantities 0 through 9. Other numbers are constructed by assigning different values (or weights) to the position of the symbol relative to the decimal point. For example, the number 008 (more commonly written simply 8) represents eight units, while the number 080 (again more commonly written just 80) represents a quantity of eighty, and the number 800 represents a quantity of eight hundred.

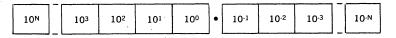

Each position in a decimal number has a value which is ten times the value of the next position to the right. In other words, every positional weight is a multiple of ten and can be expressed by ten raised to some power. The tens position is  $10^1$ , the hundreds position is  $10^2$ , the thousands position is  $10^3$ , etc.

Simple exponential arithmetic shows that the ones position is  $10^{\circ} = 1$  (in fact, any number raised to the 0 power, except 0, is equal to 1). This progression of increasing exponents can be continued as far as desired to the left of the decimal point. The same progression can also be extended to the right of the decimal point, but here the exponents will be negative. For example, the first position to the right of the decimal point is the tenths position, it has a weight of  $10^{-1}$  or  $1/10^{1}$ .

Figure 1 represents a general skeleton for any decimal number. The symbol which is placed in any of the positions indicates how many multiples of that power of 10 are in the total quantity represented by the number.

#### Figure 1

Ten is not a particularly magical number; there is no reason for the number of symbols to be extended to ten (or limited to ten). It would be just as simple to have twelve symbols or eight symbols or two symbols, or any other number of symbols. However, one of the features of the decimal system is that there is only one way in which any given number can be written, and on seeing a number written, there is only one value which can be ascribed to it. In order to keep this feature in a number system with a different number of symbols, it is necessary to change the weights of the different positions. The values which must be assigned, in fact, turn out to be powers of the number of symbols available. The number of symbols used is called the radix of the number system. Figure 2 shows the skeleton of a general number system with a radix R.

| R٩ | -   | R <sup>3</sup> | R² | R1 | R <sup>o</sup> | • | R-1 | R-2 | R∙3 |   | R <sup>.</sup> N |  |

|----|-----|----------------|----|----|----------------|---|-----|-----|-----|---|------------------|--|

|    | - 1 |                |    |    |                | ļ |     |     |     | - | L                |  |

#### Figure 2

Examples of counting in different number systems are illustrated in Figure 3. The duodecimal number system has a radix of 12 and the symbols A and B are used here to represent the quantities 10 and 11, respectively. The octal number system has a radix of 8 and the binary number system has a radix of 2. The positional weights are given in decimal at the top of each column.

## COUNTING IN DIFFERENT NUMBER SYSTEMS

| DECIMAL                                                                                                                                                                                                                                                                    | DUODECIMAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | OCTAL                                                                                                                                                                                              | s –                                                                                              | BINARY                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------|

| to<br>en<br>ne<br>ss                                                                                                                                                                                                                                                       | t<br>w<br>lo<br>vn<br>ee<br>Ss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | e<br>i g o<br>h n<br>s s                                                                                                                                                                           | i<br>x e<br>t i<br>e g<br>e h<br>n t<br>s s                                                      | f<br>oto<br>uwn<br>roe<br>sss                        |

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>1<br>0<br>1<br>1<br>1<br>2<br>1<br>3<br>1<br>4<br>1<br>5<br>1<br>6<br>1<br>7<br>8<br>9<br>1<br>0<br>1<br>1<br>1<br>2<br>1<br>3<br>1<br>4<br>1<br>2<br>1<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2 | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>A<br>B<br>1<br>0<br>1<br>1<br>2<br>1<br>3<br>1<br>4<br>5<br>6<br>7<br>8<br>9<br>A<br>B<br>1<br>1<br>1<br>2<br>1<br>3<br>1<br>4<br>5<br>6<br>7<br>8<br>9<br>A<br>B<br>1<br>1<br>1<br>2<br>1<br>3<br>1<br>4<br>5<br>6<br>7<br>8<br>9<br>A<br>B<br>1<br>1<br>1<br>1<br>2<br>1<br>3<br>1<br>4<br>5<br>6<br>7<br>8<br>9<br>A<br>B<br>1<br>1<br>1<br>1<br>1<br>2<br>1<br>3<br>1<br>4<br>5<br>6<br>7<br>8<br>9<br>A<br>B<br>1<br>1<br>1<br>1<br>5<br>1<br>6<br>1<br>7<br>1<br>1<br>1<br>1<br>2<br>1<br>3<br>1<br>4<br>5<br>1<br>6<br>1<br>7<br>1<br>8<br>9<br>1<br>1<br>1<br>1<br>5<br>1<br>6<br>1<br>7<br>1<br>8<br>9<br>1<br>1<br>1<br>1<br>1<br>1<br>5<br>1<br>6<br>1<br>7<br>1<br>8<br>9<br>1<br>8<br>9<br>1<br>1<br>1<br>1<br>1<br>5<br>1<br>6<br>1<br>7<br>1<br>8<br>9<br>1<br>8<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>5<br>1<br>6<br>1<br>7<br>1<br>8<br>9<br>1<br>8<br>1<br>7<br>1<br>8<br>9<br>1<br>8<br>1<br>7<br>1<br>8<br>9<br>1<br>8<br>1<br>7<br>1<br>8<br>1<br>7<br>1<br>8<br>1<br>7<br>1<br>8<br>1<br>7<br>1<br>8<br>1<br>7<br>1<br>8<br>1<br>2<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>9<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>1<br>8<br>1<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>8<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>8<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | $\begin{array}{c} 0\\ 1\\ 2\\ 3\\ 4\\ 5\\ 6\\ 7\\ 1\\ 0\\ 1\\ 1\\ 1\\ 2\\ 1\\ 3\\ 1\\ 4\\ 1\\ 5\\ 1\\ 6\\ 1\\ 7\\ 2\\ 0\\ 2\\ 1\\ 2\\ 2\\ 3\\ 2\\ 4\\ 2\\ 5\\ 2\\ 6\\ 2\\ 7\\ 3\\ 0\\ \end{array}$ | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>0<br>1<br>0<br>1<br>0 | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |

Figure 3

## BINARY NUMBER SYSTEM

Since the binary number system uses two symbols, it has a radix of 2 and the positional weights are powers of 2. Examination of the binary counting sequence, Figure 3, shows that the binary number system follows the same number system skeleton which was previously outlined. Because of this, the method of performing arithmetic operations in binary numbers is the same as the methods used for decimal numbers. For example, 0 + 0 = 0, and 0 + 1 = 1. Since there is no symbol for two, however, 1 + 1 = 0 and 1 to carry. The tables for performing arithmetic operations are given in Figure 4. Since there are only two symbols, the tables are considerably simpler than those required to outline the same operations in the decimal number system. This, of course, leads to considerably simpler computer circuitry also. Some typical examples of arithmetic operations in binary are shown in Figure 5.

Binary Addition

A + B = S (Sum) 0 + 0 = 0 0 + 1 = 1 1 + 0 = 11 + 1 = 0 & 1 to carry

#### Binary Multiplication

$\begin{array}{l} \mathsf{A}\times\mathsf{B}=\mathsf{P} \mbox{ (Product)}\\ \mathsf{0}\times\mathsf{0}=\mathsf{0}\\ \mathsf{0}\times\mathsf{1}=\mathsf{0}\\ \mathsf{1}\times\mathsf{0}=\mathsf{0}\\ \mathsf{1}\times\mathsf{1}=\mathsf{1} \end{array}$

**Binary Subtraction**

A - B = D (Difference) 0 - 0 = 0 0 - 1 = 1 & 1 to borrow 1 - 0 = 11 - 1 = 0

**Binary Division**

| Ā | ÷ | В | = | Q | (Qı | iotie | ent) |

|---|---|---|---|---|-----|-------|------|

| 0 | ÷ | 0 | = | ? |     |       |      |

|   | ÷ |   |   |   |     |       |      |

| 1 | ÷ | 0 | = | ? | -   |       |      |

| 1 | ÷ | 1 | = | 1 |     | •     |      |

Figure 4

| Addition       |        | Subtraction        |

|----------------|--------|--------------------|

| 101101         | 101101 | 101101 101101      |

| + 1010         | +1100  | -1100 $-11001$     |

| 110111         | 1H001  | 100001 10100       |

| Multiplication | · •    | Division           |

| 101101         |        | 1001               |

| × 101          |        | $101\sqrt{101101}$ |

| 101101         |        | 101                |

| 00000          |        | 0001               |

| 101101         |        | <u>0000</u><br>10  |

| 11100001       |        | 00                 |

|                | 1.1    | $\frac{33}{101}$   |

|                |        | 101                |

Figure 5

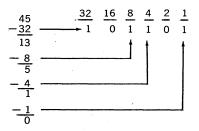

### **BINARY-DECIMAL CONVERSION**

Numbers can be converted from binary to decimal and vice versa by hand by using the methods outlined in Figure 6. As shown, a binary number is converted to decimal simply by adding the positional weights of all those positions where a 1 appears. Decimal to binary conversion is more a process of trial and error. First, subtract the largest power of 2 which will go into the number that is being converted. This process is repeated on the remainder until the remainder is equal to 0. The binary number then has ones in those positions with the values corresponding to the powers of 2 which were subtracted; all other positions are 0.

#### BINARY TO DECIMAL CONVERSION

DECIMAL BINARY CONVERSION

#### **BINARY-CODED-DECIMAL NUMBERS**

Since computer inputs and outputs must often be in decimal notation, a variety of special codes are used. These hybrid number systems are referred to as binary-coded decimal or BCD.

An example of BCD is the 8421 code. This is often referred to as simply BCD since the weights of the positions are the same as in the binary number system, as illustrated below.

| Decimal        | 8421 Code |

|----------------|-----------|

| 0              | 0000      |

| 1              | 0001      |

| 2              | 0010      |

| 3              | 0011      |

| 4              | 0100      |

| 5              | 0101      |

| 6 <sup>.</sup> | 0110      |

| 7              | 0111      |

| 8              | 1000      |

| 9              | 1001      |

The 8421 code employs four bits to represent each decimal digit. For instance, the number 987 may be represented by the 12-bit number 1001 1000 0111. Although this number contains only ones and zeros, it is not a true binary number since it does not follow the rules previously established. Arithmetic operations with BCD would be quite involved. However, it is relatively easy for the computer to convert to true binary, perform the necessary calculations, and reconvert to BCD.

BCD numbers do not always follow the pure binary number system. Special purpose number systems such as Excess Three Code, Gray Code, and Biquinary Code are often used.

## OCTAL NUMBER SYSTEM

As the name implies, the octal number system has a radix of 8, i.e., it uses eight discreet symbols: 0, 1, 2, 3, 4, 5, 6, and 7. The positional weights in the octal number system are powers of 8.

The octal number system is widely used by digital engineers and computer programmers since it can easily be converted to binary. At the same time, it is considerably easier to work with, or to record, octal numbers than to use a long string of binary zeros and ones.

The binary-octal conversion may be performed quite simply due to the fact that 8 is the third power of 2. This produces a direct correlation between the successive 3-bit groups in a binary number and the octal digits. That is, an octal number may be converted to binary digit by digit, while with a decimal number the entire number must be converted to binary. The table for octal to binary conversion is shown in Figure 7.

#### OCTAL TO BINARY CONVERSION

| Octal | Binary |

|-------|--------|

| 0 '   | 000    |

| 1     | 001    |

| 2     | 010    |

| 3     | 011    |

| 4     | 100    |

| 5     | 101    |

| 6     | 110    |

| 7     | 111    |

Figure 7

Using this table, the octal number 777, for example, could be easily and directly converted to the binary number 111111111. Going in the opposite direction, the binary number 110101110 can be converted directly to 656. (As in other number systems, zeros are always assumed in the most significant bits. For example, the number 1110110 converts to 166 in octal.)

Arithmetic operations in octal are quite similar to the operations in decimal. A more detailed discussion of this can be found in some of the reference books in the bibliography.

## NOTATION

When there may be some doubt as to the number system being employed, it is customary to indicate this by writing the radix of the number system (in decimal) as a subscript to the number. For example,  $777_8$  indicates that this is the number 777 written in the octal number system. The same number in the decimal system would be  $511_{10}$ .

In working with different number systems it is extremely important to be certain which system is being used. For example, take that tricky little question, "what's two and two?"

2 + 2 = (meaningless for radix of 2)

$2 + 2 = 11_3$

$2 + 2 = 10_4$

$2 + 2 = 4_{6}$  or more.

# **BOOLEAN ALGEBRA**

Boolean algebra was introduced in 1847 by an English mathematician, George Boole. The purpose of the algebra was to find a shorthand notation for the system of logic originally set forth by Aristotle. Aristotle's system dealt with statements which were considered to be either true or false, but never partially true or false. Boole's algebra was based on a single valued function with two discrete possible states.

Boolean algebra lay almost dormant until recent times. Today, however, it is gaining widespread recognition as an efficient method for handling any single valued function with only two possible states. When it is applied to binary arithmetic, the two states are 0 and 1. When discussing a switch, the two values are open and closed.

Figure 8 Switch Analogy

The convention used will be that the open state corresponds to the 0 state, while the closed state corresponds to the 1 state.

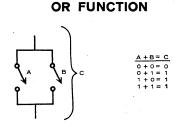

Figure 9 OR Function

If two switches, A and B, are connected in parallel to form a gate, inspection shows that the gate can only transmit information if A or B or both are in the transmitting state, i.e., closed. This is written in equation form as

$$A + B = C$$

(A or B equals C)

Figure 9 shows the parallel combination of two switches along with a table giving the value of C for all possible values of A and B.

Figure 10 Compound OR Functions

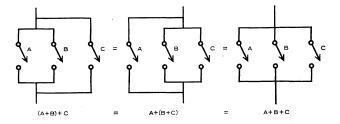

By adding a third gate in parallel, as in Figure 10 it becomes obvious how the OR function may be extended to any number of variables. This figure also serves to illustrate that the communicative and associative laws are valid for the OR function, i.e.,

A + B = B + A $(A + B) + C \equiv A + (B + C) \equiv A + B + C$

Figure 11 AND Function

If two or more gates are placed in series, the result is known as an AND gate. Inspection of the arrangement in Figure 11 shows that the resulting gate will transmit only if both A and B are closed, i.e., equal to 1. The equivalent equation in Boolean form is

AB = C

(A and B equals C)

Figure 12 Compound AND Functions

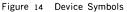

Figure 12 demonstrates how the AND function is applied to more than one variable. The commutative and associative laws also hold.

AB = BA

$A(BC) \equiv (AB)C \equiv ABC$

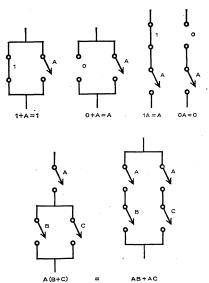

**IDENTITIES**

. .

Figure 13 Indentities

10

To enable the simplification of Boolean functions, there are many identities which are helpful. In Figure 13 the combination of switches and corresponding equations demonstrate these identities.

## COMPLEMENT

If two gates are connected so that the same signal will open both of them or close both of them simultaneously, the switches are given the same symbol. If two gates are connected so that a single signal will open one gate while closing the other gate, and vice versa, these gates are said to be the complement of each other. Thus, if one gate is labeled A, the other gate will be labeled  $\overline{A}$  (read "not A" or "A not").

An entire function may also be complemented. For example,

if D = A(B + C)then  $\overline{D} = \overline{A(B + C)}$

The use of one label for more than one gate makes the following identities helpful:

$$A + A = A \qquad A + \overline{A} = 1 \qquad \overline{A} = A$$

$$AA = A \qquad A\overline{A} = 0$$

## DE MORGAN'S LAWS

Two unique laws which can be applied only to Boolean algebra are known as De Morgan's laws.

$$\overline{A + B + C + \ldots + N} = \overline{A}\overline{B}\overline{C} \dots \overline{N}$$

$$\overline{A}\overline{B}\overline{C} \dots \overline{N} = \overline{A} + \overline{B} + \overline{C} \dots + \overline{N}$$

These laws may be verified by constructing a table of various possible values.

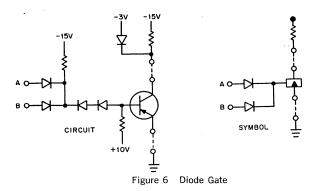

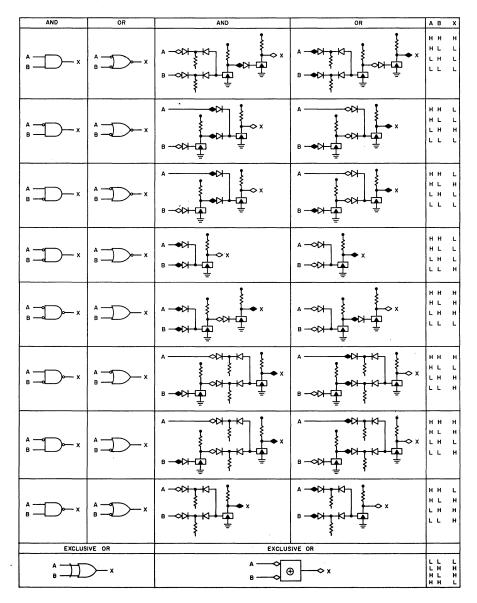

### BOOLEAN ALGEBRA FOR USE WITH VOLTAGE LEVELS

Since DEC voltage levels have only two possible values, Boolean algebra can also be useful in the study of these levels.

#### it

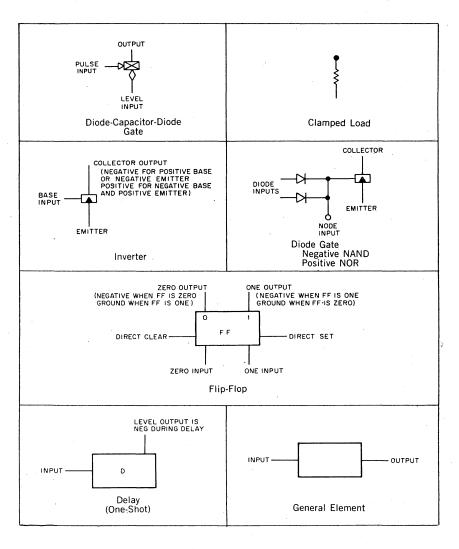

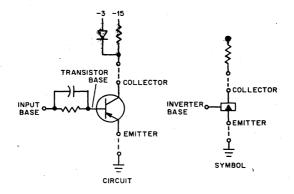

An inverter or single input diode gate may be used to perform a complement. If the emitter is at ground and a signal is applied to the base, the resulting output is the complement of the base input as shown in Figure 15.

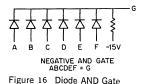

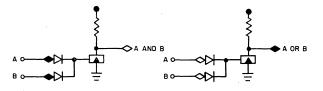

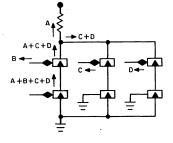

R, B, and W Series Standard levels are defined as -3 volts = 1, and 0 volts = 0, hence a simple AND gate is formed by diodes shown in Figure 16. Only if A and B and C and D and E and F are negative will the resulting output G be negative.

Inspection of these diode units shows that the AND gate becomes an OR gate if the levels are defined in the opposite manner; i.e., if ground is defined as a 1 and -3 volts is defined as a 0. This is a demonstration of De Morgan's law.

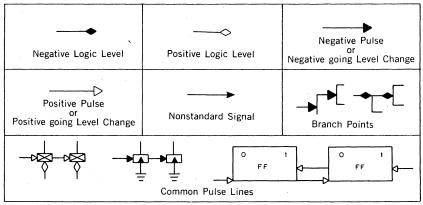

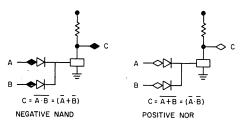

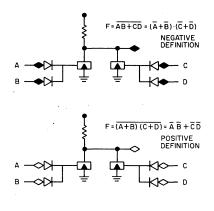

The use of symbols for signal definitions helps the designer keep track of these definitions if he wants to change conventions in a system. The symbols used are shown in Figure 17. Figure 18 shows the basic diode gate with its corresponding negative and positive logic definitions.

Figure 17 Symbols for Standard Signals

13

Figure 18 Diode Gate Definitions

Regardless of level convention chosen, there is only one unique state which indicates coincidence of inputs for the diode gate shown. That is, if, and only if both inputs are —3 volts, the output will be at ground. This means that in a decoding situation, the only active decoder output is ground in either definition of logic levels.

The circuit design is such that a number of gates may be connected together at a common point to produce a positive OR function. In Figure 19, if either gate output goes to ground, the output of the logic will be ground. Thus a convenient function is derived.

Figure 19 OR Gate Definitions

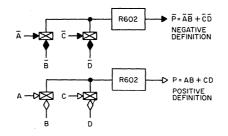

The DCD gate performs a positive AND function. If the DCD gate could be used as a separate logic element (not in conjunction with pulse amplifiers or flip-flops) its positive and negative definitions would be as shown in Figure 20.

Figure 20 DCD Gate Definitions

When DCD gates are used in conjunction with an R602 Pulse Amplifier, for example, the functions of the combined elements are defined as shown in Figure 21.

# **BINARY-CODED DECIMAL CODES**

The digital computer can be thought of as an assemblage of two-state devices because it manipulates the ones and zeros of the binary number system. People, on the other hand, are more accustomed to decimal numbers, and for this reason it is often desirable to build a computing system which can be operated in decimal.

To build a decimal computer with two-state devices, it is necessary to encode the decimal digits with binary bits. Four binary bits are needed. Although only 10 of the 16 permutations possible with the 4-bit decade will be used, all are available. The number of codes that can be generated is calculated as follows:

$$\frac{16!}{6!} \simeq 2.9 \times 10^{10}$$

The choice of a code is obviously important. Desirable features of the code are: ease in performing arithmetic operation, economy of storage space, economy of gating operations, error detection and correction, and simplicity. Several possible codes are shown below, followed by a detailed explanation of arithmetic operations using two especially convenient codes, the 8 4 2 1 and the Excess 3.

# FOUR-BIT CODES

The 8 4 2 1 code is commonly referred to simply as binary-coded decimal because the weights of the positions are the same as in the binary number system. Arithmetic operations are easily performed using the same basic method as in binary since the number sequence is the same.

In the Excess 3 code, a decimal number D is represented by the binary equivalent of the number D + 3. The Excess 3 code is not a weighted code, but since it follows the same number sequence as binary, it is useful in arithmetic operations. Addition is facilitated since the need for a correction factor is easily detected and easily implemented. Because it is self-complementing, the Excess 3 code is also useful in subtraction.

The 2 4 2 1 is a self-complementing weighted code which is commonly employed in counting systems. Other examples of four-bit weighted codes include the 5 4 2 1, the 5 3 1 1, and the 7 4 -2 -1 code. All of these codes are shown in Figure 22.

More than four bits may be used in each decade to provide additional special features such as the detection of errors and the simplification of decoding.

| DECIMAL | 8421 | Excess 3 | 2421 |

|---------|------|----------|------|

| 0       | 0000 | 0011     | 0000 |

| 1       | 0001 | 0100     | 0001 |

| 2       | 0010 | 0101     | 0010 |

| 2<br>3  | 0011 | 0110     | 0011 |

| 4       | 0100 | 0111     | 0100 |

| 5       | 0101 | 1000     | 1011 |

| 6       | 0110 | 1001     | 1100 |

| . 7     | 0111 | 1010     | 1101 |

| 8       | 1000 | 1011     | 1110 |

| 9       | 1001 | 1100     | 1111 |

|         |      |          |      |

| DECIMAL | 5421 | 5311     | 7421 |

| 0       | 0000 | 0000     | 0000 |

| 1       | 0001 | 0001     | 0111 |

| 2       | 0010 | 0011     | 0110 |

| 3       | 0011 | 0100     | 0101 |

| 4       | 0100 | 0101     | 0100 |

| 5       | 1000 | 1000     | 1010 |

| 6       | 1001 | 1001     | 1001 |

| 7       | 1010 | 1011     | 1000 |

| 8       | 1011 | 1100     | 1111 |

| 9       | 1100 | 1101     | 1110 |

Figure 22 Four-bit decimal codes

### ARITHMETIC OPERATIONS WITH THE 8 4 2 1 OR EXCESS 3 CODES

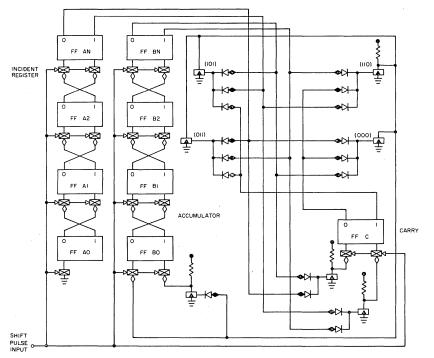

Because the 8 4 2 1 and the Excess 3 codes follow the same number sequence as the binary number system, standard binary methods may be used. However, in binary notation sitxeen states are represented with four bits. In binary-coded decimal only ten of these states are used; therefore, special correction factors must be added to account for the six unused states.

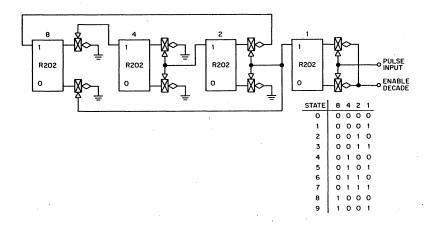

### Counting

In a binary-coded decimal (BCD) counter, the corrective action is very simple. The counter is divided into four-bit decades, and special gating is added to each decade. This gating detects the number 9 and reroutes the next count pulse so that it will reset the decade to 0 and generate a carry to the next decade.

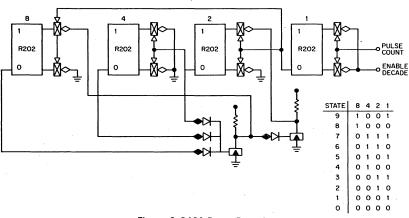

In a down counter, the same approach is used. Starting with a standard binary down counter, the number 0 is detected, and the next count input resets the counter to the appropriate 9 designation and produces a borrow.

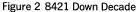

A reversible BCD counter may be implemented by combining the techniques for the individual up and down counters. Such a counter, however, is more difficult to construct than a single direction counter since provision must be made for isolating the carry and borrow chains and for assuring that count up and count down signals do not occur simultaneously.

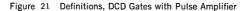

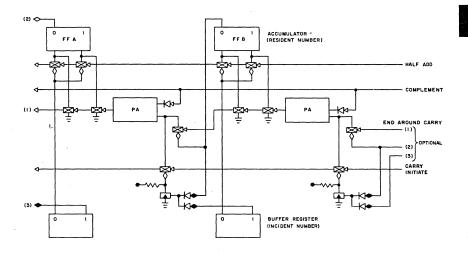

### Addition

A common method of performing BCD addition is to add two numbers in the binary adder and, if necessary, add or subtract an appropriate correction factor (see Figure A19). When addition is to be performed in a decade by decade fashion (serial addition with parallel decades), either code is useful. If addition is performed in parallel, however, the Excess 3 code is superior to the 8 4 2 1 code.

In 8 4 2 1 code the sum will be correct if it does not exceed 9. If the decimal sum is between 10 and 15, it is necessary to add +6 to the binary sum and generate a carry to the next decade. If the decimal sun exceeds 15, a carry signal is generated by the initial addition, but the correction factor +6 must still be added to the binary sum.

Addition of 8 4 2 1 coded numbers has the disadvantage that a carry signal can be generated during the correction process. For this reason each decade in the adder has to be corrected individually. Therefore it is not a desirable code in a parallel adder (see Figure 23).

No correction necessary (Sum  $\leq$  9)

0100 = 4 dec. 0011 = 3 dec.0111 = 7 dec.

Initial sum in forbidden state (10  $\leq$  sum  $\leq$  15)

$1000 = 8 \, \text{dec.}$

$0100 = 4 \, \text{dec.}$

1100 = forbidden state

0110 = correction factor of +6

$1 \leftarrow \overline{0010} = 2$  dec. plus carry

Initial sum in incorrect notation (16 < sum < 18)

$1001 = 9 \, \text{dec.}$

1000 = 8 dec.

1 - 0001 = 1 plus carry  $\frac{0110}{0111} = \text{correction factor of } + 6$  0111 = 7 dec. (plus carry from firstaddition)

#### Multiple decade addition

#### Figure 23 Addition with the 8 4 2 1 code

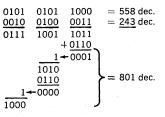

When two Excess 3 numbers are added, the sum will contain an excess 6; if the decimal sum is 9 or less, it is necessary to subtract 3 in order to return to Excess 3 notation; if the decimal sum is greater than 9, the excess 6 contained in the sum cancels the effect of the six unused binary states, but it is necessary to add 3 to return to the Excess 3 notation.

Whether the correction factor is +3 or -3 is determined by whether or not a carry signal appears during the initial addition. An initial carry requires a positive correction; no carry, a negative correction. The correction process will never yield an additional carry, thus simultaneous correction of all decades is possible.

The steps for performing Excess 3 addition are:

- 1. Add the two BCD numbers in binary fashion

- 2. Check each decade for a carry signal

- Subtract 3 from each decade in which a carry has not occurred, while simultaneously adding 3 to each decade in which the carry signal has occurred.

The +3 correction is made by adding 0011 to the appropriate decade. Subtracting 3 from a decade is done by adding 1100 and using the end around carry from the most significant bit of the decade. This is a method of 9's complement subtraction, described under subtraction below.

| Sum <u>&lt;</u> 9                                                                                                | $Sum \ge 10$                                                                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0111 = 4  dec.<br>0110 = 3  dec.<br>1101 = uncorrected sum<br>-0011 = correction factor of  -3<br>1010 = 7  dec. | $1011 = 8 \text{ dec.}$ $0111 = 4 \text{ dec.}$ $1 \longleftarrow 0010 = \text{uncorrected sum}$ $0011 = \text{correction factor of } +3$ $0101 = 2 \text{ dec., plus carry from}$ initial addition |

|                                                                                                                  | initial addition                                                                                                                                                                                    |

#### Multiple Decade Addition

| 1000  | 1000   | 1011   | = | 558 dec. |

|-------|--------|--------|---|----------|

| 0101  | 0111   | 0110   | = | 243 dec. |

|       |        |        |   |          |

| 1110  | → 0000 | ← 0001 |   |          |

| -0011 | +0011  | +0011  |   |          |

| 1011  | 0011   | 0100   | = | 801 dec. |

Figure 24 Addition with the Excess 3 code

#### Subtraction

Since subtraction is the inverse of addition, the same circuits may be used for both operations. Subtractions by this process is known as the system of adding complements. The 9's complement of any number is that number which is obtained by subtracting each individual digit from 9. With a self-complementing BCD code, such as Excess 3, the 9's complement of any number can be easily obtained by changing all zeros to ones and all ones to zeros. Figure 25 illustrates Excess 3 code with 9's complement notation.

| DECIMAL |

|---------|

|---------|

|          | sign | tens decade | ones decade |

|----------|------|-------------|-------------|

| +99      | 0    | 1100        | 1100        |

| +98      | 0    | 1100        | 1011        |

| +10      | 0    | 0100        | 0011        |

| +3       | 0    | 0011        | 0110        |

| +2       | 0    | 0011        | 0101        |

| +1       | · 0  | 0011 -      | 0100        |

| +0       | 0    | 0011        | 0011        |

| 0        | 1    | 1100        | 1100        |

| -1       | 1    | 1100        | 1011        |

| -2<br>-3 | 1    | 1100        | 1010        |

| -3       | 1    | 1100        | 1001        |

| -10      | 1    | 1011        | 1100        |

| 98       | 1    | 0011        | 0100        |

| -99      | 1    | 0011        | 0011        |

Figure 25 Nines complement, Excess 3 code

To subtract with Excess 3, 9's complement code, the subtrahend is first complemented then added to the minuend. During the first step of the addition process the individual bits (in the decimal decades and in the sign bits) are added just as in binary. Carries propagate from each digit to the digit of more significance and from the most significant digit to the sign bit produces a carry, it is added to the least significant decade, a process known as end around carry.

| 0 | 1000<br>1001              | 0100<br><u>1000</u> | 51 dec.<br>(complement of 34 dec.) | +51 dec.<br>- <u>34</u> dec. |

|---|---------------------------|---------------------|------------------------------------|------------------------------|

|   | 0001                      | 1100<br>1           | end around carry                   |                              |

| 0 | 0001<br>0011              | 1101<br>1100        | correction factor                  |                              |

| _ | 0100                      |                     | end around carry                   |                              |

| 0 | 0100                      | 1010                | 17 dec.                            | +17 dec.                     |

| 0 | 0110                      | 0111                | 34 dec.                            | +34 dec.                     |

| 1 | 0111                      | 1011                | (complement of 51 dec.)            | <u>-51</u> dec.              |

| 1 | 1110 <del>-</del><br>1100 | 0010<br>            | correction factor                  |                              |

|   |                           | 0101                | end around carry                   | <b>`</b>                     |

| 1 | 1011                      | 0101                | —17 dec.                           | -17 dec.                     |

Figure 26 Subtraction with the Excess 3 code, 9's complement notation

After this initial portion of the subtraction, a correction factor must be applied just as in addition. That is, a binary 3 (0011) must be added to each decade in which a carry signal has occurred, and binary 3 must be subtracted from each decade in which a carry signal did not occur.

Subtraction of the correction factor may be performed in the same way as well as the overall subtraction. However, the subtraction in this case operates only on the individual digits. Thus, if a carry occurs from the most significant bit of the digit, it is not carried out to the next digit; rather, it is added into the least significant bit of the same digit.

A second method of performing subtraction is through the use of the 10's complement notation. The 10's complement of any number may be obtained by adding 1 to the 9's complement. Operations are similar to those used in the 9's complement notation except that the end around carry is not required. Hence this is useful in systems where a feed back loop would be particularly time consuming.

| DECIMAL                                        | BIQUINARY RING COUNTER CODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                | 5, 0, 4, 3, 2, 1, 0 9, 8, 7, 6, 5, 4, 3, 2, 1, 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9 | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| DECIMAL                                        | SWITCH TAIL RING COUNTER CODE DECODING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9 | 0       0       0       0       A       E         0       0       0       1       D       E         0       0       1       1       C       D         0       0       1       1       B       C         0       0       1       1       1       A       B         1       1       1       1       A       E         1       1       1       1       O       D       C         1       1       1       0       O       C       D         1       1       1       0       0       C       D         1       1       0       0       A       B |

# CODES GREATER THAN FOUR BITS

Figure 27 Codes greater than four bits

21

Codes greater than four bits are often used for error detection and simplicity in decoding (Figure 27). The biquinary code is commonly used when error detection is required. It is a 7-bit weighted code in which two ones and five zeros appear in the representation of any number; thus it is always possible to detect single errors, and it is often possible to detect multiple errors.

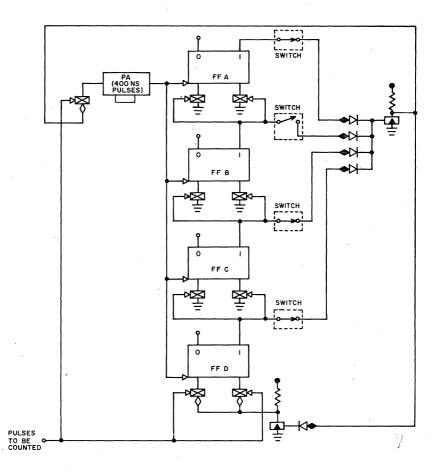

The ten-bit weighted code shown in Figure <sup>27</sup> allows any number to be represented with a single 1 and nine zeros. This code is often used in counting operations; the counter is a ten-stage shift register with the final stage connected to the initial stage. This counter, often given the name of ring counter, requires no carrying propagate time and the numbers may be decoded into ten lines without additional gates.

The switch-tail ring counter is a five-stage ring counter with reversed feed-back from the initial stage to the final stage. It requires fewer flip-flops than the ring counter and has the same advantage that no carry propagate time is required. Any state may be decoded by a two-input gate conditioned by two neighboring flip-flops.

# PART II: FLIP CHIP MODULES

,

# R SERIES

À

;

# R-SERIES BASIC CIRCUITS

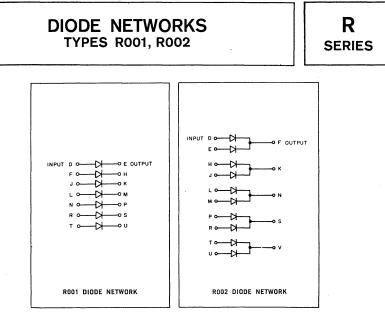

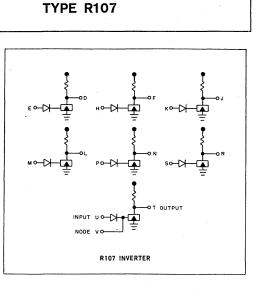

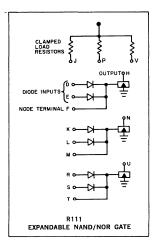

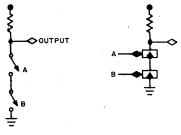

# DIODE GATE

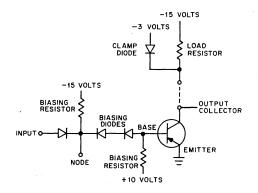

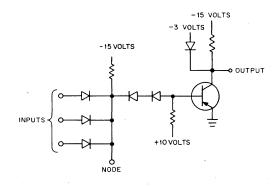

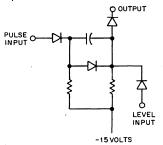

The basic element of digital logic described in this chapter is the diode gate. The diode gate is used in the R (2-megahertz) series to combine, amplify, invert, and standardize the signals which represent various logic functions. Figure 1 is a schematic of a simple diode gate with one input.

Figure 1 Single Input Diode Gate

When the input is negative, the node point is also negative and current flows from the transistor emitter through the biasing diodes and the biasing resistor to minus 15 volts (-15v). As a result, the PNP transistor is turned on, forming a short circuit between the collector and the emitter. Thus, when the input voltage is negative, the output voltage is ground. Since the output is from a saturated transistor, it has a low output impedance and good driving power.

When the diode gate input voltage is ground, the biasing diodes and the resistor, which is connected to the 10v supply, hold the transistor base more positive than the emitter, and the transistor is turned off. The output is then an open circuit, and it will follow the voltage of any other circuit connected to it.

If the load resistor and clamp diode are attached to the transistor collector, they serve as a voltage source and hold the output at -3v while the transistor is off. When the transistor is on, the diode is cut off and the load resistor follows the output to ground.

The single-input diode gate therefore has three functions. First, it inverts the input signal. Second, it standardizes the output voltage to -3v or ground (if the clamped load diode and resistor are connected). Third, since the output current available from the transistor is much greater than the required input current, the diode gate amplifies.

A fourth function, gating, is obtained by adding more diode inputs to the node point, as shown in Figure 2.

Figure 2 Multiple Input Diode Gate

The node terminal in this diagram will be at approximately the same voltage as the most positive input. Thus, when any input terminal is grounded, the node terminal is also at ground and the circuit output is at -3v. If all of the inputs are negative, the node terminal will be negative and the circuit output will be at ground.

Gating functions may also be performed by wiring together two or more diode gate outputs and one load resistor, as shown in Figure 3. When any input is negative, it saturates the corresponding transistor and forces the output line to ground. If all inputs are at ground, all of the transistors are open circuits and the output voltage, determined by the clamped load resistor, is -3v.

Figure 3 Diode Gates in Parallel

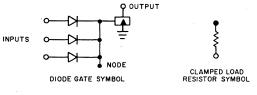

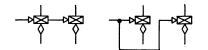

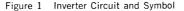

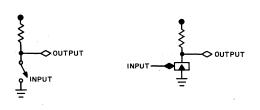

The basic diode gate can be used to construct very complex logical functions. A drawing that showed all of the circuit components, however, would be tedious to draw and difficult to read. For this reason, the diagrams that follow use a shorthand notation which represents one or more components as a single functional unit. Referring to Figure 4, diodes are shown in the conventional way. The transistor circuit, including the biasing resistors and diodes, is shown as a simple rectangle with an arrowhead indicating the direction of the transistor emitter. This part of the circuit is called an inverter because of the function it performs. The load resistor is shown as a resistor with a large dot at the top indicating that it is diode clamped to -3v. With these symbols, one can easily and quickly draw complex logical functions.

Assertion input and output voltage levels are shown by diamonds. A solid diamond indicates a -3v level, and an open diamond indicates a ground level. In the 2-input diode gate of Figure 5, for example, if input A and input B are both negative, the output will be at ground. If either A or B is at ground, the output will be negative.

Figure 5 Diamonds Indicating the Voltage Levels

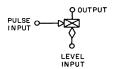

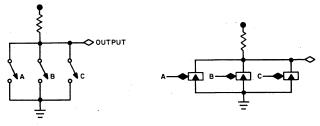

### DIODE-CAPACITOR-DIODE GATES

The diode-capacitor-diode (DCD) gate is used to standardize the input to various units such as flip-flops, delays, and pulse amplifiers. It provides logical isolation between pulse and level inputs and produces a logical delay which is essential for sampling flip-flops at the same time they are being changed. It also acts as a logical AND gate since both pulse and level inputs must meet certain requirements for a signal to appear at the output. Either positive pulses or positive-going level changes (both —3v to ground) may be used as the pulse input.

Figure 6 Diode-Capacitor-Diode Gate Circuit

A schematic drawing of a DCD gate is shown in Figure 6. If the level input is held at ground and the pulse input is held at -3v, the capacitor will become charged after the setup time has passed. If the pulse input then suddenly goes to ground, a positive-going pulse will appear at the output. There is delay at the level input, but the pulse input goes to the output without delay. Even if the level input changes simultaneously with a positive transition at the pulse input, the delay acts as a temporary memory: the pulse input is gated according to the level input that existed during the interval before the pulse.

Figure 7 Diode-Capacitor-Diode Gate Symbol

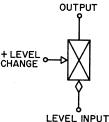

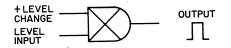

The symbol for the DCD gate (Figure 7) is distinguished from the diode gate by an X in the rectangle. The output is at the top, the delayed (level) input is at the bottom, and the differentiating (level change or pulse) input is on the side. The input signal to be differentiated, whether a level change or a pulse, is indicated by an arrowhead, rather than a diamond. The pulse symbols are hollow when positive-going and solid when negative-going. In the DCD gate, the pulse input must be positive-going.

Since many DCD gates may be driven by the same pulse, the side of the rectangle opposite the pulse may be used to show a continuation of the same line, as in Figure 8. The illustration on the left below is a simplified version of the identical logical configuration on the right.

Figure 8 Pulse Lines to Multiple Gates

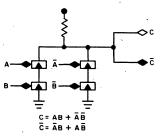

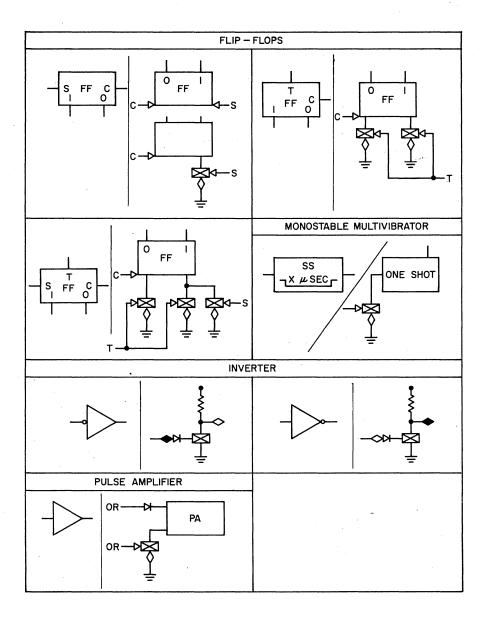

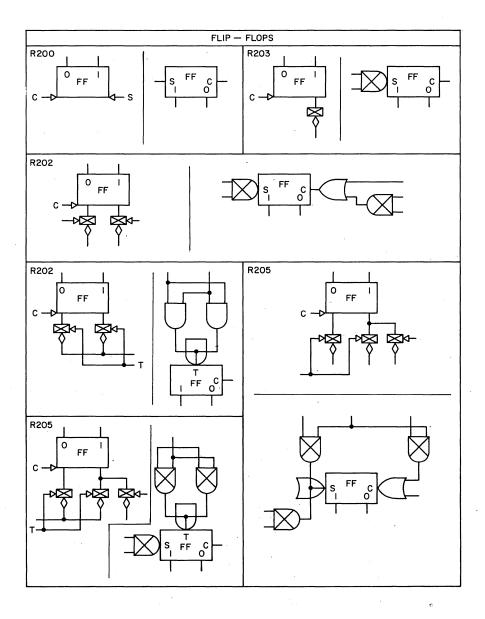

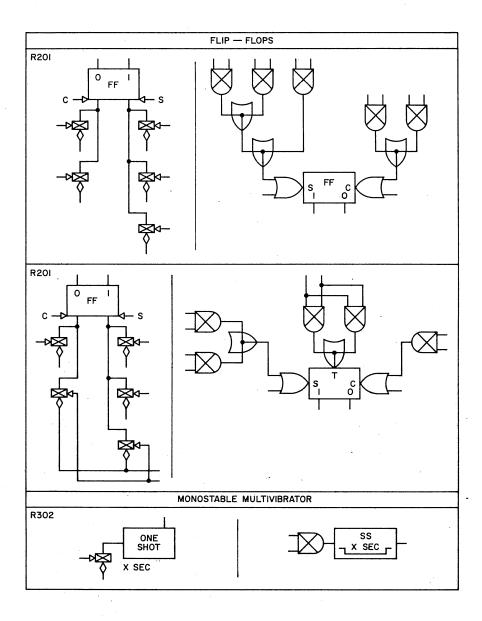

### FLIP-FLOPS

The flip-flop provides a convenient means of storing logical conditions within a digital system. It has two stable states representing 0 and 1, and remains in one of these states until an appropriate command to change state is received. Three commands may be given: set, which puts the flip-flop in the 1 state; clear, which puts the flip-flop in the 0 state; and complement, which changes the state of the flip-flop regardless of its previous state.

| Command    | State Before Command | State After Command |       |

|------------|----------------------|---------------------|-------|

| Set        | 1<br>0               | 1                   | . S D |

| Clear      | 10                   | 0                   | ~     |

| Complement | 10                   | 0<br>1              |       |

TABLE 1 FLIP-FLOP COMMANDS

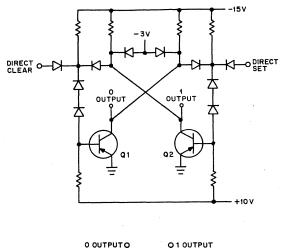

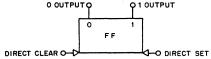

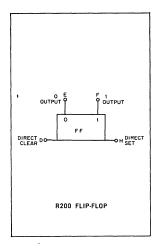

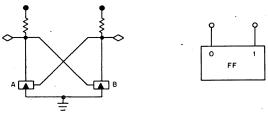

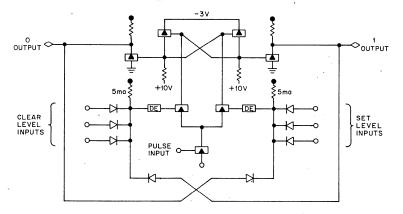

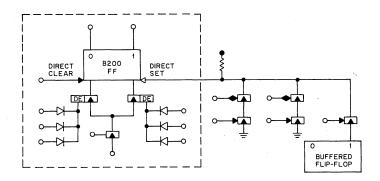

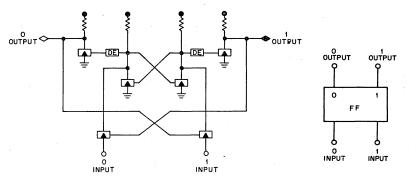

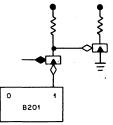

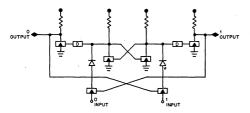

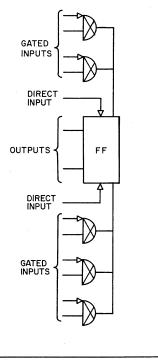

Figure 9 shows a schematic diagram and the symbolic equivalent of an R series flip-flop. The flip-flop consists of two diode gates, connected "back-to-back." When transistor Q1 is off, its output is negative. This holds transistor Q2 on, which in turn maintains the off condition of transistor Q1. Direct set and direct clear inputs are provided for operation of the flip-flops directly from external logical elements. When the flip-flop is set to the 1 state, the 1 output is at -3v.

Figure 9 Flip-Flop Schematic and Symbol

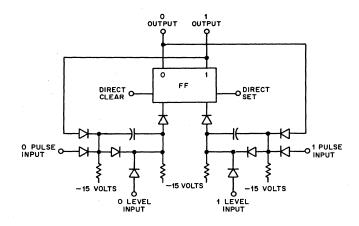

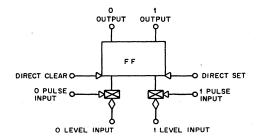

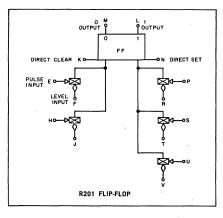

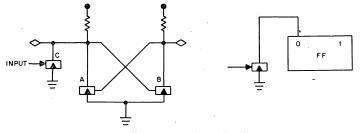

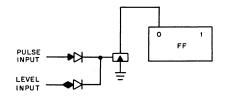

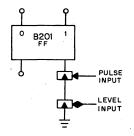

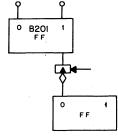

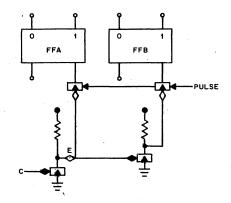

Inputs to this flip-flop are often made through DCD gates as shown in Figure 10. The gates provide sufficient delay so that information may be read out of one flip-flop and into another at the same time that the first flip-flop receives a command to change state. The DCD gate can also be used to perform additional logical operations, since it is basically an AND gate. That is, both the pulse and level inputs of the DCD gate must meet the proper input requirements for an output signal to occur.

Figure 10 Flip-Flop with DCD Gates, Schematic and Symbol

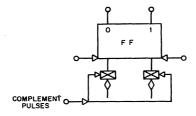

As can be seen from the schematic in Figure 10, the DCD gate level inputs are conditioned by the flip-flop outputs. Thus, a set signal will reach the flip-flop only if the flip-flop was previously in the 0 state. Similarly, a clear command reaches a flip-flop only if it was previously in the 1 state. For simplicity, this conditioning is not shown on the symbol but should be remembered because it is a very powerful element of the flip-flop. A complement terminal can be made simply by tying the set and clear pulse inputs together as shown in Figure 11. The gate inputs are still available for external enables. This technique allows a flip-flop with its DCD gates to be used in such varied applications as up counter, down counter, up-down counter, shifting, multiple source buffering, jam transfer register, ring counter, BCD counting, and special counts of  $2^{R}$  ( $2^{P}$  + 1) all without need for additional gate modules.

Figure 11 Complementing

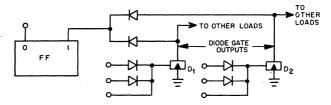

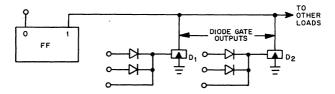

Flip-flops may be collector-triggered by tying a flip-flop output to the output of one or more diode gates. As illustrated in Figure 12, when the output of either diode gate  $D_1$  or  $D_2$  is asserted (at ground), the corresponding flip-flop is cleared (put to 0). If the gates are attached to the flip-flop through diode networks (Figure 12a), the diode gate outputs ( $D_1$  and  $D_2$ ) can be logically independent. If they are attached in parallel without diode networks (Figure 12b), the ouputs will be dependent. That is, if any output is at ground, the output of all gates connected in parallel with it will be at ground.

(A) WITH DIODE NETWORK -- DIODE GATE OUTPUTS INDEPENDENT

(B) WITHOUT DIODE NETWORK -- DIODE GATE OUTPUTS DEPENDENT

Figure 12 Collector Triggering of a Flip-Flop

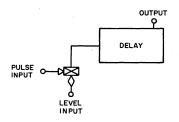

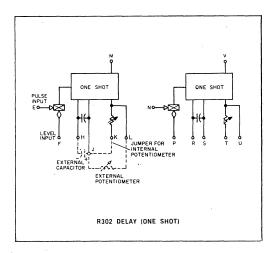

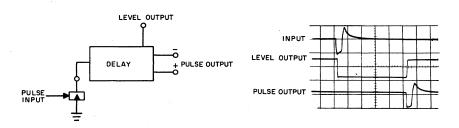

### DELAYS

The delay one-shot, or monostable multivibrator, is a basic timing element. The input to the delay, like that of the flip-flop, is through a DCD gate (see Figure 13). When the gate is properly enabled, and when its pulse input terminal is brought to ground by a positive pulse or a positive-going level change, the output of the delay changes from its normal ground level to a -3v level for a fixed, but adjustable, period of time. After the fixed time has elapsed, the output returns to ground. This delayed output is suitable for driving many R series modules. A pulse output can be obtained with the addition of a pulse amplifier to the delay output.

Figure 13 Delay One-Shot

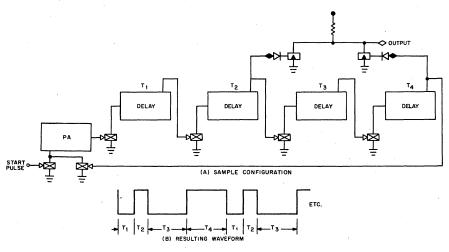

Delay units are particularly useful in generating delayed pulses or signals of arbitrary width. The network of delays in Figure 14a will produce the waveform shown in Figure 14b.

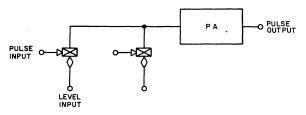

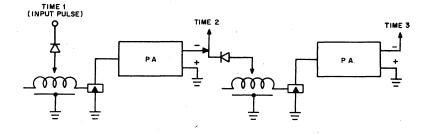

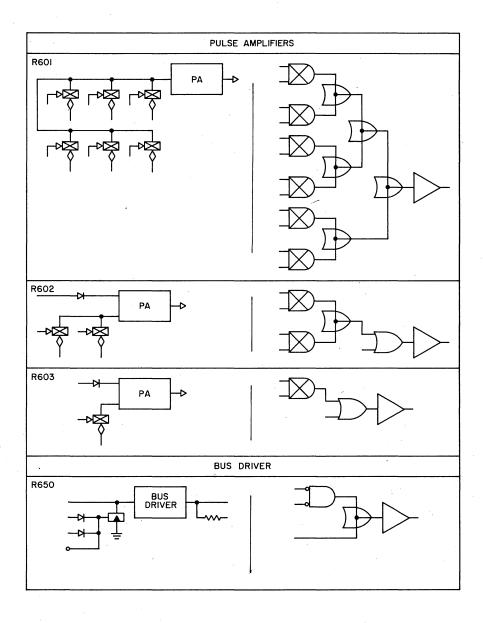

# PULSE AMPLIFIERS

Pulse amplifiers are extremely versatile elements since they not only amplify and standardize various signals into standard 100-nanosecond pulses (—3v to ground), but they may also be used to carry the results of gating to many units. For example, when the same gating is to be done on an entire register of flip-flops, it is most economically performed at the input to the pulse amplifier which drives the register.

Figure 15 Pulse Amplifier with Gates

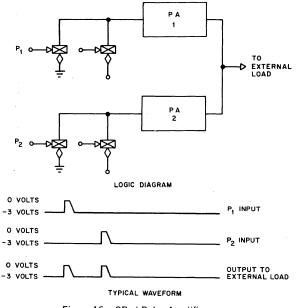

Several pulse amplifier outputs may be ORed together by simply connecting their outputs in parallel (Figure 16). Thus two levels of logic can be performed by pulse amplifiers.

Figure 16 ORed Pulse Amplifiers

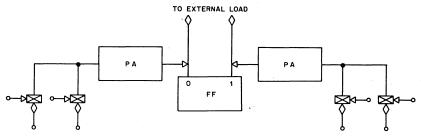

Flip-flops may be collector-triggered by connecting the output of one or more pulse amplifiers to the output terminals of the flip-flop (Figure 17). This connection may be made directly or through the diode networks, as with the diode gates shown in Figure 12.

Figure 17 Collector Triggering of Flip-Flops

### CLOCKS

Variable R series clocks produce standard, 100-nsec pulses (-3v to ground) from stable RC-coupled oscillators. These clocks are often used as a primary source of timing for large systems (Figure 18).

Figure 18 Clock

Where precise timing is required, a clock with a single frequency crystal oscillator may be used.

### LOADING RULES

When interconnecting basic circuits to perform logical operations, it is important to keep the load on each circuit within its driving ability. The R series loading rules are simple because all inputs draw current from the same direction and because all inputs are either diode gate circuits or DCD circuits.

Each diode gate input draws 1 ma (milliampere) and the output drives 20 ma. The load resistor draws 2 ma; so a diode gate with a clamped load resistor tied to it can drive 18 ma.

A flip-flop is two slightly modified diode gates cross-connected. The direct set and clear terminals draw 1 ma. The output will drive 21 ma less 3 ma for the load resistor permanently connected in the flip-flop and less 1 ma for conditioning the opposite side of the flip-flop for a remainder of 17 ma.

The single shot delay has a similar output circuit with a built-in load resistor. It will drive 20 - 2 or 18 ma.

The pulse amplifiers will drive loads of up to 70 ma.

The DCD gates on flip-flops, delays, and pulse amplifiers draw 2 ma at the level inputs and 3 ma at the pulse inputs. When two DCD gates are driving both sides of the same flip-flop, the load on both pulse inputs totals only 4 ma. When the level inputs are tied together as in a complement configuration, the total input load is only 3 ma, as shown in Figure 19.

Figure 19 Flip-Flop Input Loads

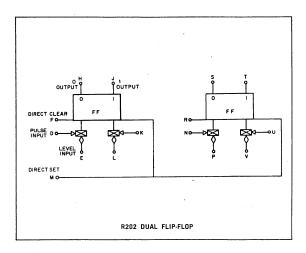

On flip-flops which have built-in DCD gates, the output driving ability is less because the internal diode capacitor gate draws current from the flip-flop. Table 2 lists the output driving capability for each of the six types of flip-flops.

Table 2 Flip-Flop Output Driving Capability

| Flip-Flop    | 0 Output | 1 Output |

|--------------|----------|----------|

| R200<br>R201 | 17       | 17<br>13 |

| R202         | 15       | 15       |

| R203<br>R204 | 15<br>17 | 17<br>17 |

| R205         | 13       | 15       |

# R-SERIES LOGIC CONFIGURATIONS

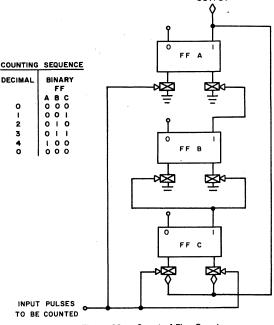

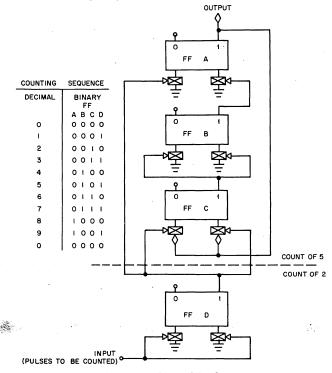

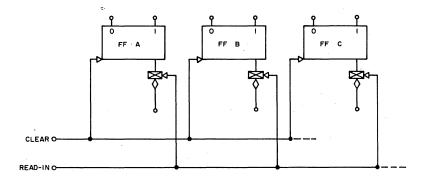

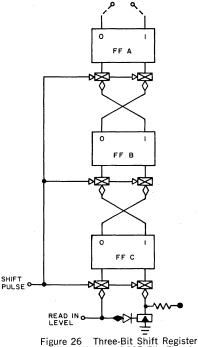

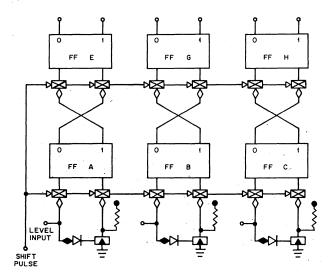

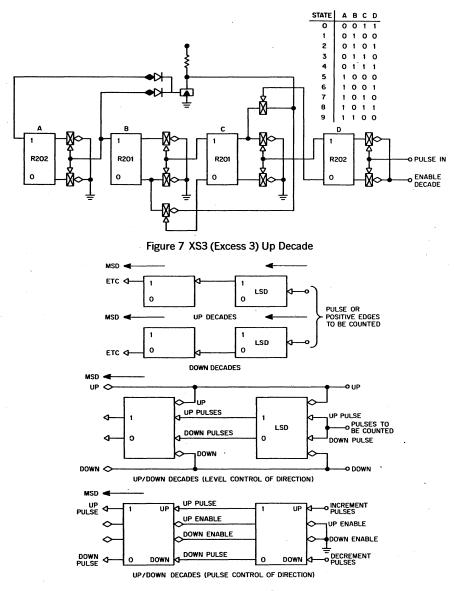

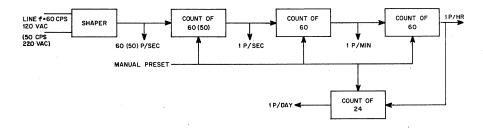

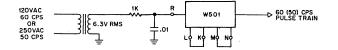

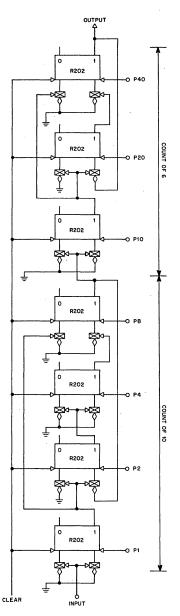

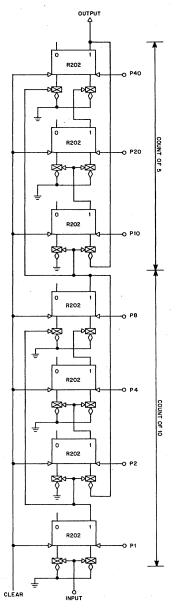

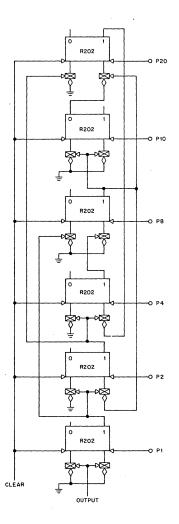

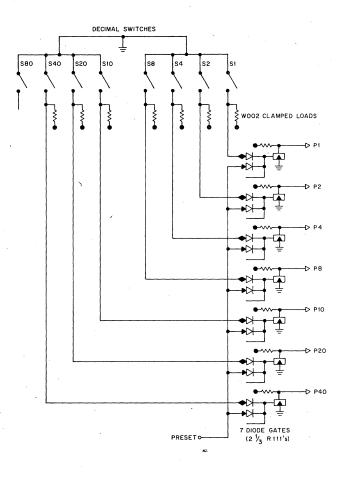

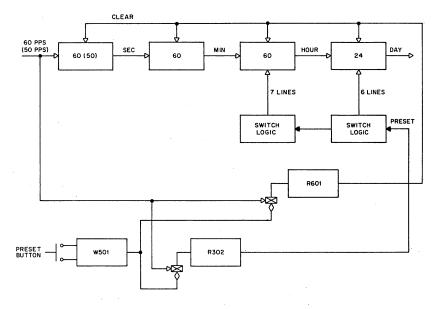

# COUNTERS