# NVAX CPU Chip Functional Specification

The NVAX CPU Chip is a high-performance, single-chip implementation of the VAX Architecture for use in low-end and mid-range systems.

**Revision/Update Information:**

This is Revision 1.2 of this specification, which supersedes Revision 1.1 released in August 1991. The information in this specification reflects pass 2 of the NVAX CPU chip. Only the Electrical Characteristics Chapter was updated from Revision 1.1 to Revision 1.2.

#### DIGITAL CONFIDENTIAL

This information shall not be disclosed to persons other than DIGITAL employees or generally distributed within DIGITAL. Distribution is restricted to persons authorized and designated by the originating organization. This document shall not be transmitted electronically, copied unless authorized by the originating organization, or left unattended. When not in use, this document shall be stored in a locked storage area. These restrictions are enforced until this document is reclassified by the originating organization.

ioc

Digital Equipment Corporation, Hudson, Massachusetts

THR.

#### December 1991

2.

. ..

$\mathbb{S}_{+}^{-1}$

1.1

15

The drawings and specifications in this document are the property of Digital Equipment Corporation and shall not be reproduced or copied or used in whole or in part as the basis for the manufacture or sale of items without written permission.

The information in this document may be changed without notice and is not a commitment by Digital Equipment Corporation. Digital Equipment Corporation is not responsible for any errors in this document.

This specification does not describe any program or product that is currently available from Digital Equipment Corporation, nor is Digital Equipment Corporation committed to implement this specification in any program or product. Digital Equipment Corporation makes no commitment that this document accurately describes any product it might ever make.

Copyright ©1989, 1990, 1991 by Digital Equipment Corporation All Rights Reserved Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation:

£,

· ...

55

DEC DECnet DECUS MicroVAX MicroVMS PDP ULTRIX ULTRIX-32 UNIBUS VAX VAXBI VAXCluster

VAXstation

VMS

VT

## Contents

|           |                                                | a na ang sa kanangana na kanang na kanangana na kanang na kanangana na kanangana na kanang na kanang na kanang<br>Kanang na kanang na ka |                                          |

|-----------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

|           |                                                | waa aanaa aanaa aa ah a                                                                                                                                                                              |                                          |

| CHAPTER 1 | INTRODUCTION                                   |                                                                                                                                                                                                                                    | 1–1                                      |

| 1.1       | SCOPE AND ORGANIZATION OF THIS SPECIFICATION   |                                                                                                                                                                                                                                    | 1—1                                      |

| 1.2       | RELATED DOCUMENTS                              |                                                                                                                                                                                                                                    | 1–1                                      |

| 1.3       | TERMINOLOGY AND CONVENTIONS                    | - 1 <sup>*</sup>                                                                                                                                                                                                                   | 1—1                                      |

|           | 1.3.1 Numbering                                | 10.5 <b>8</b> (1997)                                                                                                                                                                                                               | 1–1                                      |

|           | 1.3.2 UNPREDICTABLE and UNDEFINED              |                                                                                                                                                                                                                                    | 1—1                                      |

|           | 1.3.3 Ranges and Extents                       |                                                                                                                                                                                                                                    | 1–2                                      |

|           | 1.3.4 Must be Zero (MBZ)                       |                                                                                                                                                                                                                                    | 12                                       |

|           |                                                | and the second second second                                                                                                                                                                                                       | 1–2                                      |

|           | 1.3.6 Register Format Notation                 |                                                                                                                                                                                                                                    | 1–2                                      |

|           | 1.3.7 Timing Diagram Notation                  |                                                                                                                                                                                                                                    | 1-5                                      |

| 1.4       | REVISION HISTORY                               |                                                                                                                                                                                                                                    | 16                                       |

| CHAPTER 2 | ARCHITECTURAL SUMMARY                          |                                                                                                                                                                                                                                    | 2–1                                      |

| 2.1       | OVERVIEW                                       |                                                                                                                                                                                                                                    | 2–1                                      |

| 2.2       | VISIBLE STATE                                  |                                                                                                                                                                                                                                    | 2-1                                      |

|           | 2.2.1 Virtual Address Space                    |                                                                                                                                                                                                                                    | 2–1                                      |

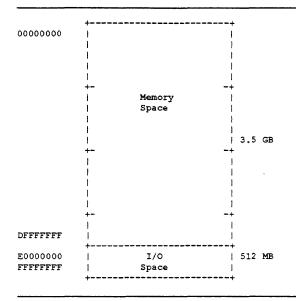

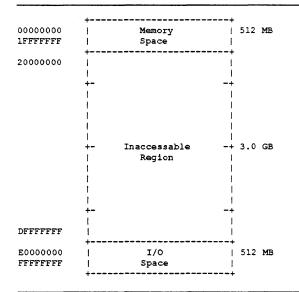

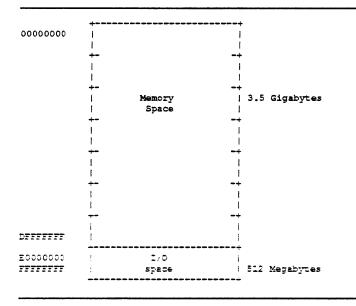

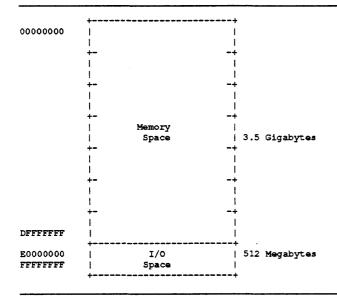

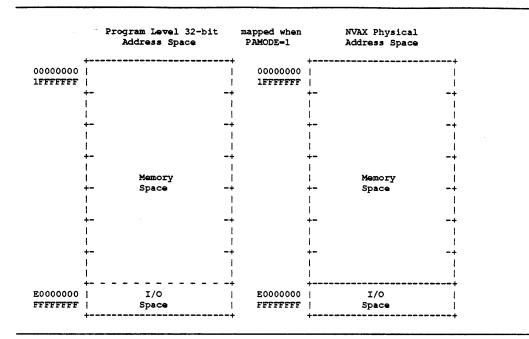

|           | 2.2.2 Physical Address Space                   |                                                                                                                                                                                                                                    | 2–2                                      |

|           | 2.2.2.1 Physical Address Control Registers • 2 | 24                                                                                                                                                                                                                                 |                                          |

|           | 2.2.3 Registers                                |                                                                                                                                                                                                                                    | 2-4                                      |

| 2.3       | DATA TYPES                                     |                                                                                                                                                                                                                                    | 26                                       |

| 2.4       | INSTRUCTION FORMATS AND ADDRESSING MODES       |                                                                                                                                                                                                                                    | 28                                       |

|           | 2.4.1 Opcode Formats                           |                                                                                                                                                                                                                                    | 28                                       |

|           | 2.4.2 Addressing Modes                         |                                                                                                                                                                                                                                    | 28                                       |

|           | 2.4.3 Branch Displacements                     |                                                                                                                                                                                                                                    | 2–11                                     |

| 2.5       | INSTRUCTION SET                                |                                                                                                                                                                                                                                    | 2–11                                     |

| 2.6       | MEMORY MANAGEMENT                              |                                                                                                                                                                                                                                    | 2–25                                     |

|           | 2.6.1 Memory Management Control Registers      |                                                                                                                                                                                                                                    | 225                                      |

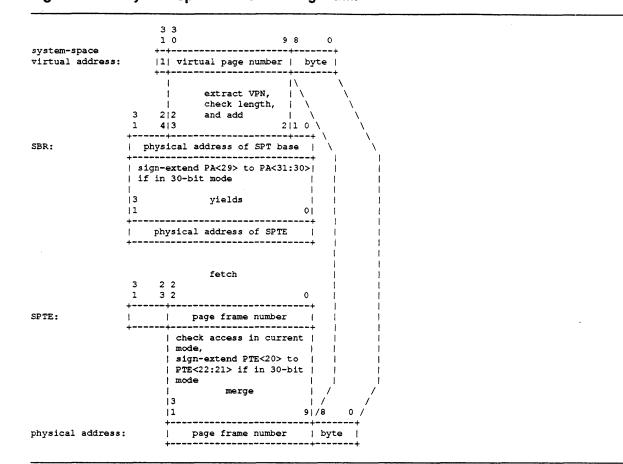

|           | 2.6.2 System Space Address Translation         |                                                                                                                                                                                                                                    | 2–26                                     |

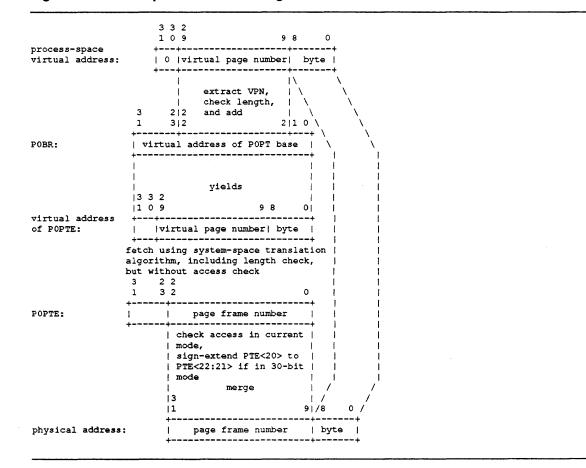

|           | 2.6.3 Process Space Address Translation        |                                                                                                                                                                                                                                    | 228                                      |

|           | 2.6.3.1 P0 Region Address Translation • 2–28   |                                                                                                                                                                                                                                    |                                          |

|           | 2.6.3.2 P1 Region Address Translation • 2-29   |                                                                                                                                                                                                                                    |                                          |

|           | 2.6.4 Page Table Entry                         |                                                                                                                                                                                                                                    | 2-31                                     |

|           | 2.6.5 Translation Buffer                       |                                                                                                                                                                                                                                    | 232                                      |

| 2.7       | EXCEPTIONS AND INTERRUPTS                      |                                                                                                                                                                                                                                    | 2–33                                     |

|           | 2.7.1 Interrupts                               |                                                                                                                                                                                                                                    | 233                                      |

|           | 2.7.1.1 Interrupt Control Registers • 2–34     |                                                                                                                                                                                                                                    | an a |

111

.

:

n Brezza Granden and

|      |       | 2.7.2    | Exceptio   | ns                                                                 | 2-35          |

|------|-------|----------|------------|--------------------------------------------------------------------|---------------|

|      |       |          | 2.7.2.1    | Arithmetic Exceptions • 2–36                                       |               |

|      |       |          | 2.7.2.2    | Memory Management Exceptions • 2–37                                |               |

|      |       |          | 2.7.2.3    | Emulated Instruction Exceptions • 2-38                             |               |

|      |       |          | 2.7.2.4    | Vector Unit Disabled Fault • 2-40                                  |               |

|      |       |          | 2.7.2.5    | Machine Check Exceptions • 2-40                                    |               |

|      |       |          | 2.7.2.6    | Console Halts • 2–40                                               |               |

|      | 2.8   | SYSTEM   | CONTROL    | BLOCK                                                              | 2-41          |

|      |       | 2.8.1    |            | Control Block Vectors                                              | 2-41          |

|      |       | 2.8.2    | •          | Control Block Layout                                               | 2-42          |

|      | 2.9   |          | NTIFICATIO | •                                                                  |               |

|      |       |          |            |                                                                    | 2-44          |

|      | 2.10  |          |            |                                                                    | 2-44          |

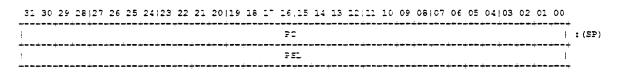

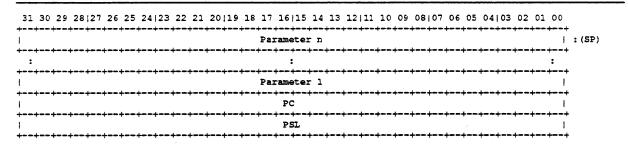

|      | 2.11  |          | SS STRUCT  |                                                                    | 2-46          |

|      | 2.12  | PROCES   | SOR REGIS  | STERS                                                              | <b>2–49</b> . |

|      | 2.13  | I/O SPAC | CE ADDRES  | SES                                                                | 2–61          |

|      | 2.14  | REVISIO  | N HISTORY  |                                                                    | 2-62          |

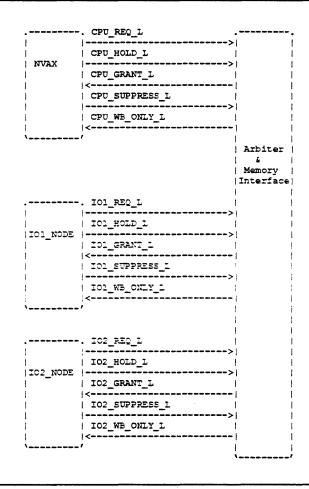

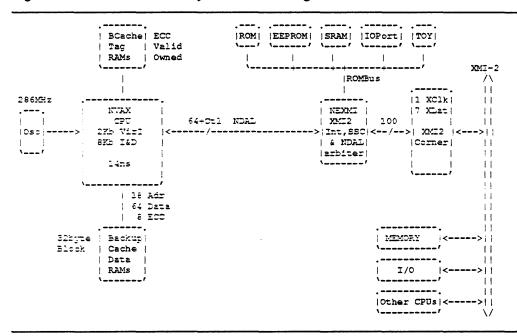

| СНАР | TER 3 | NVAX CI  | HIP INTERI | FACE                                                               | 3-1           |

|      | 3.1   | INTROD   | UCTION     |                                                                    | 3-1           |

|      | 3.2   | NVAX C   | PU PINOUT  |                                                                    | 3–1           |

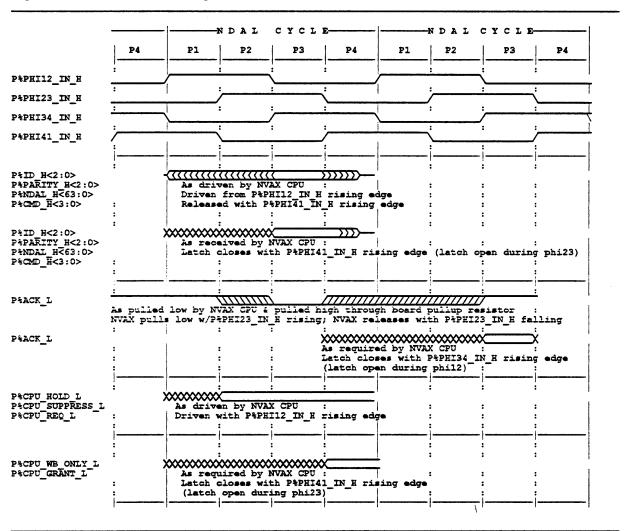

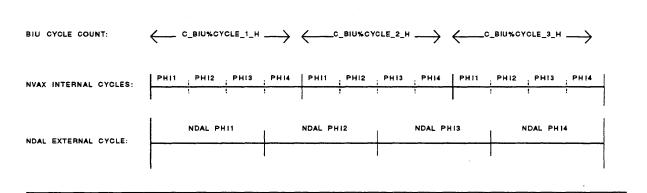

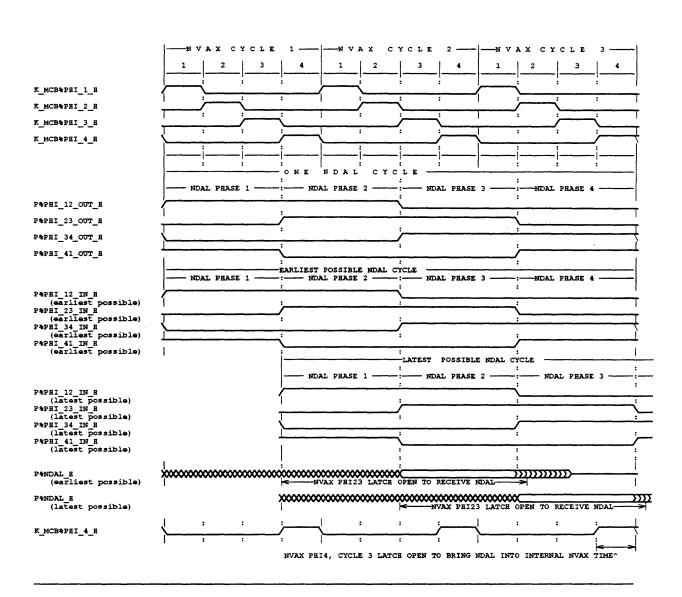

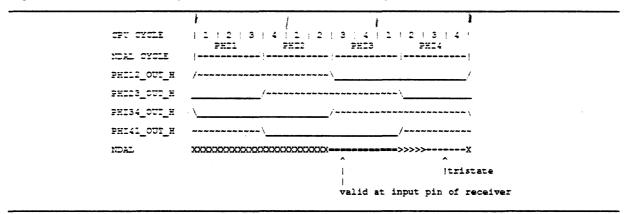

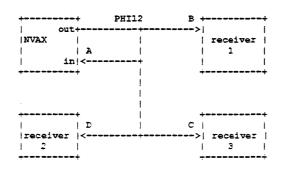

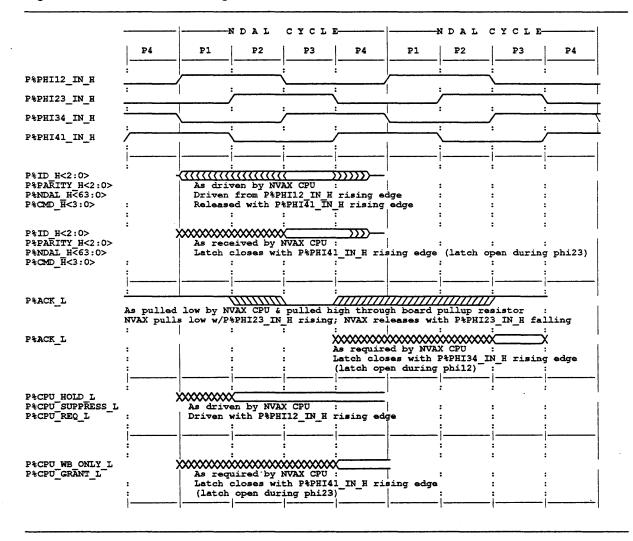

|      |       | 3.2.1    | NDAL SI    | gnals and Timing                                                   | 3-4           |

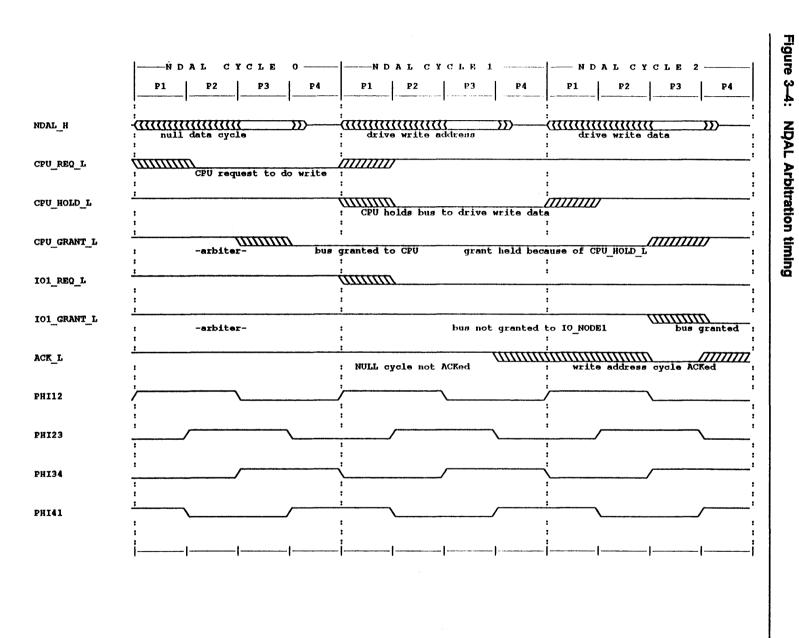

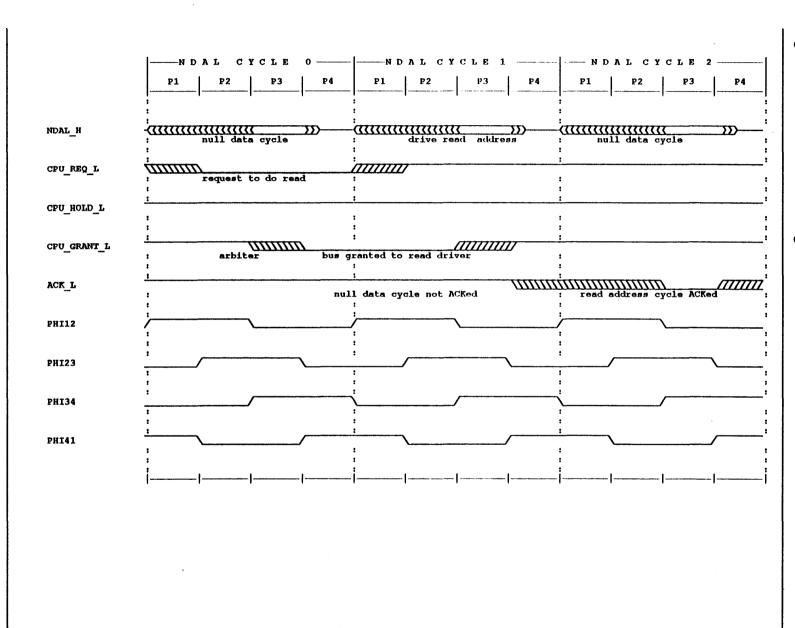

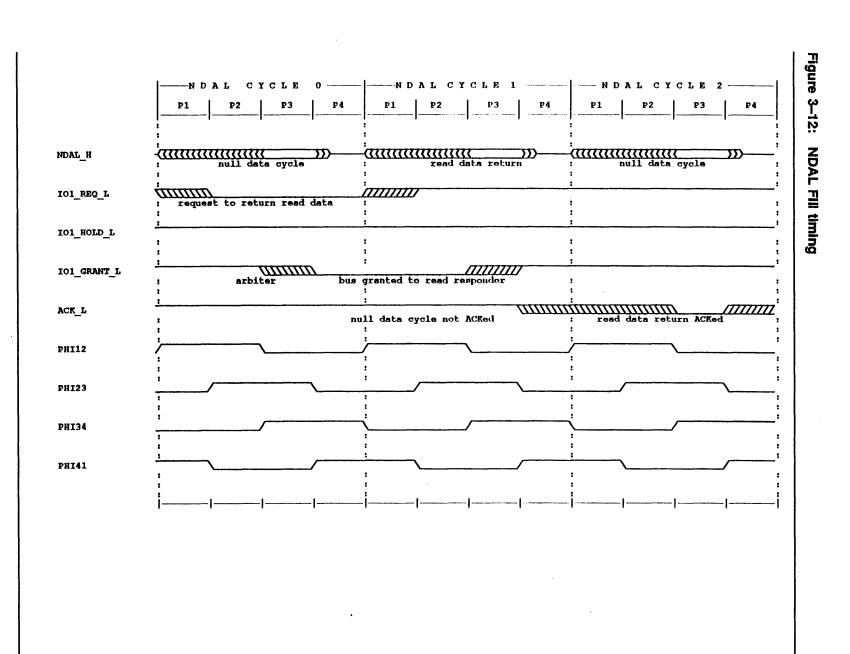

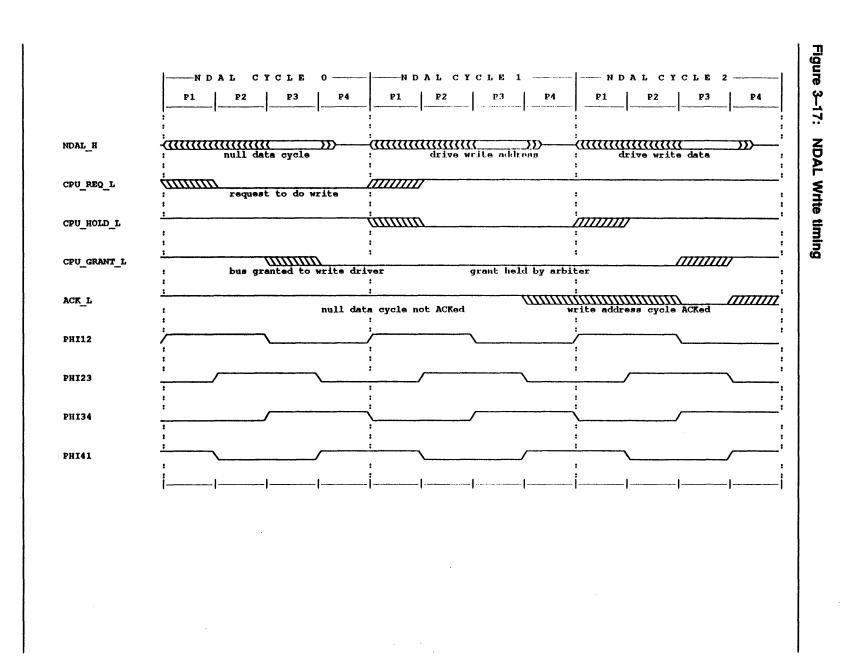

|      |       |          | 3.2.1.1    | P%CPU_REQ_L • 3-6                                                  |               |

| -*   |       |          | 3.2.1.2    | P%CPU_HOLD_L • 3-7                                                 |               |

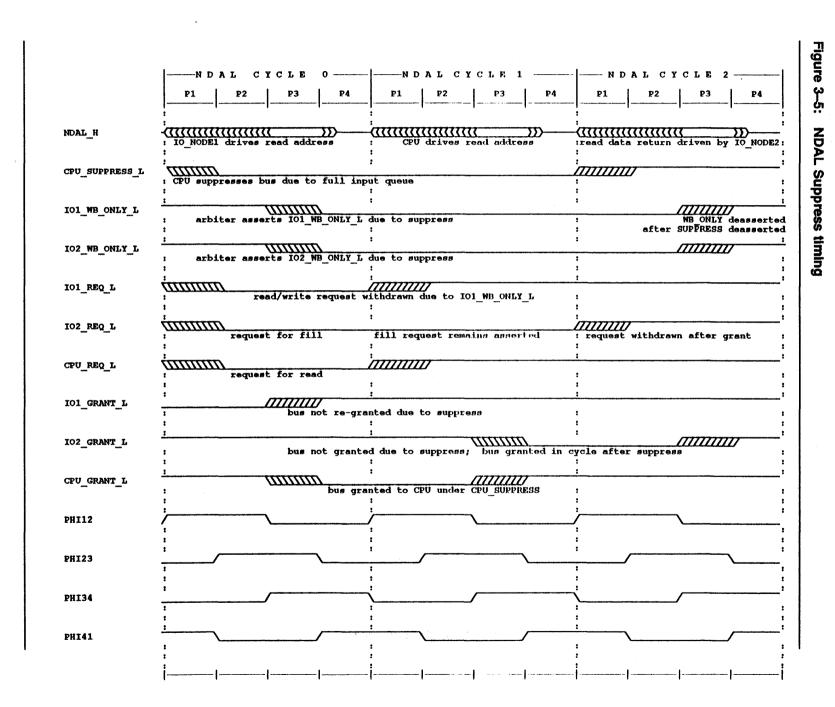

|      |       |          | 3.2.1.3    | P%CPU_SUPPRESS_L · 3-7                                             |               |

| č    |       |          | 3.2.1.4    | P%CPU_GRANT_L • 3–7                                                |               |

|      |       |          | 3.2.1.5    | P%CPU_WB_ONLY_L • 3-7                                              |               |

|      |       |          | 3.2.1.6    | <b>P%NDAL_H&lt;63:0&gt; •</b> 3–7                                  |               |

|      |       |          | 3.2.1.7    | P%CMD_H<3:0> • 3-7                                                 |               |

|      |       |          | 3.2.1.8    | <b>P%ID_H&lt;2:0&gt; ・</b> 3−7                                     |               |

|      |       |          | 3.2.1.9    | <b>P%PARITY_H&lt;2:0&gt; ·</b> 3-7                                 |               |

|      |       |          | 3.2.1.10   | <b>P%ACK_L •</b> 3–7                                               |               |

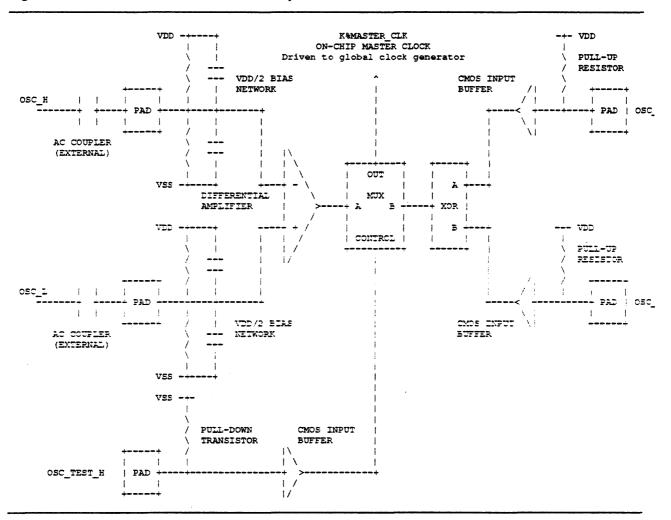

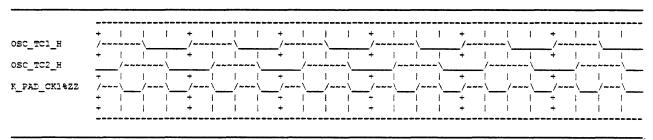

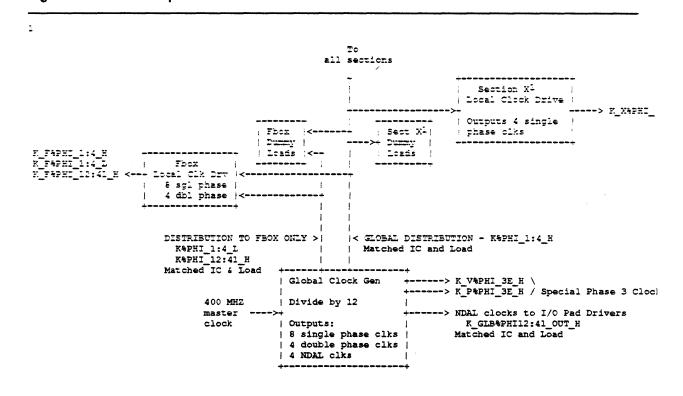

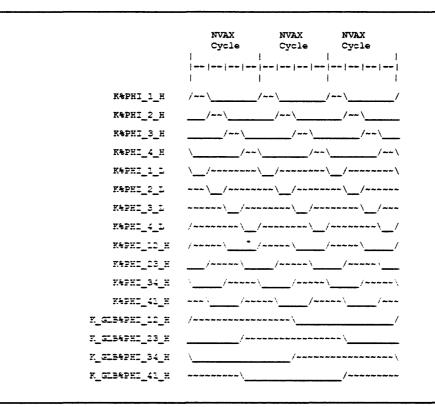

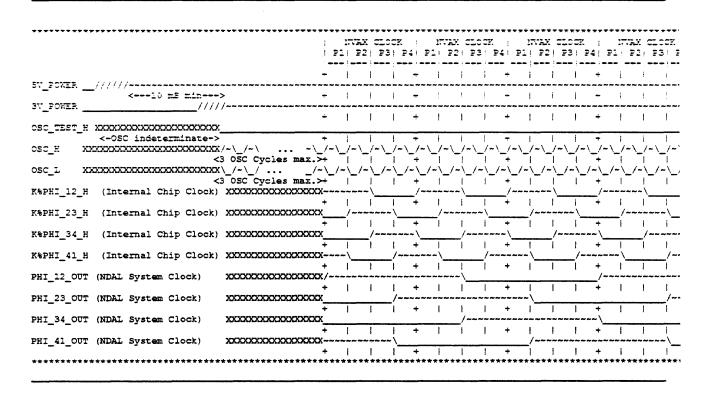

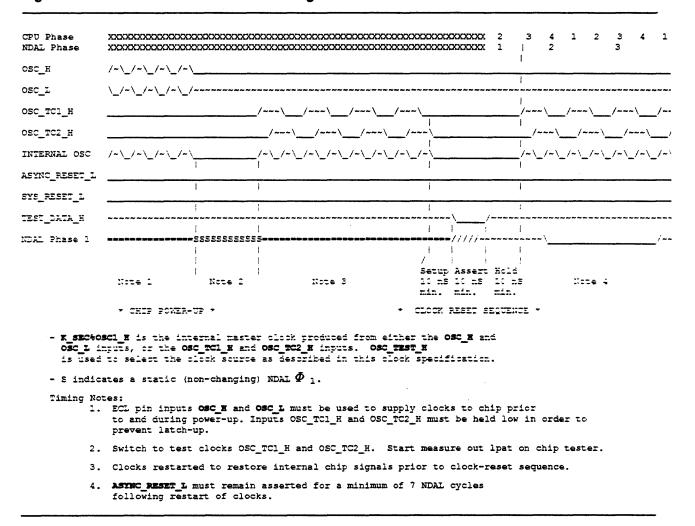

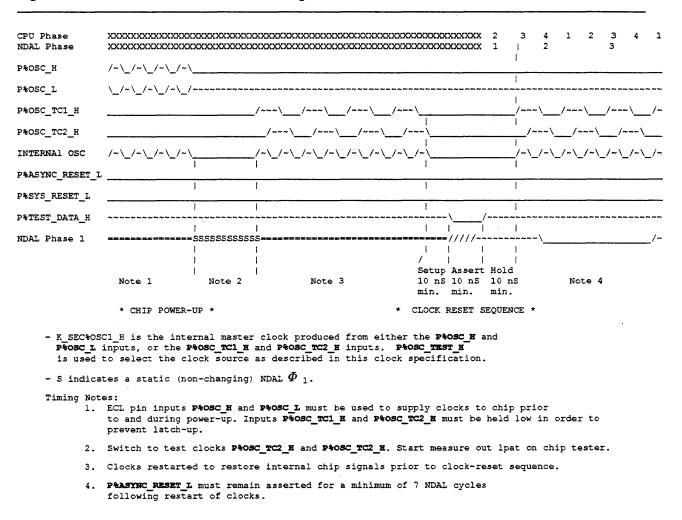

|      |       | 3.2.2    | Clocking   | •                                                                  | 38            |

|      |       |          | 3.2.2.1    | <b>P%OSC_H</b> , <b>P%OSC_L</b> • 3-8                              |               |

|      |       |          | 3.2.2.2    | <b>P%OSC_TC1_H</b> , <b>P%OSC_TC2_H</b> • 3–8                      |               |

|      |       |          | 3.2.2.3    | P%OSC_TEST_H • 3-8                                                 |               |

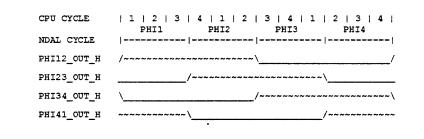

|      |       |          | 3.2.2.4    | P%PHI12_OUT_H, P%PHI23_OUT_H, P%PHI34_OUT_H,<br>P%PHI41_OUT_H • 38 |               |

|      |       |          | 3.2.2.5    | P%PHI12_IN_H, P%PHI23_IN_H, P%PHI34_IN_H,<br>P%PHI41_IN_H • 3-8    |               |

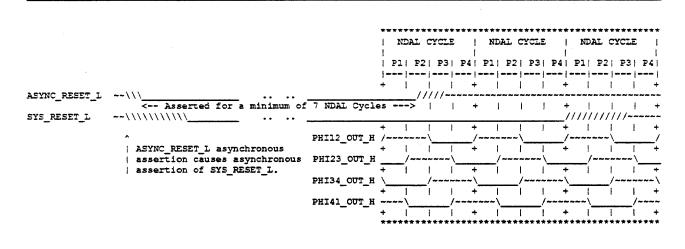

|      |       |          | 3.2.2.6    | P%ASYNC_RESET_L • 3-8                                              |               |

|      |       |          | 3.2.2.7    | P%SYS_RESET_L • 3-9                                                |               |

|      |       | 3.2.3    |            | and Error Signals                                                  | 3-9           |

|      |       |          | 3.2.3.1    | P%MACHINE_CHECK_H · 3-9                                            |               |

|      |       |          | 3.2.3.2    | P%IRQ_L<3:0> • 3-9                                                 |               |

|      |       |          | 3.2.3.3    | <b>P%H_ERR_L •</b> 3–9                                             |               |

|      |       |          | 3.2.3.4    | P%S_ERR_L • 3-9                                                    |               |

|      |       |          | 3.2.3.5    | P%INT_TIM_L • 3-10                                                 |               |

|      |       |          | 3.2.3.6    | P%PWRFL_L • 3-10                                                   |               |

- 7.4

DIGITAL CONFIDENTIAL

ċ

#### Contents

|             |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | the state of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |                | 3.2.3.7 <b>P%HALT_L •</b> 3–10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

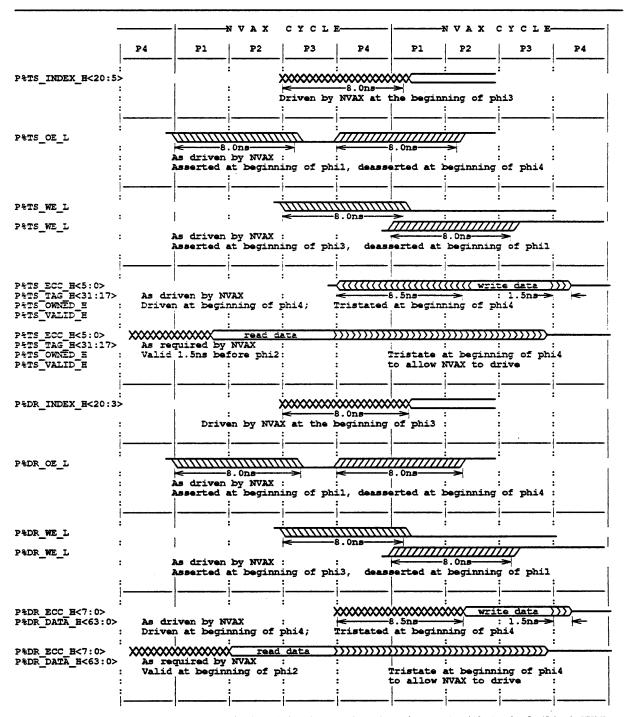

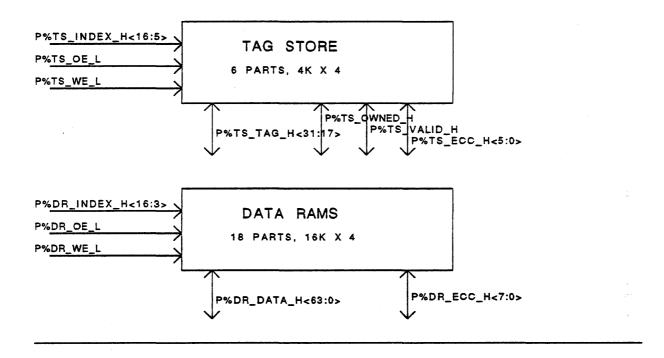

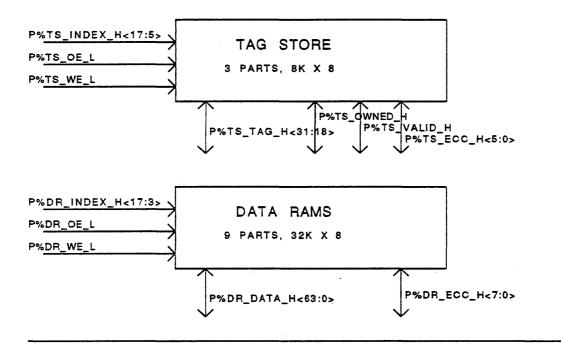

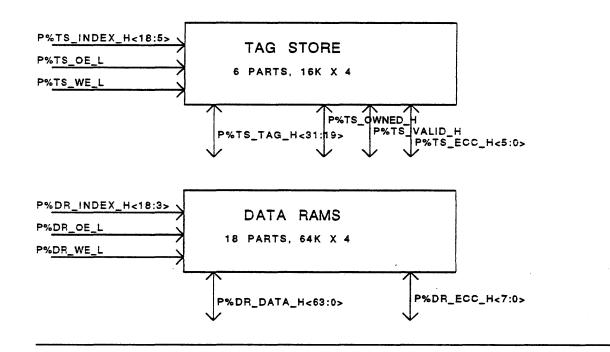

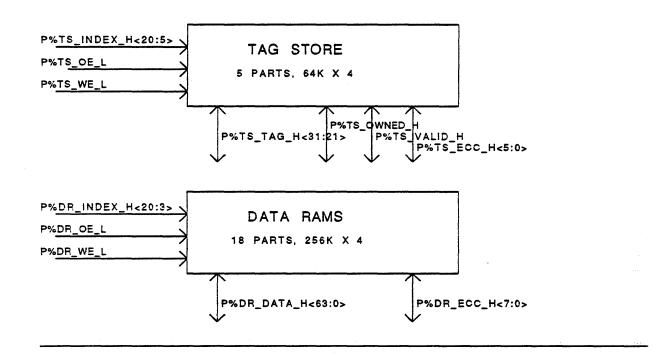

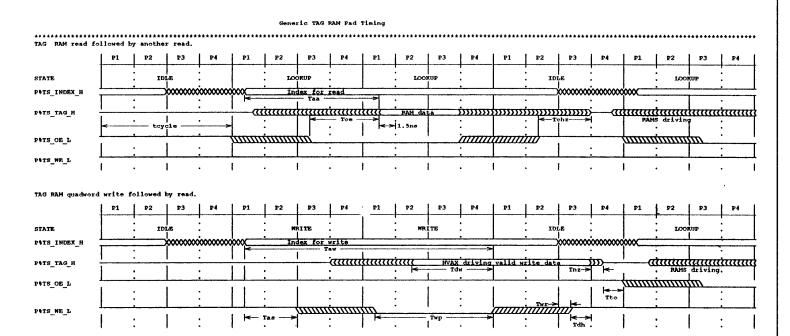

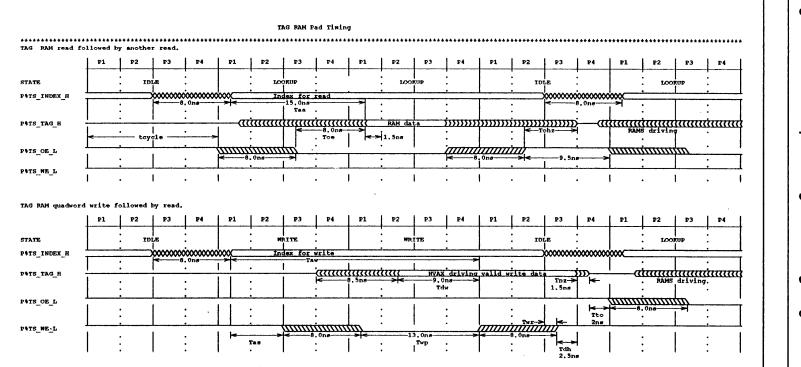

|             | 3.2.4          | Cache interface signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|             |                | 3.2.4.1 <b>P%TS_INDEX_H&lt;20:5&gt; •</b> 3–10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|             |                | 3.2.4.2 <b>P%TS_OE_L</b> •3–10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|             |                | 3.2.4.3 <b>P%TS_WE_L •</b> 3–10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | - · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

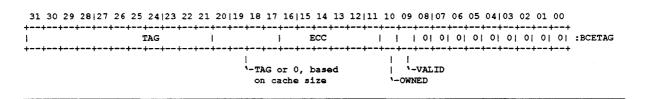

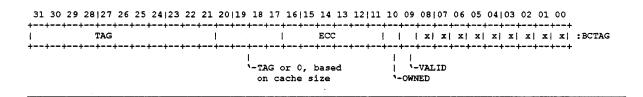

|             |                | 3.2.4.4 <b>P%TS_TAG_H&lt;31:17&gt; •</b> 3–12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|             |                | 3.2.4.5 <b>P%TS_ECC_H&lt;5:0&gt; •</b> 3–12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|             |                | 3.2.4.6 <b>P%TS_OWNED_H • 3</b> –12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|             |                | 3.2.4.7 <b>P%TS_VALID_H ·</b> 3–12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

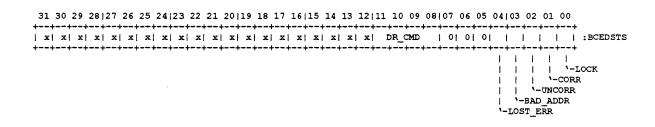

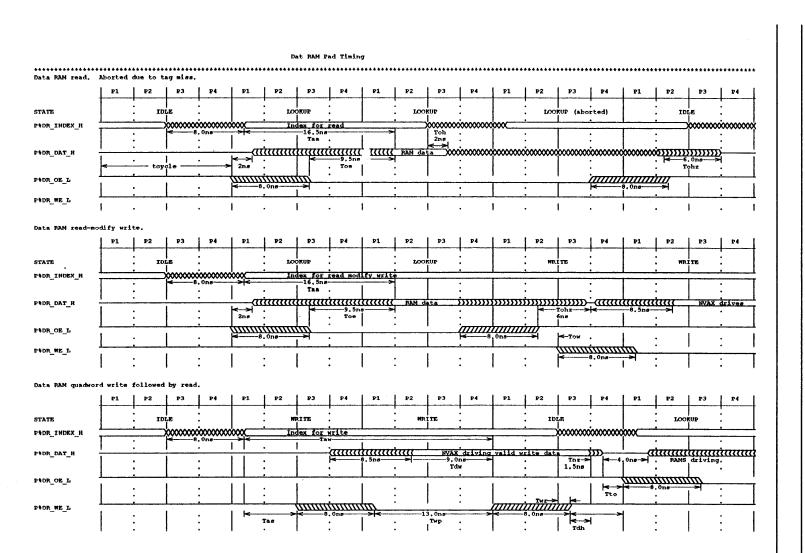

| ¥ — 5       |                | 3.2.4.8 <b>P%DR_INDEX_H&lt;20:3&gt; •</b> 3–12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|             |                | 3.2.4.9 <b>P%DR_OE_L •</b> 3–12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|             |                | 3.2.4.10 <b>P%DR_WE_L · 3</b> –12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | · (이 이 · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|             |                | 3.2.4.11 <b>P%DR_DATA_H&lt;63:0&gt; ·</b> 3–12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | and the second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|             |                | 3.2.4.12 <b>P%DR_ECC_H&lt;7:0&gt; ·</b> 3–12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

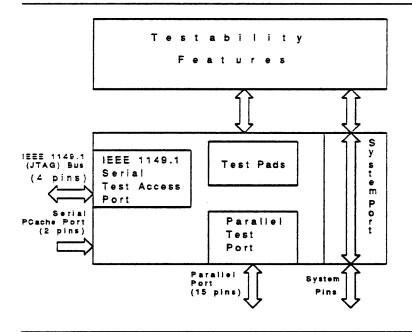

|             | 3.2.5          | Test Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3–13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|             |                | 3.2.5.1 <b>P%TEST_DATA_H •</b> 3–13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

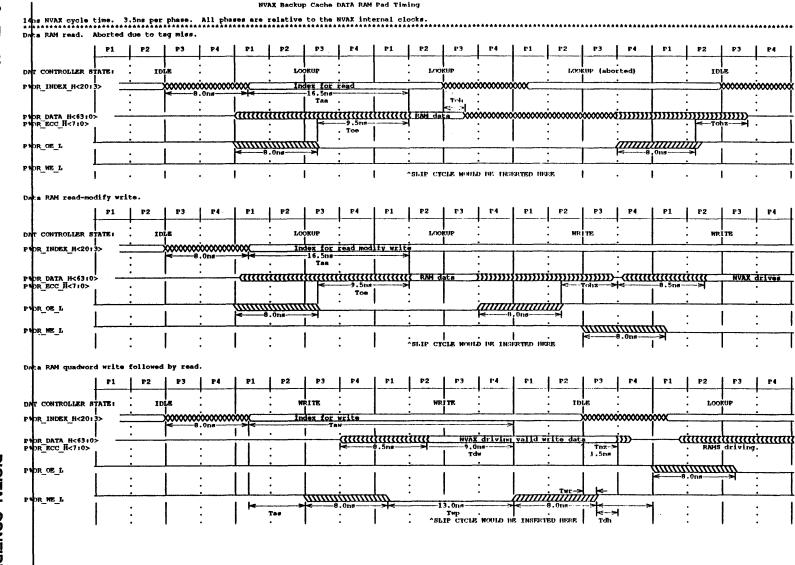

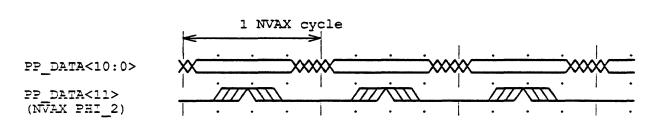

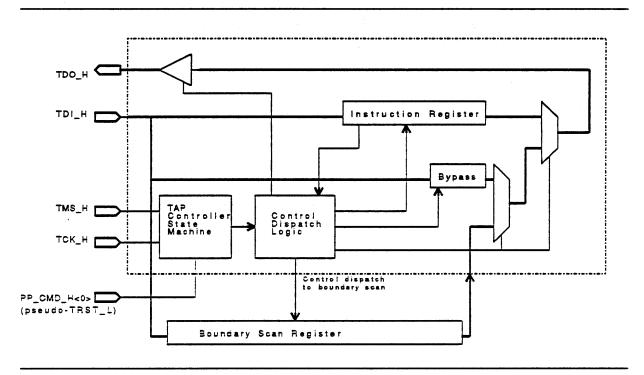

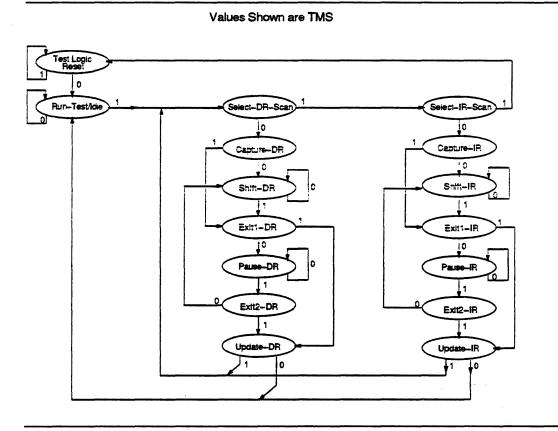

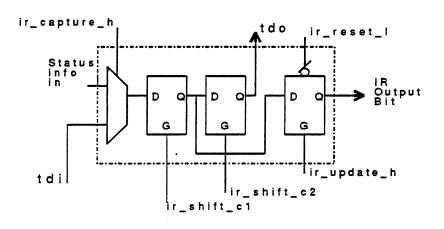

|             |                | 3.2.5.2 <b>P%TEST_STROBE_H •</b> 3–13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3 Control for an end of the state of the |