EK-TSV05-UG-001

# TSV05 Tape Transport Subsystem

User's Guide

# TSV05 Tape Transport Subsystem

User's Guide

Prepared by Computer Special Systems of Digital Equipment Corporation

1st Edition, September 1982

# Copyright (c) 1982 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| d i g i t a 1  TM | DECsystem-10 | MASSBUS |

|-------------------|--------------|---------|

| DEC               | DECSYSTEM-20 | OMNIBUS |

| PDP               | DIBOL        | OS/8    |

| DECUS             | EDUSYSTEM    | RSTS    |

| UNIBUS            | VAX          | RSX     |

|                   | VMS          | IAS     |

# CONTENTS

| CHAPTER 1                                                                                                                                | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1 $1.2$ $1.2.1$ $1.2.2$ $1.2.3$ $1.3.1$ $1.3.2$ $1.3.3$ $1.3.3.1$ $1.3.3.1$ $1.3.3.1$ $1.3.3.1$ $1.3.3.2$ $1.3.3.2$ $1.3.3.3$ $1.4$    | PURPOSE AND SCOPE.1-1GENERAL DESCRIPTION.1-1Features and Capabilities.1-3Functional Overview.1-5Controls and Indicators.1-6PHYSICAL DESCRIPTION.1-9Mechanical Characteristics.1-9Electrical Requirements.1-9Environmental Considerations.1-10Operating Conditions.1-11Emissions.1-11RELATED DOCUMENTS.1-12                                                                                                                                                                                                               |

| CHAPTER 2                                                                                                                                | INSTALLATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.1<br>2.1.1<br>2.1.2<br>2.1.3<br>2.1.4<br>2.2<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.3<br>2.3.1<br>2.3.2<br>2.3.3<br>2.3.4<br>2.3.4.1 | SITE PREPARATION.<br>Accessibility.<br>Power Receptacles.<br>Cooling.<br>Air Purity.<br>UNPACKING AND INSPECTION.<br>Tools and Working Space.<br>Unpacking the Cabinet.<br>Deskidding the Cabinet.<br>2-4<br>Deskidding the Cabinet.<br>2-4<br>Deskidding the Smaller Cartons.<br>2-8<br>TAPE TRANSPORT CABINET INSTALLATION.<br>2-8<br>Tools Required.<br>Moving the Side Panel.<br>2-10<br>Connecting the Cabinets.<br>2-15<br>Removing Shipping Foam.<br>2-18<br>Removing the Top Foam Piece.<br>2-10<br>2-10<br>2-18 |

| 2.3.4.2                                                                                                                                  | Removing the Bottom Foam Pieces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.3.5                                                                                                                                    | Connecting Line Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2.4.1<br>2.4.2                                                                                                                           | Power Up Test2-24<br>Tape Loading Test2-25                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.4.3<br>2.4.4                                                                                                                           | Tape Movement Test2-27<br>Tape Unloading Test2-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2.5                                                                                                                                      | BUS INTERFACE/CONTROLLER MODULE INSTALLATION2-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.6                                                                                                                                      | CABLE INSTALLATION2-29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2.6.1                                                                                                                                    | M7196 Module and Tape Transport<br>Interconnection2-29                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2.6.2                                                                                                                                    | Power Controller Interconnection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.7                                                                                                                                      | TSVØ5 SUBSYSTEM CHECKOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.7.1                                                                                                                                    | Power Up Checks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

# CONTENTS (CONT)

-

-

| 2.7<br>2.7.1<br>2.7.2<br>2.7.3<br>2.7.4<br>2.7.5<br>2.7.6<br>2.7.7<br>2.7.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | TSVØ5 SUBSTYSTEM CHECKOUT           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| CHAPTER 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | OPERATION                           |

| 3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.5.1<br>3.1.5.2<br>3.1.6<br>3.1.7<br>3.1.8<br>3.1.8.1<br>3.1.8.1<br>3.1.8.2<br>3.2<br>3.3<br>3.3.1<br>3.3.2<br>3.3.2.1<br>3.3.2.3<br>3.3.2.4<br>3.3.2.5<br>3.3.2.6<br>3.3.2.7<br>3.3.2.6<br>3.3.2.7<br>3.3.2.8<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.3.1<br>3.3.3.1<br>3.3.3.1<br>3.3.3.1<br>3.3.3.1<br>3.3.3.1<br>3.3.3.1<br>3.3.3.1<br>3.3.3.1<br>3.3.3.1<br>3.3.3.1<br>3.3.3.1<br>3.3.3.1<br>3.3.3.1<br>3.3.3.1<br>3.3.3.1<br>3.3.3.1<br>3.3.3.1<br>3.3.3.1<br>3.3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.2.10<br>3.3.3.1<br>3.3.3.1<br>3.3.3.1<br>3.3.3.1<br>3.3.3.1<br>3.3.3.1<br>3.3.3.1<br>3.3.3.1<br>3.3.3.1<br>3.3.3.1<br>3.3.3.1<br>3.3.3.1<br>3.3.3.1<br>3.3.3.1<br>3.3.3.1 | ROUTINE OPERATING PROCEDURES        |

| 3.3.3.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | General Status Handling Information |

# CONTENTS (CONT)

# Page

| 3.3.4      | COMMANDS                        |

|------------|---------------------------------|

| 3.3.4.1    | Command Packet Definitions      |

| 3.3.4.2    | Get Status Command              |

| 3.3.4.3    | Read Command                    |

| 3.3.4.4    | Write Characteristics Command   |

| 3.3.4.5    | Write Command                   |

| 3.3.4.6    | Position Command                |

| 3.3.4.7    | Format Command                  |

| 3.3.4.8    | Control Command                 |

| 3.3.4.9    | Inititalize Command             |

| 3.3.4.10   | Write Subsystem Memory Command  |

| 3.3.5      | Record Buffering                |

| 3.3.5.1    | Read Buffering                  |

| 3.3.5.2    | Write Buffering                 |

| APPENDIX A | CONFIGURATION DATAA-1           |

| APPENDIX B | MANUAL LOADINGB-1               |

| APPENDIX C | SUMMARY OF KNOWN DIFFERENCESC-1 |

|            |                                 |

# FIGURES

| Figure No                                                   | o. Title                                                                                                                                                                                                                                                                | Page                                                   |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| 1-1<br>1-2<br>2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7 | TSVØ5 Subsystem Components<br>Operator Front Panel<br>Cabinet Access Requirements<br>Cabinet Carton Removal<br>Removing Shipping Bolts<br>Deskidding the Cabinet<br>Tape Transport Cabinet Connection<br>Installing Leveling Feet<br>Computer Cabinet Ground Connection | 1-7<br>2-3<br>2-5<br>2-6<br>2-7<br>2-9<br>2-11<br>2-12 |

| 2-8<br>2-9<br>2-10<br>2-11<br>2-12                          | Removing Side Panel<br>Mounting the Side Panel<br>Cabinet Alignment<br>Cabinet Interconnection Hardware<br>Cabinet Top Cover                                                                                                                                            | 2-14<br>2-16<br>2-17                                   |

| 2-13<br>2-14<br>2-15<br>2-16<br>2-17<br>2-18                | Tape Transport Top Cover<br>Tachometer and Takeup Hub<br>Service Access Position<br>Front Panel Controls and Indicators<br>Inserting Tape<br>Cabling the M7196 Module                                                                                                   | 2-2Ø<br>2-21<br>2-22<br>2-24<br>2-26                   |

v

# је

| 2-19    | Cabling the Tape Transport                        |

|---------|---------------------------------------------------|

| 2-20    | Remote Power Control Connections                  |

| 3-1     | Opening the Front Door Panel                      |

| 3-2     | Accessing the Tape Path Area                      |

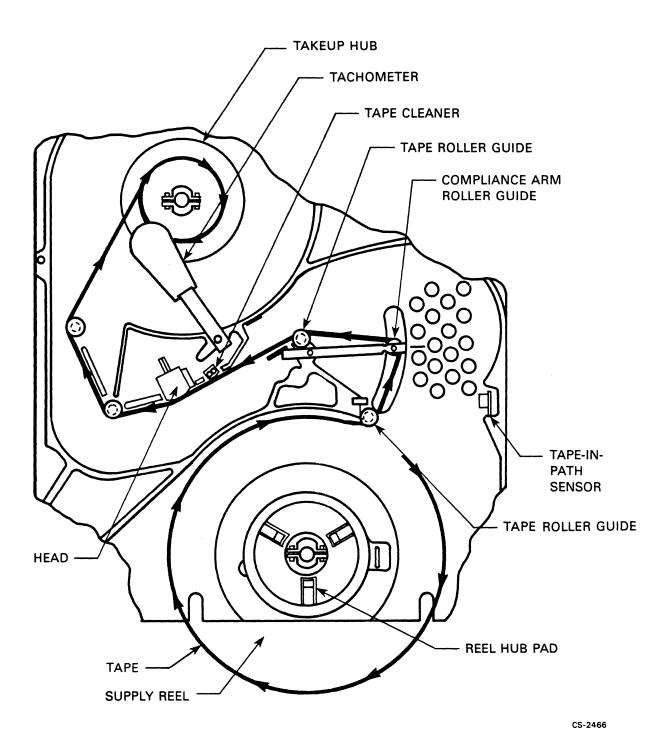

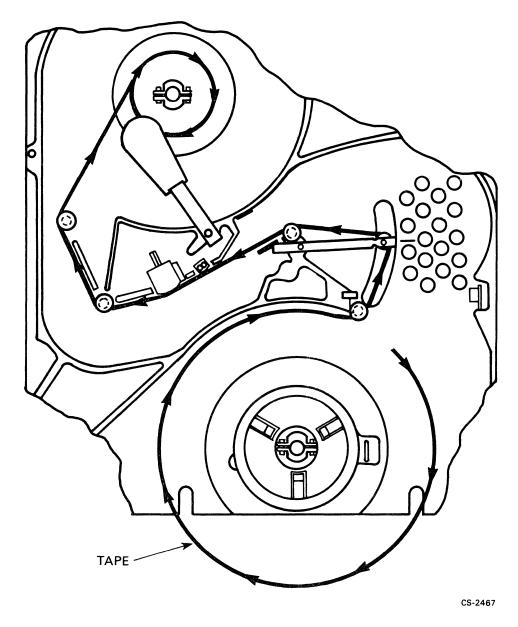

| 3-3     | Tape Path and Related Parts                       |

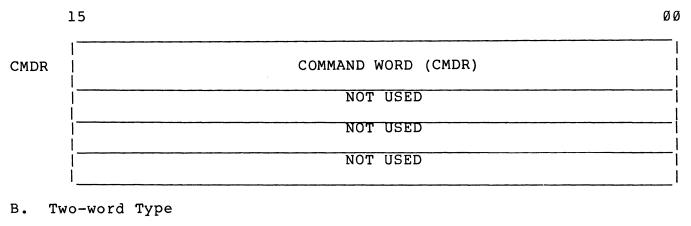

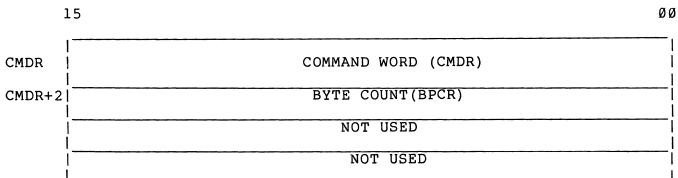

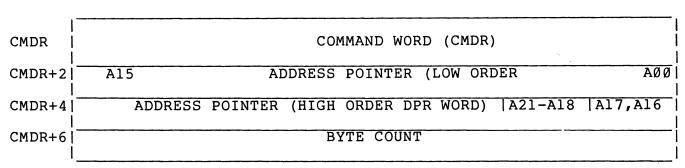

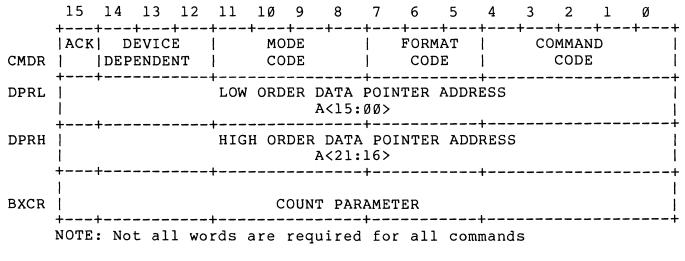

| 3-4     | Command Packet Types                              |

| 3-5     | TSBA Register Format                              |

| 3-6     | TSDB Register Format                              |

| 3-7     | TSSR Register Format                              |

| 3-8     | TSDBX Register Format                             |

| 3-9     | XSTØ Register Format                              |

| 3-1Ø    | XST1 Register Format                              |

| 3-11    | XST2 Register Format                              |

| 3-12    | XST3 Register Format                              |

| 3-13    | XST4 Register Format                              |

| 3-14    | TSVØ5 Hardware Device Registers                   |

| 3-15    | TSVØ5 Extended Status Registers3-38               |

| 3-16    | TSVØ5 Command Register Format                     |

| 3-17    | Message Packet Format                             |

| 3-18    | Command Packet Header Word3-54                    |

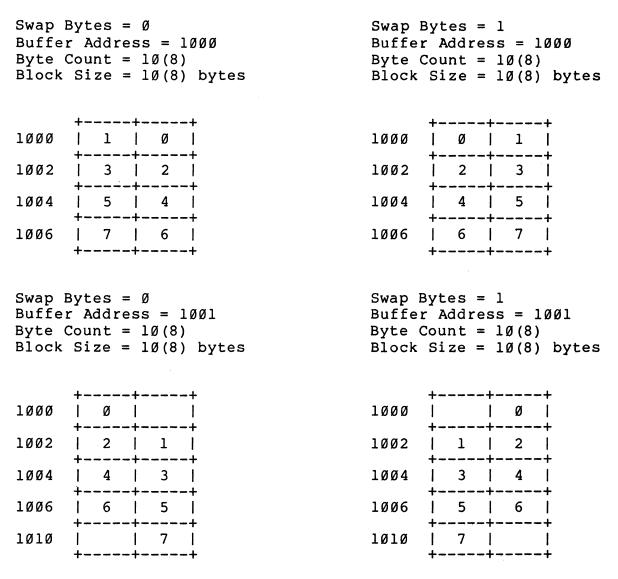

| 3-19(a) | Memory/Tape Data Byte Positioning (Forward Tape   |

|         | Direction, Read or Write; Reverse Read with Even  |

|         | Byte Count)                                       |

| 3-19(b) | Memory/Tape Data Byte Positioning (Forward or     |

|         | Reverse Read, Odd Byte Count)                     |

| 3-2Ø    | Get Status Command Packet                         |

| 3-21    | Read Command Packet                               |

| 3-22    | Write Characteristics Command Format              |

| 3-23    | Write Command Packet                              |

| 3-24    | Position Command Packet                           |

| 3-25    | Format Command Packet                             |

| 3-26    | Control Command Packet                            |

| 3-27    | Initialize Command Packet                         |

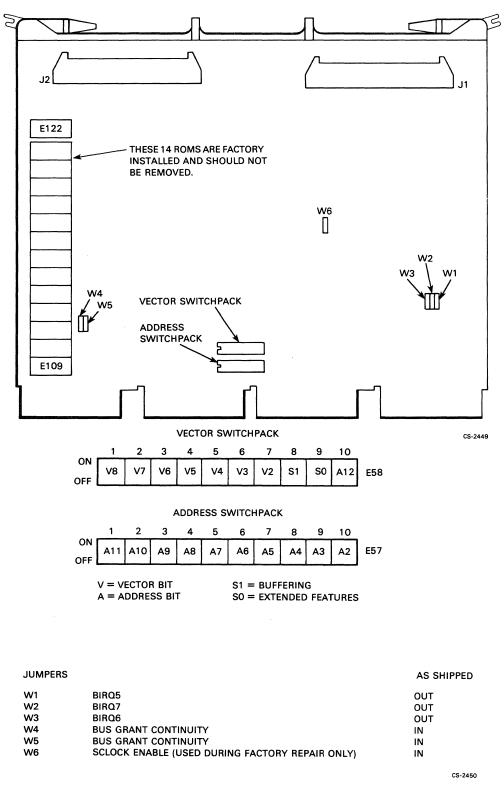

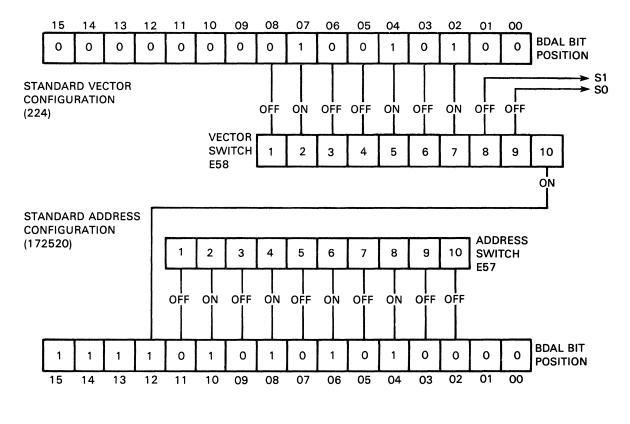

| A-1     | M7196 Switch and Jumper IdentificationA-1         |

| A-2     | M7196 Vector and Address SwitchesA-2              |

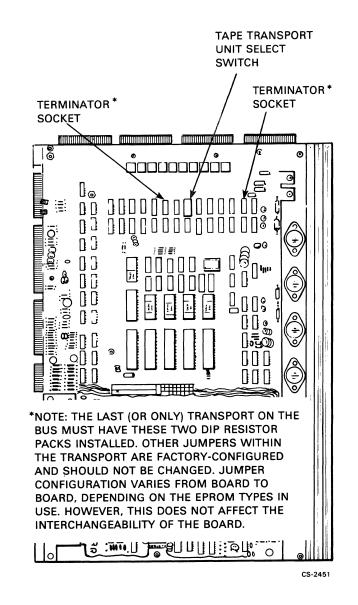

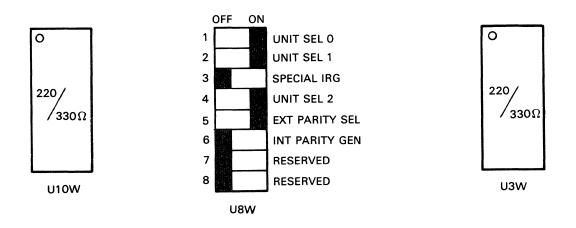

| A-3     | Transport Switch and Terminator IdentificationA-3 |

| B-1     | Accessing the Tape Path AreaB-2                   |

| B-2     | Tape Threading PathB-3                            |

# TABLES

| Table No. | Title                                          | Page |

|-----------|------------------------------------------------|------|

| 1-1       | Controls and Indicators                        |      |

| 2-1       | Power Line Connections                         | 2-2  |

| 2-2       | TSVØ5 Subsystem Diagnostics                    | 2-32 |

| 3-1       | Suggested Preventive Maintenance Schedule      | 3-8  |

| 3-2       | TSVØ5 Assigned Command Modes                   | 3-14 |

| 3-3       | TSBA Register Bit Definitions                  |      |

| 3-4       | TSDB Register Bit Definitions                  | 3-21 |

| 3-5       | TSSR Register Bit Definitions                  | 3-22 |

| 3-6       | TSDBX Register Bit Definitions                 |      |

| 3-7       | XSTØ Register Bit Definitions                  |      |

| 3-8       | XST1 Register Bit Definitions                  | 3-31 |

| 3-9       | XST2 Register Bit Definitions                  | 3-33 |

| 3-1Ø      | XST3 Register Bit Definitions                  |      |

| 3-11      | XST4 Register Bit Definitions                  |      |

| 3-12      | Buffer Ownership Transfers                     |      |

| 3-13      | Message Packet Field Definitions               |      |

| 3-14      | Termination Class/Message Type Relationship    | 3-48 |

| 3-15      | Command Packet Header Word Bit Definitions     |      |

| 3-16      | Command Code and Mode Field Definitions        |      |

| 3-17      | Characteristic Mode Data Word Bit Definitions. | 3-66 |

| 3-18      | Extended Characteristics Data Word Bit         |      |

|           | Definition                                     |      |

#### 1.1 PURPOSE AND SCOPE

This manual describes how to unpack, install, and check out the TSV05 Tape Transport Subsystem. It also describes the capabilities and basic functions of the subsystem. An overview of the functional characteristics and the physical specifications appears in Chapter 1, while Chapter 2 is devoted to the installation. Chapter 3 discusses various aspects of system operation, including routine operating procedures and programming requirements. For further information, refer to the documents listed in Section 1.4.

#### **1.2 GENERAL DESCRIPTION**

The TSV05 Tape Transport Subsystem provides magnetic tape storage capabilities to computer systems using quad-sized LSI-11 bus backplanes. The subsystem reads or writes up to 160,000 bytes per second in ANSI standard format. Data is recorded by phase encoding 1600 bits per inch on nine-track tape. Reading and writing are performed at either 25 or 100 inches per second.\* The TSV05 subsystem is hardware compatible with 18- and 22-bit addressing versions of the LSI-11 bus quad backplane. It is software compatible with system and application programs written for the TS11 tape transport subsystem (as long as such programs use the DECsupplied device handler). Tape formatting, error detection and correction, and self-test diagnostics are included as integral components of the TSV05 subsystem.

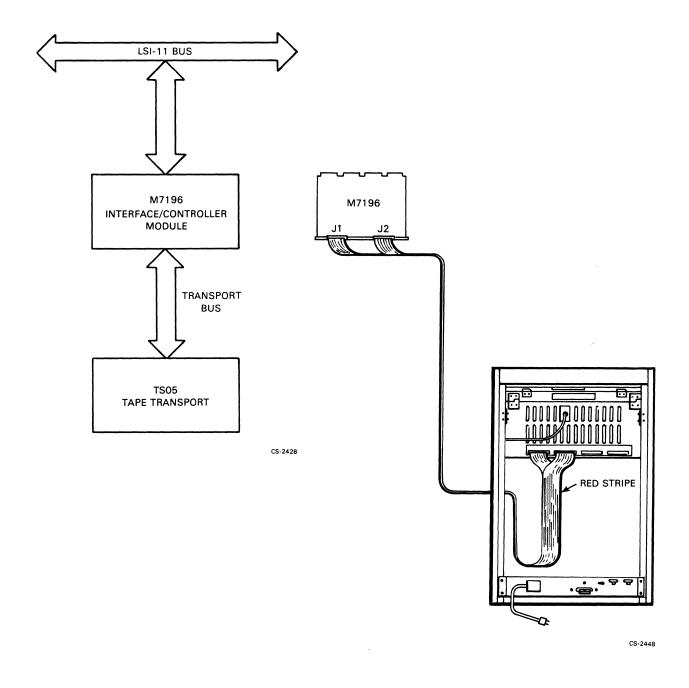

The TSVØ5 hardware consists of four items:

- 1. TSØ5 tape transport

- 2. M7196 LSI-ll bus interface/controller module

- 3. H9642-series cabinet, including 874 power controller and remote power control cable

- 4. Pair of 7016855 bus cables for connecting tape transport input and output to the bus interface/controller module.

The bus interface/controller module plugs into the LSI-11 bus (see Figure 1-1). The two cables connect the module with the tape transport.

\*100 IPS operating speed requires enabling special features and the appropriate software.

Figure 1-1 TSV05 Subsystem Components

#### 1.2.1 Features and Capabilities

The TSV05 Tape Transport Subsystem offers the following:

- o Bidirectional reading capability

- o 3.5K bytes of RAM in controller for buffering tape data

- Streaming, or reel-to-reel, technology (meaning that the tape is not required to stop in the interrecord gap)

- o Automatic tape loading (threading)

- Microprocessor control in both the controller and the tape transport

- o Microcoded diagnostic and maintenance features

- Tape formatting and error detection following ANSI X

3.39-1973 Standard

- o Both ANSI and IBM tape mark detection

- Industry standard bus between controller and tape transport

- On-line diagnostics that verify data path integrity during idle periods

- o Uses media conforming to ANSI X 3.40-1976 Standard

- o Automatic read after write verification

- o Small form factor with low power consumptions.

The tape handling characteristics and parameters are as follows:

#### Tape Characteristics

| Туре:               | Mylar base, iron-oxide coated                                                      |

|---------------------|------------------------------------------------------------------------------------|

| Length:             | 731 m (2400 ft) maximum                                                            |

| Width:              | 1.3 cm (0.5 in)                                                                    |

| Thickness:          | 1.5 mil (industry compatible)                                                      |

| Reel Diameter:      | 26.7 cm (10.5 in) 2400 ft<br>21.6 cm ( 8.5 in) 1200 ft<br>17.8 cm ( 7.0 in) 600 ft |

| Capacity/Tape Reel: | 46 million bytes (10.5 in reel, unfor-<br>matted)                                  |

#### Tape Motion

Handling: Bidirectional reel-to-reel, with compliance arm Tape Tension: 212.6 g (7.5 oz) nominal 64 cm/sec (25 in/sec) (using TS11 Read/Write Speed: software) 64 or 254 cm/sec (25 or 100 in/sec) (program selectable using special software) 330 to 457 cm/sec (130 to 180 in/sec) Rewind Speed: (nominal), depending on reel size 445 cm/sec (175 in/sec) (average), using 26.7 cm (10.5 in) reel

Rewind Time:

| Reel Size, cm (in) | <u>Minutes, maximum</u> |

|--------------------|-------------------------|

| 17.8 (7.0)         | Ø.9                     |

| 21.6 (8.5)         | 1.6                     |

| 26.7 (10.5)        | 2.8                     |

#### Auto Loading

Reliability: An average of 96% of attempted loads will be successful, with automatic retries, assuming a properly maintained transport and tape library. Retries:

Three automatically provided.

| Times: | 3Ø | sec | typical | with | n no | retry      |       |

|--------|----|-----|---------|------|------|------------|-------|

|        | 3Ø | sec | maximum | for  | each | additional | retry |

#### Unloading

Time: 15 sec maximum with tape located at BOT

#### Tape Speed Variation:

| Long Term:     | + | 18 | of | nomir | nal  |

|----------------|---|----|----|-------|------|

| Instantaneous: | + | 48 | of | long  | term |

#### Data Access Times:

|               | 64 cm/sec (25 in/sec) | 254 cm/sec (100 in/sec) |

|---------------|-----------------------|-------------------------|

| Tape at Rest: | 40 ms                 | 260 ms                  |

| Worst Case:   | 140 ms                | 1040 ms                 |

| Data Transfer Rate:            | 40K bytes/sec a<br>in/sec)                                       | it 64                    | cm/sec (25                             |

|--------------------------------|------------------------------------------------------------------|--------------------------|----------------------------------------|

|                                | l60K bytes/sec a<br>in/sec)                                      | t 254                    | cm/sec (100                            |

| Data Organization              |                                                                  |                          |                                        |

| Number of Tracks:              | Nine (eight data;                                                | one pa                   | rity)                                  |

| Recording Density:             | 1600 bits/in (non                                                | selecta                  | ble)                                   |

| Interrecord Gap:               | l.3 cm (0.5 in)<br>(0.65 in) typical<br>in/sec)                  |                          | -                                      |

| Recording Method:              | Phase encoded (PE)                                               | )                        |                                        |

| Error Rates:                   | Recoverable Write                                                | : l en<br>bits           | rror in 10 <sup>8</sup><br>transferred |

|                                | Recoverable Read:                                                | l en<br>bits             | rror in 10 <sup>9</sup><br>transferred |

|                                | Unrecoverable Read                                               | d: l er<br>bits          | ror in lØ <sup>1Ø</sup><br>transferred |

| The LSI-11 bus interface chara | acteristics are as                                               | follow                   | s:                                     |

| Address Space Required:        | 772520/772522<br>772524/772526<br>772530/772532<br>772534/772536 | lst<br>2nd<br>3rd<br>4th | unit<br>unit<br>unit<br>unit           |

| Vectors Required:              | 224                                                              | lst                      | unit                                   |

#### 1.2.2 Functional Overview

Tape loading is automatic. There are no vacuum columns, retaining clips, or multiple tension arms. When the tape transport is powered up, sets of internal diagnostics are run by the microprocessors in the tape transport electronics package and the bus interface/controller module. The subsystem is then ready for loading. Once the tape has been inserted and the door closed, the TSØ5 tape transport automatically seats and locks the tape reel on the spindle, and threads the tape through the correct path to the takeup reel. The threading operation is accomplished by precisely directed air flows that blow the tape along the path to the takeup reel. When this power up and load sequence is complete, control of the tape transport switches to the controller module.

2nd

3rd

4th

unit

unit

unit

Rank of 37 in the floating vector area starting at 300.

The TSV05 subsystem operates under the control of a microprocessor on the M7196 bus interface/controller module. The module is a direct memory access (DMA) device in that it transfers data di-rectly into or out of the LSI-11 memory without requiring the control of the LSI-11 CPU. To perform a data transaction with the TSV05 subsystem, the LSI-ll first builds a "packet" of command words in main memory. Next, it passes the starting address of the command packet to the M7196 module. Using this address, the M7196 module performs a DMA transfer to bring the command packet out to the controller memory. The command packet tells the controller what type of operation is to be performed and where the data is to come from or go to. The module then controls the movement of data from LSI-11 memory to the tape, or from tape to memory. It buffers this data so that DMA transfers can be handled independently of the mechanical movements of the tape. Additionally, it generates interrupts when necessary to provide the LSI-11 with status information.

The TSØ5 tape transport has an internal formatter that controls tape motion, formatting and writing of data on tape, reading of data from tape, and tape transport status monitoring. Commands from the M7196 module are latched into registers and then processed by a microprocessor in the formatter electronics. The formatter creates the identification (ID) burst, preamble, post amble, and file mark during a write operation, and it interprets these during a read operation. The formatter also oversees the handling of error conditions.

#### 1.2.3 Controls and Indicators

The M7196 bus interface/controller module has jumpers, DIP switchpacks, and LED indicators. The jumpers and switchpacks are preset to the normal configuration and do not need to be changed unless there is an address conflict with an existing device. The LED indicators are provided as maintainability features, and are not exposed to view during normal operation.

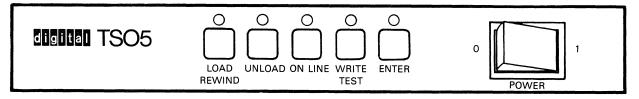

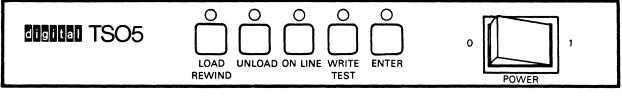

The TSØ5 tape transport has an ON/OFF  $(1/\emptyset)$  power switch and five tactile switches, each with an LED indicator. (Refer to Figure 1-2.) The functions of these controls and indicators are described in Table 1-1. The TSØ5 tape transport also has internal switches for selecting tape units and enabling certain features, but these are preset and normally not changed. It also has an LED fault indicator. This LED is not exposed to view during normal operation.

# Figure 1-2 Operator Front Panel

| Control/<br>Indicator | Туре                                  | Function                                                                                                          |

|-----------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| POWER                 | On/off rocker switch<br>and indicator | Switches line power on and off.                                                                                   |

| LOAD<br>REWIND        | Tactile switch and indicator          | <ol> <li>Blinks when the tape drive<br/>is executing a load or re-<br/>wind sequence.</li> </ol>                  |

|                       |                                       | <ol> <li>Lit continuously when the<br/>beginning of tape (BOT)<br/>marker is sensed.</li> </ol>                   |

|                       |                                       | 3. Pressing the switch:                                                                                           |

|                       |                                       | a. Initiates load sequence<br>and advances tape to<br>load point.                                                 |

|                       |                                       | b. Rewinds the tape to<br>load point.                                                                             |

| UNLOAD                | Tactile switch and indicator          | <ol> <li>Pressing the switch causes<br/>the tape to be unloaded<br/>regardless of tape posi-<br/>tion.</li> </ol> |

|                       |                                       | <ol> <li>Blinks when the tape drive<br/>is executing an unload se-<br/>quence.</li> </ol>                         |

# Table 1-1 Controls and Indicators

| Control/<br>Indicator | Туре                                                                        | Function                                                                                                                                                                                                              |

|-----------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       |                                                                             | 3. Lit continuously when the<br>tape drive has completed<br>its unload sequence and<br>the front access door is<br>unlocked. At this time,<br>the tape may be removed<br>and another tape inserted<br>into the drive. |

|                       |                                                                             | <ol> <li>Lit continuously after a<br/>successful power up, indi-<br/>cating a tape may be<br/>loaded.</li> </ol>                                                                                                      |

| ON-LINE               | Tactile switch and<br>Indicator                                             | <ol> <li>Lit when drive is ready<br/>and on-line.</li> </ol>                                                                                                                                                          |

|                       |                                                                             | 2. Pressing the switch:                                                                                                                                                                                               |

|                       |                                                                             | a. Takes the tape drive<br>off-line and extin-<br>guishes the indicator.                                                                                                                                              |

|                       |                                                                             | b. Puts the tape drive<br>on-line and lights the<br>indicators.                                                                                                                                                       |

|                       | NOT<br>Pressing the switch<br>quence puts the tape<br>the BOT marker is sen | during a load se-<br>drive on-line when                                                                                                                                                                               |

| TEST                  | Tactile switch                                                              | Operational only in the test<br>mode. Selects alternative op-<br>erational mode for other<br>switches.                                                                                                                |

| WRITE                 | Indicator                                                                   | <ol> <li>Lit when the write ring is<br/>installed and data may be<br/>written on tape.</li> </ol>                                                                                                                     |

|                       |                                                                             | <ol> <li>When indicator is off,<br/>write ring is not in-<br/>stalled and tape is file<br/>protected.</li> </ol>                                                                                                      |

| ENTER                 | Tactile switch                                                              | This control is used for man-<br>ual loading, and controlling<br>the test mode.                                                                                                                                       |

| Table 1-1 | Controls | and | Indicators | (Cont)  |

|-----------|----------|-----|------------|---------|

| Table T-T | CONCLOYS | ana | THUTCALOLD | (00110) |

#### 1.3 PHYSICAL DESCRIPTION

# 1.3.1 Mechanical Characteristics

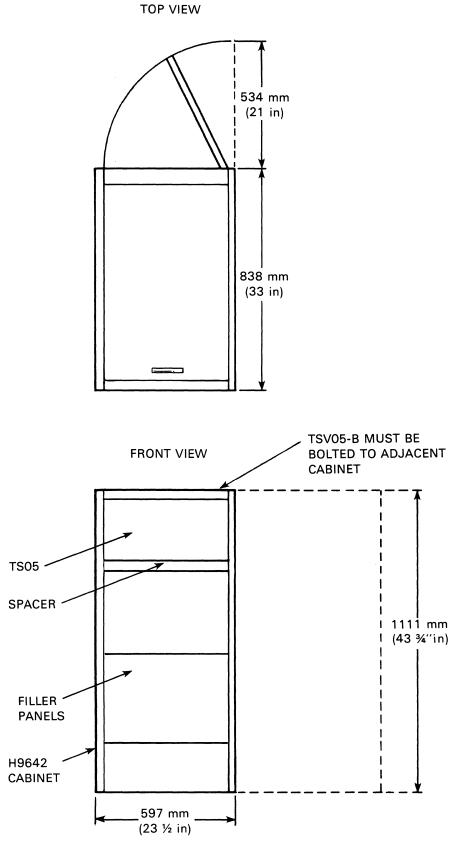

# Tape Transport Cabinet

| Height: | 111.13 cm (43.75 in) |

|---------|----------------------|

| Width:  | 59.69 cm (23.50 in)  |

| Depth:  | 83.82 cm (33.00 in)  |

| Weight: | 121 kg (265 lb)      |

# M7196 Bus Interface/Controller Module

| Length:    | (From contact fingers to handles): 228.6 mm (9.0 in) |

|------------|------------------------------------------------------|

| Width:     | 266.7 mm (10.5 in)                                   |

| Thickness: | 12.7 mm (Ø.5 in)                                     |

| Weight:    | Ø.51 kg (l.13 lb)                                    |

# Formatter Bus Cables

| Connectors: | 50-pin, | right-angle,                   | flat     | cable | header | con- |

|-------------|---------|--------------------------------|----------|-------|--------|------|

|             | -       | at controller<br>er connectors | •        |       | -      |      |

|             |         |                                | <u>-</u> |       | -      |      |

Length: 2.4 m (8.0 ft)

# 1.3.2 Electrical Requirements

# Tape Transport Cabinet

| Power | Consumption: | 220 | W | average |

|-------|--------------|-----|---|---------|

|       |              | 27Ø | W | maximum |

Voltage (+7% or -15%):

|          | Nominal, Vdc | Low Limit, Vdc | <u>High Limit, Vdc</u> |

|----------|--------------|----------------|------------------------|

| TSVØ5-BA | 120          | 102            | 128                    |

| TSVØ5-BB | 24Ø          | 204            | 256                    |

| TSVØ5-BD | 220          | 187            | 235                    |

Frequency:  $\pm$  1 Hz

| Nominal, Hz | Low Limit, Hz | <u>High Limit, Hz</u> |

|-------------|---------------|-----------------------|

| 50 or 60    | 49            | 61                    |

Frequency Rate of Change: 1.5 Hz/sec maximum

#### M7196 Controller

Power Consumption: 5 Vdc + 5% at 6.5 A (maximum)

LSI-11 Bus Loading: DC: One load AC: Three loads (maximum)

#### 1.3.3 Environmental Considerations

1.3.3.1 Operating Conditions -- The TSV05 subsystem is designed to operate under the following conditions:

#### Temperature

$15^{\circ}C$  to  $32^{\circ}C$

Temperature Shock: 20° C change/hr maximum

#### Relative Humidity

20% to 80% noncondensing

#### Altitude

Sea level to 3 km (10,000 ft)

#### Vibration

Frequency Range: 5 to 500 Hz

Peak Acceleration: 0.25 g, 22 to 500 Hz, 0.01 in DA5-22 Hz

Application: Each of three orthogonal axes

#### Shock

+10 g peak, Halfsine, 10 ms

#### Pollutants

Atmospheric Particulates: 60 mg/1000 cu ft air by weight of particle (5 micron diameter)

#### Electrostatic Discharge

10 kV through 100 ohms from 350 pF

1.3.3.2 Nonoperating Conditions -- The TSV05 subsystem is designed to withstand the following conditions during nonoperating periods (e.g., shipping): Temperature  $-40^{\circ}$  C to  $66^{\circ}$  C Relative Humidity 95% maximum, noncondensing Altitude Sea level to 15 km (49,000 ft)NOTE Magtape media typically has more restricting nonoperating environmental considerations. Vibration (in shipping container) Frequency Range: 10 to 300 Hz Peak Acceleration: 1.4 g rms vertical axis Ø.68 g rms longitudinal and lateral axis 200 Hz maximum Shock (in shipping container) Peak Acceleration: 20 g Duration: 30 + 10 ms Waveshape: 1/2 sine 1.3.3.3 Emissions -- During normal operation, the TSV05 subsystem is designed to emit no more than the following levels: Heat 1100 Btu/hr maximum Acoustic Noise Standby (blower on): 57 dB A scale Operating Conditions: 60 dB A scale

1-11

#### Electromagnetic Interference (EMI)

Complies with FCC Part 15, Subpart J, Class A. Designed to comply with VDE Ø871 B requirements.

NOTE

The TSV05 subsystem has been designed and tested to meet Digital standards including FCC requirements. The specifications in this chapter are based on this testing. Digital cannot guarantee the TSV05 subsystem will meet these specifications if nontested equipment is installed into the TSV05 cabinet or the TSV05 cabinet is installed in nontested configurations.

#### 1.4 RELATED DOCUMENTS

| Title                                                                                 | Order Number |

|---------------------------------------------------------------------------------------|--------------|

| TSVØ5 Tape Transport Pocket Service Guide                                             | EK-TSVØ5-PS  |

| Operation and Maintenance Instructions for<br>Model F880 Tape Transport               | 799816-000*  |

| TSVØ5 Tape Transport Subsystem Installation Guide                                     | EK-TSVØ5-IN  |

| XXDP User Guide                                                                       | AC-90931-MC  |

| DEC/X11 User Document                                                                 | AC-824ØZ-MC  |

| TS05 Tape Transport Operation and Acceptance<br>Preventive Maintanance Remove/Replace | EY-D3142-PS  |

| TSVØ5 Field Print Set                                                                 | MP-01157     |

| TSVØ5 Subsystem Technical Manual                                                      | EK-TSVØ5-TM  |

| Microcomputers and Memories                                                           | EB-18451-2Ø  |

| Microcomputer Interfaces Handbook                                                     | EB-17723-2Ø  |

#### CAUTION Reference the appropriate TSVØ5 Manual for installation, operation, and maintenance information.

<sup>\*</sup>Available from Cipher Data Products, 10225 Willow Creek Road, San Diego, California 92131. This document contains detailed drawings of the TS05 formatter and power supply.

This chapter explains the TSV05 Tape Transport Subsystem installation. A section is devoted to each of the following:

- 1. Site preparation

- 2. Unpacking and inspection

- 3. Installing the tape transport cabinet

- 4. Checking out the tape transport

- 5. Installing the bus interface/controller module

- 6. Installing the interconnecting cables

- 7. Checking out the TSV05 subsystem.

#### NOTE

BEFORE YOU UNPACK the cartons, inspect for signs of shipping damage. If the shipment has been damaged, call the dealer from whom the equipment was purchased. If the equipment is covered under "Digital Transit Insurance", the Digital representative will estimate the damage and put in a claim. If the equipment is not insured by "Digital Transit Insurance" contact the carrier who handled the equipment and your own insurance company. Digital Field Service is available on a per-call basis to make estimates of damage for any resulting insurance claims.

#### 2.1 SITE PREPARATION

The TSV05 Tape Transport Subsystem mounts to the left side of the existing computer cabinet. It requires a 59.7 centimeter (23.5 inch) wide by 83.8 centimeter (33.0 inch) deep area of floor space that is capable of supporting, as a minimum, 121 kilograms (265 pounds). The cabinet is capable of supporting up to 205 kilograms (450 pounds).

Beyond this mounting space, the TSVØ5 subsystem also requires room for access to the cabinet, the correct power receptable, and an adequate flow of cooling air.

#### 2.1.1 Accessibility

The cabinet requires sufficient space behind it for opening the rear door. If any expansion is anticipated, room in front of the cabinet will be required to allow future equipment to be pulled out of the cabinet for maintenance. Refer to Figure 2-1 for the required dimensions.

#### 2.1.2 Power Receptacles

Ensure that the correct power receptacle is available (refer to Table 2-1). It should be capable of handling at least the 270 watts required by the tape transport.

| MODEL           | PLUG                                               | RECEPTACLE         | CIRCUIT RATING   |

|-----------------|----------------------------------------------------|--------------------|------------------|

| TSV05-BA        | SILVER<br>BRASS<br>NEMA #L5-30P<br>DEC #12-11193   | L5-30R<br>12-11194 | 120 V<br>24 A    |

| TSV05-BB<br>-BD | BRASS 2<br>BRASS 1<br>NEMA #6-15P<br>DEC #90-08853 | 6-15R<br>12-11204  | 220/240 V<br>12A |

#### Table 2-1 Power Line Connections

CS-2431

Power Cord Color Code

#### Pin Connection

| Color        | Function | <u>L5-30P</u> | <u>6-15P</u> |

|--------------|----------|---------------|--------------|

| Brown        | Hot      | Brass         | Brass l      |

| Blue         | Neutral  | Silver        | Brass 2      |

| Green/yellow | Ground   | Ground        | Ground       |

#### 2.1.3 Cooling

The TSV05 subsystem requires 1100 Btu per hour of cooling to be provided by the movement of room air through the cabinet.

Figure 2-1 Cabinet Access Requirements

#### 2.1.4 Air Purity

The tape transport is equipped with internal filters to prevent dust from accumulating on the tape and tape heads. Nevertheless, it is good practice to avoid placing the cabinet in the path of a dust-laden current of air (such as beside a door).

#### 2.2 UNPACKING AND INSPECTION

The TSV05 is shipped as one skid-mounted carton and one or more smaller cartons. The carton on the skid contains the TS05 tape transport cabinet. The smaller carton(s) contain the M7196 controller, the documentation and accessories, and two individually packaged cables. These smaller items may be shipped in one carton or two, depending on shipping requirements. Check the shipping documents to ensure that the correct model has been shipped. If anything is missing, damaged, or incorrect, contact the dealer from whom the equipment was ordered.

**2.2.1 Tools and Working Space** The following tools are required for unpacking the TSVØ5 subsystem:

- 1. Scissors

- 2. 9/16 inch wrench

- 3. 3/4 inch wrench

- 4. Hammer

- 5. 5/32 inch hex key

Also, an area of approximately 3 meters (10 feet) square is required for moving the cabinet off the shipping skid.

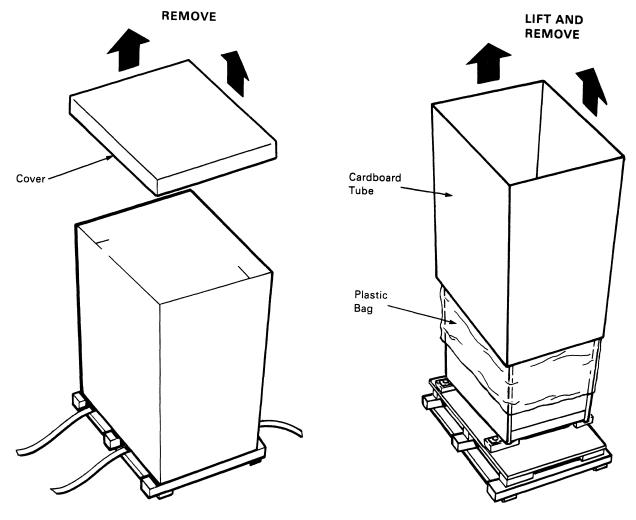

2.2.2 Unpacking the Cabinet

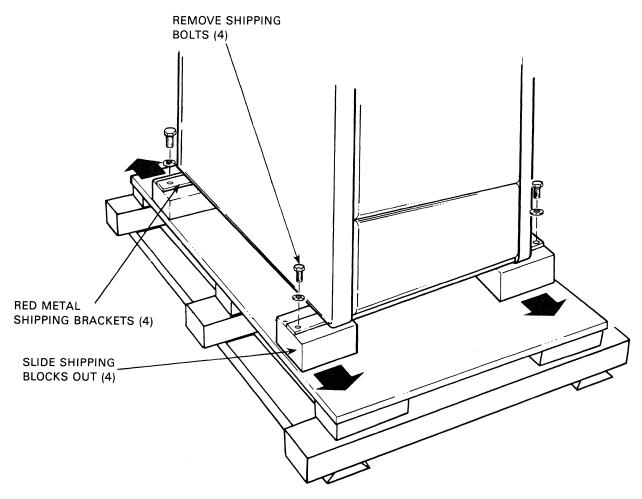

- Cut the nylon straps and remove the cardboard pieces of the cabinet carton as shown in Figure 2-2. Remove the plastic bag.

- 2. Using a 9/16 inch wrench, remove the four bolts that hold the cabinet to the skid.

- 3. Slide the wooden blocks out from under the cabinet (see Figure 2-3).

CAUTION Once the blocks have been removed, the cabinet is free to roll on its casters. The cabinet is top-heavy and must be handled with care.

The blocks may require a few taps with a hammer to move them out from under the cabinet. It may be helpful to tilt the cabinet slightly while removing the blocks.

Figure 2-2 Cabinet Carton Removal

#### Figure 2-3 Removing Shipping Bolts

#### 2.2.3 Deskidding the Cabinet

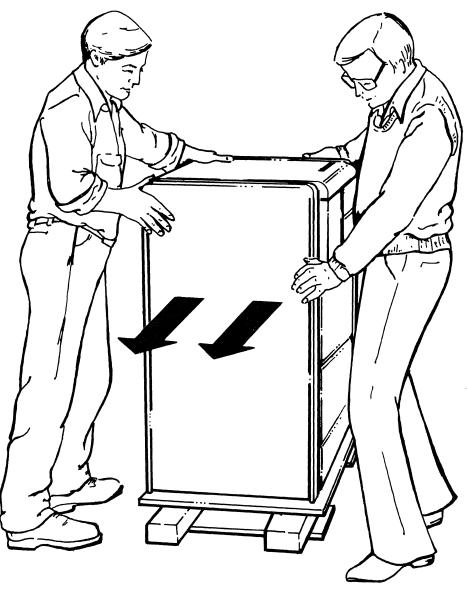

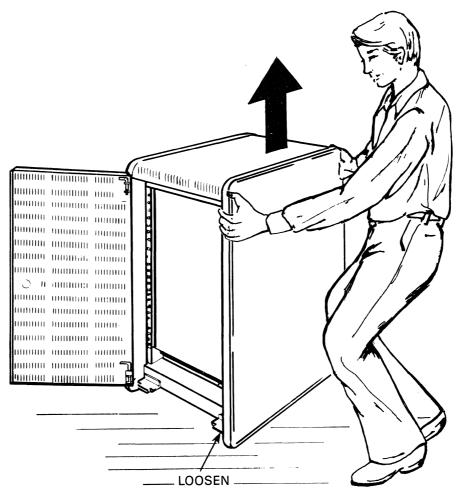

#### WARNING Two people are required for moving the cabinet off the skid.

The recommended procedure for removing the tape transport cabinet from the skid is as follows:

- 1. One person stands in front of the cabinet while the other person stands behind it.

- 2. Grasp the cabinet by right top and by the left center, as shown in Figure 2-4.

- 3. Roll the cabinet off the side of the skid, taking care to prevent it from toppling over.

- 4. When the casters on the left side of the cabinet are on the floor, push the skid out from under the right side of the cabinet. Take care to prevent the cabinet from hitting the floor hard or toppling.

# Figure 2-4 Deskidding the Cabinet

- With the cabinet standing on the floor, use a 3/4 inch wrench to remove the red metal shipping brackets from the bottom. After they are loosened, the brackets slide outward.

- 6. Open the rear door using a 5/32 inch hex key (see Figure 2-6) and verify that the envelope taped to the bottom of the cabinet contains:

- a. 7008288-8F remote cable

- b. H9544-HB leveler feet and hardware

- c. 7422224/7422225 intercabinet hardware

2.2.4 Unpacking the Smaller Cartons Open the smaller cartons and check that they contain the following:

- 1. M7196 bus interface/controller module

- 2. Two interconnection cables (part number 7016855-08)

- 3. TSV05 Tape Transport Installation Manual (EK-TSV05-IN) (this manual)

- 4. TSV05 Tape Transport User's Guide (EK-TSV05-UG)

- 5. TSVØ5 Pocket Service Guide (EK-TSVØ5-PS)

- 6. 26.7 centimeter (10.5 inch) magtape number 30-18709-08

- 7. Tape cleaning kit part number TUCO2

- 8. MPØ1157 field print set.

Visually inspect each item. If any item is damaged, missing, or incorrect, contact the dealer from whom the system was purchased.

### 2.3 TAPE TRANSPORT CABINET INSTALLATION

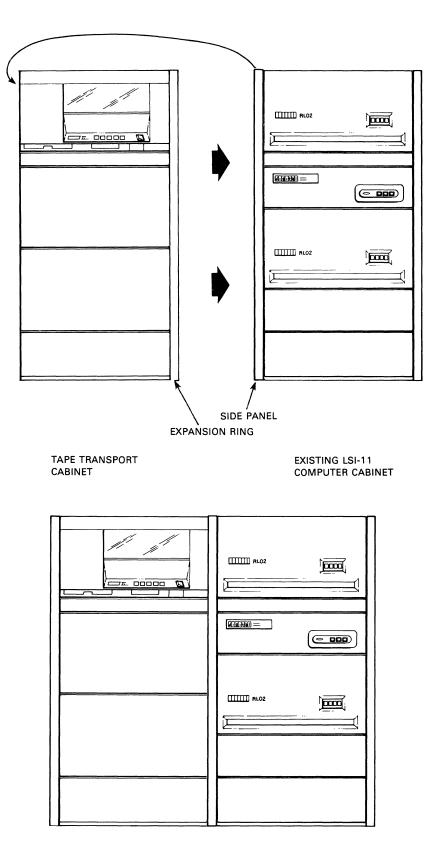

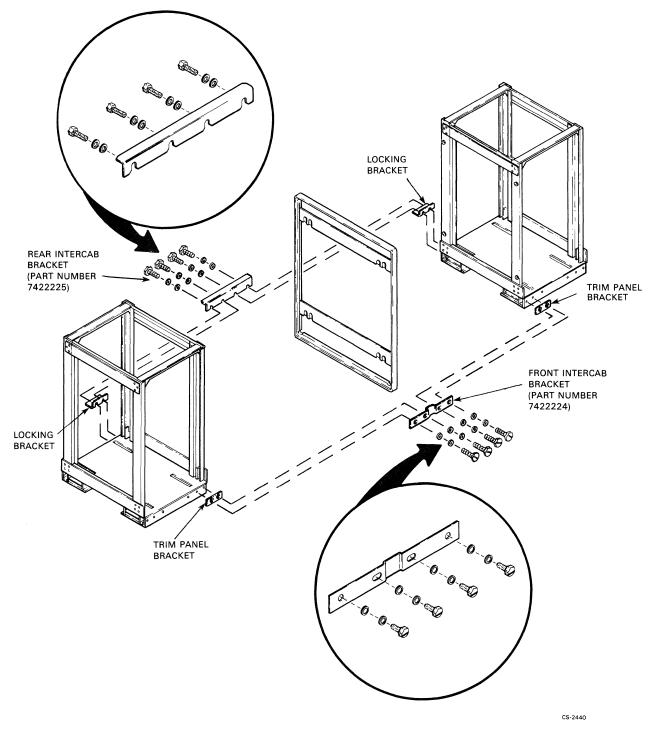

The TSV05 subsystem is designed to be connected to the left side of an H9642 cabinet that contains a PDP-11/23 computer. Older LSI-11 computer systems that use H9612 cabinetry require alternative installation procedures. These procedures are defined in the MP01157 print set. The tape transport cabinet is shipped with no side panels, but with an expansion ring on the right side of the cabinet. (Refer to Figure 2-5.) The left side panel of the computer cabinet is moved to the left side of the tape transport cabinet. Then the right side of the tape transport cabinet is bolted to the left side of the computer cabinet.

#### EXPANDED SYSTEM

CS-2436

Figure 2-5 Tape Transport Cabinet Connection

This configuration has been tested for compliance with FCC requirements. Installing the TSV05 subsystem in other configurations may result in higher levels of EMI radiation.

# 2.3.1 Tools Required

Cabinet installation requires the following tools:

- 1. 9/16 and 11/16 inch wrench (for leveling feet)

- 2. 5/32 inch hex key (for door)

- 3. 7/16 inch wrench (for bolting cabinet together)

- 4. Screwdriver or nut driver, as applicable, for connecting ground cable.

#### 2.3.2 Moving the Side Panel

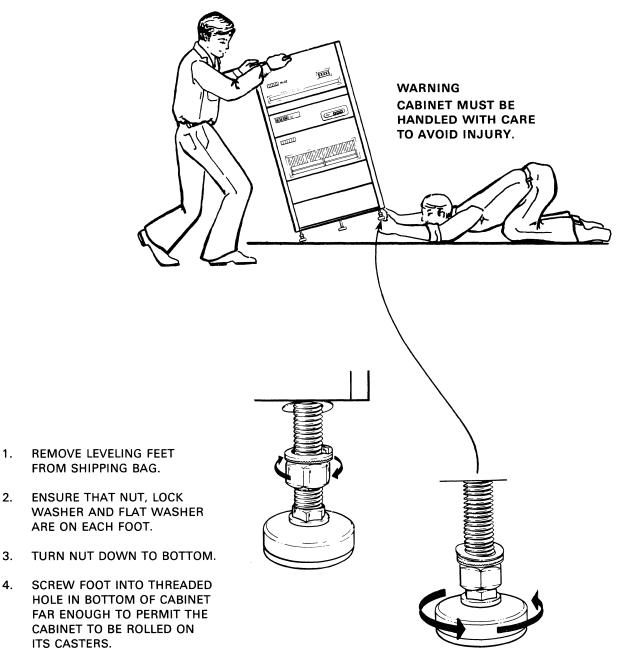

Install the TSØ5 cabinet levelers and move the side panel as follows:

Install the four leveling feet on the bottom of the TSØ5 cabinet (Refer to Figure 2-6.) The leveling feet are screwed into the holes previously used by the red shipping brackets. The cabinet must be tilted to the left to provide clearance for installing the feet on the right side, and tilted to the right while installing the feet on the left side.

#### CAUTION

Do not tilt cabinet more than necessary. Approximately 5 centimeters (2 inches) of clearance is necessary to insert the leveling feet.

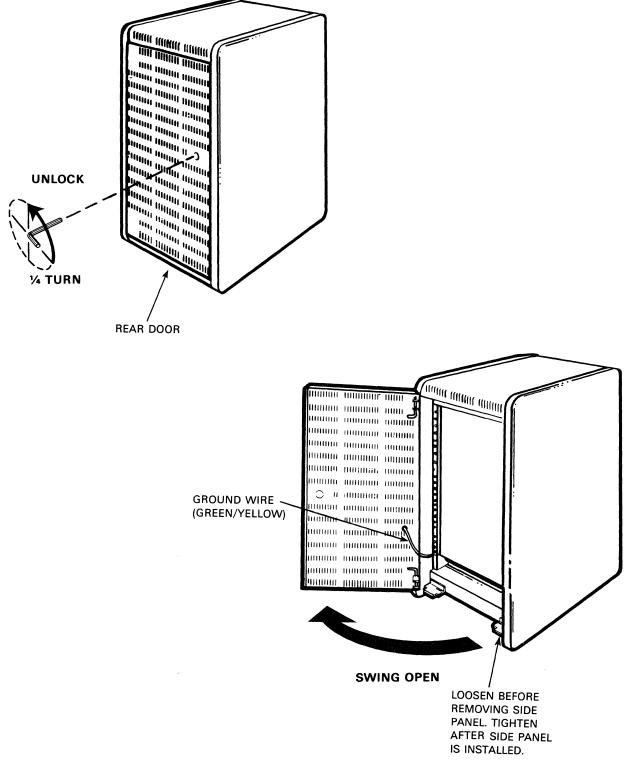

- Open the rear door of the TSØ5 cabinet and the CPU cabinet. Typically, this requires inserting the hex key into the latch and turning it 1/4 turn counterclockwise. (See Figure 2-7.)

- 3. Remove the locking bracket located at the rear bottom, right-hand side of both cabinets. Each bracket is held by two bolts. Loosen but DO NOT remove the bolts.

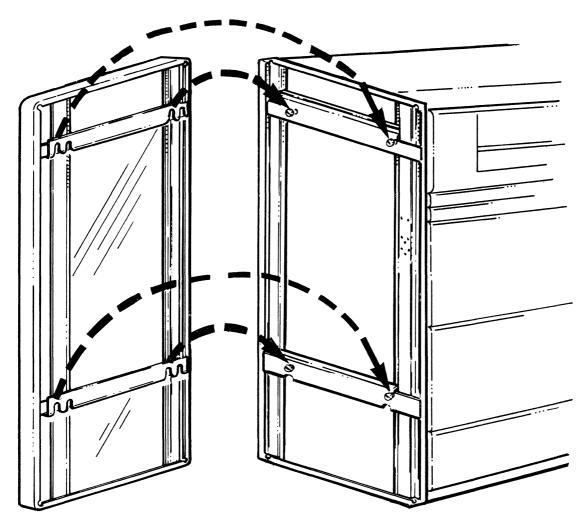

- 4. Lift the side panel straight up and remove it from the CPU cabinet left side (see Figure 2-8). Disconnect the side panel ground wire from the cabinet frame.

- 5. Place the side panel removed in step 4 next to the TSØ5 cabinet left side. Connect the side panel ground strap to the TSØ5 cabinet using the hardware supplied on the left rear cabinet rail.

Figure 2-6 Installing Leveling Feet

Figure 2-7 Computer Cabinet Ground Connection

CS-2441

Figure 2-8 Removing Side Panel

- 6. Position the side panel against the TSØ5 cabinet such that the slots align with the pins. (Refer to Figure 2-9.) Hold the side panel a few inches above its mounted position until it is even with the front and rear of the cabinet. Slide the panel straight down such that the four pins engage the four slots.

- 7. Reinstall and tighten the bracket located on the TSØ5 cabinet at the rear bottom right side. This was one of the brackets removed in step 3.

Figure 2-9 Mounting the Side Panel

#### 2.3.3 Connecting the Cabinets

The two cabinets must be connected together both mechanically and electrically. The mechanical connection is made as follows:

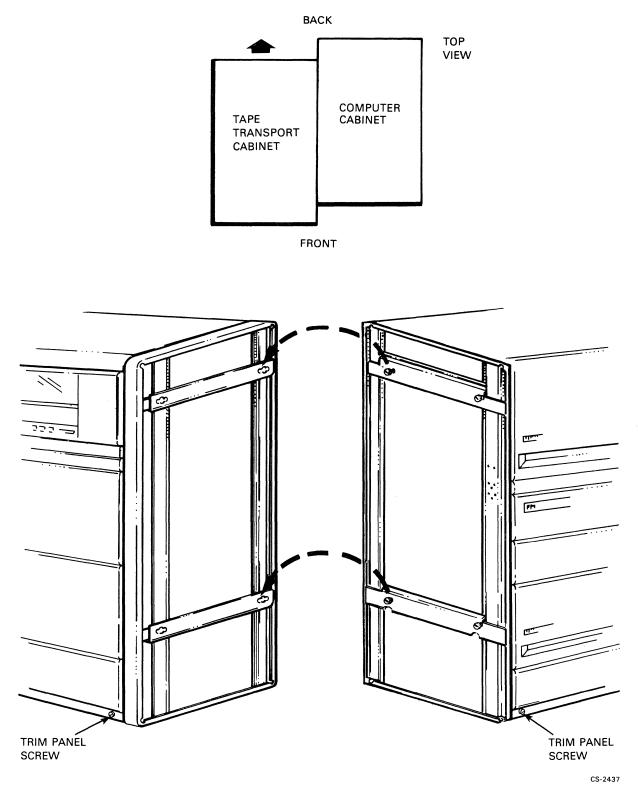

- 1. Roll the TSØ5 cabinet, with side panel attached, next to the CPU cabinet left side. Place the TSØ5 cabinet 1 inch forward of the CPU cabinet such that the pins in the CPU cabinet align with the cutouts in the trim panel. To obtain this alignment, adjust the TSØ5 leveling feet until the top of the TSØ5 cabinet is level with the top of the CPU cabinet.

- 2. Push the TSØ5 cabinet sideways so that it is against the computer cabinet. Push the TSØ5 cabinet backwards until it is even with the CPU cabinet. Check that all the pins are engaged properly into the trim panel. (Refer to Figure 2-10.)

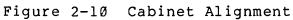

- 3. Reinstall the second locking bracket that was removed in Section 2.3.2, step 3. Do not tighten it. This bracket is located on the CPU cabinet bottom rear, right-hand side. (Refer to Figure 2-11.)

- 4. Loosen, but DO NOT REMOVE, the TSØ5 locking bracket that holds the rear door bottom pivot pin. This is easier if you partially remove the TSØ5 rear door by pushing down on the top pivot pin and raising the rear door out of the bottom pivot hole.

- 5. Install the rear intercab bracket as shown in Figure 2-11. Tighten the four screws, ensuring all brackets are fully down. Reinstall the TSØ5 rear door if it was removed in step 4.

- Remove the bottom trim panels located on the CPU and TSØ5 cabinets. Typically, this panel is held in place by two phillips head screws.

- 7. Remove the four center-most bolts and two center-most trim panel brackets from the cabinetry.

- 8. Refer to Figure 2-11 and install the front intercab bracket. Reinstall the two trim panel brackets and tighten the four bolts, and then reinstall both bottom trim panels.

- 9. Recheck the cabinetry leveling. Adjust the leveling feet of both cabinets, if necessary, to ensure that the system is properly leveled and all leveling feet are properly supporting the system.

Figure 2-11 Cabinet Interconnection Hardware

# 2.3.4 Removing Shipping Foam

The tape transport is shipped with foam cushions protecting the takeup hub and blower motor. These cushions must be removed before the unit is powered up. This requires opening the tape transport to the operator maintenance access position to remove the foam from around the takeup hub, and opening it to the service access position to remove two other pieces of foam.

# 2.3.4.1 Removing the Top Foam Pieces

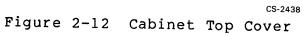

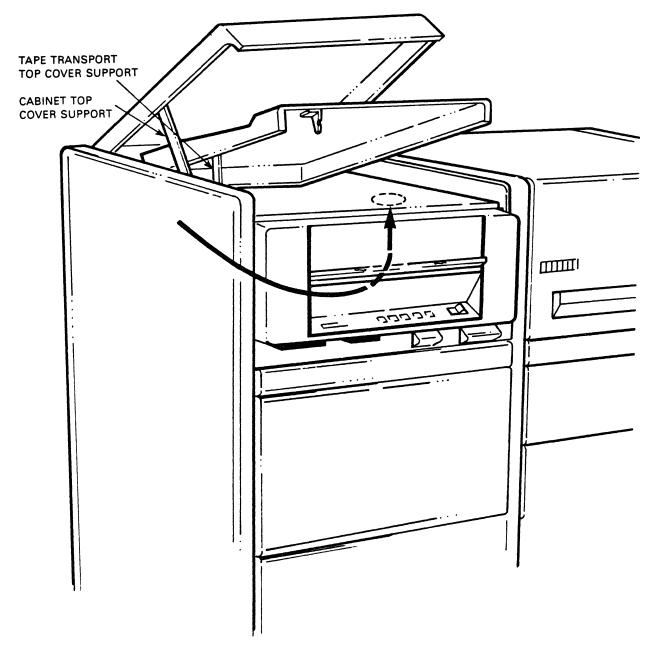

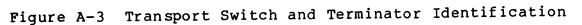

- Raise the top of the cabinet by grasping the handle on the top cover and lifting. When the top cover is raised far enough, the support arm latches to keep the cover up. (Refer to Figure 2-12.)

- 2. Raise the top cover of the tape transport unit by reaching in through the front door and pushing upward on the front of the top cover. Prop the cover up using the nylon support that hangs from the left side of the cover. (Refer to Figure 2-13.)

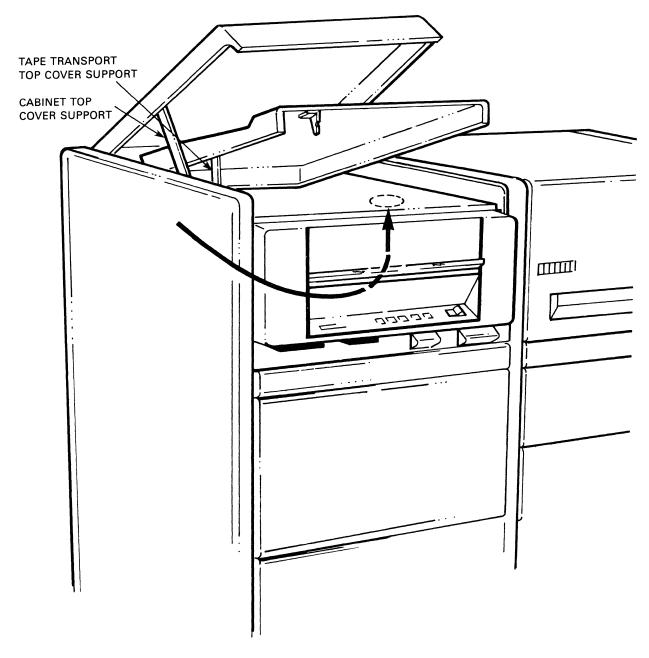

- 3. Refer to Figure 2-14. Gently move the tachometer assembly away from the takeup hub. Remove the foam cushion. Care-fully place the tachometer assembly back on the takeup hub.

- 4. Inspect and ensure that the tape path area is free of any foreign matter. With the cover still in the operator maintenance access position, proceed to Section 2.3.4.2.

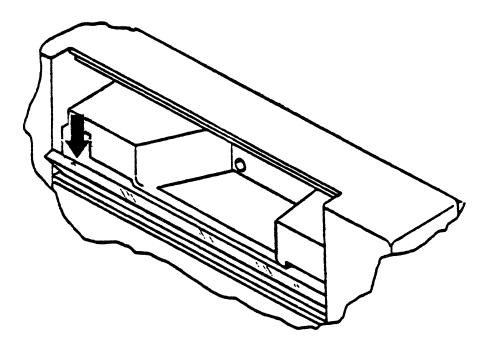

# 2.3.4.2 Removing the Bottom Foam Pieces

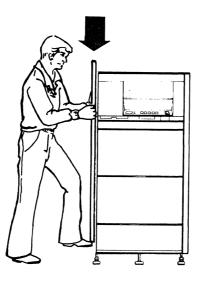

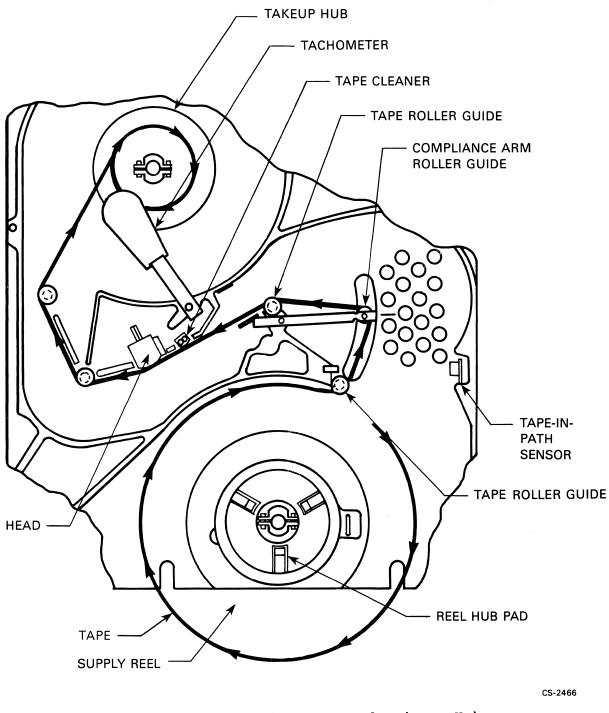

- Loosen the two spring-loaded captive screws, located on each side (as viewed from the top of the TSØ5 tape transport unit), that secure the TSØ5 unit to the top rail assembly. (See Figure 2-15.)

- 2. Lower the top cover of the tape transport unit.

- 3. With both hands, grasp the lower front of the TSØ5 unit and lift the entire assembly to its maximum upright position. (This engages the locking mechanism automatically.)

### WARNING

Keep hands clear of the corners of the tape unit while lifting. This is important to avoid brushing the mounting rails with your hands while lifting the unit.

CS-2444

Figure 2-13 Tape Transport Top Cover

Figure 2-14 Tachometer and Takeup Hub

Figure 2-15 Service Access Position

Carefully lower the TSØ5 unit approximately 2.5 centimeters (l.Ø inch). (This will activate the locking mechanism automatically.)

### WARNING

To eliminate the possibility of the tape unit dropping due to a failure in the locking mechanism, insert the supplied safety pin into the hole provided [2.5 centimeters (1.0 inch)] above the locking mechanism on the top plate supporting slide. Route the safety pin behind the supporting slide and across in front, and install it from left to right.

- 5. Release the drive/formatter module by pulling down on the two Ny-Lok fasteners that secure it to the bottom of the top plate assembly. When the Ny-Lok fasteners are released, carefully lower the drive/formatter module as far as it will go.

- 6. Remove the sheet and block of foam from the unit.

- 7. Place the TSØ5 unit back to the operating position by reversing steps 1 through 5.

- 8. Close the top cover of the tape unit and the top cover of the cabinet.

NOTE

To release the cabinet top cover support arm, it is necessary to raise the top cover slightly and move the top of the arm forward.

2.3.5 Connecting Line Power Before connecting the line power, perform the following checks:

- 1. Power switch on the front panel of the tape transport is in the  $\emptyset$  (OFF) position.

- Power controller voltage rating is correct for your system.

- 3. Power controller circuit breaker switches are in the OFF position.

- 4. Power controller LOCAL/REMOTE switch is in the LOCAL position.

With the switches in these positions, unwind the power cable and plug it into the receptacle.

### 2.4 TAPE TRANSPORT CHECKOUT

The tape transport is tested by itself before being cabled to the bus interface/controller module. This standalone testing is performed with the line power controlled locally at the cabinet power controller. After standalone operation has been verified, operation with the computer system is tested. At that point, the tape transport cabinet power is placed under the control of computer cabinet power controller by connecting the remote control cable. For the tests in this section, however, the remote control cable remains unconnected.

# 2.4.1 Power Up Test

- Switch the circuit breaker switches on the cabinet power to the ON position. Observe that the power controller pilot lamp lights. Close the cabinet rear door.

- On the tape transport front panel (Figure 2-16), press the power switch to the 1 (ON) position. Observe that all indicators light for approximately 2 seconds.

- 3. Observe that after 2 seconds all the indicators extinguish, and then the UNLOAD indicator lights.

If these indications have occurred, the tape transport unit has successfully completed the internal verification checks that it performs automatically at power up. If the indications were different, there is a problem. Refer to the <u>TSV05 Pocket Service</u> Guide or call your local Digital representative.

CS-2429

# 2.4.2 Tape Loading Test

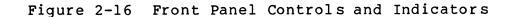

This test verifies the ability of the TSV05 subsystem to automatically load a tape. It requires a tape that is blank except for the beginning-of-tape (BOT) and end-of-tape (EOT) markers. Refer to Figure 2-17 and proceed as follows:

- 1. Ensure that the tape is wound completely onto the reel and that the end has been properly crimped.

- 2. Open the front panel door by gently pressing down on the top center area of the door.

- Hold the tape with the file-protect ring side down, and insert it into the transport unit, centering it on the hub.

- 4. Close the door.

### CAUTION

Both the tape transport top cover and the front panel door are locked when a tape is loaded. Any attempt to force open either the cover or the door before the tape is unloaded will result in mechanical damage to the locking mechanism.

- 5. Press the LOAD switch. This locks the cover and the door and begins the loading sequence.

- 6. Observe the LOAD indicator. It blinks while the tape is being loaded. After a maximum of 135 seconds, it stops blinking and remains lit. This indicates that the tape loading sequence is complete.

If the LOAD indicator does not stop blinking, or if the other indicators begin to blink, there is a problem. Unload the tape, check for a proper crimp, and retry the test. If the tape does not load, refer to the <u>TSV05</u> <u>Pocket Service Guide</u> or to the manual loading instructions in Appendix B.

Figure 2-17 Inserting Tape

### 2.4.3 Tape Movement Test

This test exercises the tape drive in both forward and reverse directions and at both high and low speeds.

NOTE

If you make an error and enter an illegal test sequence, or if you stop during the sequence and permit more than 2 seconds to pass before pressing the next switch in the sequence, the system aborts the test instruction and you must start the sequence from the beginning. An erroneous or aborted test instruction results in an expanding pattern of blinking.

- Start the test by pressing the front panel control switches in the following sequence:

- a. TEST

- b. ENTER

- c. UNLOAD

- d. UNLOAD

- e. ENTER

- 2. The tape should begin to move after step e.

- 3. Observe the indicators. If, over a period of 2 minutes, they change their blinking value substantially, there is a problem. If the blinking remains about the same, the test is progressing successfully.

- 4. After 2 minutes, terminate the test by pressing the TEST key. This causes the tape to rewind (which may take several minutes) and the LOAD indicator to light.

If problems are encountered, refer to the <u>TSV05 Pocket Service</u> <u>Guide</u>.

### 2.4.4 Tape Unloading Test

This test verifies the ability of the tape unit to unload the tape automatically.

- 1. Press the UNLOAD switch.

- Observe the UNLOAD indicator. It blinks to indicate that the tape is being unloaded. When the unloading process is complete, the UNLOAD indicator lights continuously, and the front panel door and top cover are unlocked. This should take a maximum of 15 seconds.

- 3. Open the front panel door and lift the tape reel out of the tape transport.

- 4. Close the door.

- 5. Press the tape transport power switch to the  $\emptyset$  (OFF) position.

- 6. Switch the circuit breaker switches on the cabinet power controller to the OFF position.

### 2.5 BUS INTERFACE/CONTROLLER MODULE INSTALLATION

The M7196 bus interface/controller module plugs into a quad slot in the LSI-11 backplane. It connects to the LSI-11 bus on the A and B sets of edge connectors (module fingers). It is shipped with the DIP switches set for an interrupt vector of 224 and for addresses of 772520 and 772522. If your system already uses any of these addresses, the M7196 module must be switched to other addresses. Refer to Appendix A for information on switching the DIP switchpacks on the M7196 module. Refer to the <u>Microcomputers</u> and <u>Memories Handbook</u> or your system configurator for guidance in selecting new addresses.

For guidance in choosing the best backplane slot in which to install the M7196 module, refer to your system documentation or to the Microcomputers and Memories Handbook.

Install the M7196 module as follows:

- Test the computer system to verify that it is functioning properly.

- 2. Power down the computer system.

- 3. Remove the cover to gain access to the backplane. (Which panel must be removed depends on which system you have. Earlier systems accept modules in the front, while in more recent models the modules are inserted in the back. Refer to your system documentation.)

- 4. Insert the module into the LSI-11 backplane. Do not fully seat the module until the cables have been installed.

# 2.6 CABLE INSTALLATION

Cable installation involves connecting the M7196 module to the tape transport unit and connecting the tape transport cabinet power controller to the computer cabinet power controller.

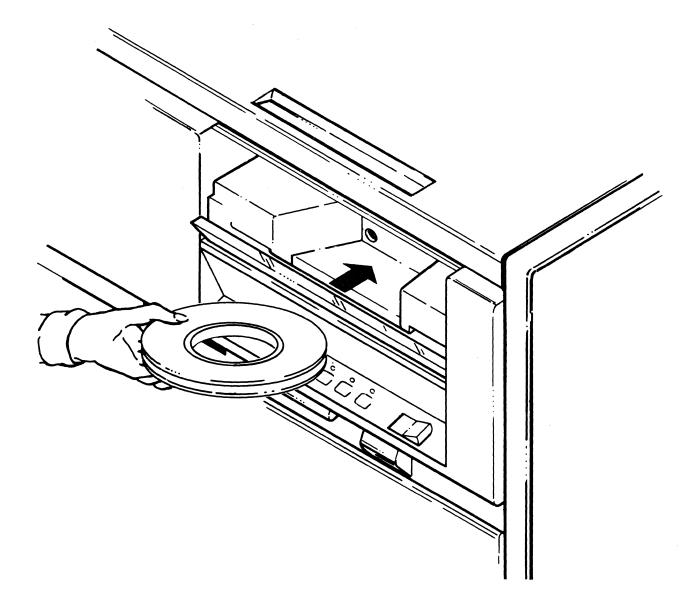

## 2.6.1 M7196 Module and Tape Transport Interconnection

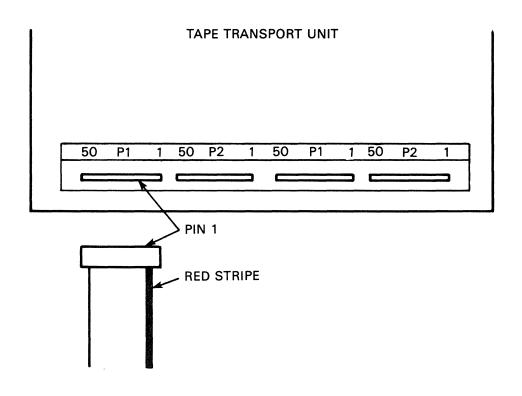

Each of the two flat interconnection cables has a large connector on one end and a small connector on the other end. The large connectors go to the tape transport unit and the small connectors to the M7196 module. Refer to Figure 2-18 and proceed as follows:

- Take a cable and position it so that pin 1 of the smaller, "low profile" connector lines up with pin 1 of connector J1 on the M7196 module. Pin 1 on the cable connector is indicated by a red stripe on the cable.

- 2. Gently push the cable connector into the Jl module connector until it is seated.

- 3. Route the cable to the rear of the cabinet. Cable routing depends on the model and configuration of the computer system, however, try to avoid blocking ventilation or running the cable where it may get caught on other equipment when a chassis is pulled out. Refer to drawing UA-TSV05-B for typical cable routing.

- 4. Pass the cable through the open side of the computer cabinet and into the tape transport cabinet. Do not route the cables outside the cabinetry.

- 5. Refer to Figure 2-19. Line up pin 1 of the cable connector with pin 1 of connector Pl on the tape transport unit. There are two sets of connectors on the back of the tape transport unit. The TSV05 subsystem uses the left-hand set of connectors.

- 6. Gently press the cable connector onto the Pl edge connector in the back of the tape transport cabinet.

- Repeat this procedure to cable J2 of the M7196 module to P2 of the tape transport unit. Ensure that pin 1 of J2 connects to pin 1 of P2.

- 8. After both interconnection cables have been installed, fully seat the module.

CS-2447

Figure 2-18 Cabling the M7196 Module

Figure 2-19 Cabling the Tape Transport

### 2.6.2 Power Controller Interconnection

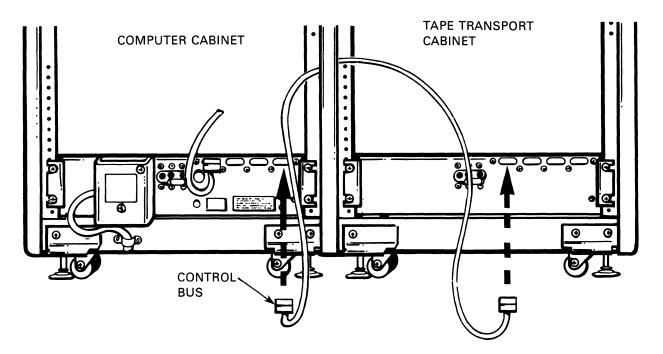

The power controllers in the two cabinets are to be interconnected by a remote control cable. This enables the computer cabinet power to switch on the tape transport cabinet power automatically whenever the computer is powered up.

The remote control cable, part number 7008288-8F, has a three-pin connector on each end. The cable connectors are the same, and they are keyed to plug in only one way. Refer to Figure 2-20 and install the remote control cable as follows:

- In the computer cabinet, plug one end of the cable into the power controller connector labeled DEC POWER CONTROL BUS.

- Route the remote control cable through the open side of the computer cabinet and into the tape transport cabinet. Do not route the cable outside the cabinetry.

- 3. In the tape transport cabinet, plug the cable into the power controller connector labeled DEC POWER CONTROL BUS.

- 4. Place the LOCAL/REMOTE switch in the REMOTE position.

- 5. Switch the circuit breaker switches to the ON position.

The tape transport cabinet power is now fully interconnected with the computer cabinet.

Figure 2-20 Remote Power Control Connections

CS-2434

# 2.7 TSVØ5 SUBSYSTEM CHECKOUT

The TSV05 subsystem is tested by checking the M7196 LED indicators and voltage supply, and by running the diagnostic programs listed in Table 2-2. These programs are available on the XXDP+ diagnostic software package that is shipped with the computer system. If your system is an earlier model and has the XXDP package instead of the XXDP+, contact your local Digital representative for ordering information.

# 2.7.1 Power Up Checks

- 1. Set the power switch on the tape transport unit to the ON position.

- 2. Switch on the computer system power and observe that the tape unit powers up with the system.

- 3. After a few seconds, all the tape unit indicators should be extinguished except for the the UNLOAD indicator.

- 4. Verify that the +5 V power to the M7196 module is within specification. Typically, the additional load of the M7196 module lowers the power supply voltage slightly. Adjust if necessary.

- 5. On the M7196 module, verify that the center LED (D2) is blinking. This indicates that the M7196 module self-test diagnostics are running. If other indications occur, there is a problem. Refer to the <u>TSV05 Pocket Service</u> <u>Guide</u> or contact your local Digital representative.

- 6. Replace the access panel on the computer and close the rear doors of the cabinets.

| Program Title           | File Name |  |

|-------------------------|-----------|--|

| Logic Test              | CVTSAA    |  |

| Advanced Logic Test     | CVTSBA    |  |

| Transport Test          | CVTSCA    |  |

| Advanced Transport Test | CVTSDA    |  |

| Data Reliability Test   | CVTSEA    |  |

| DEC-X11                 | XTSAAØ    |  |

Table 2-2 TSV05 Subsystem Diagnostics

# 2.7.2 System Setup

- To prevent erroneous error indications, ensure the tape transport is clean and the blank tape is of known good quality.

- 2. Load the blank tape into the tape transport by:

- a. Opening the front panel access door.

- b. Inserting the tape reel, with the file-protect ring side down, and centering it on the hub.

- c. Closing the door.

- d. Pressing the LOAD switch.

- e. Waiting for the LOAD indicator to stop blinking and stay on continuously.

- f. Pressing the ON-LINE switch.

- 3. Load the computer system diagnostic diskpack or floppy.

- 4. Before running the tape subsystem diagnostics, run the system exerciser or diagnostics to verify that the computer is operating properly. For instructions on running the computer system tests, refer to the documentation for the system.

### NOTE

The logic test and the advanced logic test (CVTSAA and CVTSBA) do not require a tape to be loaded in order to run. The other diagnostics, however, require the tape to be loaded and the tape subsystem to be ON-LINE.

### 2.7.3 TSVØ5 Logic Test

This program tests the logic on the M7196 bus interface/controller module. It checks the microprocessor, RAM, and various registers. It verifies that the computer can move data out to the module and receive status in from the module. After you have booted the XXDP+ disk (DL, DX, or DY) and answered the questions about the date, the processor, and the power line frequency, start the logic test as follows (operator responses are underlined):

### .R VTSA?? <CR>

The system responds with a display similar to the following: