# **TS11 Subsystem**

**Technical Manual**

Prepared by Educational Services of Digital Equipment Corporation 1st Edition, October 1980 2nd Edition, January 1983 3rd Edition, January 1984

Copyright © 1980, 1983, 1984 by Digital Equipment Corporation. All Rights Reserved. Printed in U.S.A.

The reproduction of this material, in part or whole, is strictly prohibited. For copy information, contact the Educational Services Department, Digital Equipment Corporation, Maynard, Massachusetts 01754.

The information in this document is subject to change without notice. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

This equipment generates, uses, and may emit radio frequency. The equipment has been type tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC rules, which are designed to provide reasonable protection against such radio frequency interference. Operation of this equipment in a residential area may cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

Faston<sup>™</sup> and Mate-N-Lok<sup>™</sup> are trademarks of AMP, Inc.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts.

| digital      | DECwriter    | RSTS           |

|--------------|--------------|----------------|

| DEC          | DIBOL        | RSX            |

| DECsystem-10 | MASSBUS      | UNIBUS         |

| DECSYSTEM-20 | PDP          | VAX            |

| DECUS        | P/OS         | VMS            |

| DECmate      | Professional | VT             |

| DECnet       | Rainbow      | Work Processor |

|              |              |                |

# **CONTENTS**

# CHAPTER 1 GENERAL INFORMATION

| 1.1   | Introduction 1-1                  |

|-------|-----------------------------------|

| 1.2   | Subsystem Overview 1-2            |

| 1.3   | Physical Description 1-3          |

| 1.3.1 | Unibus Interface                  |

| 1.3.2 | Transport                         |

| 1.4   | System Functional Description 1-6 |

| 1.5   | Unit Specifications 1-10          |

| 1.6   | Applicable Documents 1-13         |

| 1.7   | Available Options 1-14            |

# CHAPTER 2 INSTALLATION

| 2.1     | Site Planning and Considerations       |

|---------|----------------------------------------|

| 2.1.1   | Space Requirements                     |

| 2.1.2   | Power Requirements                     |

| 2.1.3   | Floor Loading                          |

| 2.1.4   | Installation Constraints               |

| 2.1.5   | Fire and Safety Precautions 2-4        |

| 2.1.6   | Temperature                            |

| 2.1.7   | Relative Humidity                      |

| 2.1.8   | Heat Dissipation                       |

| 2.1.9   | Acoustics                              |

| 2.1.10  | Altitude                               |

| 2.1.11  | Radiated Emissions 2-5                 |

| 2.1.12  | Required Tools                         |

| 2.2     | Unpacking                              |

| 2.2.1   | Rackmount Option                       |

| 2.2.2   | H960 Cabinet Unpacking 2-6             |

| 2.2.3   | H9602 Cabinet Unpacking 2-8            |

| 2.2.4   | H9646 Cabinet Unpacking 2-8            |

| 2.3     | Inspection                             |

| 2.4     | Transport Installation and Cabling 2-9 |

| 2.4.1   | Rackmount Installation 2-9             |

| 2.4.2   | H960 Cabinet Installation 2-10         |

| 2.4.3   | H9602 Cabinet Installation             |

| 2.4.3.1 | Cabinet Dissassembly 2-11              |

| 2.4.3.2 | Caster Locks                           |

| 2.4.3.3 | Cabinet Leveling 2-13                  |

| 2.4.3.4 | Bolting Cabinets Together 2-13         |

|         | -                                      |

| 2.4.3.5 | Cabinet Reassembly                           | -13 |

|---------|----------------------------------------------|-----|

| 2.4.4   | H9646 Cabinet Installation 2-                | -14 |

| 2.4.4.1 | Rear Door Removal                            | -14 |

| 2.4.4.2 | End Panel Removal                            | -14 |

| 2.4.4.3 | Leveling Feet Installation                   | -14 |

| 2.4.4.4 | Cabinet Leveling                             |     |

| 2.4.4.5 | Cabinet Stabilizers                          |     |

| 2.4.4.6 | Bolting Cabinets Together 2-                 | -15 |

| 2.5     | TS11 Interface Installation                  |     |

| 2.5.1   | Cabling                                      | -18 |

| 2.6     | Configuration Guidelines 2-                  | -19 |

| 2.7     | Acceptance Testing                           | -20 |

| 2.7.1   | TS11 Off-Line Checkout 2-                    |     |

| 2.7.2   | Customer Confidence Check (Optional) 2-      | -20 |

| 2.7.3   | Corrective Maintenance Diagnostics (On-Line) | -20 |

# CHAPTER 3 USER INFORMATION

| 3.1   | Customer Responsibilities             | 3-1 |

|-------|---------------------------------------|-----|

| 3.2   | Care of Magnetic Tape                 | 3-1 |

| 3.3   | Customer Preventive Maintenance       | 3-2 |

| 3.3.1 | Preventive Maintenance                | 3-2 |

| 3.3.2 | Magnetic Tape Transport Cleaning Kit  | 3-2 |

| 3.3.3 | Cleaning the TS11 Subsystem Transport | 3-3 |

| 3.3.4 | Ordering                              | 3-4 |

# CHAPTER 4 OPERATION

| 4.1     | Controls and Indicators               | 4-1         |

|---------|---------------------------------------|-------------|

| 4.2     | Operating Procedures                  |             |

| 4.2.1   | Application of Power                  | 4-4         |

| 4.2.2   | Loading and Threading Tape            | <b>1</b> -4 |

| 4.2.3   | Unloading Tape                        |             |

| 4.2.3.1 | Tape Loaded, Not at BOT               |             |

| 4.2.3.2 | Tape Loaded, at BOT                   | 1-6         |

| 4.2.4   | Restart After Power Failure           |             |

| 4.2.5   | Restart After Fail-Safe               | 1-6         |

| 4.3     | Operator Troubleshooting              | 1-6         |

| 4.4     | Customer Confidence Check             |             |

| 4.4.1   | Running the Customer Confidence Check | 1-7         |

# CHAPTER 5 PROGRAMMING

| 5.1     | TS11 Registers                                                 | 5-1 |

|---------|----------------------------------------------------------------|-----|

| 5.1.1   | TSBA (Unibus Address Register – Base Address – Read Only)      |     |

| 5.1.2   | TSDB (Unibus Data Buffer Register - Base Address - Write Only) | 5-3 |

| 5.1.2.1 | Normal Operation                                               |     |

| 5.1.2.2 | Data Wraparound Internal to the M7982 (Diagnostic Mode)        |     |

| 5.1.2.3 | Data Wraparound External with Transport                        | 5-4 |

| 5.1.3   | TSSR (Status Register – Base Address +2 – Read/Write)          | 5-4 |

| 5.1.4   | XST (Extended Status Registers)                                | 5-8 |

| 5.1.5   | TS11 Register Summary                                          |     |

| 5.2     | Packet Processing                                              |     |

| 5.2.1   | Command Packet/Header Word                                     |     |

| 5.2.2   | Command Packet Examples 5-23       |

|---------|------------------------------------|

| 5.2.2.1 | Get Status Command 5-23            |

| 5.2.2.2 | Read Command 5-24                  |

| 5.2.2.3 | Write Characteristics Command 5-25 |

| 5.2.2.4 | Write Command                      |

| 5.2.2.5 | Position Command 5-27              |

| 5.2.2.6 | Format Command 5-28                |

| 5.2.2.7 | Control Command 5-28               |

| 5.2.2.8 | Initialize Command 5-28            |

| 5.2.3   | Message Packet Header Word 5-28    |

| 5.2.4   | Message Packet Example 5-31        |

| 5.3     | Operational Information            |

| 5.3.1   | Unibus Registers                   |

| 5.3.2   | Command and Message Packets 5-32   |

| 5.3.3   | Special Conditions and Errors 5-32 |

| 5.3.4   | Status Error Handling Notes 5-34   |

| 5.4     | Operational Differences            |

# CHAPTER 6 THEORY OF OPERATION

| 6.1      | Introduction                           |

|----------|----------------------------------------|

| 6.2      | System Description 6-3                 |

| 6.2.1    | Modules                                |

| 6.2.1.1  | M7982, Unibus to Serial Bus Controller |

| 6.2.1.2  | G057, TS04 Read Preamplifiers          |

| 6.2.1.3  | G157, TS04 Read Amplifiers             |

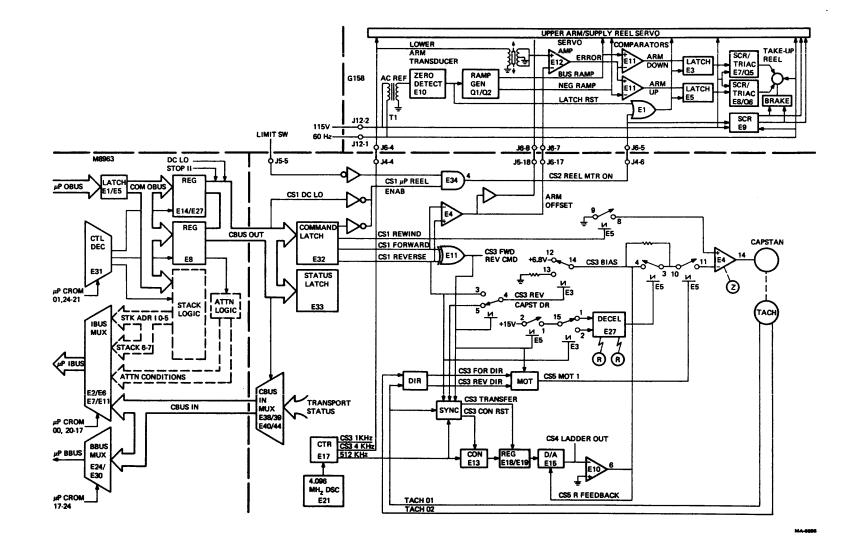

| 6.2.1.4  | G158, Reel Servo                       |

| 6.2.1.5  | G159, Capstan Servo 6-3                |

| 6.2.1.6  | M8922, Branch Logic and VCO Control    |

| 6.2.1.7  | M8923, Read Control 6-3                |

| 6.2.1.8  | M8924, PE Formatter 6-3                |

| 6.2.1.9  | M8929, Write Control                   |

| 6.2.1.10 | M8962, Microprocessor Board 1          |

| 6.2.1.11 | M8963, Microprocessor Board 2 6-3      |

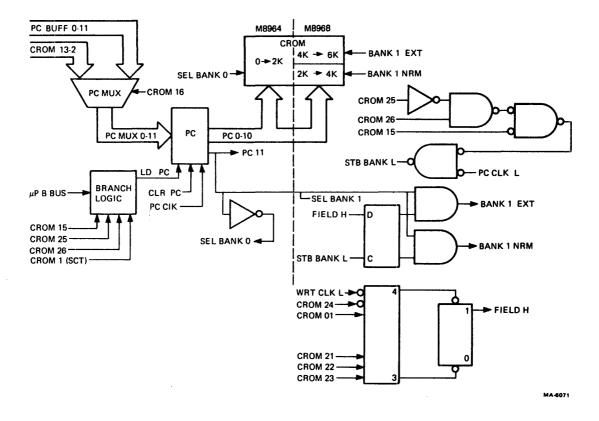

| 6.2.1.12 | M8964, ROM Board                       |

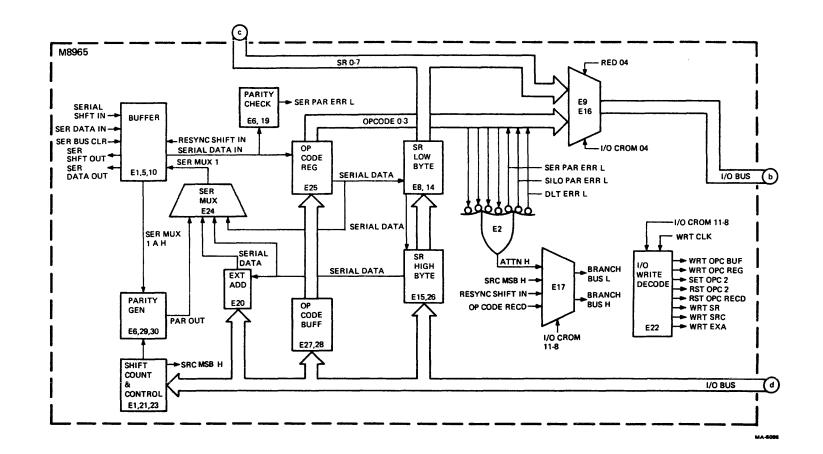

| 6.2.1.13 | M8965, I/O Section 1 6-10              |

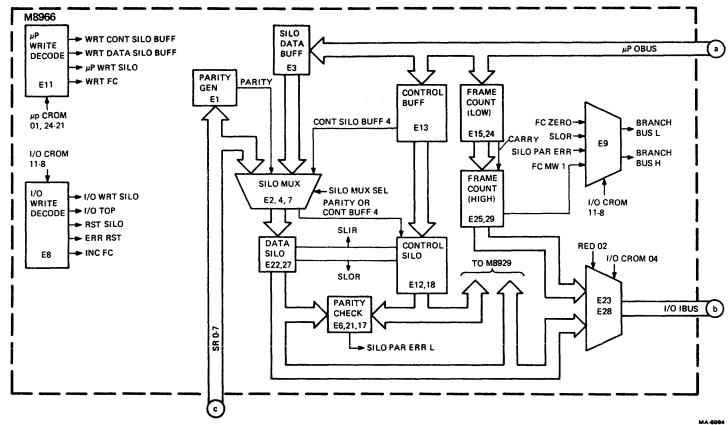

| 6.2.1.14 | M8966, I/O Section 2 6-10              |

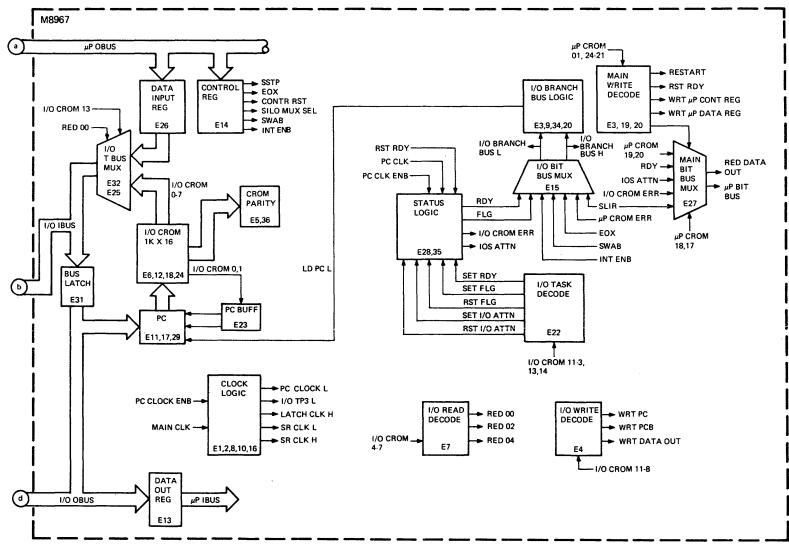

| 6.2.1.15 | M8967, I/O Section 3 6-10              |

| 6.2.1.16 | M8968, ROM Extension Board 6-10        |

| 6.2.2    | Buses and Major Interconnecting Lines  |

| 6.2.2.1  | Unibus                                 |

| 6.2.2.2  | Serial Bus                             |

| 6.2.2.3  | Shift Register Lines                   |

| 6.2.2.4  | Input/Output BBUS 6-11                 |

| 6.2.2.5  | Input/Output IBUS 6-11                 |

| 6.2.2.6  | Input/Output OBUS 6-11                 |

| 6.2.2.7  | Main Microprocessor BBUS               |

| 6.2.2.8  | Main Microprocessor IBUS 6-11          |

| 6.2.2.9  | Main Microprocessor OBUS 6-11          |

| 6.2.2.10 | Main Microprocessor CROM 6-11          |

| 6.2.2.11 | COM OBUS                               |

| 6.2.2.12 | Capstan Output Bus 6-11                |

| 6.2.2.13 | Capstan Input Bus 6-11                 |

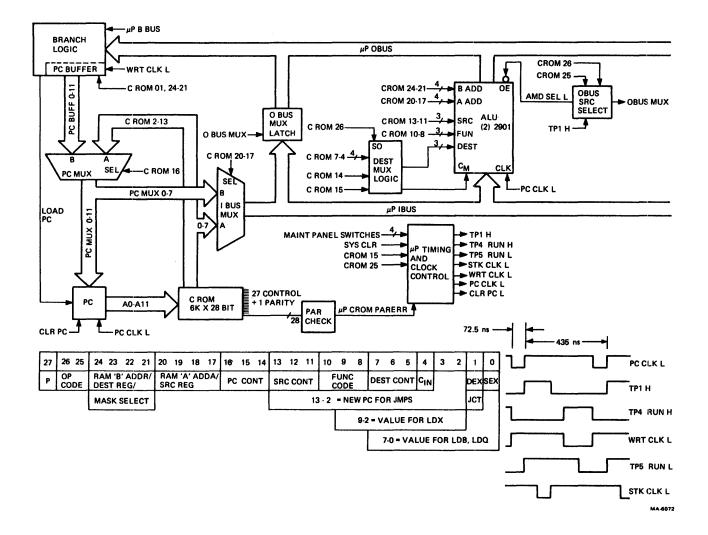

| 6.3      | Control Microprocessor                 |

| 6.3.1   | Microprocessor Basic Description             |              |        |

|---------|----------------------------------------------|--------------|--------|

| 6.3.2   | Microprocessor Functional Description        |              |        |

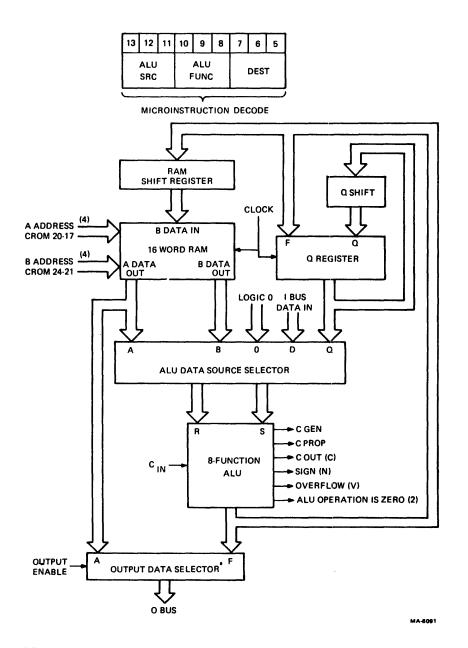

| 6.3.2.1 | 2901                                         | 6-15         | 10 mar |

| 6.3.2.2 | CROM Organization                            | 6-17         |        |

| 6.3.2.3 | Basic Instructions                           | 6-21         |        |

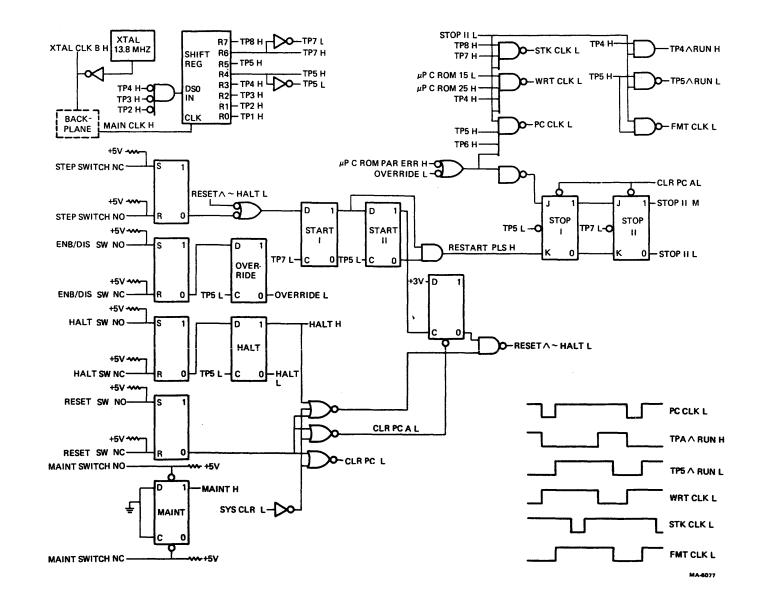

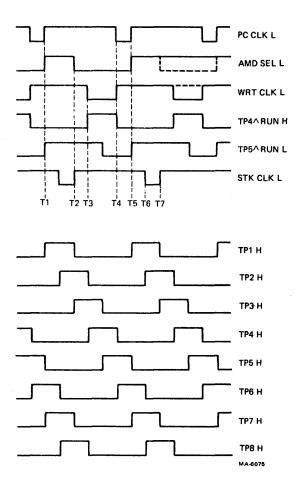

| 6.3.2.4 | Clock Generation and Control                 | 6-26         |        |

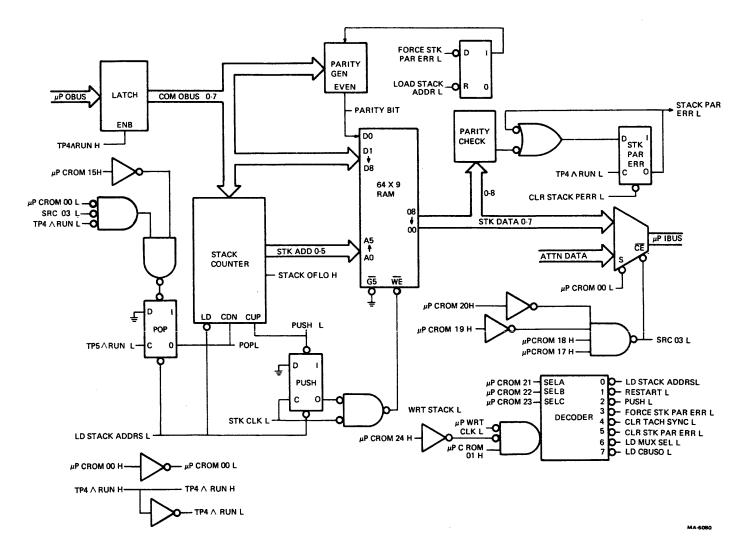

| 6.3.2.5 | Stack Operation                              | 6-30         |        |

| 6.4     | Input/Output Functional Description          |              |        |

| 6.4.1   | Serial Bus                                   |              |        |

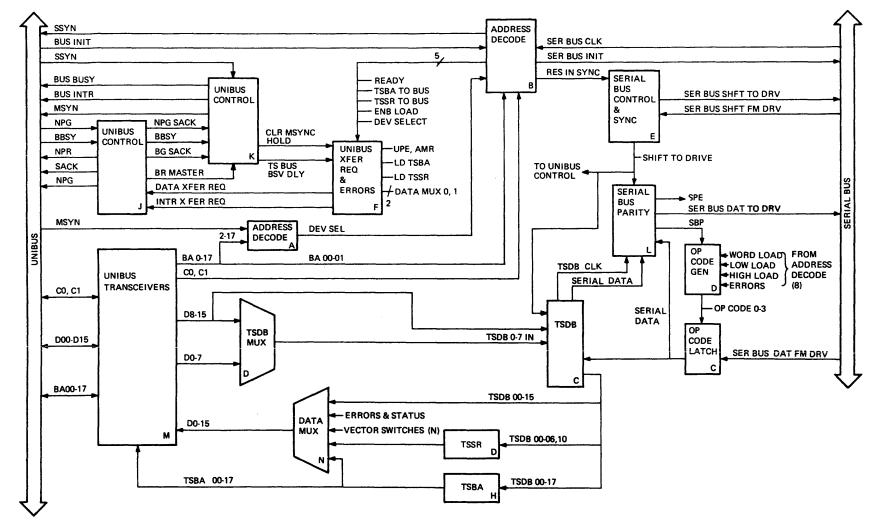

| 6.4.2   | M7982 – Unibus to Serial Bus Controller      |              |        |

| 6.4.2.1 | M7982 Data Path                              |              |        |

| 6.4.2.2 | M7982 Operation                              |              |        |

| 6.4.2.3 | M7982 Op Codes                               |              |        |

| 6.4.3   | Drive I/O                                    |              |        |

| 6.4.3.1 | I/O Registers                                |              |        |

| 6.4.3.2 |                                              |              |        |

|         | Data Paths                                   |              |        |

| 6.4.3.3 | Drive I/O Operation                          |              | _      |

| 6.5     | Tape Handling                                |              |        |

| 6.5.1   | Overview                                     |              |        |

| 6.5.2   | Tape Handling Commands and Status            |              |        |

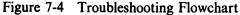

| 6.5.3   | Capstan Motion                               |              |        |

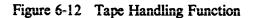

| 6.5.3.1 | Motion and Direction Detection               |              |        |

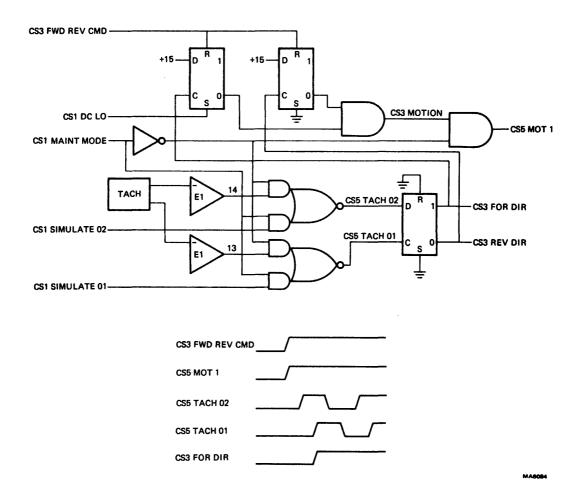

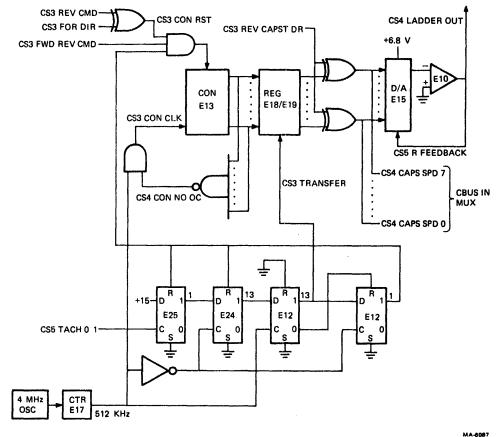

| 6.5.3.2 | Speed Regulation                             |              |        |

| 6.5.3.3 | Capstan Drive                                |              |        |

| 6.5.3.4 | Deceleration                                 | 6-56         |        |

| 6.5.4   | Tape Tension                                 | 6-59         |        |

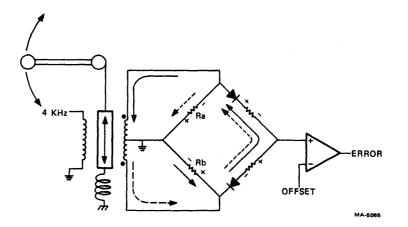

| 6.5.4.1 | Tension Arm Error Signal                     | 6-60         |        |

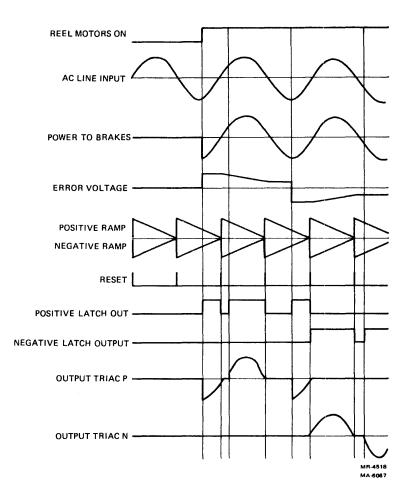

| 6.5.4.2 | Ramp Generation                              | 6-63         |        |

| 6.5.4.3 | Reel Motor Control                           |              |        |

| 6.5.4.4 | Reel Motor On                                |              |        |

| 6.6     | Tape Data Handling                           |              |        |

| 6.6.1   | Read Function                                |              |        |

| 6.6.1.1 | Read Preamplifiers                           |              |        |

| 6.6.1.2 | Read Amplifiers                              |              |        |

| 6.6.1.3 | Read Control                                 |              |        |

| 6.6.1.4 | Outputs                                      |              |        |

| 6.6.2   | PE Formatter                                 |              |        |

| 6.6.2.1 | VCO Operation                                |              |        |

| 6.6.2.2 | Data Detection                               |              |        |

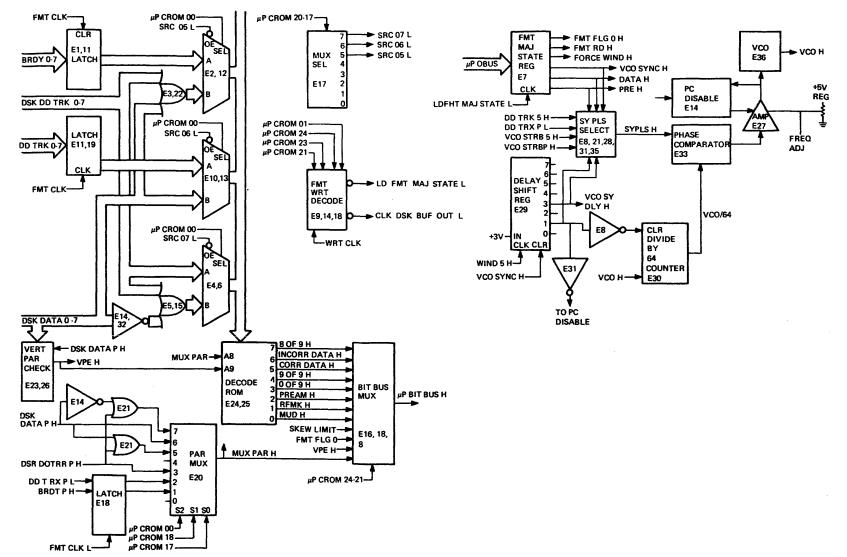

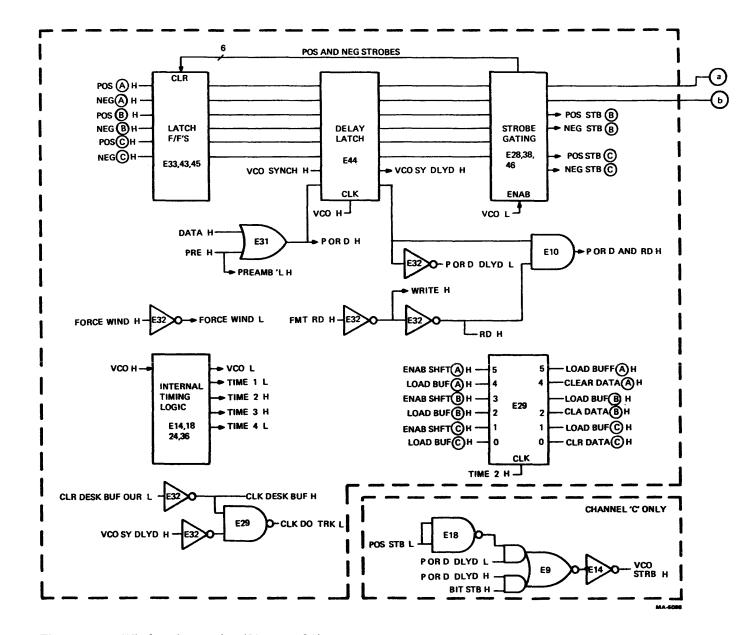

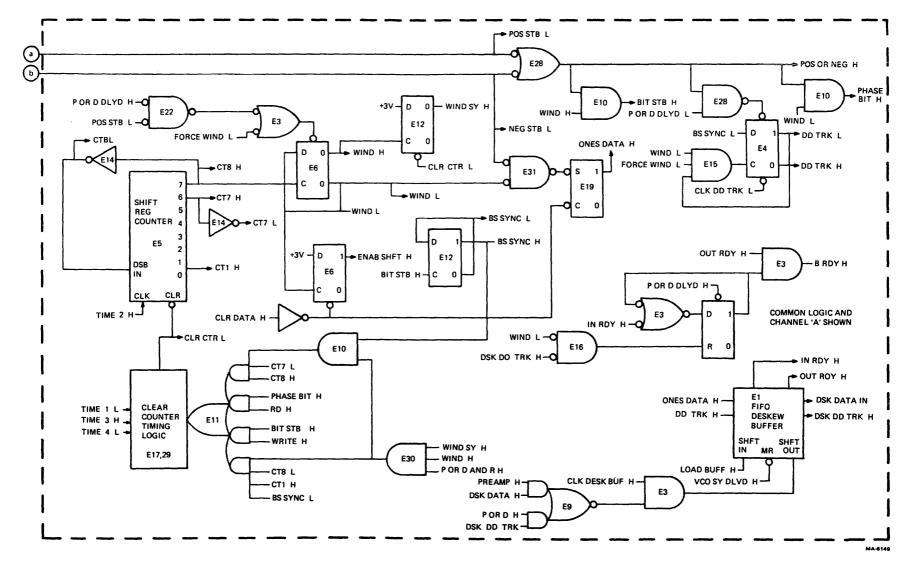

| 6.6.2.3 | Formatter Multiplexers and ROM Look-Up Table | 6_72<br>5_78 |        |

| 6.6.2.4 | Read Operation                               |              |        |

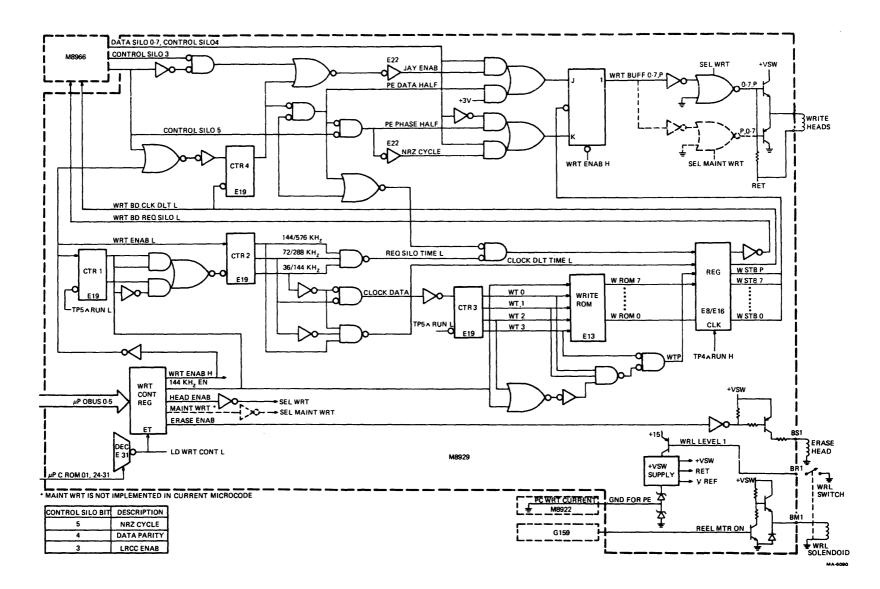

| 6.6.3   | Write Function                               |              |        |

| 6.6.3.1 | Control and Data Silo                        |              |        |

| 6.6.3.2 |                                              |              |        |

| 6.6.3.3 | Write Control                                |              |        |

| 6.6.3.4 | Data Write Operation                         | 0-03<br>6 01 |        |

| 6.6.3.5 | IDB and Tape Mark Write                      | 0-04         |        |

|         | Read After Write                             |              |        |

| 6.7     | Status Reporting                             | D-87         |        |

# CHAPTER 7 SERVICING

| 7.1      | Scope                                                 | . 7-1  |

|----------|-------------------------------------------------------|--------|

| 7.2      | Maintenance Philosophy                                |        |

| 7.3      | Special Tools                                         |        |

| 7.4      | Diagnostics                                           |        |

| 7.4.1    | Initialization and In-Line Diagnostics                |        |

| 7.4.1.1  | UTSTM                                                 |        |

| 7.4.1.2  | STAKM                                                 |        |

| 7.4.1.3  | IOTSM                                                 |        |

| 7.4.1.4  | CATSM                                                 |        |

| 7.4.1.5  | PETSM                                                 |        |

| 7.4.2    | Off-Line Diagnostics                                  |        |

| 7.4.2.1  | Customer Confidence Test                              | • • •  |

| 7.4.2.2  | Maintenance Mode Diagnostics                          |        |

| 7.4.3    | On-Line Diagnostics                                   |        |

| 7.4.3.1  | PDP-11 Based Diagnostics                              |        |

| 7.4.3.2  | VAY Based Diagnostics                                 | . 1-21 |

|          | VAX-Based Diagnostics                                 | . 1-22 |

| 7.4.4    | Failure Description                                   |        |

| 7.4.4.1  | Fatal Microprocessor Errors                           | . 1-22 |

| 7.4.4.2  | Nonfatal Microprocessor Errors                        |        |

| 7.4.4.3  | Off-Line Test Errors                                  |        |

| 7.4.4.4  | On-Line Failures                                      |        |

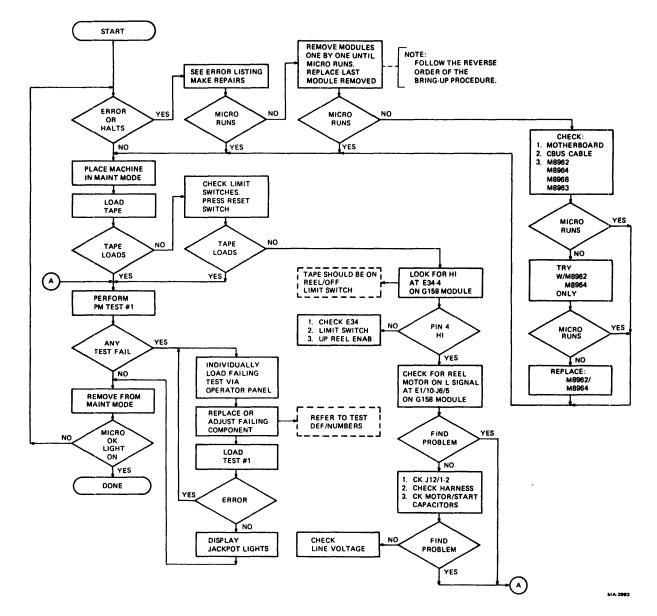

| 7.5      | Troubleshooting                                       |        |

| 7.5.1    | Maintenance Mode Operation                            |        |

| 7.5.2    | Manual Switch Test (Test 57)                          |        |

| 7.5.3    | Bring-Up Procedure                                    |        |

| 7.5.4    | Data Track Card Identifier                            |        |

| 7.6      | Checks and Adjustments                                | . 7-37 |

| 7.6.1    | Power Supply Checks and Adjustment                    |        |

| 7.6.2    | Mechanical Adjustments                                |        |

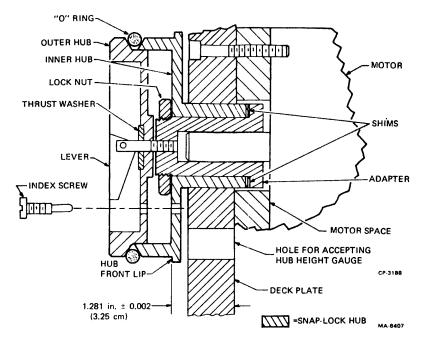

| 7.6.2.1  | Snap Lock Hub Height Check and Adjustment             | . 7-39 |

| 7.6.2.2  | Fixed Reel Hub Height Adjustment                      | . 7-41 |

| 7.6.2.3  | Tension Arm Transducer Coarse Adjustment              | . 7-42 |

| 7.6.2.4  | Tension Arm Transducer Fine Adjustment                | . 7-42 |

| 7.6.2.5  | Reel Motor and Brake Check                            | . 7-43 |

| 7.6.2.6  | Tape Tension Coarse Adjustment                        | . 7-43 |

| 7.6.2.7  | Tape Tension Fine Adjustment                          |        |

| 7.6.2.8  | Tape Path Alignment                                   | . 7-44 |

| 7.6.2.9  | BOT/EOT Adjustment                                    |        |

| 7.6.2.10 | Limit Switches Check                                  |        |

| 7.6.2.11 | Write Lock Assembly Adjustment                        |        |

| 7.6.3    | Electrical Checks and Adjustments                     |        |

| 7.6.3.1  | Capstan Null Adjustment                               |        |

| 7.6.3.2  | Capstan Tachometer Alignment (Duty Cycle and Phasing) | . 7-49 |

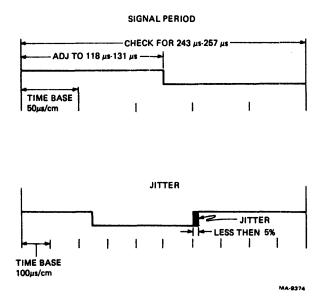

| 7.6.3.3  | Capstan Speed Check                                   |        |

| 7.6.3.4  | Capstan Forward and Reverse Deceleration Adjustment   | . 7-53 |

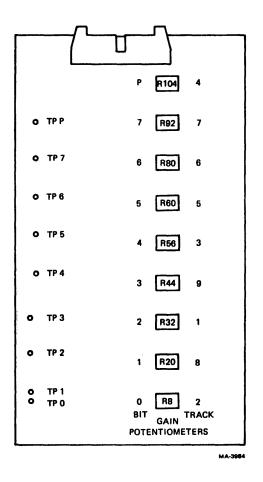

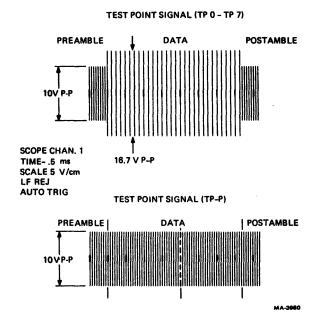

| 7.6.3.5  | Read Preamplifiers                                    |        |

|          | •                                                     |        |

•

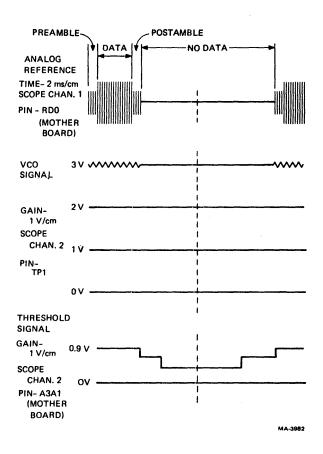

| 7.6.3.6  | VCO Adjustment                       |

|----------|--------------------------------------|

| 7.6.3.7  | Threshold Adjustment 7-55            |

| 7.6.3.8  | Skew Meter Ådjustment 7-56           |

| 7.6.3.9  | Head Skew Check and Adjustment 7-56  |

| 7.7      | Removal and Replacement Procedures   |

| 7.7.1    | Module Removal and Replacement       |

| 7.7.1.1  | Double-Height Module                 |

| 7.7.1.2  | G158 Reel Servo Board 7-60           |

| 7.7.1.3  | G159 Capstan Servo Board 7-60        |

| 7.7.1.4  | G057 Read Amplifier Board 7-60       |

| 7.7.2    | Snap Lock Hub Assembly (Supply Reel) |

| 7.7.2.1  | Removal                              |

| 7.7.2.2  | Replacement                          |

| 7.7.2.3  | Rebuilding                           |

| 7.7.3    | Take-Up Reel                         |

| 7.7.3.1  | Removal                              |

| 7.7.3.2  | Replacement                          |

| 7.7.4    | Capstan Wheel                        |

| 7.7.5    | Capstan Motor and Tachometer         |

| 7.7.6    | Lower Roller Guide                   |

| 7.7.7    | Headplate Assembly                   |

| 7.7.8    | BOT/EOT Sensor Assembly              |

| 7.7.9    | Lower Reel Motor Assembly            |

| 7.7.10   | Upper Reel Motor Assembly            |

| 7.7.11   | TS11 Board                           |

| 7.7.11.1 | Removal                              |

| 7.7.11.2 | Replacement                          |

| 7.7.12   | Tension Arm                          |

| 7.7.12.1 | Removal                              |

| 7.7.12.2 | Replacement                          |

| 7.7.13   | Tension Arm Transducer               |

| 7.7.13.1 | Removal                              |

| 7.7.13.2 | Replacement                          |

| 7.7.14   | Write Lock Assembly 7-70             |

| 7.7.15   | Reel Motor Capacitors 7-71           |

| 7.7.16   | Limit Switches                       |

| 7.7.17   | Operator Control Panel Bulbs 7-72    |

# FIGURES

| 1-1 | TS11 Subsystem Configurations                                      | 1-2  |

|-----|--------------------------------------------------------------------|------|

| 1-2 | TS11 Subsystem Major Assemblies                                    |      |

| 1-3 | Transport Assemblies (Front View)                                  |      |

| 1-4 | Transport Assemblies (Rear View)                                   |      |

| 1-5 | TS11 Simplified Block Diagram                                      |      |

| 1-6 | Command Packets                                                    |      |

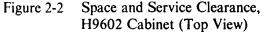

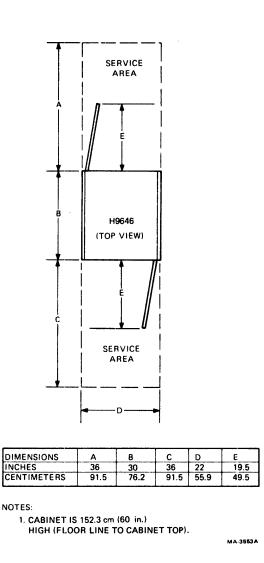

| 2-1 | Space and Service Clearance, H960 Cabinet and Rackmount (Top View) | 2-1  |

| 2-2 | Space and Service Clearance, H9602 Cabinet (Top View)              |      |

| 2-3 | Space and Service Clearance, H9646 Cabinet (Top View)              |      |

| 2-4 | H960 Cabinet Installation                                          |      |

| 2-5 | H9602 Cabinet Installation                                         |      |

| 2-6 | H960 Cabinet Filler Strips                                         | 2-10 |

| 2-7 | H9602 Stabilizer Leg and Leveler Feet Locations                    | 2-11 |

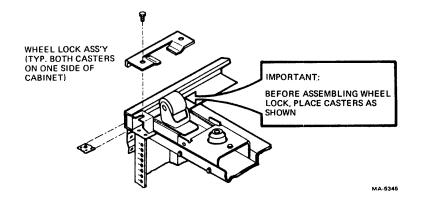

| 2-8 | Caster Lock Assembly                                               |      |

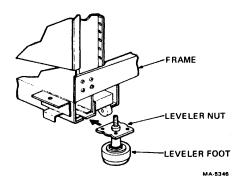

| H9646 Leveler Foot Locations                               | 2-14 |

|------------------------------------------------------------|------|

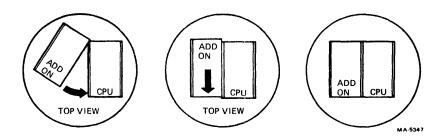

| H9646 Add-On Positioning                                   | 2-15 |

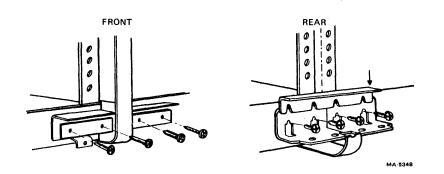

| H9646 Interconnecting Bars                                 | 2-15 |

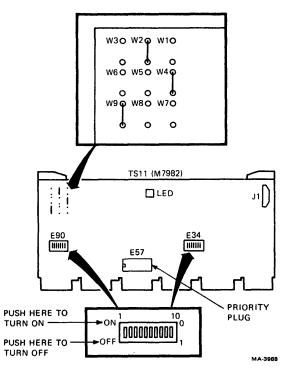

| M7982 Interface Module                                     | 2-16 |

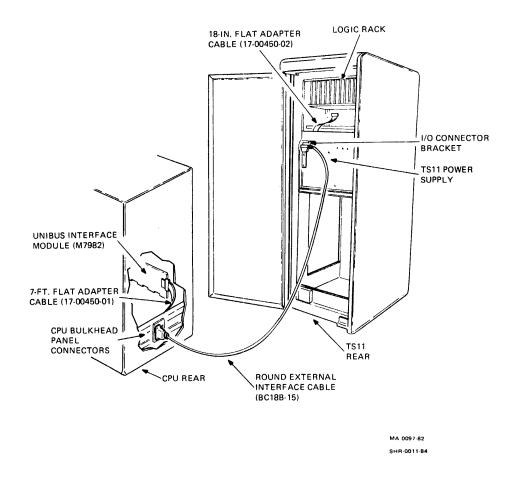

| TS11 Signal Cabling                                        | 2-19 |

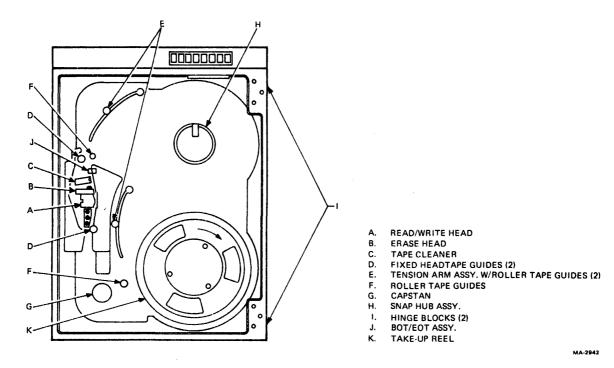

| Transport Components to Clean                              |      |

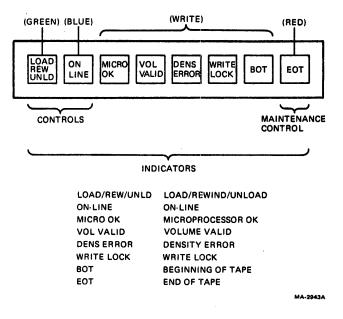

| TS11 Transport Controls and Indicators                     |      |

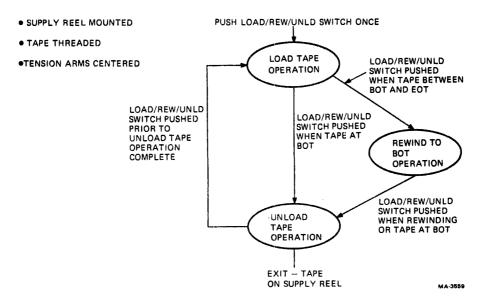

| Load Switch State Diagram                                  |      |

| Tape Loading Path                                          |      |

| TSBA Register                                              |      |

| TSDB Register (Loaded with a Command Pointer)              |      |

|                                                            |      |

| TSSR Register                                              | -    |

| TS11 Register Summary                                      |      |

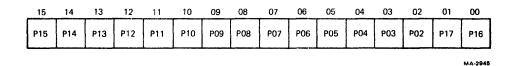

| Command Packet Header Word                                 | 5-18 |

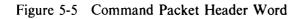

| Byte Swap Sequence, Forward Tape Direction (Read or Write) | 5-21 |

| Byte Swap Sequence, Reverse Tape Direction (Read)          | 5-22 |

| Get Status Command Packet Example                          |      |

| Read Command Packet Example                                | 5-24 |

| Write Characteristics Commnd Packet Example                |      |

| Write Command Packet Example                               | 5-27 |

| Position Command Packet Example                            | 5-27 |

| Format Command Packet Example                              | 5-29 |

| Control Command Packet Example                             | 5-29 |

| Initialize Command Packet Example                          |      |

| Message Packet First Header Word                           |      |

| Message Packet Example                                     |      |

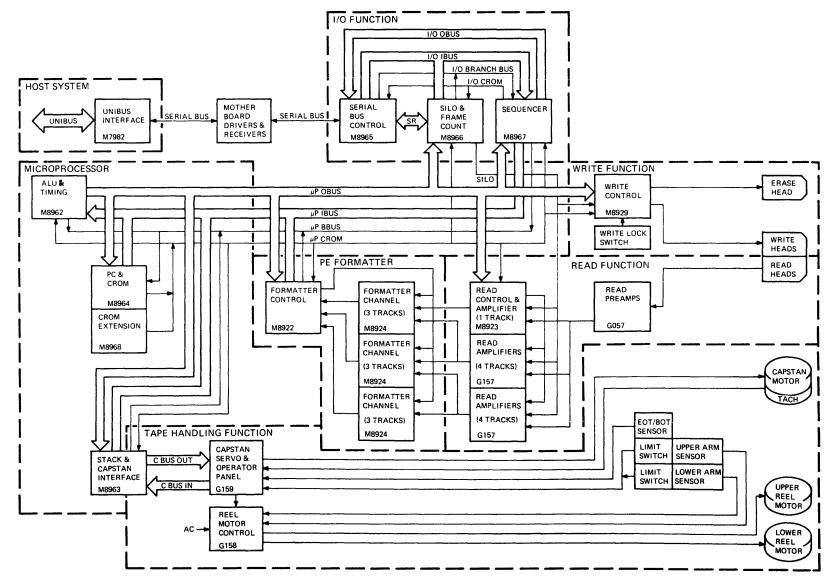

| TS11 Block Diagram                                         |      |

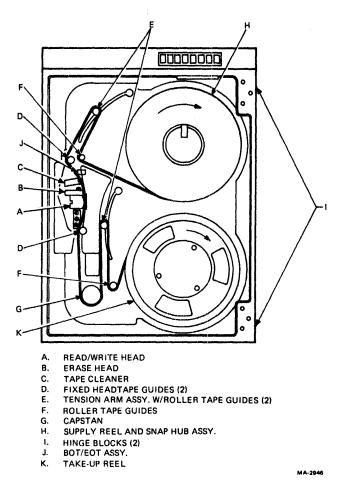

| Tape Transport Assembly                                    | 6-4  |

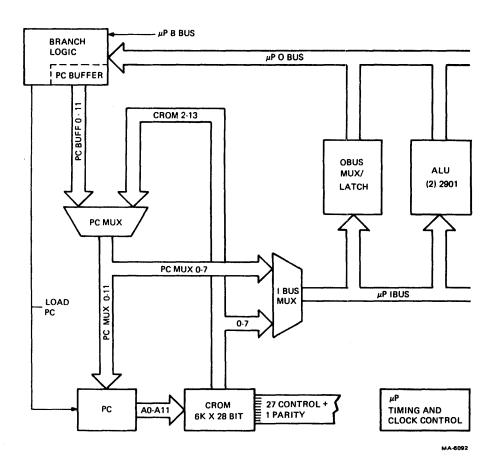

| Microprocessor Block Diagram                               |      |

| 2901 Microprocessor Slice                                  |      |

| CROM Addressing                                            |      |

| Basic Instruction Flow                                     |      |

| Clock Generator and Control Logic                          |      |

| Timing Signals                                             |      |

| Stack Operation                                            |      |

| M7982 Data Path                                            |      |

| I/O Registers                                              |      |

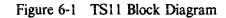

| Tape Handling Function                                     |      |

| Motion and Direction Detection                             |      |

| Capstan Speed                                              |      |

| Capstan Timing Diagram                                     |      |

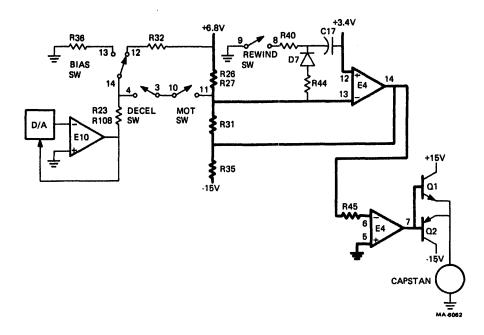

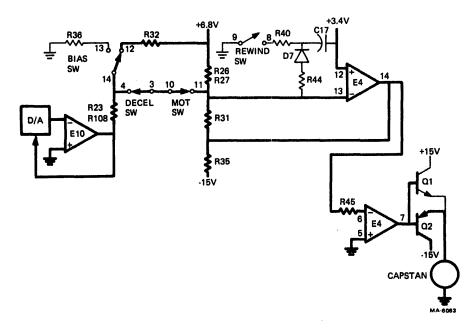

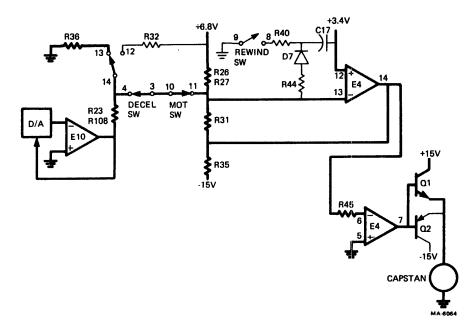

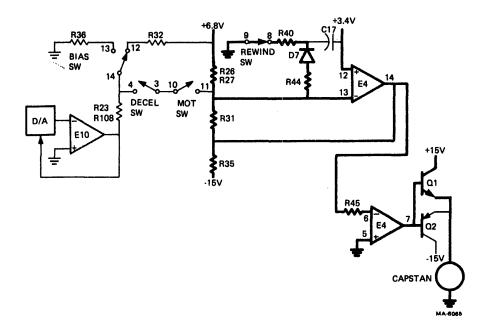

| Idle – Capstan Drive                                       |      |

| Forward – Capstan Drive                                    |      |

| Reverse – Capstan Drive                                    |      |

|                                                            |      |

| Rewind Capstan Drive                                       |      |

| Parameter Comparison                                       |      |

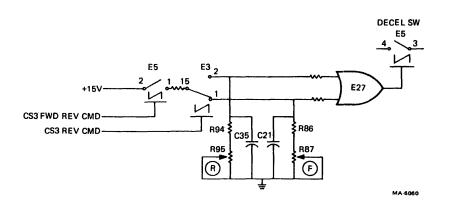

| DECEL Switch                                               | 6-58 |

| Tension Arm Transducer                                     | 6-59 |

| Signal Relationships                                       |      |

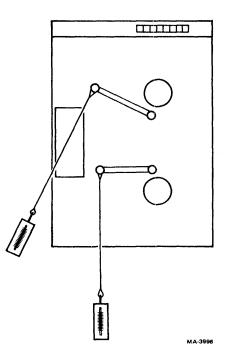

| Tape Loading Path                                          |      |

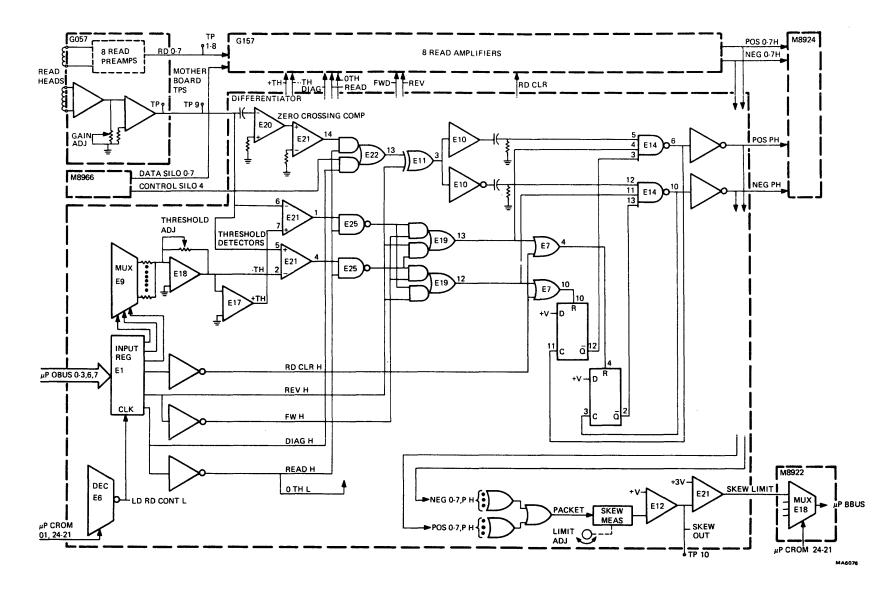

| Read Function                                              |      |

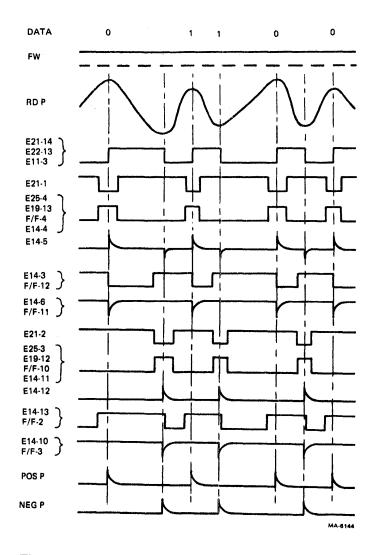

| Forward Signal                                             |      |

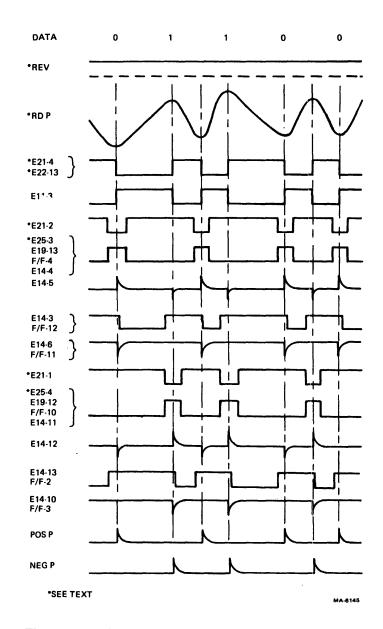

| Reverse Signal                                             |      |

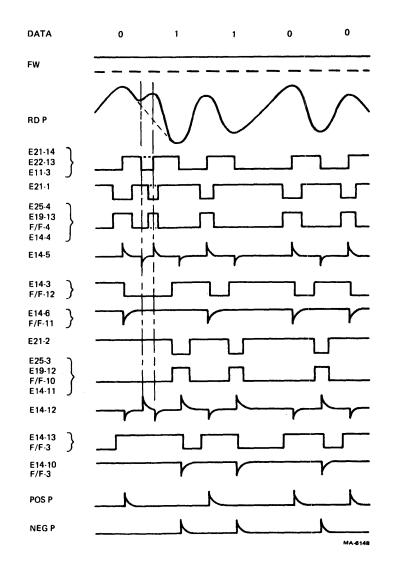

| Spurious Signal                                            | 6-68 |

| 6-29 | Low Signal                                 | 6-69 |

|------|--------------------------------------------|------|

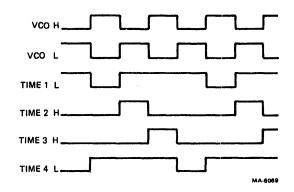

| 6-30 | VCO Operation                              |      |

| 6-31 | Window Generation                          | 6-73 |

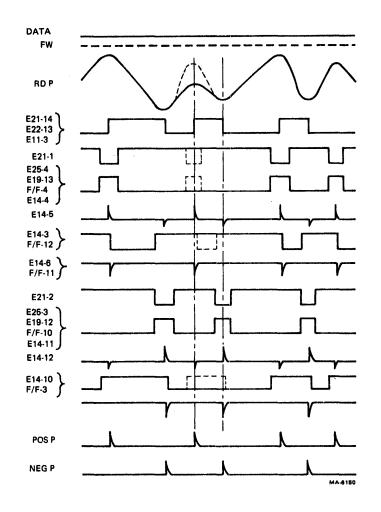

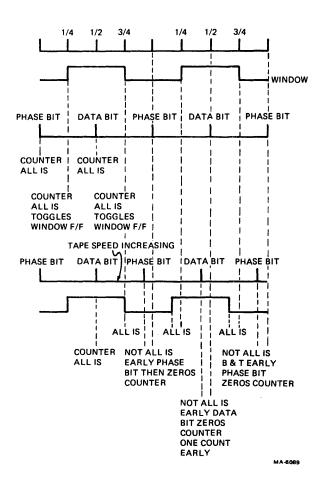

| 6-32 | Timing Relationships                       | 6-75 |

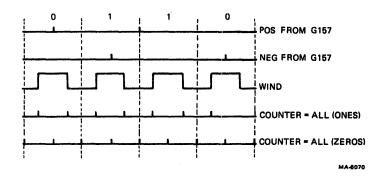

| 6-33 | Counter-Normal Signal Relationships        | 6-75 |

| 6-34 | Window Adjustment                          | 6-76 |

| 6-35 | Write Function                             | 6-82 |

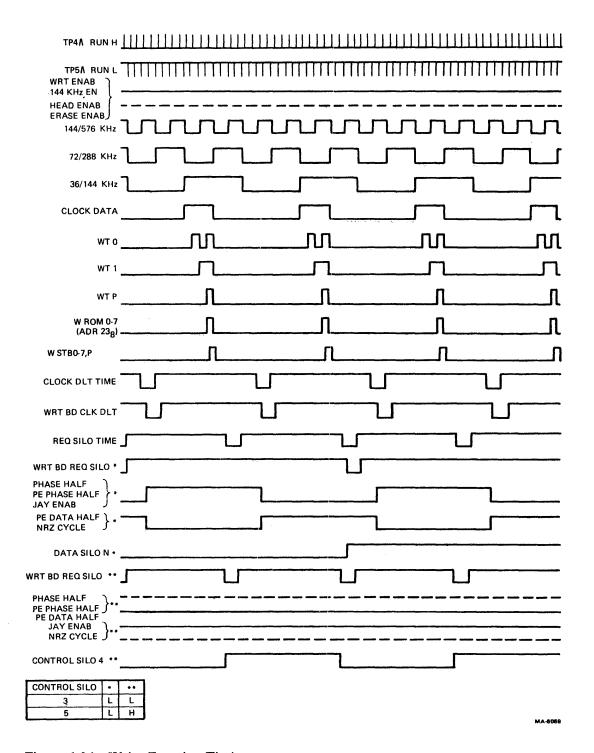

| 6-36 | Write Function Timing                      | 6-83 |

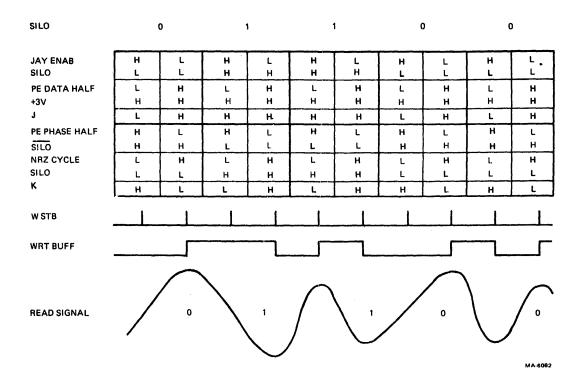

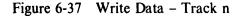

| 6-37 | Write Data – Track n                       | 6-85 |

| 6-38 | Write IDB – Track 4                        | 6-85 |

| 6-39 | Write Tape Mark – Tracks 1, 2, 4, 5, 7, 8  | 6-86 |

| 6-40 | IDB and Tape Mark – Unwritten Tracks       |      |

| 6-41 | Status Reporting                           | 6-88 |

| 7-1  | TS11 Subsystem Major Assemblies            | 7-1  |

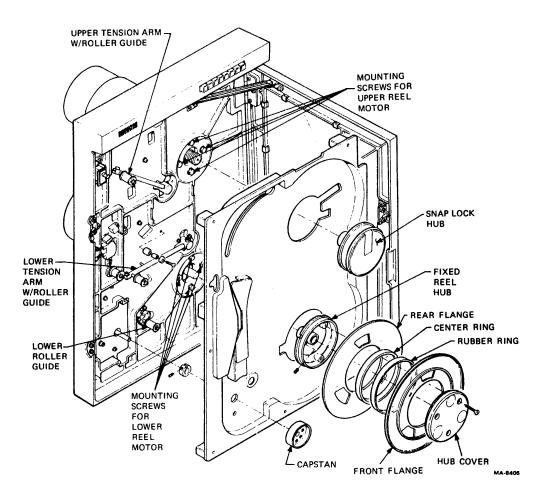

| 7-2  | Transport Assemblies (Front View)          |      |

| 7-3  | Transport Assemblies (Rear View)           | 7-3  |

| 7-4  | Troubleshooting Flowchart                  | 7-4  |

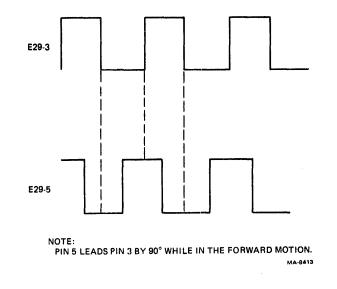

| 7-5  | Capstan Simulated Motion Waveforms         | 7-11 |

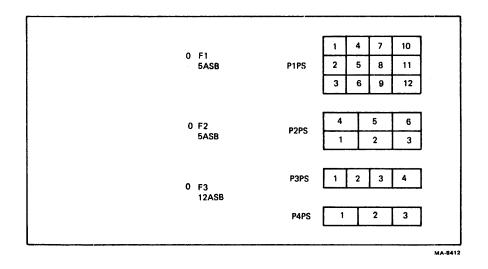

| 7-6  | Power Supply                               | 7-38 |

| 7-7  | Power Supply Mate-N-Lok Connector Layout   | 7-38 |

| 7-8  | Deckplate Assembly                         |      |

| 7-9  | Snap Lock Hub Cross Section                | 7-40 |

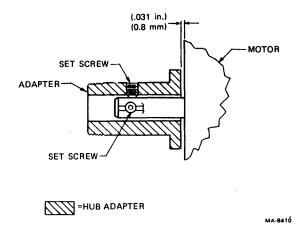

| 7-10 | Hub Adapter                                |      |

| 7-11 | Tension Arm Adjustment                     | 7-43 |

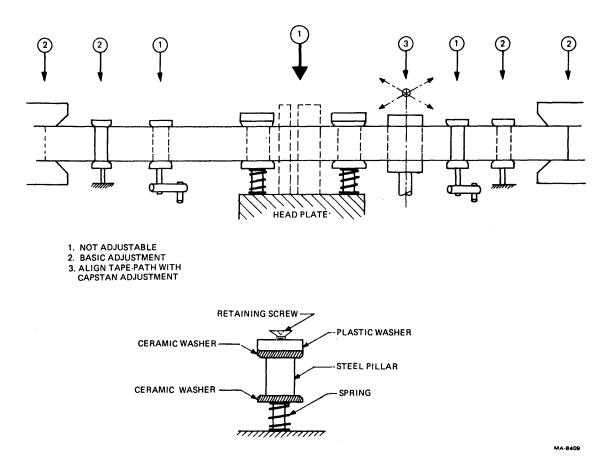

| 7-12 | Tape Path Alignment                        | 7-45 |

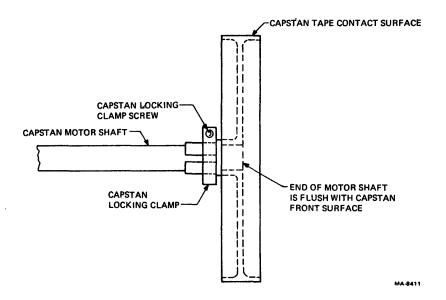

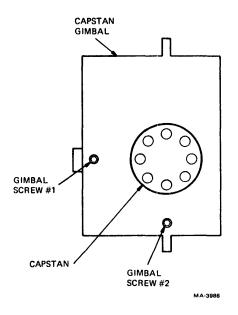

| 7-13 | Capstan Positioning on Capstan Motor Shaft | 7-46 |

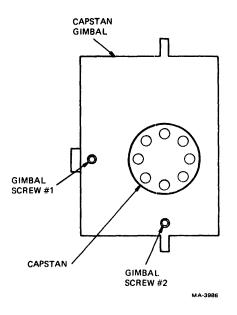

| 7-14 | Capstan Gimbal Adjustment                  | 7-47 |

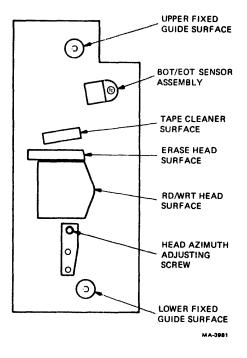

| 7-15 | BOT/EOT Sensor and Head Skew Adjustment    |      |

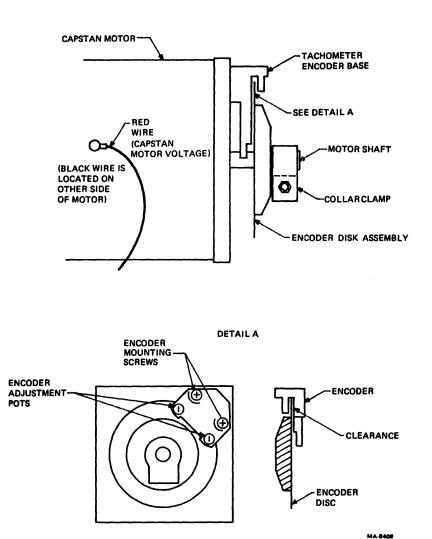

| 7-16 | Capstan Tachometer Encoder Assembly        | 7-50 |

| 7-17 | Capstan Tachometer Phase                   | 7-51 |

| 7-18 | Capstan Speed Adjustment                   | 7-52 |

| 7-19 | Read Preamplifier Locator                  | 7-54 |

| 7-20 | Read Preamplifier Adjustment               | 7-54 |

| 7-21 | VCO and Threshold Waveforms                | 7-55 |

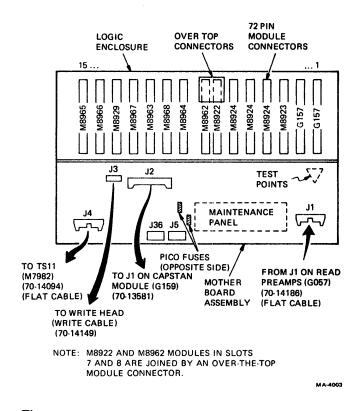

| 7-22 | Logic Rack (Rear View)                     |      |

# TABLES

| 1-1 | TS11 Assigned Command Modes          | 1-6  |

|-----|--------------------------------------|------|

| 1-2 | TS11 Subsystem Specifications        | 1-10 |

| 1-3 | Applicable Documents                 | 1-13 |

| 1-4 | Available Options                    | 1-14 |

| 2-1 | TS11 Power Plugs and Receptacles     |      |

| 2-2 | Floor Loading                        |      |

| 2-3 | Unibus Address and Interrupt Vectors | 2-17 |

| 2-4 | Address and Vector Examples          | 2-17 |

| 4-1 | Control Switch Functions             | 4-2  |

| 4-2 | Operation Indicators                 | 4-3  |

| 5-1 | TSBA Bit Definitions                 |      |

| 5-2 | TSDB Bit Definitions                 | 5-3  |

| 5-3 | TSSR Bit Definitions                 | 5-5  |

| 5-4 | RBPCR Bit Descriptions               | 5-9  |

| 5-5 | XSTAT0 Bit Definitions               | 5-10 |

| 5-6 | XSTAT1 Bit Definitions               | 5-12 |

| 5-7  | XSTAT2 Bit Definitions 5-13                                             |

|------|-------------------------------------------------------------------------|

| 5-8  | XSTAT3 Bit Definitions 5-15                                             |

| 5-9  | Command Packet Header Word Bit Definitions 5-19                         |

| 5-10 | Command Code and Mode Field Definitions 5-20                            |

| 5-11 | Write Characteristics Data Bit Definitions 5-26                         |

| 5-12 | Message Packet First Header Word Bit Definitions                        |

| 5-13 | Termination Class Codes 5-32                                            |

| 5-14 | TSSR Fatal Class Codes 5-33                                             |

| 6-1  | Module Layout                                                           |

| 6-2  | M8922–M8962 Over-the-Top Connector Pins                                 |

| 6-3  | CROM Bit Pin Out                                                        |

| 6-4  | CROM Field Configuration                                                |

| 6-5  | I/O CROM Field Configuration 6-9                                        |

| 6-6  | Serial Bus Configuration 6-10                                           |

| 6-7  | CBUSO Command and Status Interpretation                                 |

| 6-8  | CBUSI Status Interpretaion                                              |

| 6-9  | Microprocessor Function Summary 6-18                                    |

| 6-10 | CROM Bit Definition                                                     |

| 6-11 | Destination Registers and Addresses 6-23                                |

| 6-12 | Multidrive Address                                                      |

| 6-13 | Tape Tension Function Summary    6-62                                   |

| 6-14 | Threshold Levels                                                        |

| 6-15 | ROM Look-Up Configurations                                              |

| 6-16 | Status Reporting Summary 6-89                                           |

| 7-1  | Test Equipment                                                          |

| 7-2  | Maintenance Mode Diagnostics                                            |

| 7-3  | Fatal Microprocessor Errors 7-23                                        |

| 7-4  | Nonfatal Microprocessor Errors 7-26                                     |

| 7-5  | Customer Confidence or Maintenance Mode Test Errors                     |

| 7-6  | Bring-Up Procedure Errors 7-36                                          |

| 7-7  | Dead Track/Module Locations 7-37                                        |

| 7-8  | Voltage Checks and Adjustments 7-37                                     |

| 7-9  | Wiring Charts for TS11 70-16288 Power Supply Mate-N-Lok Connectors 7-39 |

| 7-10 | Component Replacement and Adjustment Cross-Reference                    |

# CHAPTER 1 GENERAL INFORMATION

#### **1.1 INTRODUCTION**

The TS11 Subsystem is a low price, medium performance, 9-track tape storage system featuring microprocessor controlled electronics for high data reliability and maintainability.

The TS11 fully integrated tape storage system is packaged with its associated interface and power supply in a standard 19-inch rack mountable frame. It can be configured in several cabinets to complement various Digital computer systems. Reading and writing are performed at 45 inches per second and data is recorded at 1600 bits per inch (bit/in) phase encoded (PE). ANSI standard format recording allows data to be transferred easily between computer systems.

The TS11 subsystem consists of a tape transport with an integrated formatter and a single hex size interface/controller module. This module, M7982, is designed for Unibus PDP-11 and VAX-11 processors. It plugs into any hex sized slot in a Unibus small peripheral controller (SPC), and it communicates with one tape transport.

#### **TS11 Subsystem Features**

#### Performance

114 cm/sec (45 inches/sec) read/write speed 72,000 bytes per second transfer rate 380 cm/sec (150 inches/sec) rewind speed Bidirectional reading capability

#### Capacity

1600 bit/in phase encoded ANSI compatible recording 15.24 cm to 26.67 cm (6 inches to 10.5 inches) tape reel capacity

#### **Reliability/Data Integrity**

Automatic error correction Read after write check In-line diagnostics that run continuously during drive standby mode Off-line self diagnostics Simple, rugged design

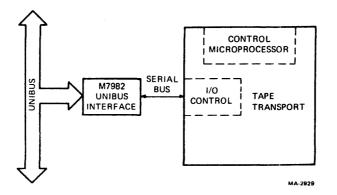

Figure 1-1 TS11 Subsystem Configuration

#### **1.2 SUBSYSTEM OVERVIEW**

Figure 1-1 shows the TS11 subsystem block diagram. The subsystem contains one transport, one TS11 interface module (M7982), and a serial bus interface cable.

The M7982 interface plugs into the Unibus and receives parallel data in the packet protocol format. (Packet protocol is discussed in Chapter 5 of this manual.) A serial bus interface cable then connects the interface to the transport. Parity for the transport command and data information is maintained and checked in the serial data stream. This ensures that an accurate transfer has been made on the serial bus interface cable.

During data transfers, the transport resident formatter controls data fetching, formatting, and transmission. It also oversees the handling of error corrections. Single track read errors are corrected by the hardware automatically. The read after write feature verifies accurate recording of data on the tape.

Each vertical frame of the 9-track tape represents one character of eight bits plus a parity bit. Groups of characters are combined to form records that, under program control, can vary in length. Each record block is separated by a formatted interrecord gap (IRG) that has a minimum length of 0.5 inches.

The TS11 features bidirectional tape reading. Writing occurs only while the tape is moving forward. Tape motion is controlled by a servo-controlled capstan. Tape buffering between capstan and reels is accomplished by low inertia tension arms.

The tape drive can be controlled locally from the front control panel. All operational tape motion is controlled by two pushbutton switches.

Whenever the TS11 is in standby mode for more than 500 ms, an extensive set of drive resident diagnostics is executed to assure the continued operating integrity of the TS11. These diagnostics exercise the electronics to the fullest extent possible short of moving the tape or altering data and status register contents.

The TS1: microprocessor controls such things as capstan speed; it monitors read and write strobe times, sets read and write voltage threshold levels, and determines the length of interrecord gaps. This advanced control system provides further confidence in the operating integrity of the TS11.

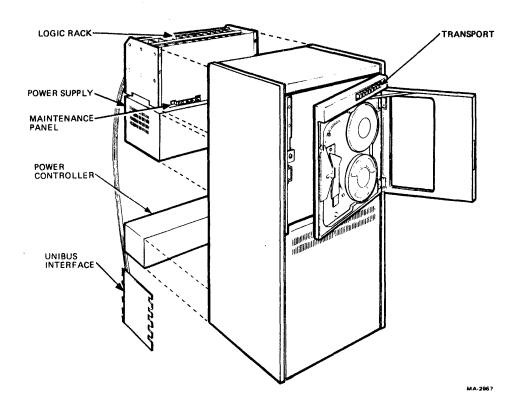

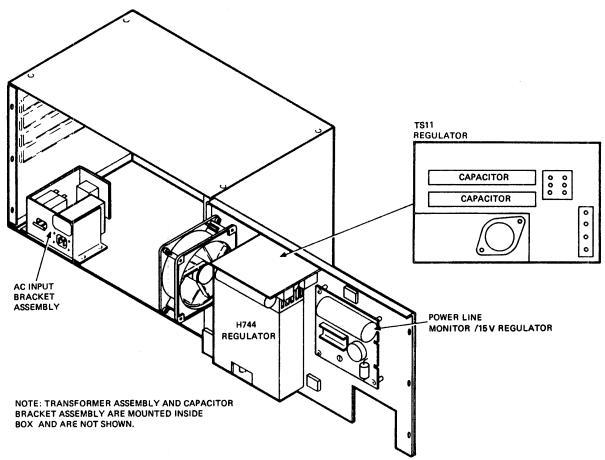

Figure 1-2 TS11 Subsystem Major Assemblies

#### **1.3 PHYSICAL DESCRIPTION**

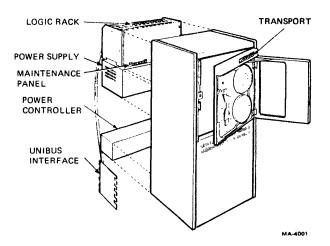

Figure 1-2 shows the TS11 major assemblies.

#### 1.3.1 Unibus Interface

The Unibus interface is a standard PDP-11 hex height, multilayer two sided module (M7982 module designation). It can be placed in any small peripheral controller (SPC) slot that is wired for all Unibus signals and accepts hex height modules. Also, it can plug into DD-11 series SPC backplanes in BA11 series expander boxes. This module links the transport with the Unibus via a serial bus interface cable.

### NOTE The nonprocessor grant (NPG) jumper must be removed when the M7982 is installed.

#### 1.3.2 Transport

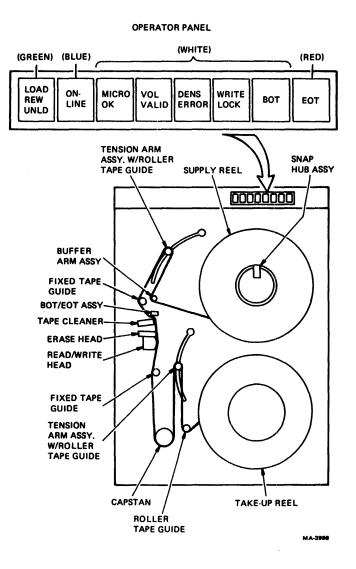

The tape transport subsystem (Figures 1-2 and 1-3) includes the following major assemblies.

Main deckplate Reel servo Capstan servo Head assembly and read preamplifiers Tape transport control and operator control logic Power supply

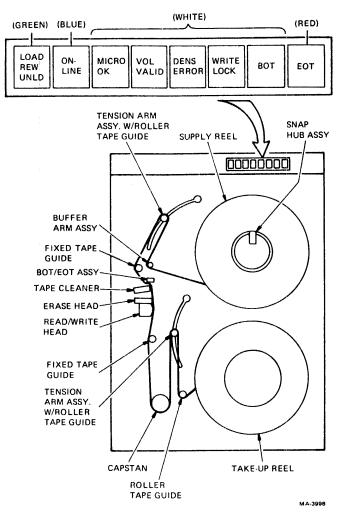

Figure 1-3 Transport Assemblies (Front View)

Main Deckplate – The main deck is die cast aluminum. It provides a single coplanar set of mounting surfaces. These machined surfaces become a single reference plane on which all tape path determining parts are mounted (Figures 1-2 and 1-3).

The casting, and hence the drive, is mounted to a cabinet rack by two hinge blocks. It swings out (hinged on the right side) to allow servicing. Also, for servicing, several reference pads are provided to check hub and reel alignment. The door, mounted to the same hinge area, can also be opened if the drive is swung outward.

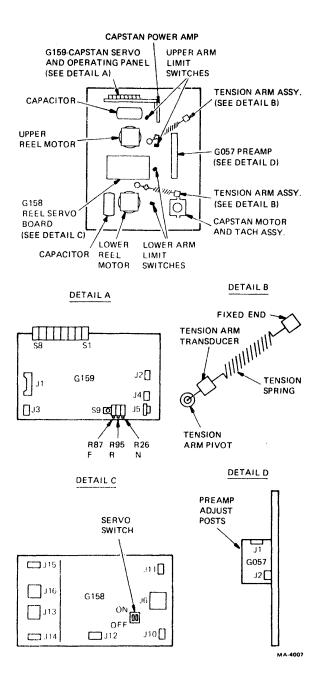

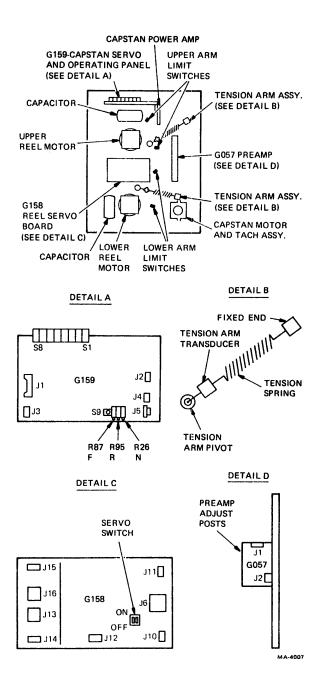

**Reel Servo** – The recl servo consists of the supply reel servo motor and snap lock hub, take-up reel servo motor and take-up reel, G158 reel motor control module, and tension arm assemblies (Figures 1-3 and 1-4). All of these components mount directly to the main deck assembly.

The tension arms control tape tension and allow rapid tape start and stops without damage to the tape or servo motors. Tension arms also sense tape motion in order to drive the reel servo motors. The G158 module receives these signals and controls the speed and direction of both servo motors.

Figure 1-4 Transport Assemblies (Rear View)

**Capstan Servo** – The capstan servo system consists of the capstan motor/tachometer assembly and the G159 capstan servo module (Figures 1-3 and 1-4). The capstan motor assembly moves the tape across the read/write head. The G159 module sets the direction and drives the motor while the optical tachometer senses the tape speed. The optical tachometer then loops the information back to the G159 module, which in turn drives the capstan motor to the correct speed.

Head Assembly – The head assembly consists of a precision head mounting plate, read/write head, head tape guides, tape cleaner, erasc head, and a BOT/EOT sensor (Figure 1-3). The head mounting plate provides a precision mounting surface for the head, cleaner, and guides.

The G057 module (read preamplifiers) is contained in a shielded enclosure and mounted to the rear of the deck casting.

**Operator Controls** – The transport (Figure 1-3) incorporates three lighted operator pushbuttons (colored) and five indicators (white). Chapter 4 details the operation of these controls.

These controls perform a dual function: operating and diagnostic control. Microdiagnostic errors are displayed in either mode. A switch on the printed circuit board backplane selects the mode.

**Power Supply** – All transport voltages are supplied by the TS11 power supply. The supply operates at 50 Hz or 60 Hz  $\pm$  1 Hz with no changes required. For 120 V or 240 V operation, only the ac input box and line cord need to be changed. A TS11K-AA kit converts a 240 V unit to 120 V and a TS11K-AB kit converts a 120 V unit to 240 V. The power system is modularized for easy maintenance and uses standard parts for increased reliability.

#### **1.4 SYSTEM FUNCTIONAL DESCRIPTION**

The functions listed in Table 1-1 make up the TS11 command set. These commands use device registers to operate the transport and to transfer data. This section describes register manipulation and provides an overview of packet protocol (the format used to transfer commands and data). Detailed descriptions of the commands are provided in Chapter 5 of this manual.

| Command Name          | Mode Name                                                                                                                                    |  |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|

| Get Status            | Get status                                                                                                                                   |  |

| Read                  | Read next (forward)<br>Read previous (reverse)<br>Reread previous (space reverse, read forward)<br>Reread next (space forward, read reverse) |  |

| Write Characteristics | Load message buffer address and set device characteristics                                                                                   |  |

| Write                 | Write data<br>Write data retry (space reverse, erase, write data)                                                                            |  |

| Position              | Space records forward<br>Space records reverse<br>Skip tape marks forward<br>Skip tape marks reverse<br>Rewind                               |  |

| Format                | Write tape mark<br>Erase<br>Write tape mark retry (space reverse, erase, write tape mark)                                                    |  |

| Control               | Message buffer release<br>Rewind and unload<br>Clean tape                                                                                    |  |

| Initialize            | Drive initialize                                                                                                                             |  |

## Table 1-1 TS11 Assigned Command Modes

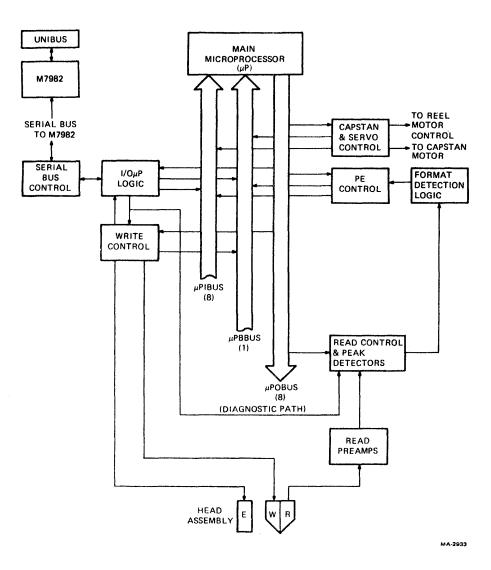

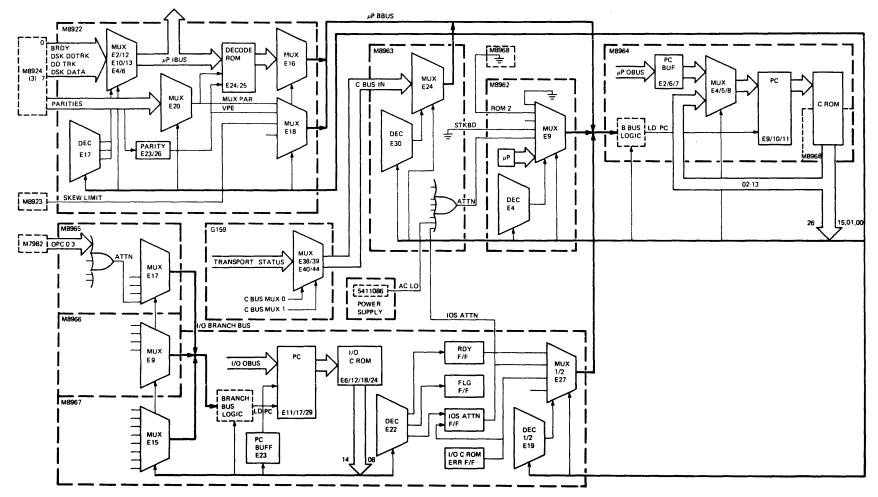

Figure 1-5 is a simplified block diagram of the TS11. The transport is under the complete control of the microprocessor and related microcode. Two TS11 registers (TSBA and TSSR) are presented to the Unibus and communication between the CPU and the transport is via packet protocol (controlled by the microcode).

The TS11 (M7982) has eight registers which occupy only two Unibus word locations: a Unibus data buffer (TSDB), a Unibus address register (TSBA), and a status register (TSSR). The five additional registers elsewhere in PDP-11 memory provide status information.

The TSDB is an 18-bit register that is parallel loaded from the Unibus or serially loaded from the transport. A 16-bit portion of this register is used as a word buffer register to the M7982 when the M7982 is the bus slave (for beginning an operation). The same word buffer register is also used by the transport [for data during nonprocessor request (NPR) transfers] when the M7982 is the bus master. The TSDB can be loaded when the M7982 is the bus slave by three different transfers from a bus master. Two transfers are for

Figure 1-5 TS11 Simplified Block Diagram

maintenance purposes (byte transfer; DATOB at high/low byte). The third transfer is for normal (word) operation (DATO). This register is write only and is not cleared at power on, subsystem initialize, or bus initialize. It cannot be loaded without the complete transport unit connected (to supply a serial bus synchronous clock). The M7982 responds with SSYN (system synchronized) every time the TSDB is accessed.

Commands are not written to the drive's Unibus registers. Instead, command pointers, which point to a command packet somewhere in memory space, are written to the TSDB register. The command pointer is used in the TS11 to retrieve words in memory called the command packet. The words in the command packet instruct the transport as to the function to be performed. These words contain any function parameters such as bus address, byte count, record count, and modifier flags.

The TSBA is an 18-bit register that is parallel loaded from the TSDB every time the TSDB is loaded as Unibus slave. TSDB bits 15-2 load into TSBA bits 15-2; TSDB bits 1 and 0 load into TSBA bits 17 and 16; and zeros are loaded into TSBA bits 1 and 0. TSBA bits 17 and 16 are displayed in TSSR bits 9 and 8 respectively. The register can be instructed by the transport to increment or decrement by two for nonprocessor request (NPR) word transfers, or by one for NPR byte transfers. The TSBA register has two major purposes.

- 1. The TSBA can be used as a command pointer to the remote transport device registers (command and message buffers). These are located somewhere in the Unibus address space. The contents, loaded into the TSDB when the M7982 is the bus slave, is considered the command pointer. In this mode, the M7982 receives data (initiated by the transport) at this command pointer address and sends the command packet (data) to the drive unit for storage and/or execution.

- 2. The TSBA can be used as a data pointer, pointing to data buffer areas located somewhere in the Unibus address space. In this mode, the transport serially loads the TSDB with the data buffer address and transfers the contents of TSDB (0 to 17) into TSBA. The contents are then used to point to data buffer areas [while the M7982 transfers data by the NPRs (initiated by the transport)] and to message packets where the TSBA is left with the highest message buffer address + 2.

The TSSR is a 16-bit register that can be updated only from the transport or M7982 internal logic. It cannot be modified from the Unibus except for SPE, UPE, RMR, NXM, and SSR bits that are cleared when the TSDB is written by the host CPU. Here system status can be observed.

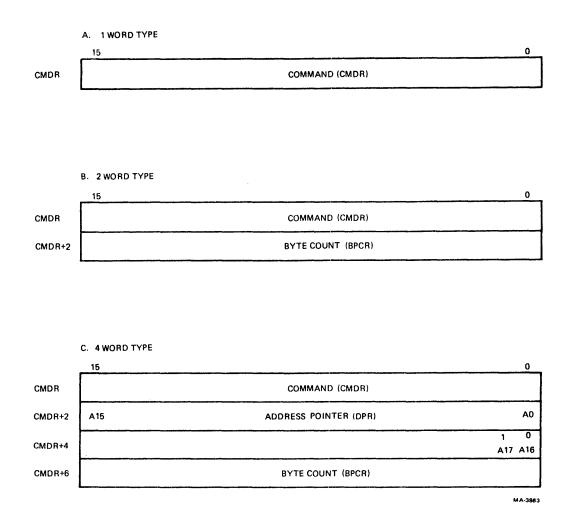

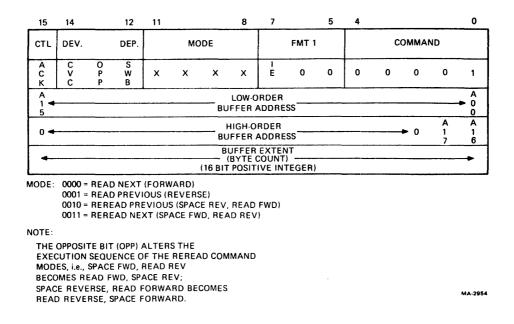

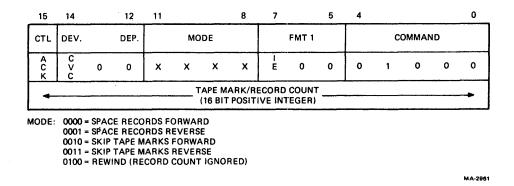

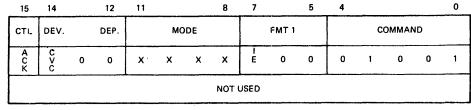

Before the TS11 can begin a function, a command packet must be assembled in the system memory. Every packet must have four words, even though not every command requires all four words. The packet may be thought of as three remote device registers (Figure 1-6).

1. Command Register (CMDR)

1

2. Data Pointer (DPR), which is made up of two word locations:

Low order address word (A15:00) CMDR+2 High order address word (A17:16) CMDR+4 in bits 1 and 0

3. Positive Byte Count Register (BPCR)

Data operations (DPR required) CMDR+6 Nondata operations (no DPR required) CMDR+2

Figure 1-6 Command Packets

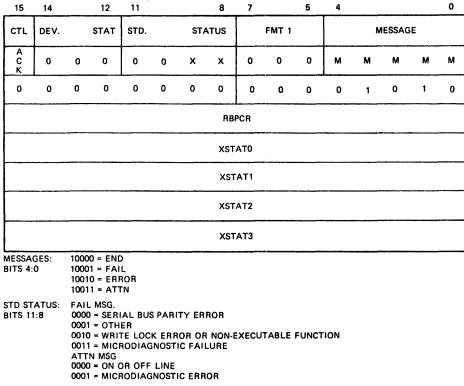

Message packets are issued by the transport and deposited in the host CPU memory space. These message packets contain complete device status information. Subsystem operation requires a message buffer address on a set characteristics command. This command must be the first command issued to the subsystem. Otherwise, all tape motion commands will be rejected.

The command pointer must be an address on a modulo-4 boundary (that is, beginning at 0, 4, 10, 14, etc.), because only the high order 16-bits can be specified by the command pointer.

The DPR is eventually loaded into TSBA to be used as the Unibus address for NPR data transfers. The BPCR is used to indicate the number of bytes (8-bits of data per byte) to be moved to or from the transport during a data transfer. It is also used to specify the number of records in a space record command or the number of files in a skip file command. The CMDR specifies the function the transport will execute.

Figure 1-5 is a simplified block diagram of the TS11. If a read forward operation is commanded, the following occurs. The capstan interface logic directs the capstan servo logic to supply motor current to the capstan servo. This moves the tape forward. When the tape is up to speed, the transport read logic is enabled and receives data from the read heads. The read data output of the read heads (RD0-RD7, RDP) is checked for vertical parity errors. If any such errors are detected, the transport error logic is notified to take appropriate corrective action. Read data from the formatter is then sent to the main microprocessor via the microprocessor in bus  $(\mu PIBUS)$ . Under microprocessor control, read data is then sent to the I/O control and sequencing logic via out bus  $(\mu POBUS)$ . From here, the I/O microprocessor transfers read data to the serial bus control logic via the I/O out bus (I/O OBUS), where the data is gated serially to the M7982 interface. A serial to parallel conversion occurs and the data word is parallel transferred to memory via the Unibus on the M7982.

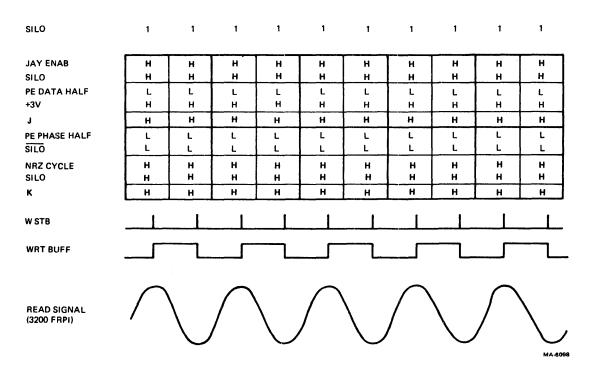

If a write operation is commanded and the request is granted, the following occurs. The capstan servo logic supplies motor current to the capstan, moving the tape forward. The first data character is placed on the Unibus and enters the M7982 when requested by the microprocessor. Subsequent transfers occur and fill up the silo in the I/O microprocessor, before writing on tape occurs. When the tape is up to speed, transferring data characters begins. As data characters are written on tape, new characters are transferred to the silo. This occurs until all data is transferred from memory to silo, and finally, silo to tape. The preamble is loaded into the silo before write data. The postamble is loaded in after. All data transfers (serial transfers) are under the control of the I/O microprocessor. The data is sent via the serial bus cable to the serial bus control logic. The I/O bus then transfers data to the write control logic and on to the write heads. The main microprocessor checks the data for write errors by doing a read after write.

Refer to Chapter 6 for detailed TS11 operating information.

#### **1.5 UNIT SPECIFICATIONS**

Table 1-2 lists the operational, environmental, mechanical, and electrical specifications for the TS11.

| Category                  | Specifications                                                          |  |

|---------------------------|-------------------------------------------------------------------------|--|

| Main Specifications       |                                                                         |  |

| Storage medium            | 12.7 mm (0.5 in) wide magnetic tape (industry compatible)               |  |

| Data transfer rate        | 72,000 characters per second, maximum                                   |  |

| Transports per controller | L ··                                                                    |  |

| Data Organization         |                                                                         |  |

| Number of tracks          | 9                                                                       |  |

| Recording density         | 64 rows/mm (1600 bpi)                                                   |  |

| Interrecord gap           | 12.7 mm (0.5 in) minimum                                                |  |

| Recording method          | PE mode at 64 rows/mm (1600 bpi);<br>conforms with ANSI DOC. X3.39-1973 |  |

#### Table 1-2 TS11 Subsystem Specifications

| Category                   | Specifications                                                                                                                                   |  |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Tape Motion                |                                                                                                                                                  |  |

| Speed, forward and reverse | 114 cm/sec (45 in/sec)                                                                                                                           |  |

| Rewind speed               | 380 cm/sec (150 in/sec) 3 minute average for 10.5 inch reel                                                                                      |  |

| Tape transport             | Direct drive ac reel motors, servo<br>controlled; capstan has biphase<br>tachometer outputs; tension arm tape<br>buffering with constant tension |  |

| Start distance             | 4.57 mm ± 0.5 mm (0.180 in ± 0.050 in)                                                                                                           |  |

| Stop distance              | 4.11 mm ± 1.1 mm (0.162 in ± 0.050 in)                                                                                                           |  |

| Start time                 | 8 ms ± 1 ms                                                                                                                                      |  |

| Stop time                  | 8  ms + 1  ms, -2  ms                                                                                                                            |  |

| Tape Characteristics       |                                                                                                                                                  |  |

| Width                      | 12.7 mm (0.5 in)                                                                                                                                 |  |

| Length                     | 732 m (2400 ft) maximum                                                                                                                          |  |

| Туре                       | Mylar base, iron-oxide coated (ANSI standard)                                                                                                    |  |

| Thickness                  | 0.038 mm (1.5 mils)                                                                                                                              |  |

| Tension                    | 255 g (9.0 oz)                                                                                                                                   |  |

| Reel diameter              | 26.7 cm (10.5 in)                                                                                                                                |  |

| Reel hub                   | 9.37 cm (3.69 in) diameter<br>(industry standard)                                                                                                |  |

| Mechanical                 |                                                                                                                                                  |  |

| Tape transport mounting    | Mounts on slides in standard 48.3 cm (19 in) cabinet                                                                                             |  |

Table 1-2 TS11 Subsystem Specifications (Cont)

| Category                                    | Specifications                                                                     |  |  |

|---------------------------------------------|------------------------------------------------------------------------------------|--|--|

| Transport dimensions<br>in rackmount option |                                                                                    |  |  |

| Depth                                       | 76 cm (30 in)                                                                      |  |  |

| Width                                       | 48 cm (19 in)                                                                      |  |  |

| Height                                      | 66 cm (26 in)                                                                      |  |  |

| Weight                                      | 68 kg (150 lbs)                                                                    |  |  |

| Electrical                                  |                                                                                    |  |  |

| Frequency                                   | 50 Hz $\pm$ 1 Hz or 60 Hz $\pm$ 1 Hz                                               |  |  |

| Voltage                                     | 90 Vac to 128 Vac or 184 Vac to 256 Vac single phase                               |  |  |

| Power                                       | 400 W (standby); 1200 W maximum<br>(start/stop)                                    |  |  |

| Input current<br>(Transport)                | 10 A maximum at 90 Vac to 128 Vac; 5 A maximum at 184 Vac to 256 Vac               |  |  |

| Input current<br>(M7982 Interface)          | 3.5 A maximum at 5 Vdc                                                             |  |  |

| Environment                                 |                                                                                    |  |  |

| Operating temperature                       | 15° to 32° C (60° to 90° F)                                                        |  |  |

| Relative humidity                           | 20% to 80%, with maximum wet bulb 25° C (77° F) and minimum dew point 2° C (36° F) |  |  |

| Maximum altitude                            | 2438 m (8000 ft)                                                                   |  |  |

| Other                                       |                                                                                    |  |  |

| BOT, EOT detection                          | Photoelectric sensing of reflective strip (industry standard)                      |  |  |

| Skew control                                | Deskewing electronics in the tape<br>transport correct static skew                 |  |  |

| Write protection                            | Write protect ring sensing on the tape transport                                   |  |  |

| Magnetic heads                              | Nine track, dual gap read after write (full-width erase)                           |  |  |

| Table 1-2 TS11 Subsystem | n Specifications (Cont) | ) |

|--------------------------|-------------------------|---|

|--------------------------|-------------------------|---|

#### **1.6 APPLICABLE DOCUMENTS**

The documents listed in Table 1-3 are applicable to the TS11 system and are available through the local Digital Sales and Service Office or the Accessories and Supplies Group. See Paragraph 3.3.4 for details.

| Title                                                                                | Number                                                                                 | Description                                                                                                                                        |

|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| TS11 Subsystem<br>User Guide                                                         | EK-0TS11-UG                                                                            | Contains functional overview,<br>installation, operating, and<br>programming information.                                                          |

| TS11 Subsystem<br>Technical Manual                                                   | EK-0TS11-TM                                                                            | Combines the user guide with<br>theory of operation and<br>maintenance information.                                                                |

| TS11 Subsystem<br>Pocket Service<br>Guide                                            | EK-0TS11-PS                                                                            | Provides a quick reference to maintenance procedures for the trained service person.                                                               |

| TS11 Subsystem<br>Illustrated Parts<br>Breakdown                                     | EK-0TS11-IP                                                                            | Provides a listing and illustration of replaceable parts.                                                                                          |

| 872 Power Controller<br>861 Power Controller<br>TS11 A<br>TS11 B<br>TS11 C<br>TS11 D | EK-00872-IP<br>EK-00861-IP<br>EK-TS11A-IP<br>EK-TS11B-IP<br>EK-TS11C-IP<br>EK-TS11D-IP |                                                                                                                                                    |

| PDP-11 Processor<br>and Systems Manual*                                              |                                                                                        | A series of maintenance and<br>theory manuals that provide a<br>detailed description of the<br>basic PDP-11 system.                                |

| PDP-11 Processor<br>Handbook†                                                        |                                                                                        | A general handbook that<br>discusses system<br>architecture, addressing<br>modes, the instruction set,<br>programming techniques, and<br>software. |

#### Table 1-3 Applicable Documents

\* Applicable manuals accompany the system at the time of installation. The document number depends on the specific PDP-11 family processor.

† Use the processor handbook unique to the actual CPU.

# 1.7 AVAILABLE OPTIONS

Table 1-4 lists the options available for the TS11 subsystem.

Table 1-4

Available Options

.

| Option   | Description                            |

|----------|----------------------------------------|

| TS11-AA  | Rackmount with M7982 120 Vac, 50/60 Hz |

| TS11-AB  | Rackmount with M7982 240 Vac, 50/60 Hz |

| TS11-BA  | TS11-AA in H9602 corporate cabinet     |

| TS11-BB  | TS11-AB in H9602 corporate cabinet     |

| TS11-CA  | TS11-AA in H9646 cabinet               |

| TS11-CB  | TS11-AB in H9646 cabinet               |

| TS11-DA  | TS11-AA in H960 tall cabinet           |

| TS11-DB  | TS11-AB in H960 tall cabinet           |

| TS11K-AA | TS11 240 Vac to 120 Vac conversion kit |

| TS11K-AB | TS11 120 Vac to 240 Vac conversion kit |

×

# CHAPTER 2 INSTALLATION

#### 2.1 SITE PLANNING AND CONSIDERATIONS

Before installing the TS11 subsystem, careful site planning is necessary to satisfy physical and electrical requirements. These aspects of site preparation are discussed in the following paragraphs.

#### 2.1.1 Space Requirements

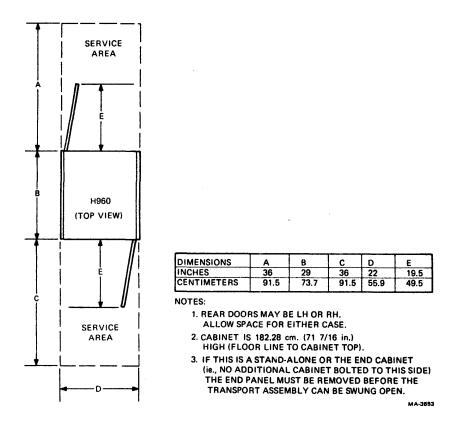

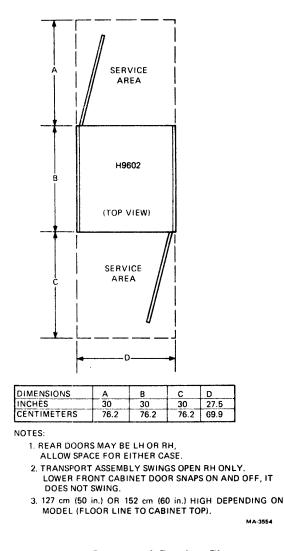

The transport is available as a rackmount option or as an H960, H9602, H9646 cabinet. Figures 2-1, 2-2, and 2-3 respectively show the space and service clearance required for each cabinet.

The TS11 interface requires a single slot in an SPC backplane or DD-11 series SPC backplane in a BA11 series expander box. The transport must be located close enough to the M7982 mounting slot to accommodate an interconnecting cable of 7.4 m (25 feet).

Figure 2-1 Space and Service Clearance, H960 Cabinet and Rackmount (Top View)

#### 2.1.2 Power Requirements

Both the 60 Hz  $\pm$  1 Hz and 50 Hz  $\pm$  1 Hz transports operate from 90 Vac to 128 Vac or 184 Vac to 256 Vac power sources. Operating input power is approximately 400 W nominal (standby), with an operating peak of approximately 1200 W. Maximum operating current in the low voltage range is 10.0 Arms maximum; in the high voltage range it is 5.0 Arms.

Table 2-1 provides a list of receptacles that accept the various voltages. The appropriate circuit breakers are also necessary.

The TS11 (M7982) typically draws 2.0 A, with a maximum of 3.5 A, calculated at +5 Vdc. No other voltage is required. A hex height SPC module is allowed to draw a maximum of 6 A at +5 Vdc (1 A maximum per module section) from an SPC slot. Do not exceed the power available to an SPC slot, DD-11 backplane, or expander box. Also, maximum usable SPC power is not always available in expander boxes. Be sure sufficient power is available.

Digital Equipment Corporation must be notified of available input power well in advance of shipment, so that the correct TS11 subsystem can be shipped.

,

**2.1.3 Floor Loading** Table 2-2 lists floor loading data.

| Rackmount                                            | Plug     | Receptacle    |

|------------------------------------------------------|----------|---------------|

| 120 V NEMA                                           | 5-15P    | 5-15R         |

| 120 V Digital                                        | 90-08938 | 12-05351      |

| 240 V NEMA                                           | 6-15P    | 6-15 <b>R</b> |

| 240 V Digital                                        | 90-08853 | 12-11204      |

| Digital Standard<br>Cabinets (H960,<br>H9602, H9646) | Plug     | Receptacle    |

|                                                      | 1 lug    | meeptack      |

| 120 V NEMA                                           | L5-30P   | L5-30R        |

|                                                      |          |               |

| 120 V NEMA                                           | L5-30P   | <br>L5-30R    |

Table 2-1 TS11 Power Plugs and Receptacles

# Table 2-2 Floor Loading

| TS11 Option                                      | Weight           |

|--------------------------------------------------|------------------|

| TS11-AA/AB<br>Rackmount (TS11 in mounting frame) | 68 kg (150 lbs)  |

| TS11-BA/BB<br>Rackmount in H9602                 | 231 kg (506 lbs) |

| TS11-CA/CB<br>Rackmount in H9646                 | 188 kg (415 lbs) |

| TS11-DA/DB<br>Rackmount in H960                  | 230 kg (504 lbs) |

#### 2.1.4 Installation Constraints

The route that the equipment will travel from the receiving area to the installation site should be studied in advance to ensure problem free delivery. Among the factors to consider are the height and location of loading doors, the size, capacity, and availability of elevators, the number and size of aisles and doors in route, and any restrictions, such as bends or obstructions, in the hallways. Any constraints should be reported to Digital Equipment Corporation as soon as possible, so that requirements of the individual installation site can be considered when the unit is packed for shipment.

Locate the TS11 in an area free of excessive dust and dirt or corrosive fumes and vapors. Place equipment so that cabinet fan inlets and air outlets are not obstructed in any way.

If the system you are installing is housed in an H9602 cabinet, the following precautions should be understood before installation.

- 1. Observe the caution symbols on the cabinet containers.

- 2. These cabinets arrive without shipping skids. A fork lift is not necessary, but one can be used if it lifts from the side of the cabinet.

- 3. When moving the cabinets, push them only on the side indicated by the caution symbols. The casters are locked to facilitate movement in the direction indicated.

- 4. Handle the cabinets carefully to avoid excessive shock.

#### CAUTION

#### Exercise special care when moving cabinets up or down ramps; they may become unstable when tilted more than 10 degrees.

#### 2.1.5 Fire and Safety Precautions

The TS11 does not present unusual or additional fire or safety hazards to an existing computer system. However, check wiring carefully, to ensure that its capacity is adequate for the added load and for any contemplated expansion.

#### 2.1.6 Temperature

The environmental operating temperature of the TS11 may range from 15° to 32° C (59° to 90° F); the maximum gradient is 17° C per hour.

#### 2.1.7 Relative Humidity

Humidity control is very important in a data storage system environment. Static electricity, which varies with humidity, can cause errors in any CPU with memory. The TS11 operates efficiently in a relative humidity range of 20 to 80 percent with a maximum wet bulb temperature of 25° C (77° F) and a minimum dew point of 2° C (36° F).

#### 2.1.8 Heat Dissipation

Heat dissipation of the transport is 900 Btu/hr nominal and 3800 Btu/hr maximum. The approximate cooling requirements for the system can be determined by performing the following calculations. Add the above figure to the maximum heat dissipation for the other system components. Then adjust the results to compensate for such factors as the number of personnel, heat radiation from adjoining areas, sun exposure through windows, system efficiency, etc. A safety margin at least 25 percent above the estimated cooling requirements is suggested.

#### 2.1.9 Acoustics

While most computer sites require some degree of acoustic treatment, the TS11 should not contribute unduly to the overall acoustic problem. However, the acoustic materials at the site should not produce or harbor dust.

### 2.1.10 Altitude

Computer systems may encounter heat dissipation problems at high altitudes. At altitudes over 610 m (2000 ft), the maximum allowable operating temperature is reduced by a factor of  $1.8^{\circ}$  C for each 1000 m (1° F for each 1000 ft). The maximum altitude specified for the transport is 2438 m (8000 ft). Therefore, its maximum allowable operating temperature at 2438 m (8000 ft) would be reduced to 27.60° C (81.7° F).

#### 2.1.11 Radiated Emissions

Radiation sources, such as FM or radar transmitters, in close proximity to the computer system may affect the operation of the processor and some peripheral equipment. The effects of these emissions can be minimized by the following actions.

- 1. Ground window screens and other large metal surfaces.

- 2. Shield interconnecting cables with a grounded shield.

- 3. Provide additional grounding to the system cabinets and chassis.

In environments subject to extreme radiation, the system may require a grounded cage.

#### 2.1.12 Required Tools

In addition to the standard DEC Tool Kit (PN 29-18303), a spirit level is also required for unpacking and installation.

#### 2.2 UNPACKING

The TS11 may be shipped in four variations: as a rackmount version, or three cabinet styles (H960, H9602, or H9646). Unpacking and installation procedures vary with the choice of cabinets.

No matter which variation is chosen for the transport, the device is shipped with all interconnecting cables installed. The M7982 Unibus interface module is delivered in a separate package.

When packaged for shipment, the transport in its cabinet weighs up to 230 kg (500 lbs). Although the package is excessively heavy and bulky for single-person handling, it does not require the use of a forklift or similar equipment to move or lift it.

#### CAUTION

When moving or lifting the transport, always grasp the frame structure. Do not hold any part of the top or side covers.

#### 2.2.1 Rackmount Option

Unpack the rackmount option as follows.

1. Remove the outer shipping container.

#### NOTE

The container may be heavy corrugated cardboard or plywood. In either case, remove any fasteners and cleats securing the container to the skid. If applicable, remove wood framing and supports from the perimeter.

2. Remove the polyethylene cover from the transport. The transport is now ready to be mounted in its cabinet.

#### CAUTION

# The TS11 AA/AB option weighs 68 kg (150 lbs). A minimum of two people are needed to move the transport to its mounting place.

#### 2.2.2 H960 Cabinet Unpacking

Unpack the H960 cabinet as follows.

1. Remove the outer shipping container.

#### NOTE

The container may be heavy corrugated cardboard or plywood. In either case, remove any fasteners and cleats securing the container to the skid. If applicable, remove the wood framing and supports from the cabinet perimeter.

- 2. Remove the polyethylene cover from the cabinet.

- 3. Unbolt the cabinet(s) from the shipping skid. Remove the bolts located on the lower supporting side rails; they are exposed by opening the access door(s).

- 4. Raise the leveling feet above the level of the roll around casters. Refer to Figure 2-4.

- 5. Use wood blocks and planks to form a ramp from the skid to the floor. Carefully roll the cabinet onto the floor.

- 6. Roll the system to the proper location for installation.

Figure 2-4 H960 Cabinet Installation

#### 2.2.3 H9602 Cabinet Unpacking

Unpack the H9602 cabinet as follows.

- 1. Unbolt the bottom protector from the crate at the front, back, and sides. Remove the protector.

- 2. Unbolt and remove the front panel of the crate.

- 3. Slide the sides, back, and top panels off, as one piece.

#### NOTE

Following step 3 will ensure that the cabinet face is not damaged. Do not ship the crating material back to the factory; it can be discarded or retained for reshipping, if reshipping is necessary.

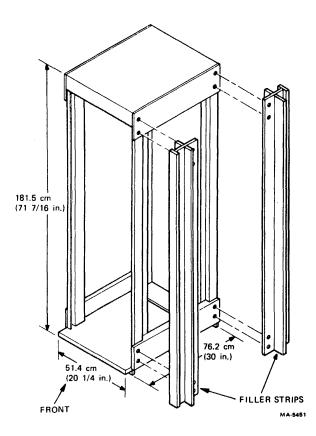

- 4. Ensure that the leveling feet are above the level of the shock isolating casters (Figure 2-5).

- 5. Roll the cabinet(s) to the proper location for installation.

#### 2.2.4 H9646 Cabinet Unpacking

Unpack the H9646 cabinet as follows.

1. Cut the binding straps and remove the bottom foam protector and top cardboard protector.

2. Roll the unit to the proper location for installation.

Figure 2-5 H9602 Cabinet Installation

#### 2.3 INSPECTION

After removing the equipment from its container, inspect it and report any damage to the responsible shipper and the local Digital sales office. Inspect the equipment in the following manner.

- 1. Inspect all switches, indicator/switches, and panels for any obvious damage.

- 2. Open or remove equipment covers, where necessary, and inspect for loose or broken modules, blower or fan damage, and loose nuts, bolts, screws, and cable connections.

- 3. Inspect the wiring side of the logic enclosure panel (motherboard assembly) for bent pins, broken wires, and any foreign material.

- 4. Check the transport for any foreign material that may be lodged in the take-up reel or in other moving parts.

- 5. Check the transport power supply to make sure the fuses and power connectors are seated properly.

#### 2.4 TRANSPORT INSTALLATION AND CABLING

This section provides procedures for installing and cabling the TS11.

#### CAUTION

For all installations, the transport must be adjacent to or bolted to the cabinets in which the M7982 is installed. A ground cable must connect the TS11 frame to the cabinet. This provides shielding for the data cable and reduces local amounts of EMI/RFI from entering the system.

#### 2.4.1 Rackmount Installation

The TS11 AA/AB option can be installed in any standard 19-inch RETMA cabinet. Complete documentation and installation instructions are shipped with the option.

#### CAUTION

The TS11 AA/AB option weighs 68 kg (150 lbs). A minimum of two people are needed to move the transport to its mounting place.

#### NOTE

Some side skins and top covers for this style of cabinet may interfere with service clearances.

#### 2.4.2 H960 Cabinet Installation

Install a TS11 shipped in an H960 cabinet as follows.

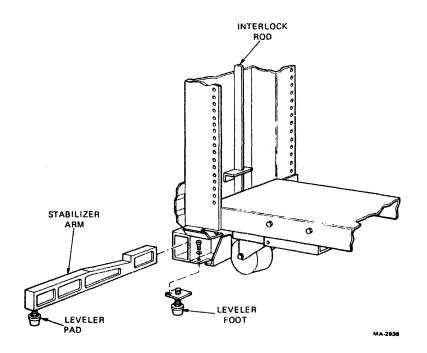

- 1. Lower the leveling feet so that the cabinet is resting on them, not on the roll around casters.

- 2. Use a spirit level to level the cabinet. Make sure that all leveling feet are resting firmly on the floor.

- 3. Remove the shipping screws that secure the equipment to the cabinet.

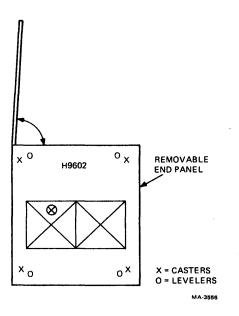

- 4. When this cabinet is bolted to another H960 cabinet, install filler strips (Filler Strip Set, PN H952-GA) between the cabinets as shown in Figure 2-6. Make sure that the notched strip is mounted at the cabinet fronts. Tighten the bolts that secure the cabinets together and then recheck to ensure that the cabinets are level.

- 5. Remove the plastic shipping pin from the top of the cabinet rear access door.

- 6. Install a cabinet ground strap from the transport frame directly to the M7982 mounting box.

- 7. Replace the end panels and doors as needed.

- 8. Install the safety stabilizer legs to the front of the cabinet.

- 9. If necessary, clean all the outer surfaces.

Figure 2-6 H960 Cabinet Filler Strips

### 2.4.3 H9602 Cabinet Installation

This section lists installation procedures for a TS11 shipped in an H9602 cabinet.

2.4.3.1 Cabinet Disassembly – All H9602 cabinets must be dissasembled before installation.

### NOTE

Separate ground straps (10 gauge stranded wire) connect the front panel, end panel, and the back door to the cabinet frame. To completely remove each panel, separate the panel from the frame (instructions below), disconnect the ground strap, and completely remove the panel.

After you remove the shipping crate, disassemble the cabinet as follows.