#### NOTEBOOK SECTION

8.5-15 -

#### **OPTION NUMBER**

2M-C183A-00

#### DRAWING SET NUMBER

#### **PROGRAM NUMBER**

| DOCUMENT NUMBER | REVISION                  |

|-----------------|---------------------------|

|                 | ويرهدون الفكرية فيترافقوه |

|                 |                           |

YM-C183C-00

В

#### DATE

DECEMBER 1981

VSV11/VS11 RASTER GRAPHICS SYSTEM

OPTION DESCRIPTION YM-C183C-00

NASHUA

lst Printing February 1981 2nd Printing (Rev) June 1981 3rd Printing (Rev) December 1

Copyright © 1981 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DECsystem-10 DECSYSTEM-20 DECtape DECwriter DIBOL Digital logo IAS MASSBUS OMNIBUS OS/8 PDP PDT

RSTS RSX SBI UNIBUS VAX/VMS VT

# TABLE OF CONTENTS

| CHAPTER | 1 | INTRODUCT | ION |

|---------|---|-----------|-----|

|         |   |           |     |

| 1.1                                | General Description                                                                                                                                   |                |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 1.2                                | Basic Functional Description                                                                                                                          |                |

| 1.3                                | Option Designations                                                                                                                                   | >              |

| 1.4                                | Specifications                                                                                                                                        | >              |

| 1.4.1                              | Environmental Requirements                                                                                                                            | )              |

| 1.4.2                              | Logic Power Requirements                                                                                                                              | >              |

| 1.4.3                              | Sync Generator (M7 <u>061)</u>                                                                                                                        | <b>}</b>       |

| 1.4.3.1                            | Video Dutput To VT100                                                                                                                                 | .0             |

| 1.4.3.2                            | Monochrome/Green, Red, Blue Video Outputs 1-1                                                                                                         | .0             |

| 1.4.3.3                            | and the second                                      | -              |

| 1.4.3.3                            | Video input & Mixer Requirements 1-1                                                                                                                  | 2              |

| 1. 4. 4                            | Video Input & Mixer Requirements 1-1<br>Image Memory (M7062)                                                                                          | 2              |

|                                    | Image Memory (M7062)                                                                                                                                  | 2              |

| 1.4.4                              | Image Memory (M7062)                                                                                                                                  | 12             |

| 1.4.4<br>1.4.5                     | Image Memory (M7062)1-1Display Processor I/D (M7064)1-1Monitor Specifications1-1                                                                      | 12<br>12<br>13 |

| 1.4.4<br>1.4.5<br>1.4.6            | Image Memory (M7062)       1-1         Display Processor I/D (M7064)       1-1         Monitor Specifications       1-1         VT100-LA/LB       1-1 | 12             |

| 1.4.4<br>1.4.5<br>1.4.6<br>1.4.6.1 | Image Memory (M7062)1-1Display Processor I/D (M7064)1-1Monitor Specifications1-1                                                                      | 2233333        |

# CHAPTER 2 VSV11/VS11 INSTALLATION PROCEDURE

| 2. 1    | Unpacking & Inventory                        |

|---------|----------------------------------------------|

| 2. 2    | System Inspection 2-4                        |

| 2.3     | Equipment Preparation                        |

| 2.4     | Option Installation                          |

| 2. 5    | Checkout                                     |

| 2.6     | Customer Configuration                       |

| 2. 6. 1 | Available Configuration Changes              |

| 2. 6. 2 | Non-Interlaced to Interlaced Conversion 2-62 |

| 2. 6. 3 | Conversion to Dual-Memory System             |

| 2. 6. 4 | Checkout of Changes                          |

| 2.7     | Acceptance                                   |

| 2.8     | Extended Configurations                      |

| 2. 8. 1 | Building Blocks                              |

| 2. 8. 2 | Installation of Extensions                   |

# CHAPTER 3 PROGRAMMING REFERENCE

| 3.1                 | Introduction                      |

|---------------------|-----------------------------------|

| 3. 2                | VSV11/VS11 Programming Concept    |

| <b>3</b> : <b>3</b> | VSV11/VS11 Addressable Registers  |

| 3.3.1               | Display Program Counter (DPC)     |

| 3. 3. 2             | Display Status Register (DSR)     |

| 3.3.2.1             | DSR (Display Status) [Select = 0] |

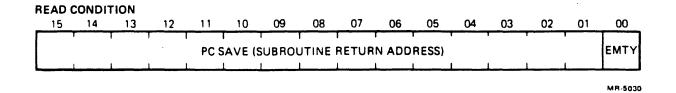

| 3. 3. 2.             | 2  | PCSAVE (Saved DPC From Subroutine)          | . 3-9   |

|----------------------|----|---------------------------------------------|---------|

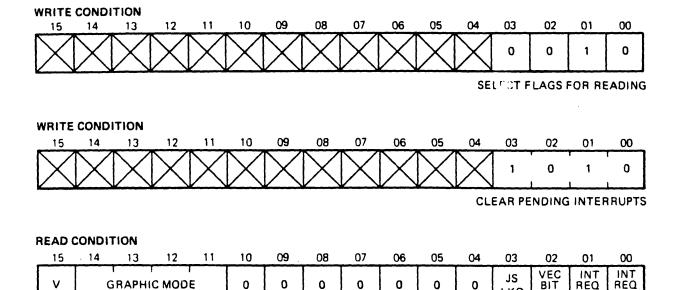

| J. J. 2.             |    | FLAGS (pending Interrupts & Graphic Mode) . |         |

| 2.3.2.               |    | CSR (Control-Status Register)               |         |

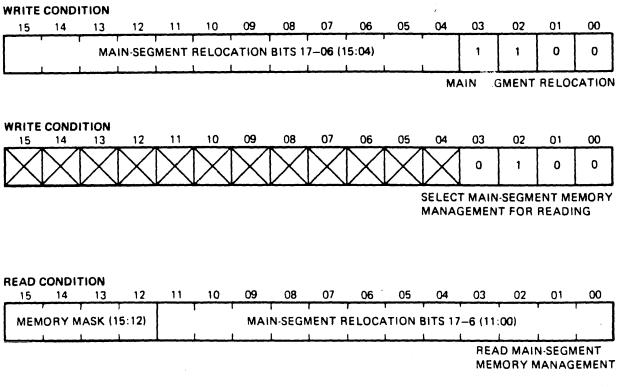

| 3.3.2.               |    | Main-Segment Relocation/Memory Management . |         |

| 3.3.2.               |    | Main-Segment Protection Mask/HBASE Read     |         |

| 3.3.2.               |    | Auxiliary-Segment Relocation/Memory Mgmt    |         |

| 3.3.2.               |    | Auxiliary-Segment Protection Mask/CBASE     |         |

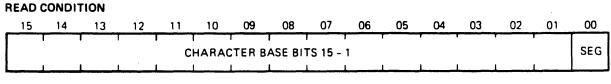

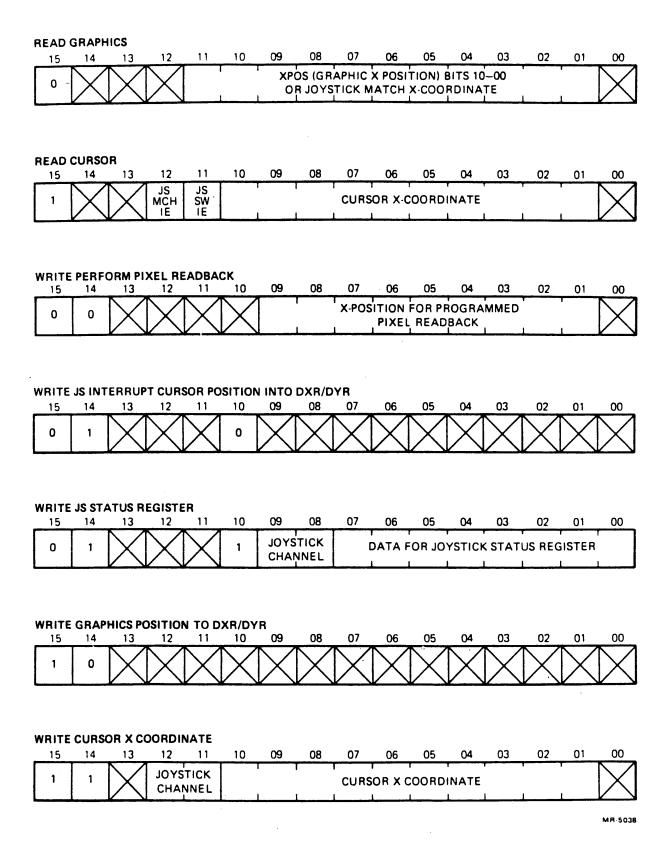

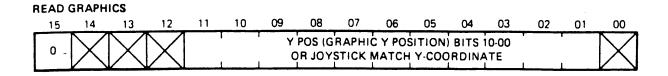

| 3.3.3                | -  | X-Status Register (DXR)                     |         |

| 3.3.4                |    | Y-Status Register (DYR)                     |         |

| 3.4                  |    | Interrupts                                  |         |

| 3.4.1                |    | STOP Interrupt                              |         |

| 3.4.2                |    | CURSOR MATCH Interrupt                      |         |

| 3.4.3                |    | ERROR Interrupt                             |         |

| 3.4.4                |    | JOYSTICK SWITCH Interrupt                   |         |

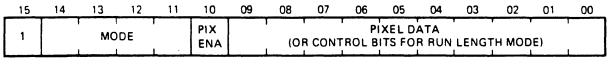

| 3.5                  |    | VSV11/VS11 Instruction Set                  |         |

| 3.5.1                |    | GRAPHIC MODE Instructions                   |         |

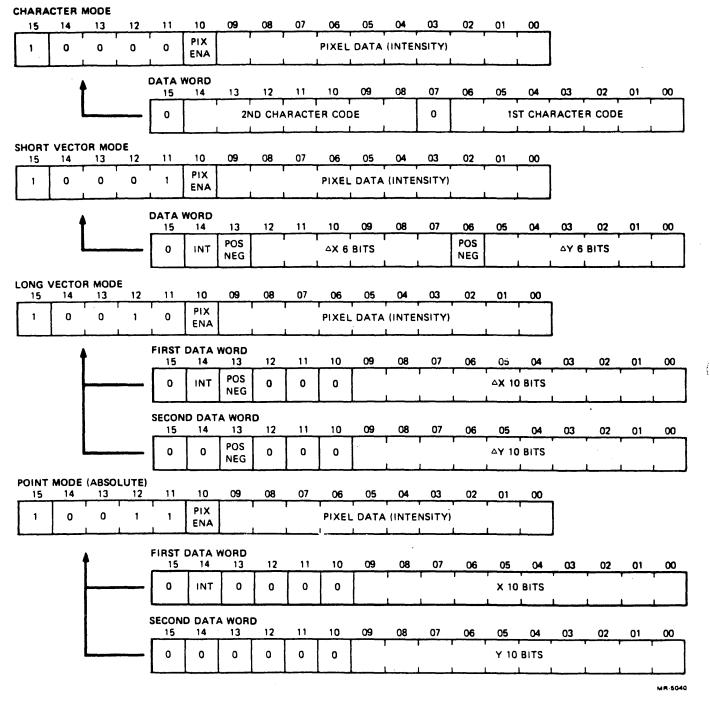

| 3.5.1.               | 1  | CHARACTER Mode                              |         |

| 3. 5. 1.             |    | SHORT VECTOR Mode                           |         |

| 3. 5. 1.             |    | LONG VECTOR Mode                            |         |

| 3. 5. 1.             |    | ABSOLUTE POINT Mode                         |         |

| 3. 5. 1.             |    | GRAPH/HISTOGRAM X Mode                      |         |

| 3. 5. 1.             |    | GRAPH/HISTOGRAM Y Mode                      |         |

| 3. 5. 1.             |    | RELATIVE POINT Mode                         |         |

| 3. 5. 1.             |    | RUN-LENGTH Mode                             |         |

| 3. 5. 2              | 0  | Control Instructions                        |         |

| 3. 5. 2.             | 1  | Joystick Status                             |         |

| 3. 5. 2.             |    | Load Extended Joystick Control              |         |

| 3. 5. 2.             |    |                                             |         |

| 3. 5. 2.<br>3. 5. 2. |    | Write Cursor Coordinates                    |         |

|                      |    | Set Histogram Base                          |         |

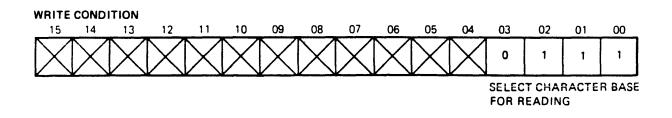

| 3. 5. 2.             |    | Set Character Base                          |         |

| 3. 5. 2.             |    | Display Jump                                |         |

| 3. 5. 2.             |    | Display Jump-to-Subroutine                  |         |

| 3. 5. 2.             | _  |                                             |         |

| 3. 5. 2.             | -  |                                             |         |

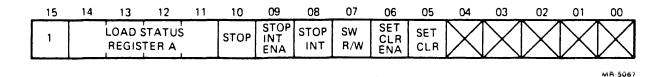

| 3. 5. 2.             |    | Luad Status Register A                      |         |

| 3. 5. 2.             |    | Load Status C                               |         |

| 3. 5. 2.             |    | Load Graphplot Increment                    |         |

| 3. 5. 2.             |    | Load Pixel-Data Inhibit                     |         |

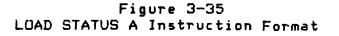

| 3. 5. 2.             | 14 | Marker No-op                                |         |

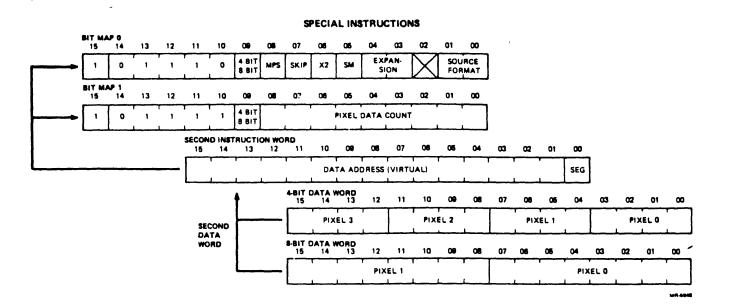

| 3. 5. 3              |    | Special Instructions                        |         |

| 3. 5. 3.             |    | Bit Map O                                   |         |

| 3. 5. 3.             |    | Bit-Map-1                                   |         |

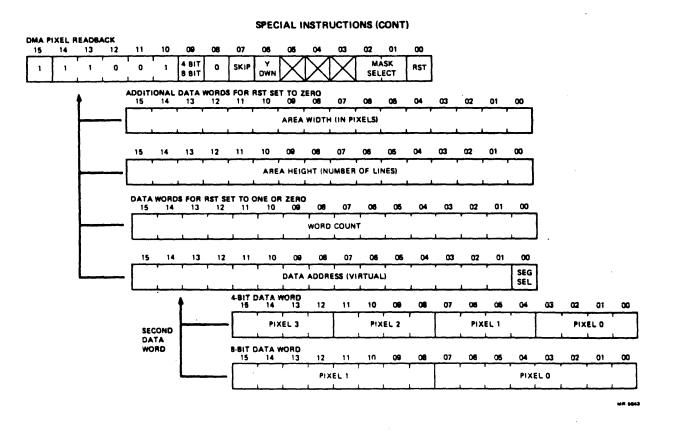

| 3. 5. 3.             | З  | DMA Pixel Readback                          | . 3-100 |

| 3.6                  |    | Host Memory Display File Make-Up            | . 3-106 |

|                      |    |                                             |         |

# CHAPTER 4 M7064 DISPLAY PROCESSOR TECHNICAL DESCRIPTION

| 4.1     | Introduction             | -1 |

|---------|--------------------------|----|

| 4. 2    | General Description      |    |

| 4.3     | Functional Description   | .3 |

| 4.3.1   | LSI-11 Bus Interface     |    |

| 4.3.1.1 | Programmed-I/O Transfers |    |

| 4.3.1.2 | DMA (Direct Memory Access) Transfers 4-8 |

|---------|------------------------------------------|

| 4.3.1.3 | Interrupt Generation                     |

| 4.3.2   | Bit-Slice Microprocessor Data Paths      |

| 4.3.2.1 | 2901A Bit-Slice Array                    |

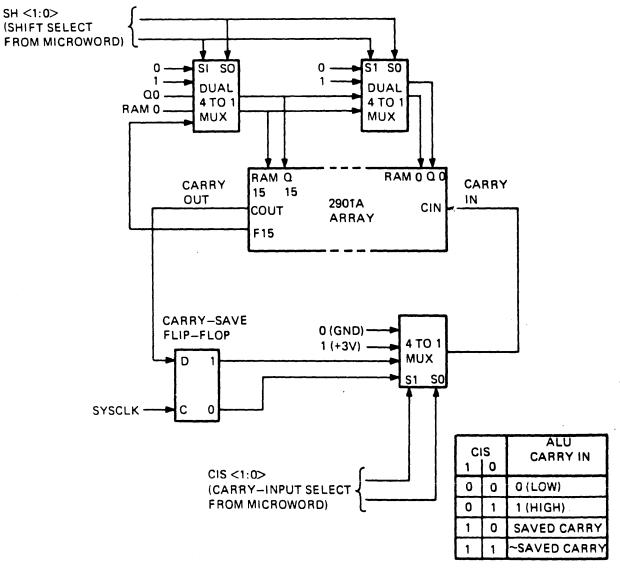

| 4.3.2.2 | Carry-Input and Shift Linkage            |

| 4.3.2.3 | Scratchpad RAM                           |

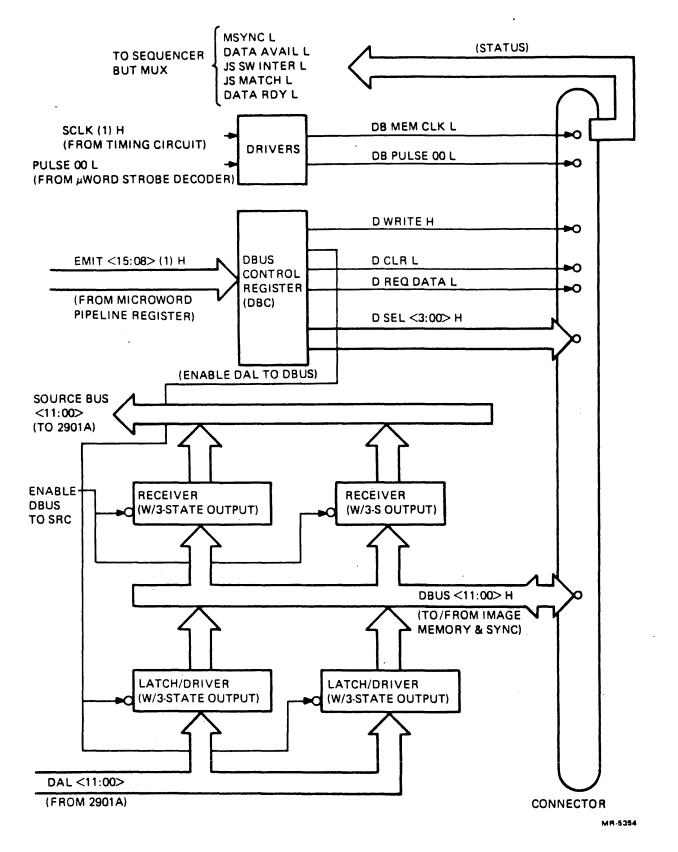

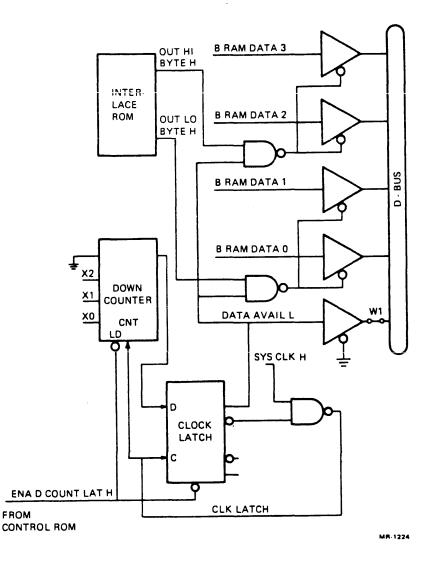

| 4.3.3   | DBUS Interface                           |

| 4.3.3.1 | DBUS Data Drivers and Receivers          |

| 4.3.3.2 | DBUS Control Register (DBC)              |

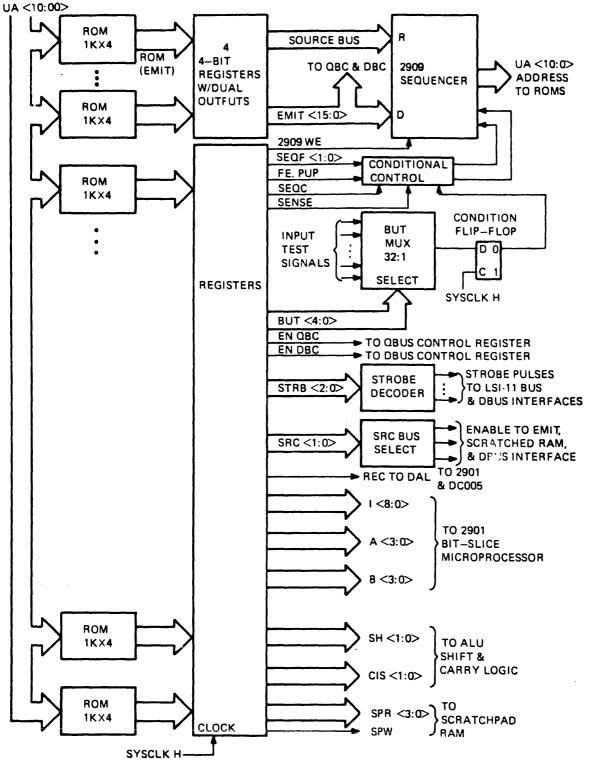

| 4.3.4   | Control ROM, Sequencer and Timing        |

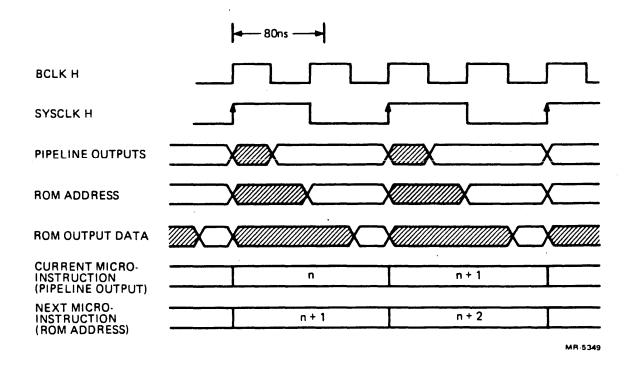

| 4.3.4.1 | Basic Machine Cycle Timing               |

| 4.3.4.2 | Microprogram Sequencing                  |

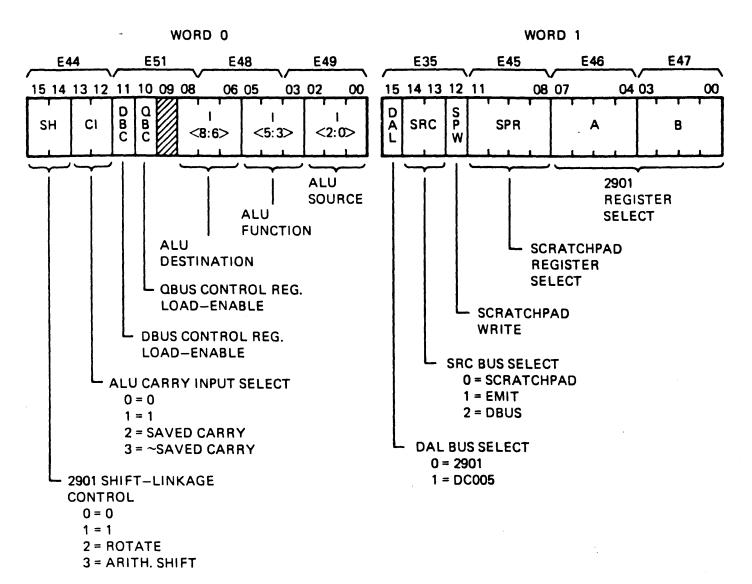

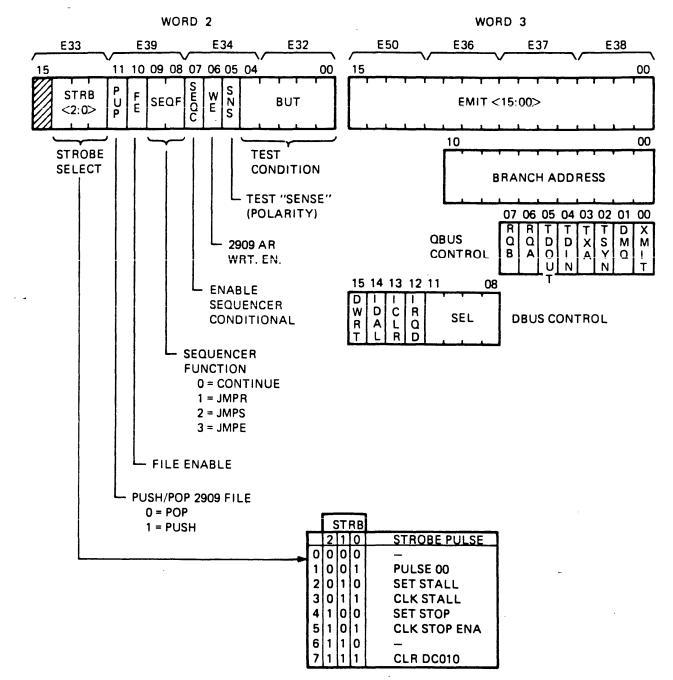

| 4.3.4.3 | Microword Format                         |

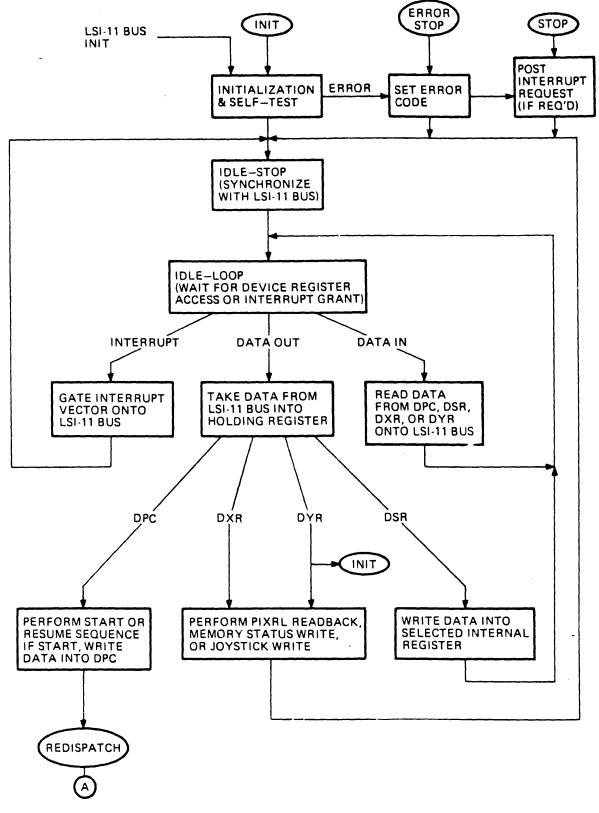

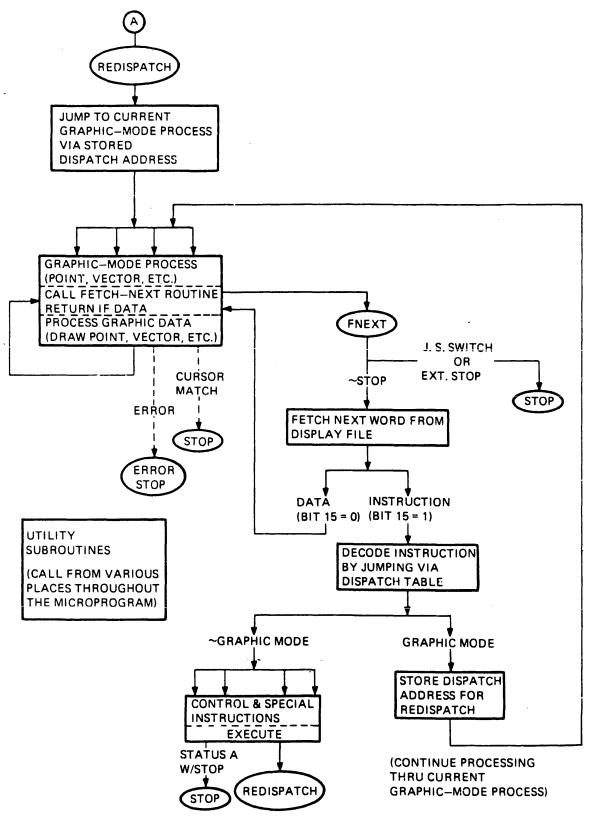

| 4.4     | Microprogram Overview                    |

| 4.4.1   | Initialization and Self-Test             |

| 4.4.2   | Idle-Stop Sequence                       |

| 4.4.3   | Idle Loop                                |

| 4.4.4   | Data Out Sequence                        |

| 4.4.5   | Data In Sequence                         |

| 4.4.6   | Display Processing                       |

| 4.4.7   | Utility Subroutines                      |

# CHAPTER 5 M7062 IMAGE MEMORY TECHNICAL DESCRIPTION

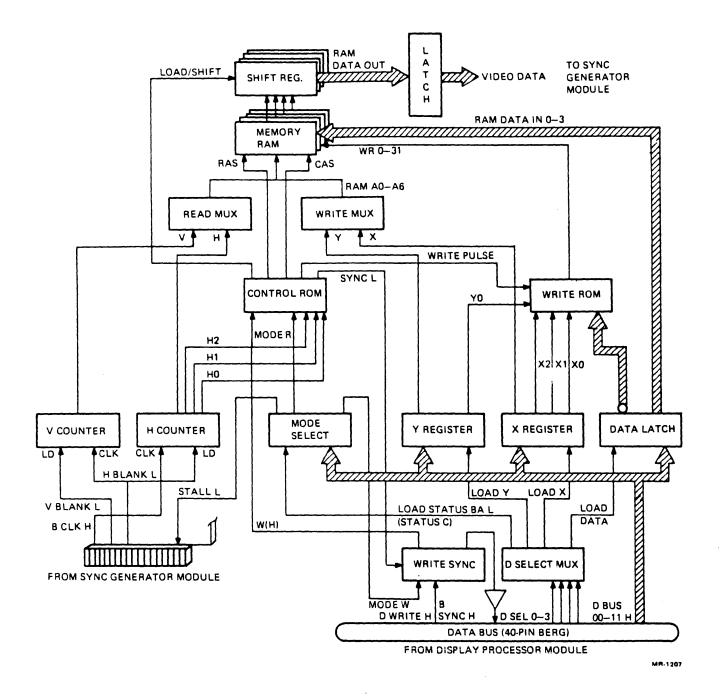

| 1  | Introduction                       |

|----|------------------------------------|

| 2  | General Description                |

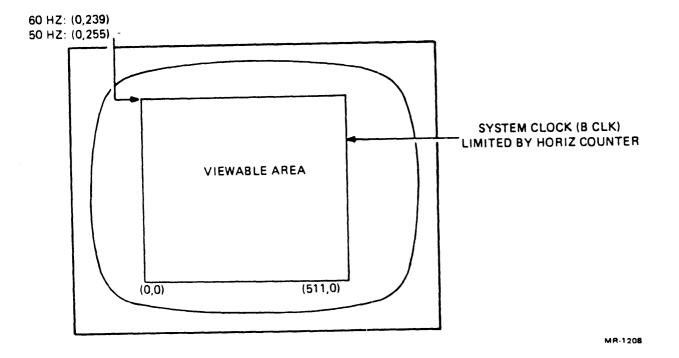

| З  | System Clock                       |

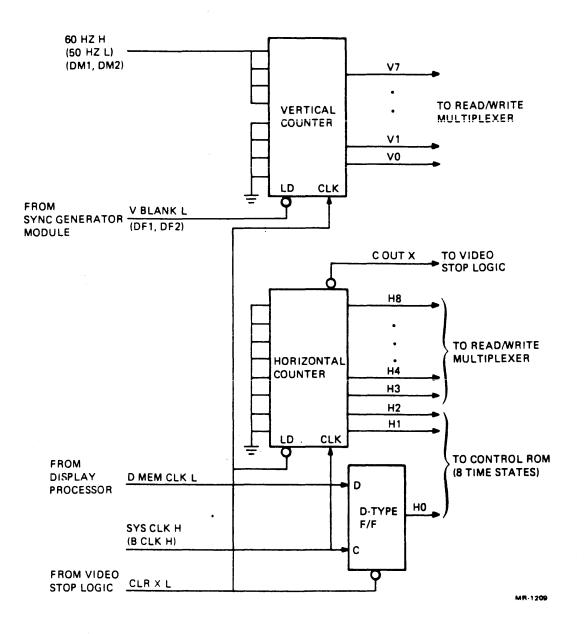

| 4  | Horizontal And Vertical Counters   |

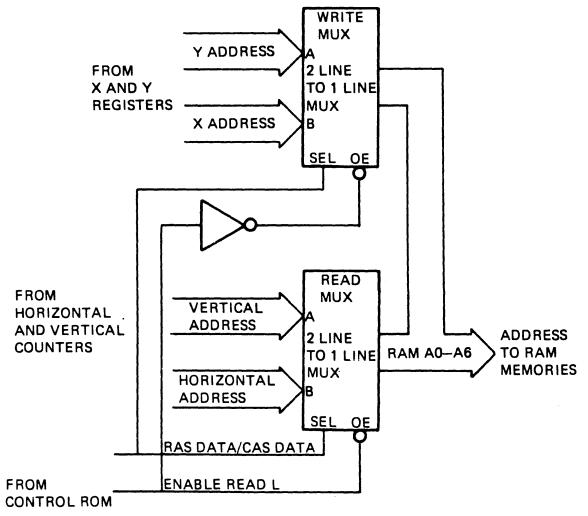

| 5  | Read/Write Multiplexer             |

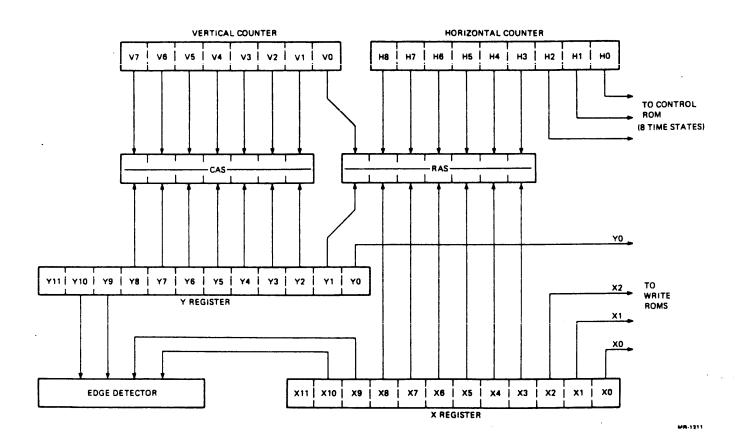

| 6  | RAS and CAS Memory Address         |

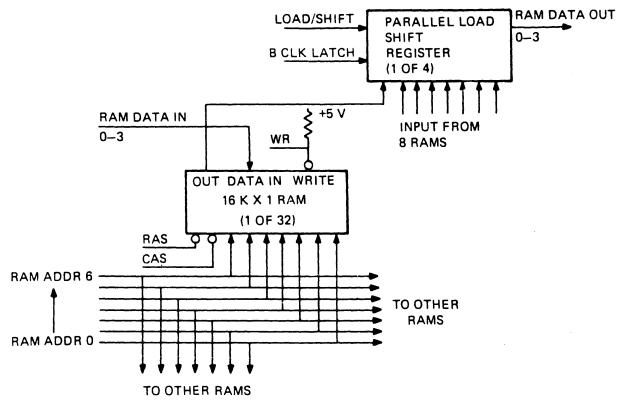

| 7  | Memory And Shift Register          |

| 8  | Video Data Out                     |

| 9  | Data Bus (DBUS)                    |

| 10 | D Select Multiplexer (Decoder)     |

| 11 | Data Latch                         |

| 12 | X and Y Registers                  |

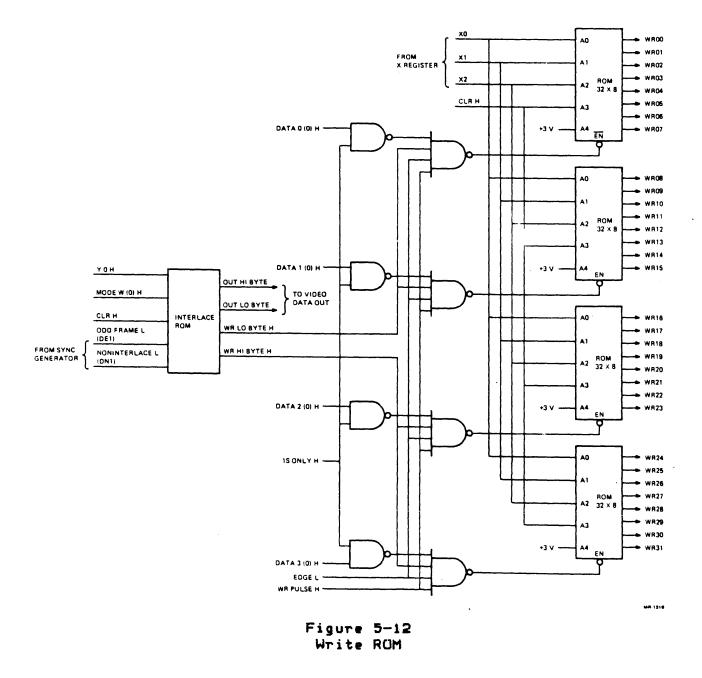

| 13 | Write ROM                          |

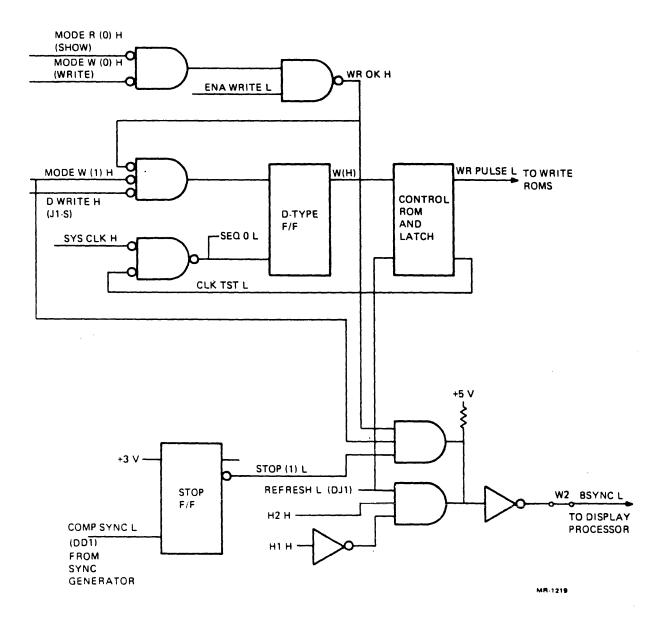

| 14 | Write Synchronization Logic        |

| 15 | Video Stop Logic                   |

| 16 | Mode Select Logic (Load Status BA) |

| 17 | Control ROM and Timing             |

| 18 | Pixel Read-Back Logic              |

|    | 23456789011123145167               |

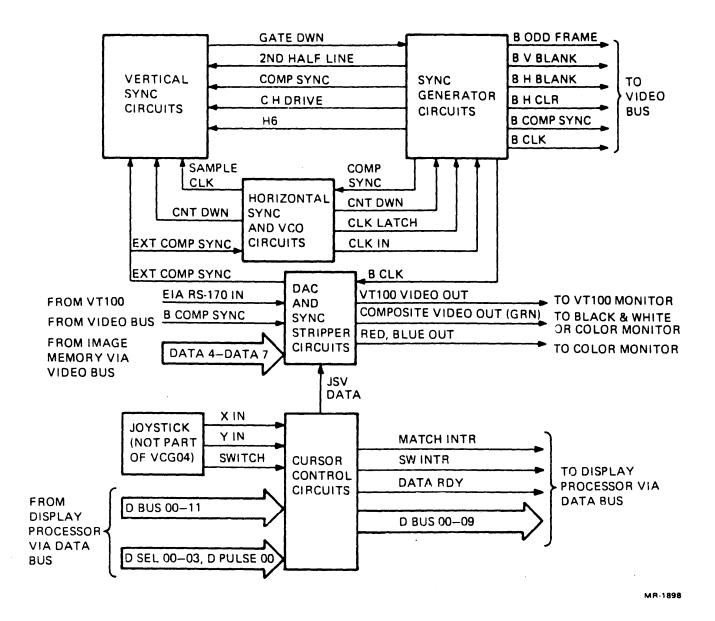

# CHAPTER 6 M7061 SYNC GENERATOR/CURSOR CONTROL DESCRIPTION

| Introduction           |                                                                                                                        |                                                                                                                          |                                                                                                                        |                                                                                                                        |                     |                     |                     |                     |                     |                     |                     | 6-1          |

|------------------------|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|--------------|

|                        |                                                                                                                        |                                                                                                                          |                                                                                                                        |                                                                                                                        |                     |                     |                     |                     |                     |                     |                     |              |

| Functional Description |                                                                                                                        |                                                                                                                          |                                                                                                                        |                                                                                                                        |                     |                     |                     |                     |                     |                     |                     | 6-4          |

|                        |                                                                                                                        |                                                                                                                          |                                                                                                                        |                                                                                                                        |                     |                     |                     |                     |                     |                     |                     |              |

|                        |                                                                                                                        |                                                                                                                          |                                                                                                                        |                                                                                                                        |                     |                     |                     |                     |                     |                     |                     |              |

|                        |                                                                                                                        |                                                                                                                          |                                                                                                                        |                                                                                                                        |                     |                     |                     |                     |                     |                     |                     |              |

|                        |                                                                                                                        |                                                                                                                          |                                                                                                                        |                                                                                                                        |                     |                     |                     |                     |                     |                     |                     |              |

|                        | General Description<br>Functional Description<br>Scanning Techniques<br>Non-Interlaced Scanning<br>Interlaced Scanning | General Description<br>Functional Description<br>Scanning Techniques<br>Non-Interlaced Scanning .<br>Interlaced Scanning | General Description<br>Functional Description<br>Scanning Techniques<br>Non-Interlaced Scanning<br>Interlaced Scanning | General Description<br>Functional Description<br>Scanning Techniques<br>Non-Interlaced Scanning<br>Interlaced Scanning | General Description | Introduction |

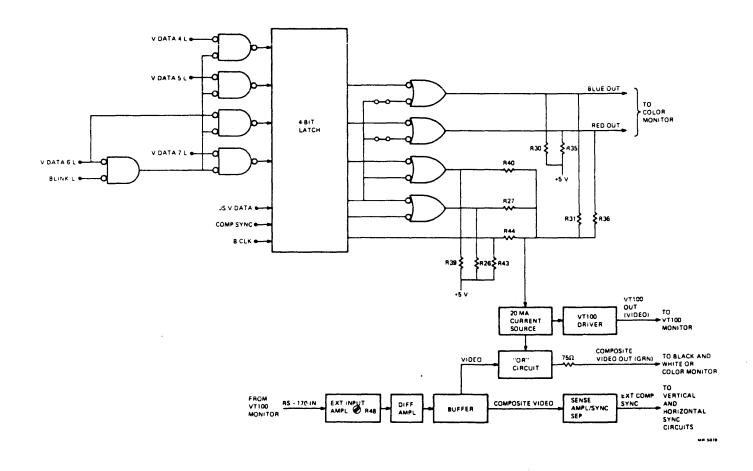

| 6. 3. 3    | DAC and SYNC Stripper Circuits                 |   |

|------------|------------------------------------------------|---|

| 6. 3. 3. 1 | DAC Circuits                                   | ŀ |

| 6. 3. 3. 2 | Sync Stripper Circuits                         | 5 |

| 6. 3. 4    | Horizontal Sync and VCO Circuits               | 5 |

| 6.3.5      | Vertical Sync Circuits                         | 1 |

| 6.3.6      | Cursor Control Circuits                        | ) |

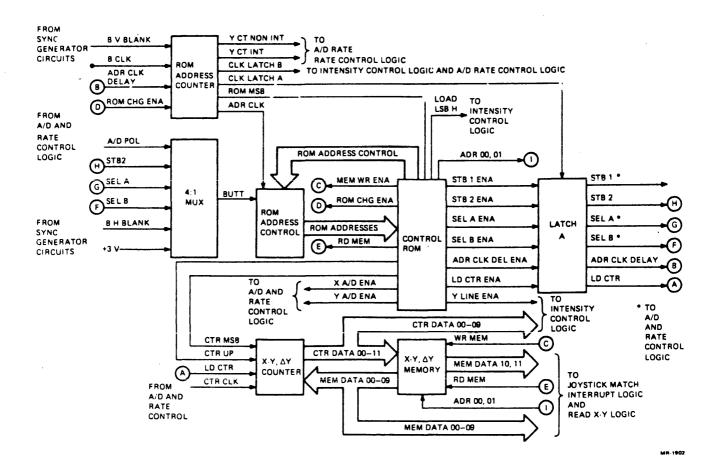

| 6.3.6.1    | Control ROM and X-Y, Delta-Y Memory Logic 6-20 | ) |

| 6.3.6.2    | Intensity Control Logic                        | 2 |

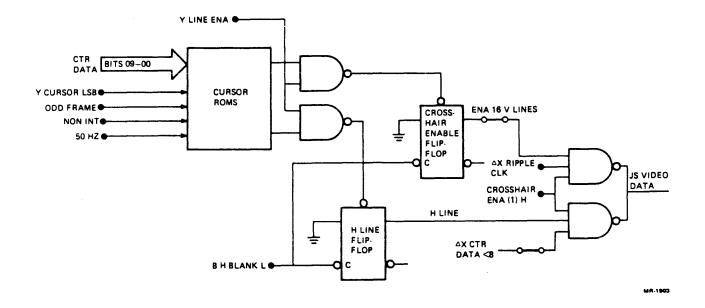

| 6. 3. 6. 3 | A/D Rate Control Logic                         | ŀ |

| 6. 3. 6. 4 | JS Address Decode/Switch Interrupt Logic 6-26  | 2 |

| 6.3.6.5    | Read X-Y Logic                                 | 3 |

| 6.3.6.6    | Joystick Match Interrupt Logic                 | ) |

| 6. 3. 6. 7 | Load X-Y Logic                                 | ) |

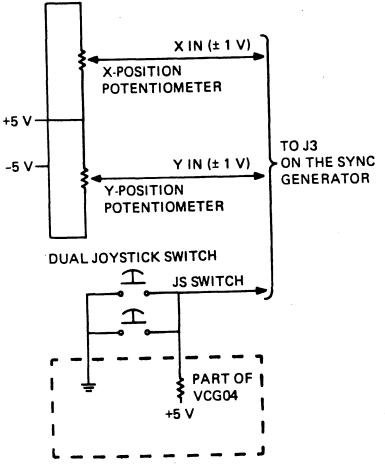

| 6.3.7      | H3060 Joystick                                 | L |

| 6. 3. 8    | 5 V Converter                                  | 3 |

| 6.3.9      | Video Bus                                      | 3 |

# CHAPTER 7 MAINTENANCE

| 7.1   | INTRODUCTION                               | 7-i  |

|-------|--------------------------------------------|------|

| 7.2   | TOOLS and TEST EQUIPMENT                   | 7-1  |

| 7.3   | TEST PROGRAMS                              | 7-2  |

| 7.3.1 | DEC/X11 System Exerciser                   | 7-2  |

| 7.3.2 | VAX/VMS Level 2 Diagnostic (EVTCA)         |      |

| 7.3.3 | VSV11/VS11 Option (Standalone) Diagnostics | 7-2  |

| 7.4   |                                            |      |

| 7.5   | M7061 SYNC ADJUSTMENT USING OSCILLOSCOPE   | 7-30 |

# APPENDIX A PARTS/DATA SHEETS

| A. 1         | VS11-AA, -AB Parts/Data Sheet  |

|--------------|--------------------------------|

| A. 2         | VS11-AC, -AC Parts/Data Sheet  |

| A. 3         | VS11-AE, -AF Parts/Data Sheet  |

| A. 4         | VS11-AH, -AJ Parts/Data Sheet  |

| A. 5         | VS11-AP, -AR Parts/Data Sheet  |

| <b>A</b> . 6 | VS11-AS, -AT Parts/Data Sheet  |

| A. 7         | VSV11-AA, -AB Parts/Data Sheet |

| A. 8         | VSV11-AC, -AD Parts/Data Sheet |

| <b>A</b> . 9 | VSV11-AE, -AF Parts/Data Sheet |

| A. 10        | VSV11-AH, -AJ Parts/Data Sheet |

| A. 11        | VSV11-AP, -AR Parts/Data Sheet |

| A. 12        | VSV11-AS, -AT Parts/Data Sheet |

# APPENDIX B VRV02-BA/BB 20mA to EIA CONVERSION

APPENDIX C VT100/VRV02 SETUP and OPERATOR INFORMATION

# Figures

| 1-1          | VSV11/VS11 Graphics System Block Diagram           | 1-4  |

|--------------|----------------------------------------------------|------|

| 1-2          | Composite Video Output Waveform                    | 1-14 |

| 1-3          | Composite Video Test Setup                         | 1-14 |

| 1-4          | External Video Input Registration                  | 1-15 |

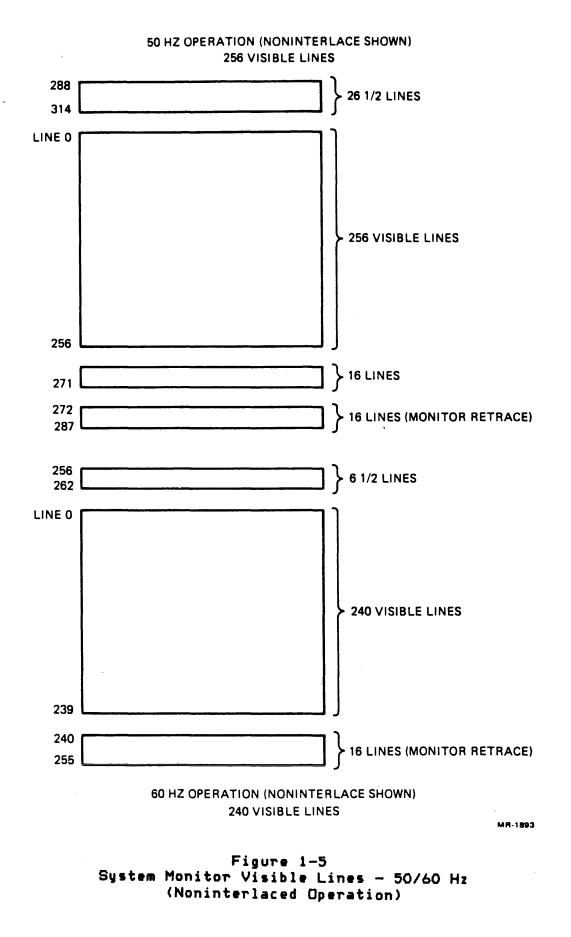

| 1-5          | System Monitor Visible Lines - 50/60 Hz            | 1-16 |

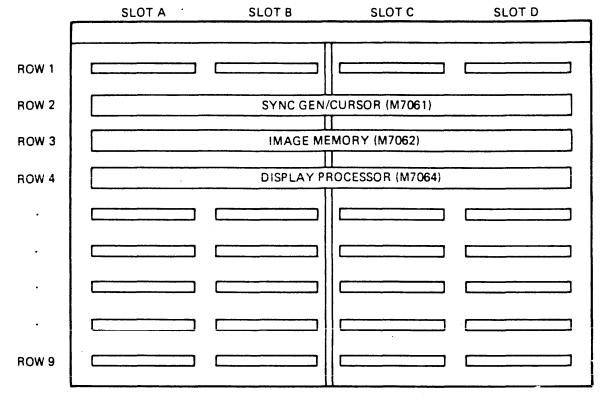

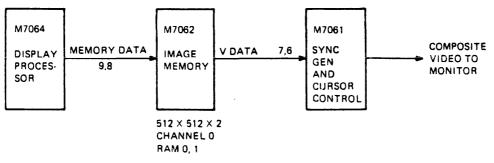

| 2-1          | Single-Memory Non-Interlaced Block Diagram         | 2-3  |

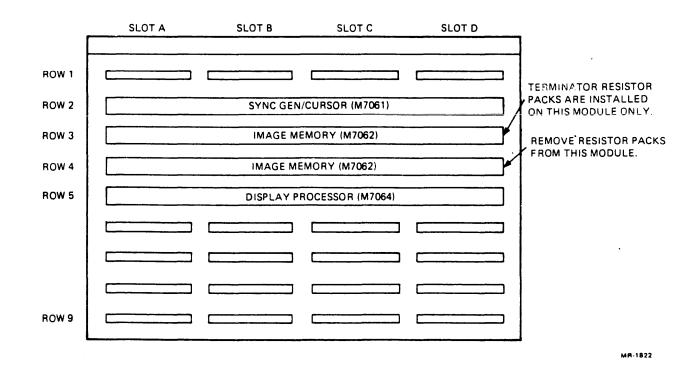

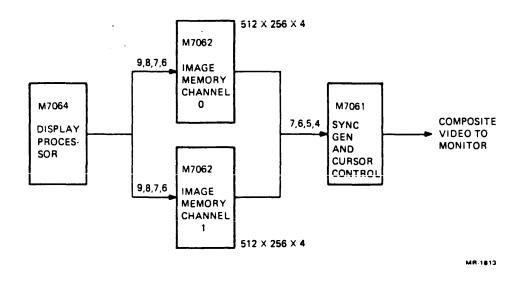

| 2-2          | Two-Memory Interlaced Block Diagram                | 2-3  |

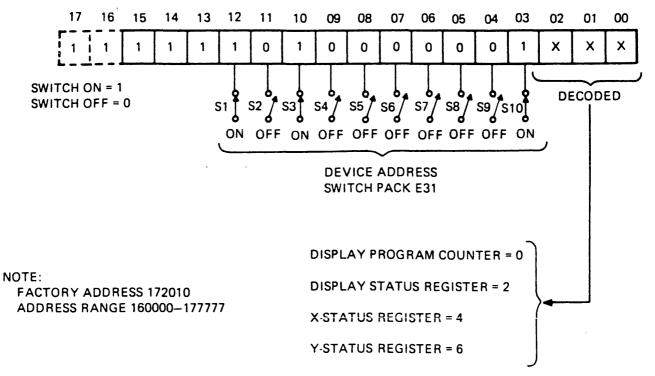

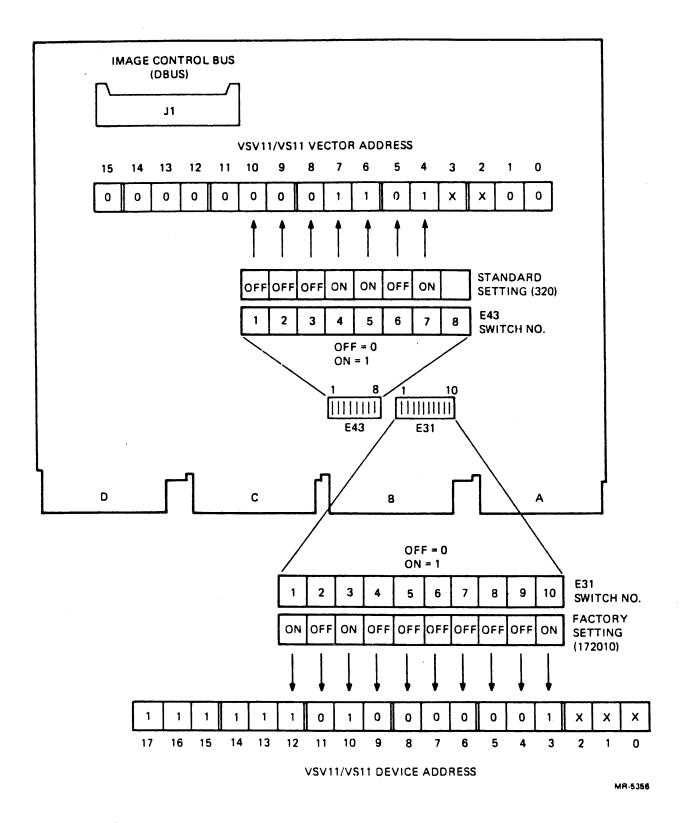

| 2-3          | Device Address Selection                           | 2-11 |

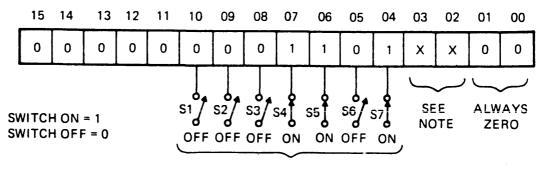

| 2-4          | Vector Address Selection                           | 2-11 |

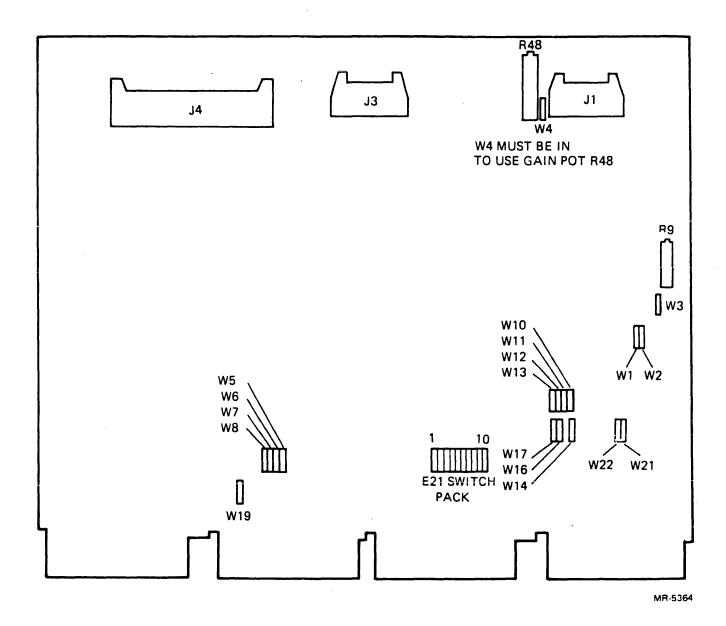

| 2- 5         | M7064 Display Processor Module                     | 2-12 |

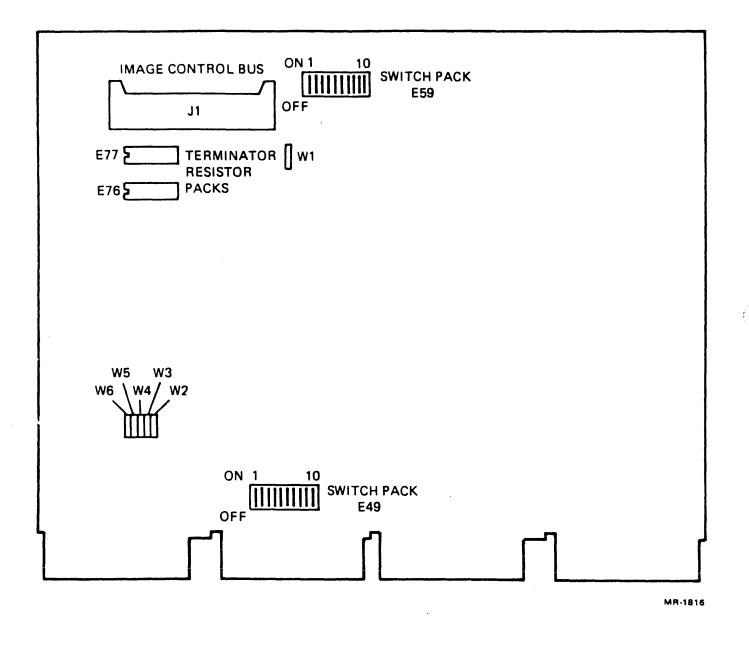

| 2- 6         | M7062 Image Memory Module                          | 2-14 |

| 2-7          | M7061 Sync Generator Module                        | 2-17 |

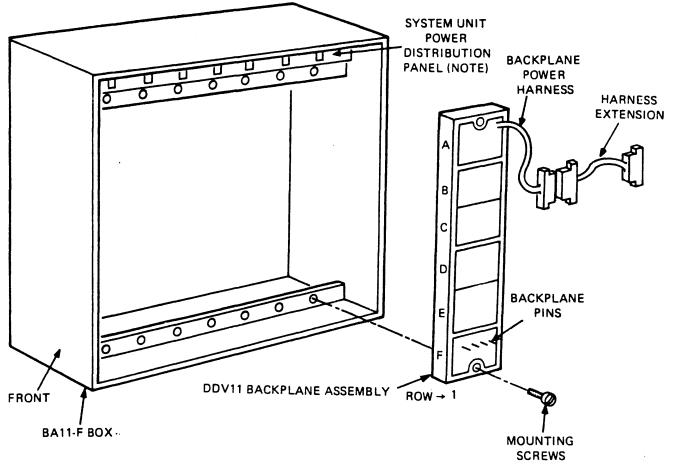

| 2-8          | Installing DDV11-CK Backplane Into BA11-F Box      |      |

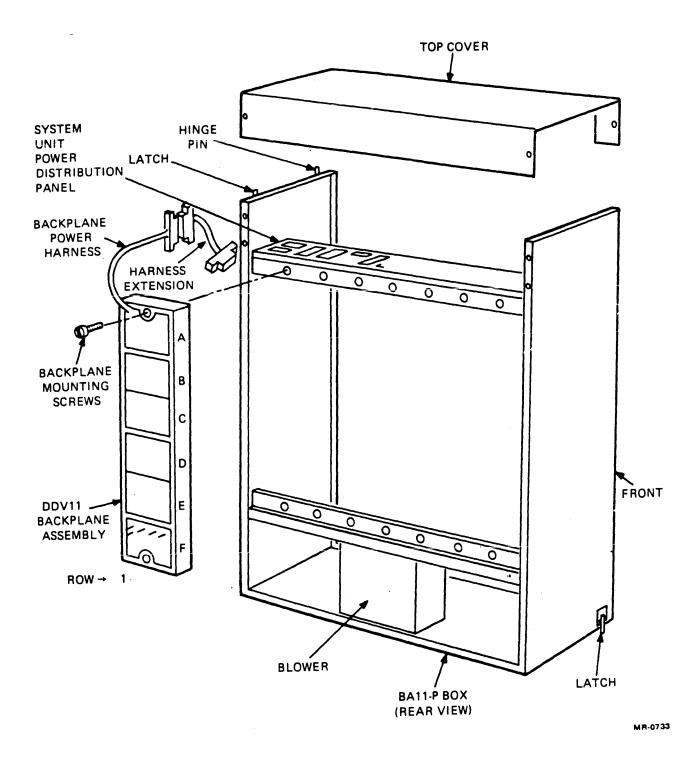

| 2-9          | Installing DDV11-CK Backplane Into BA11-P Box      | 2-29 |

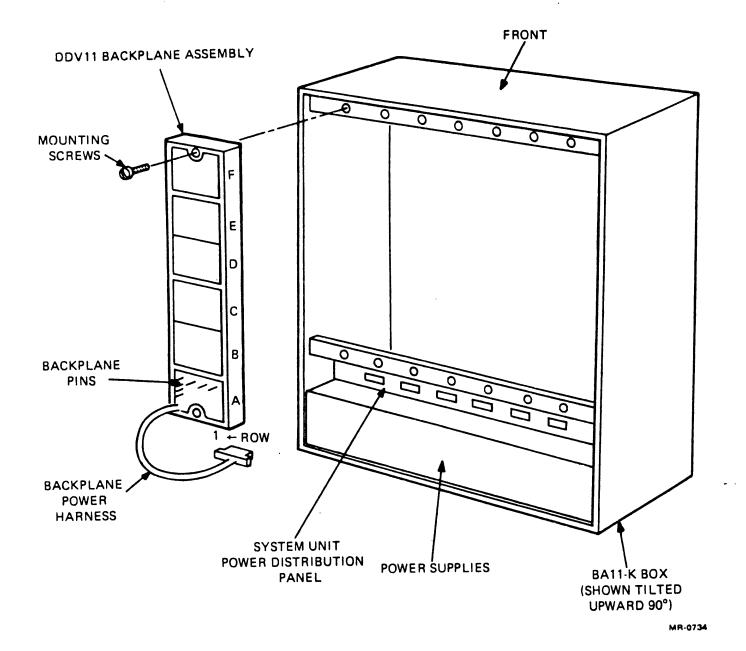

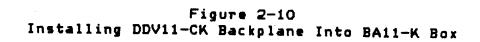

| 2-10         | Installing DDV11-CK Backplane Into BA11-K Box      | 2-30 |

| 2-11         | Installing DDV11-CK Backplane Into BA11-L Box      | 2-31 |

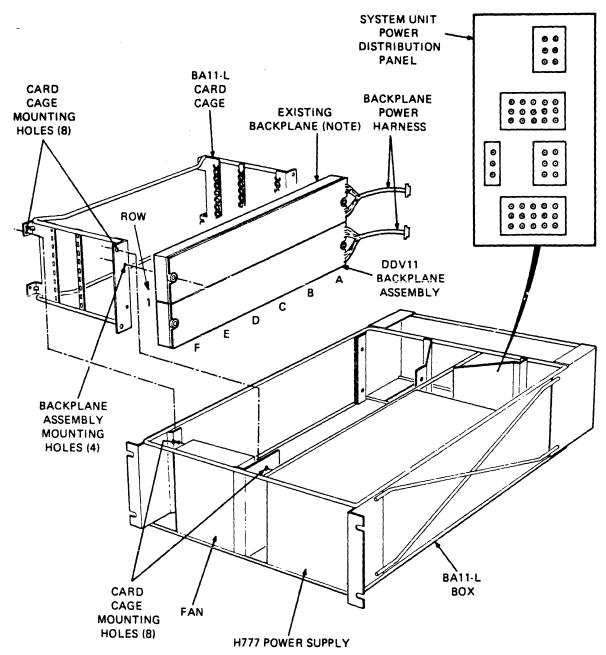

| 2-12         | VS11 Graphic System Basic Configuration            | 2-32 |

| 2-13         | H9273-A Backplane Connectors                       | 2-35 |

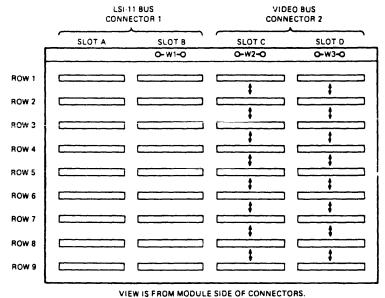

| 2-14         | DDV11-CK Backplane Connectors                      | 2-35 |

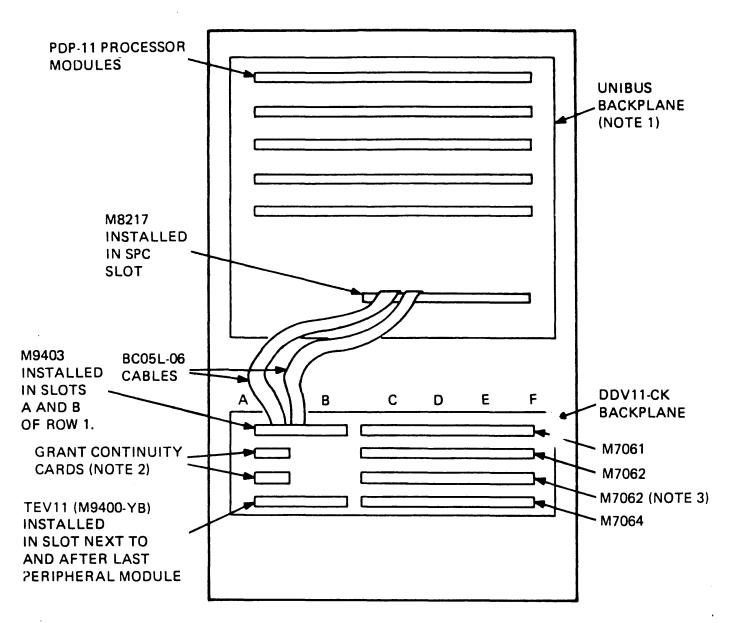

| 2-15         | VS11 Graphic System 2-Memory Configuration         |      |

| 2-16         | VSV11 Graphic System Basic Module Configuration    |      |

| 2-17         | VSV11 Graphic System 2-Memory Module Config        |      |

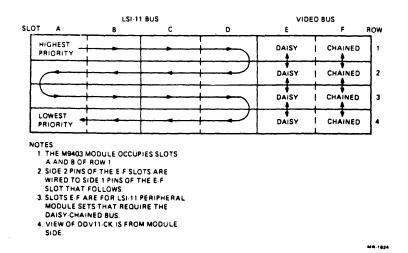

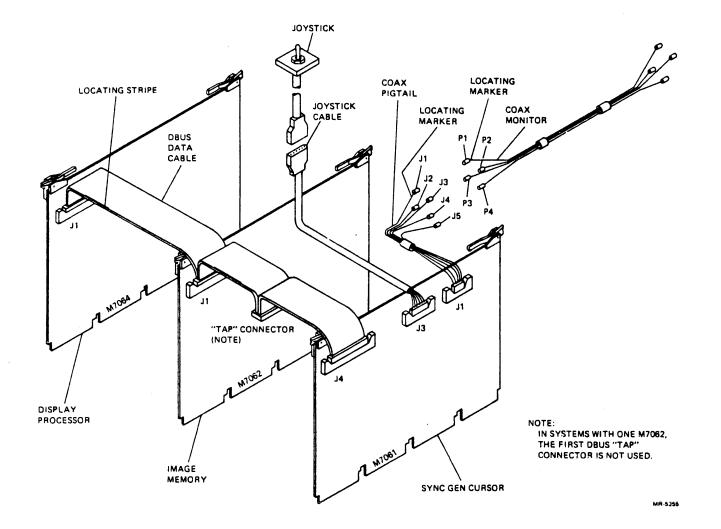

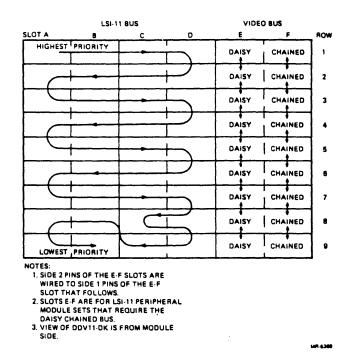

| 2-18         | VS11/VSV11 Module Set Arrangement                  |      |

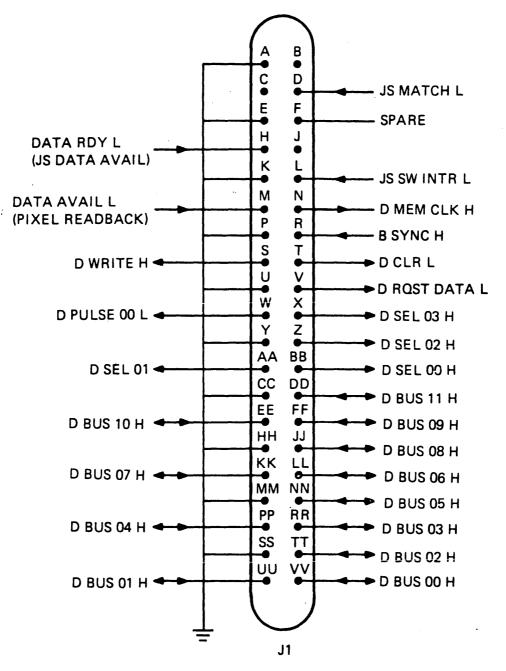

| 2-19         | DBUS Connector Pin Assignments                     |      |

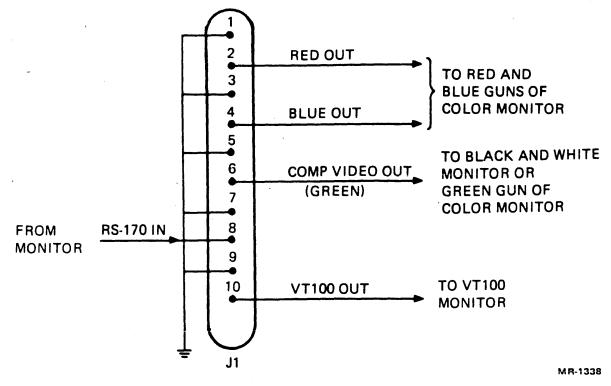

| 2-20         | M7061 Video Connector J1 Pinning                   |      |

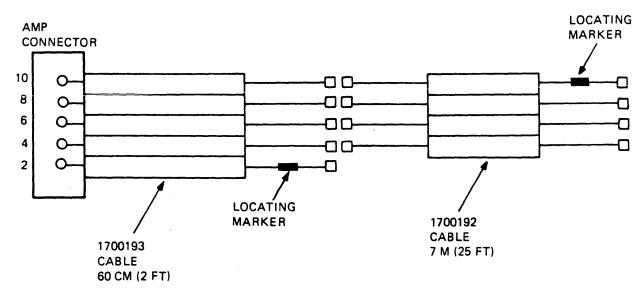

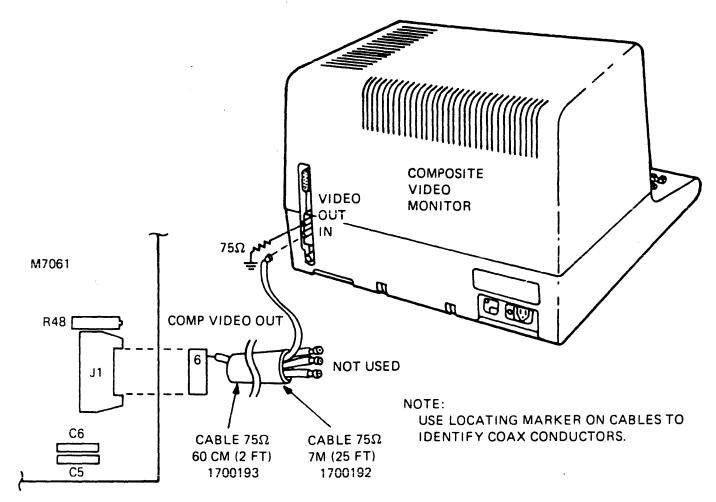

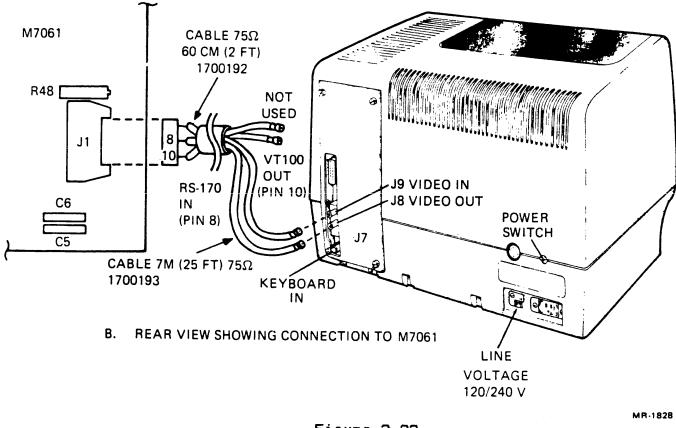

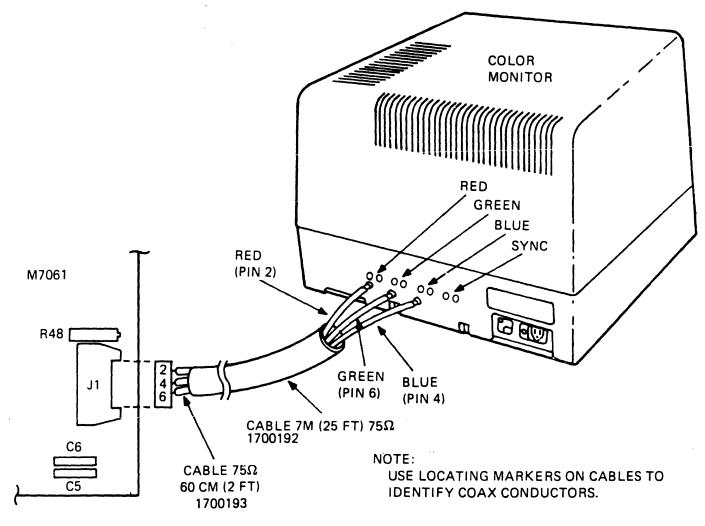

| 2-21<br>2-22 | Video Cables                                       | 2-41 |

| 2-22         | VT100-LA/LB Monochrome Monitor Installation        |      |

| 2-23         | VRVO2-BA/BB Color Monitor Installation             |      |

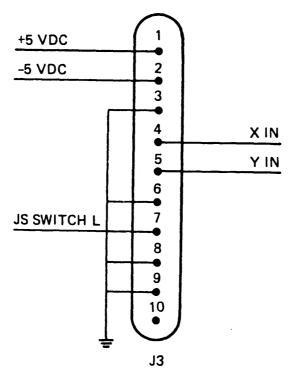

| 2-24         | Joystick Connector Pin Assignments                 |      |

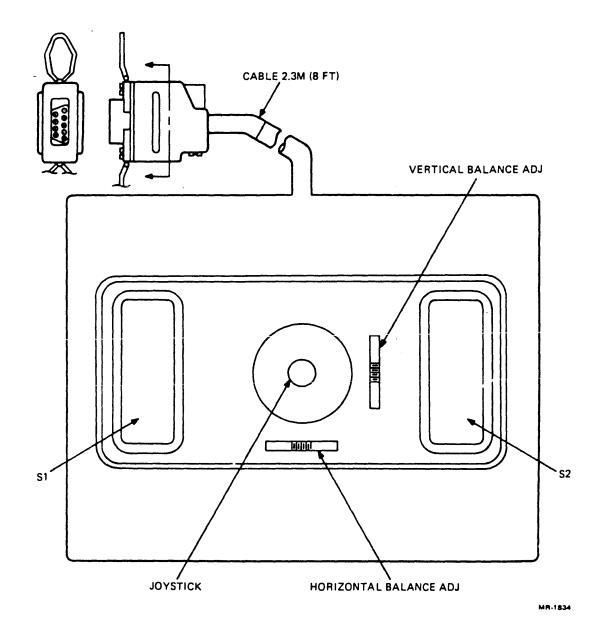

| 2-25         | H3060 Joystick Assembly                            |      |

| 2-28         | Single Interlaced Memory Block Diagram             |      |

| 2-28         | Dual-Channel Non-Interlaced Memory Block Diagram   |      |

| 2-29         | DDV11-DK 9-Slot Backplane                          |      |

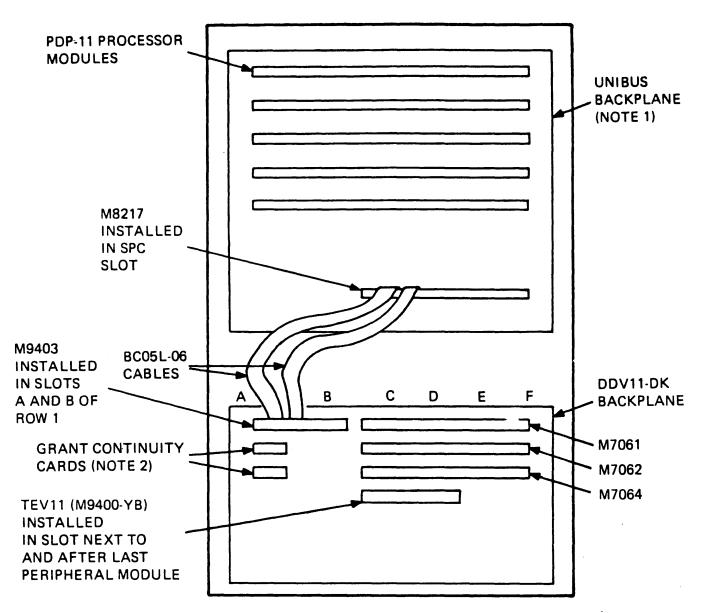

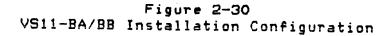

| 2-30         | VS11-BA/BB Installation Configuration              | 2-70 |

| 2-31         | VS11-BA/BB w/VSV11-MA Installation Configuration   |      |

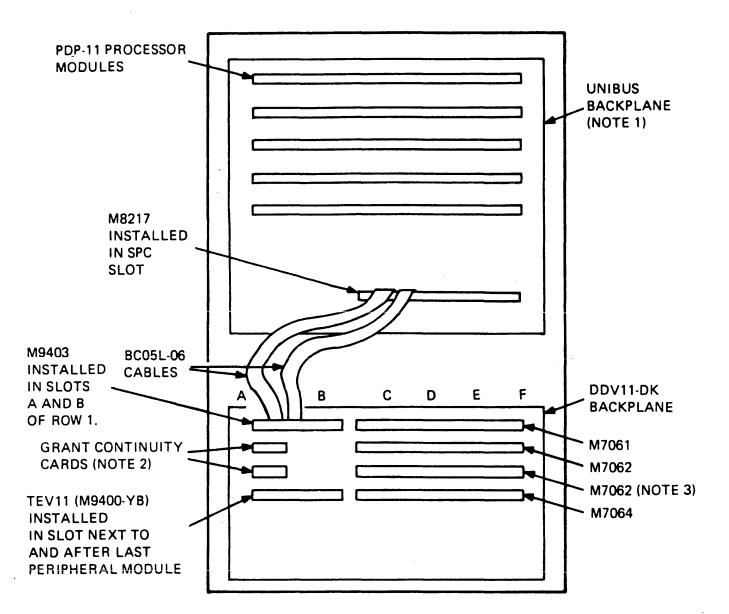

| 2-32         | VSV11 System w/ Two Independent Monitors           |      |

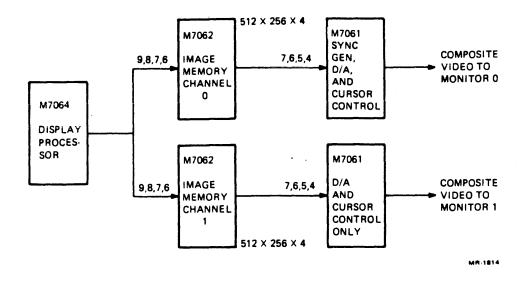

| 2-33         | Module Arrangement for 2-Monitor System            |      |

| 3-1          | Display Program Counter (DPC)                      |      |

| 3-2          | DSR Register Bit Configuration                     |      |

| 3-3          | PCSAVE/DSR Select=1 Register Configuration         |      |

| 3-4          | FLAGS/DSR - Select=2 Register Configuration        |      |

| 3-5          | CSR Register Configuration                         |      |

| 3-6          | Main-Segment Relocation/Memory Management Reg.     |      |

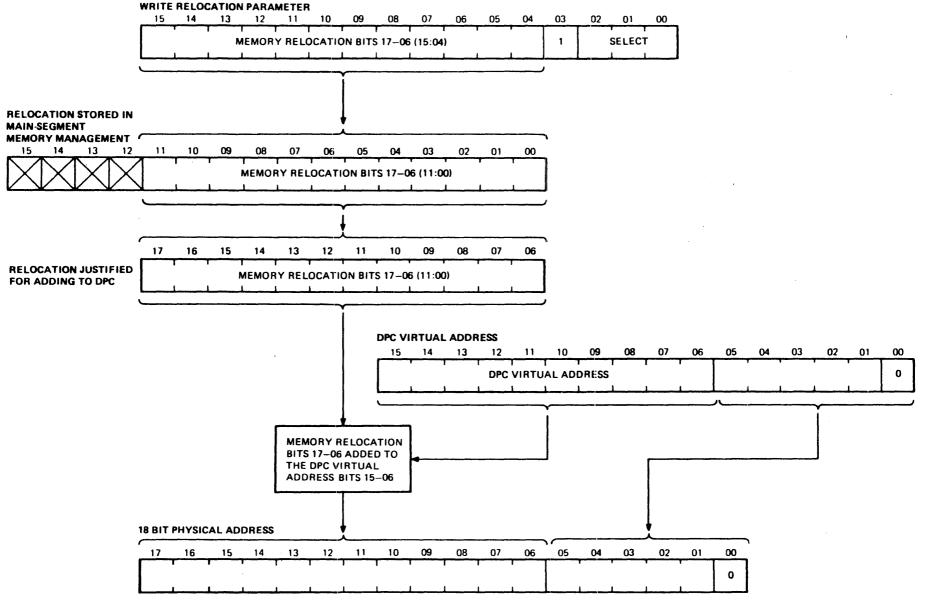

| 3-7          | Virtual-to-Physical Memory Relocation Process      |      |

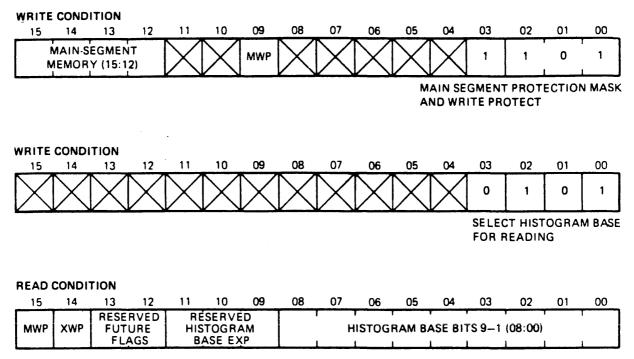

| 3-8          | DSR Select-Code 5 Register Formats                 |      |

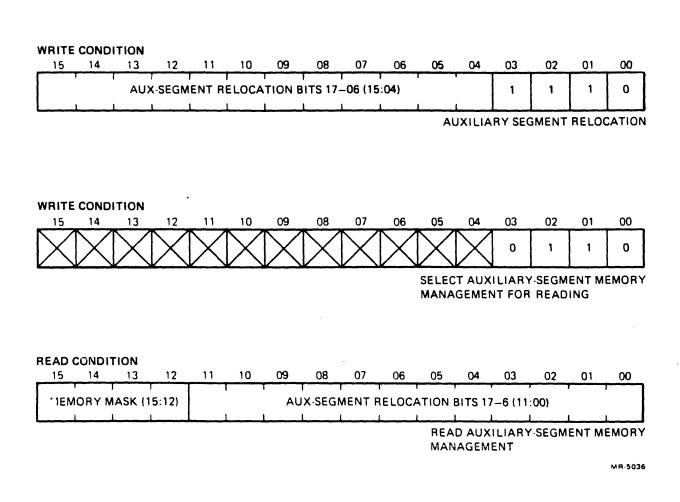

| 3- 9         | DSR Auxiliary-Segment/Relocation Register Format . |      |

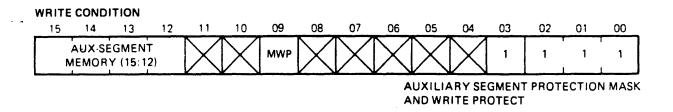

| 3-10         | DSR Auxiliary-Segment/CBASE Register Format        |      |

| 3-11         | DXR Register Formats                               |      |

| 3-12         | DYR Register Formats                               |      |

| 3-13         | VSV11/VS11 Instruction Word Summary                | 3-34 |

| 3-14         | Set-Graphic-Mode Instruction Format             | 3-41   |

|--------------|-------------------------------------------------|--------|

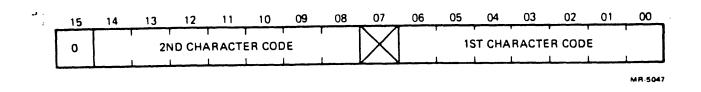

| 3-15         | Character Data Word Format (Mode 0000)          |        |

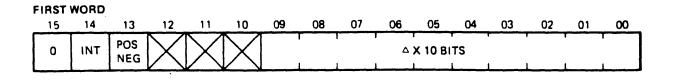

| 3-16         | Short Vector Data Word Format (Mode 0001)       |        |

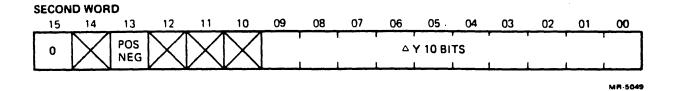

| 3-17         | Long Vector Data Word Format                    | 3-48   |

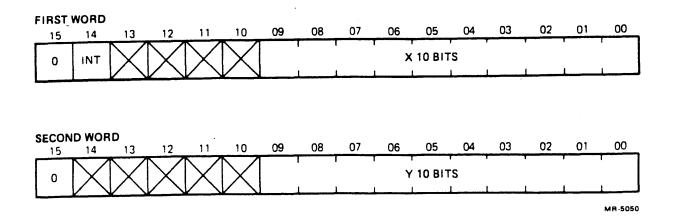

| 3-18         | Absolute Point Data Word Format                 |        |

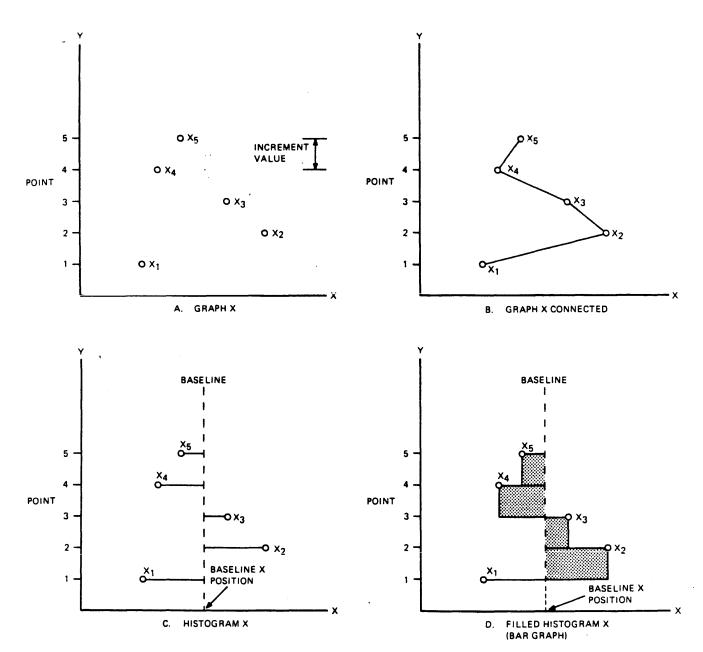

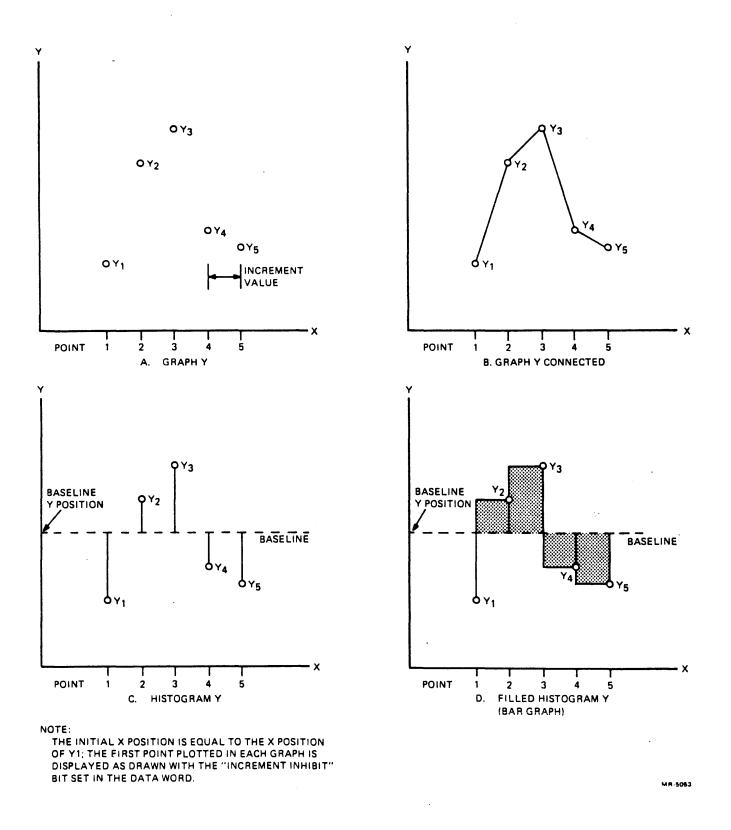

| 3-19         | Graph/Histogram-X Mode Displays                 |        |

| 3-20         | Graph/Histogram-X Data Word Format              |        |

| 3-21         | Graph/Histogram-Y Mode Displays                 |        |

| 3-22         | Graph/Histogram-Y Data Word Format              |        |

| 3-23         | Relative-Point Data Word Format                 |        |

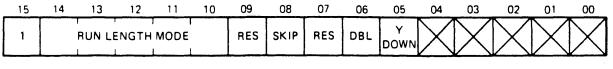

| 3-24         | Run-Length Mode Instruction Word Format         |        |

| 3-25         | Run-Length Data Word Format                     | 3-61   |

| 3-26         | Joystick Status Instruction Format              |        |

| 3-27         | Load Extended Joystick Control Instruction      |        |

| 3-28         | Write Cursor Coordinates Instruction Format     |        |

| 3-29         | Set Histogram Base Instruction Format           |        |

| 3-30         | Set Character Base Instruction Format           |        |

| 3-31         | Display Jump Instruction Format                 |        |

| 3-32         | Display Jump-to-Subroutine Instruction Format . |        |

| 3-33         | Display POP Instruction Format                  |        |

| 3-34         | DNDP Instruction Word Format                    |        |

| 3-35         | Load Status A Instruction Format                |        |

| 3-36         | Load Status C Instruction Format                | . 3-84 |

| 3-37         | Load Graphplot Increment Instruction Format     |        |

| 3-38         | Load Pixel Data Inhibit Instruction Format      |        |

| 3-39         | Marker No-Op Instruction Format                 |        |

| 3-40         | Bit Map Data Word Formats                       |        |

| 3-41         | Bit-Map-O Instruction Format                    |        |

| 3-42         | BIT-MAP-O Pixel Transfer Examples               |        |

| 3-43<br>3-44 | Bit-Map-1 Instruction Format                    |        |

| 3-44<br>4- 1 | DMA Pixel Readback Instruction Format           |        |

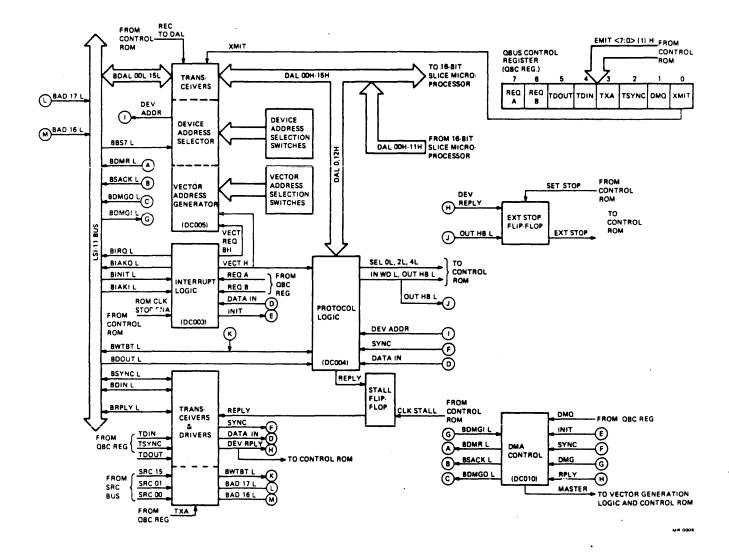

| 4- 1<br>4- 2 | LSI-11 Bus Interface Block Diagram              |        |

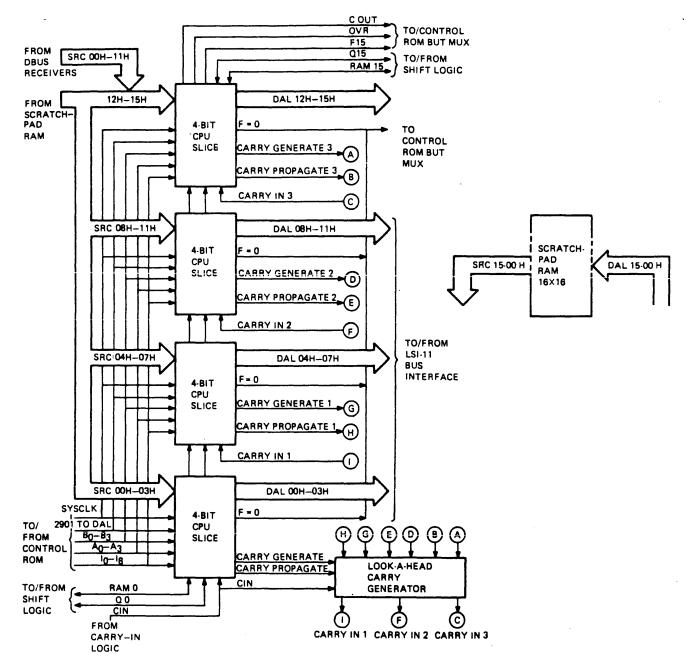

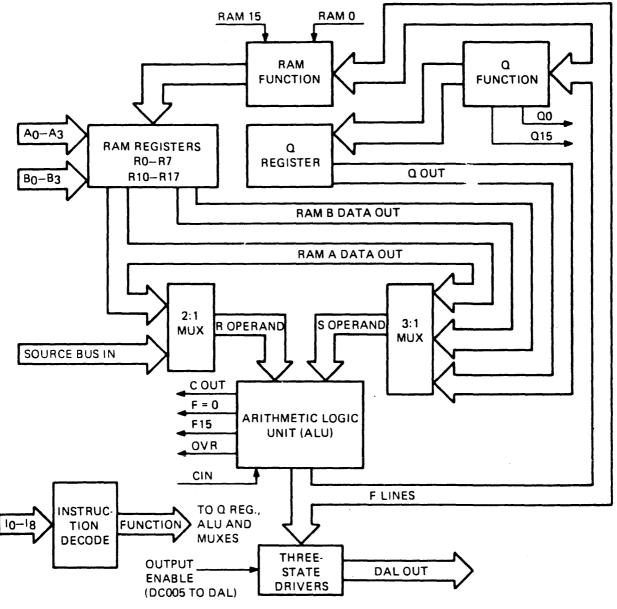

| 4-2          | 16-Bit Slice Microprocessor Block Diagram       |        |

| 4-3          | Microprocessor Block Diagram                    |        |

| 4-4          | Carry-Input and Shift Linkage Logic             |        |

| 4-5          | DBUS Interface Block Diagram                    |        |

| 4- 7         | DBUS Control Register Format                    |        |

| 4-8          | Control ROM Block Diagram                       |        |

| 4-9          | Basic Machine Cycle Timing Diagram              |        |

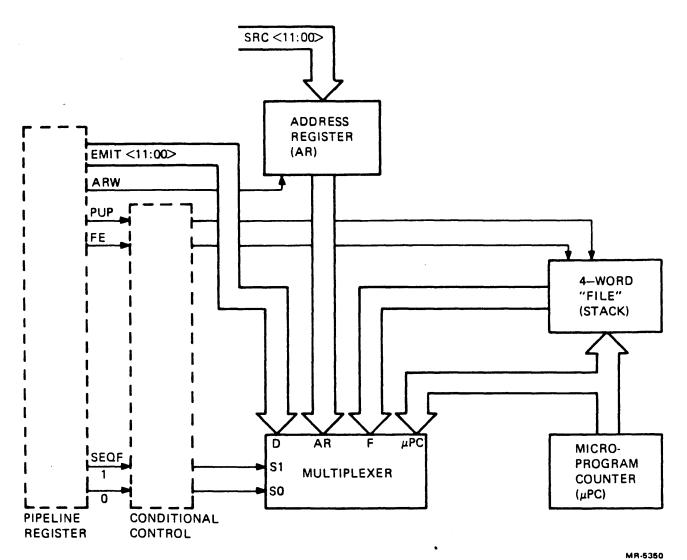

| 4-10         | 2909 Sequencer Simplified Block Diagram         |        |

| 4-11         | Microprogram Flow Example                       |        |

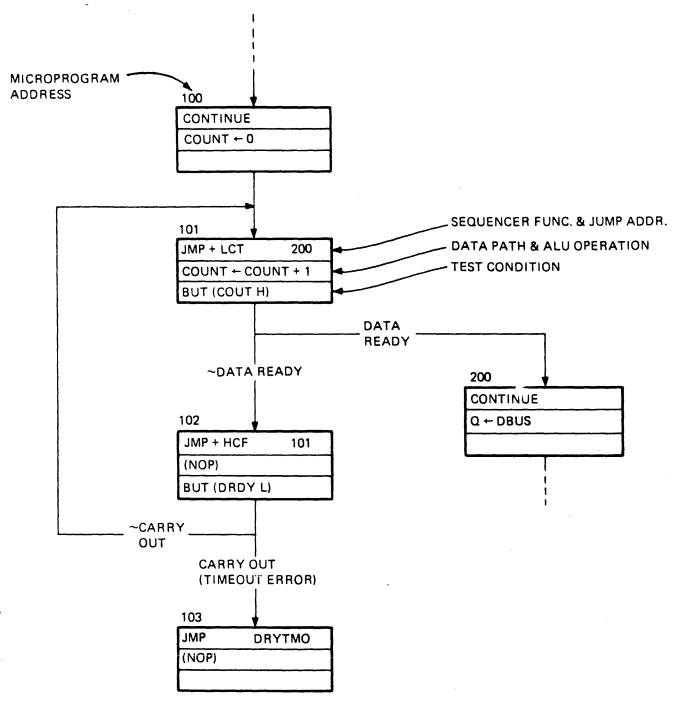

|              | Display Processor Microword Format (Sheet 1)    |        |

|              | Display Processor Microword Format (Sheet 2)    |        |

|              | Microprogram Overview (Sheet 1)                 |        |

| 4-13(2)      | Microprogram Overview (Sheet 2)                 |        |

| 5-1          | M7062 Image Memory Block Diagram                |        |

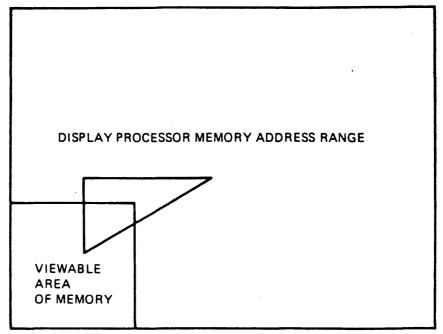

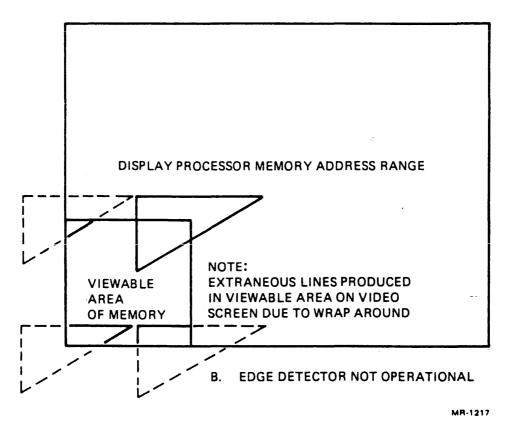

| 5-2          | Viewable Area of Video Screen                   | 5-4    |

| 5-3          | Horizontal and Vertical Counters                |        |

| 5-4          | Read/Write Multiplexer                          |        |

| 5-5          | RAS and CAS Memory Address                      |        |

| 5-6          | Memory and Shift Register                       |        |

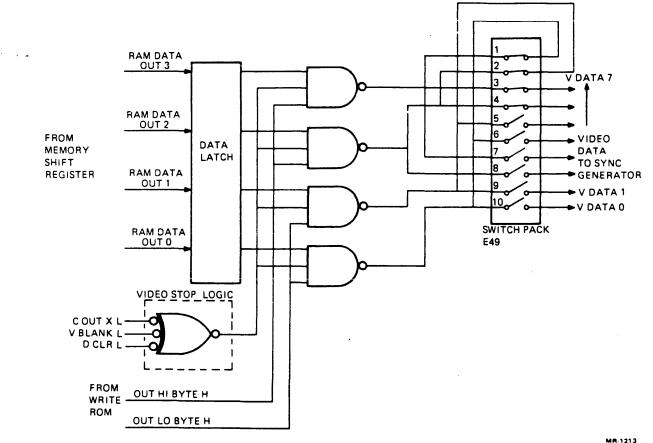

| 5-7          | Video Data Out                                  |        |

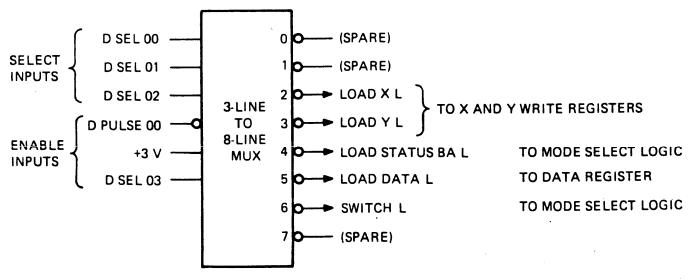

| 5- 8         | D Select Multiplexer (Decoder)                  |        |

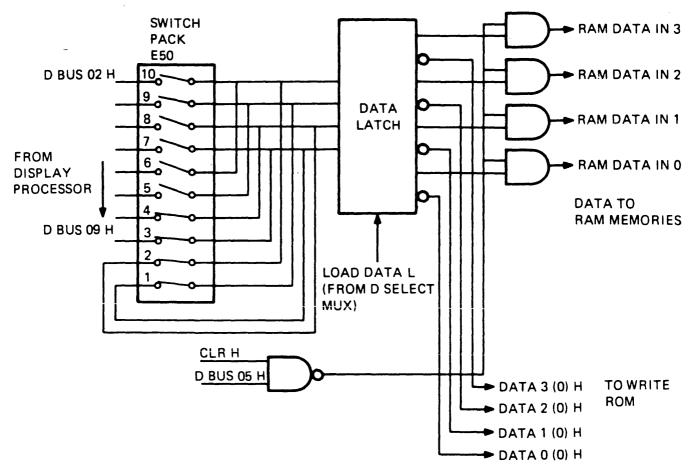

| 5~ 9         | Data Latch                                      |        |

|              |                                                 |        |

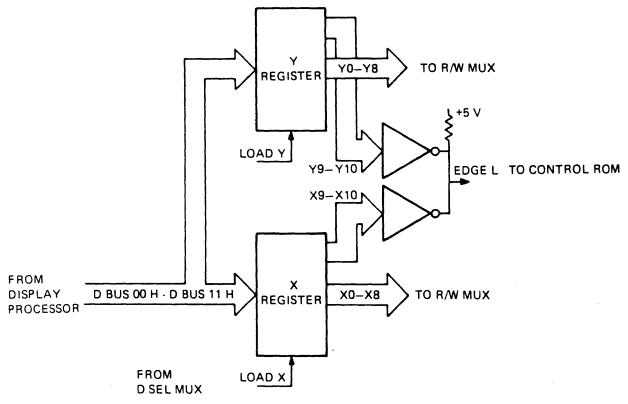

| 5-10    | X and Y Registers                                      |

|---------|--------------------------------------------------------|

| 5-11    | Edge Detector Operation                                |

| 5-12    | Write ROM                                              |

| 5-13    | Write Synchronization Logic                            |

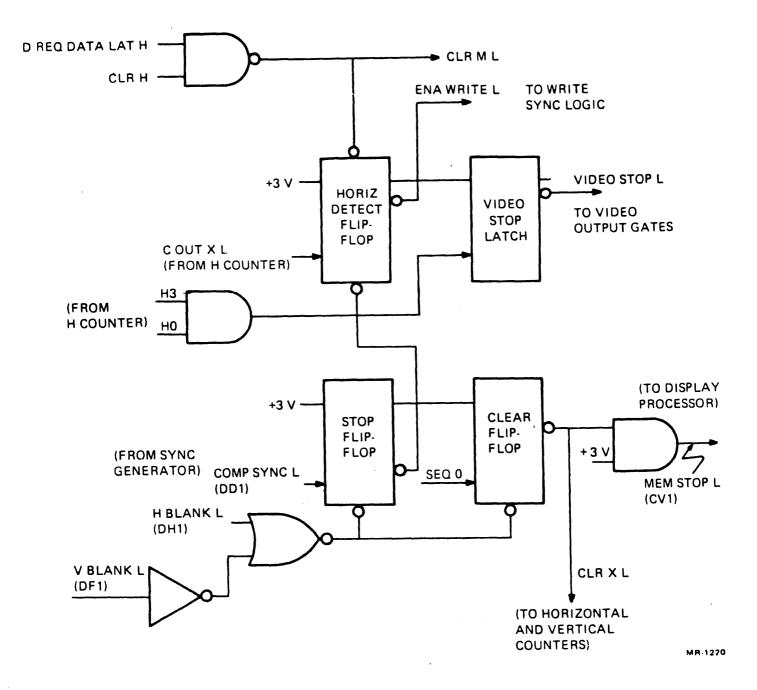

| 5-14    | Video Stop Logic                                       |

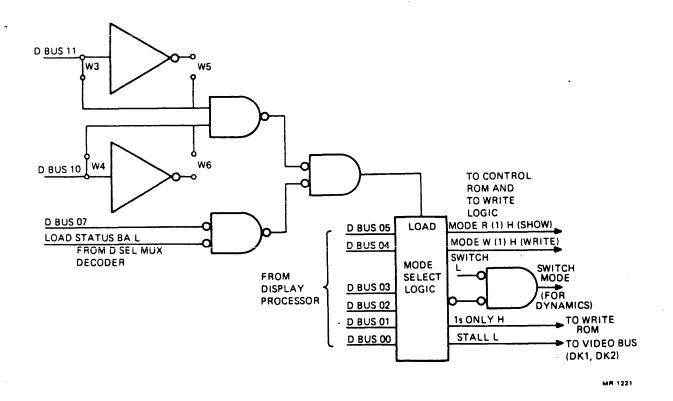

| 5-15    | Mode Select Logic                                      |

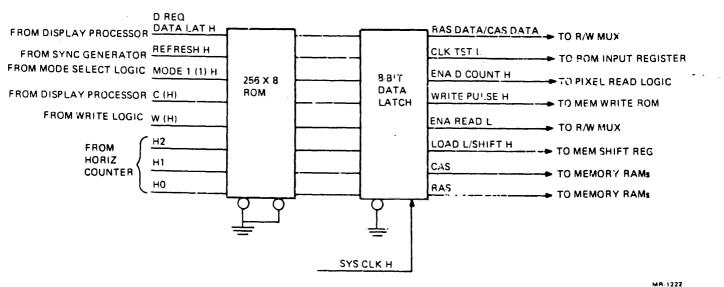

| 5-16    | Control ROM                                            |

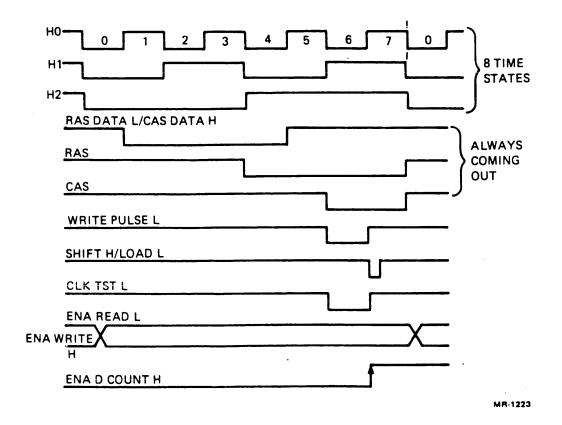

| 5-17    | Control ROM Timing Diagram                             |

| 5-18    | Pixel Read-Back Logic                                  |

| 6- 1    | M7061 Basic Block Diagram                              |

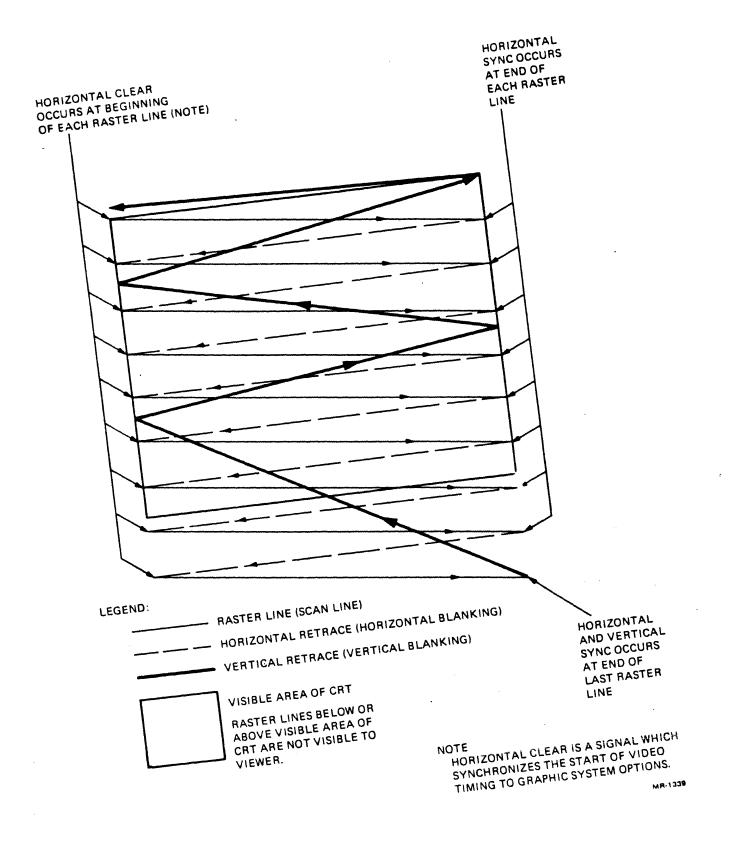

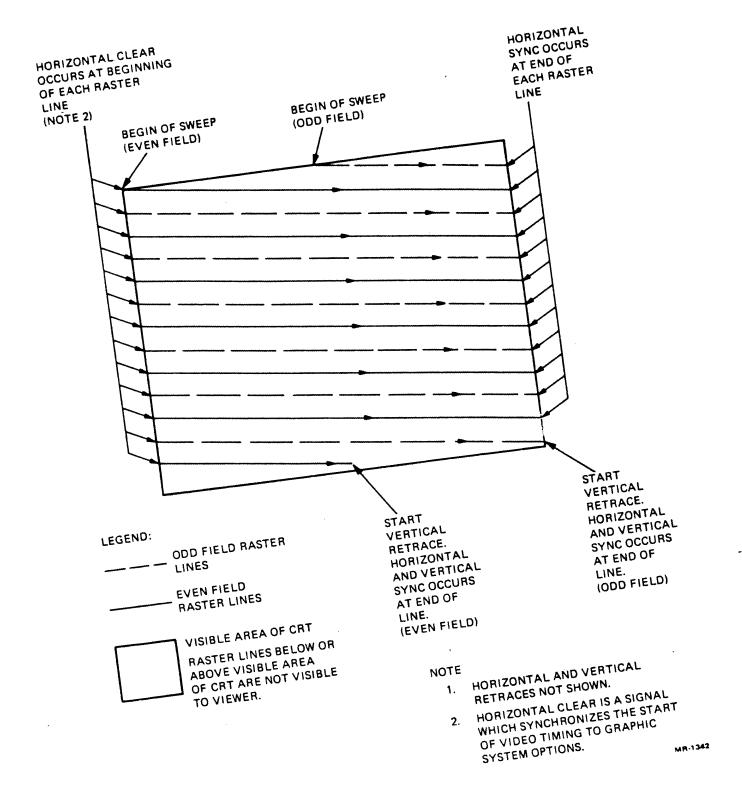

| 6-2     | Non-Interlaced Scanning                                |

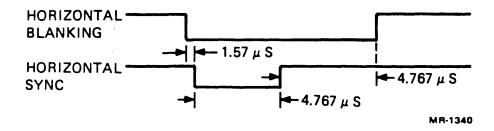

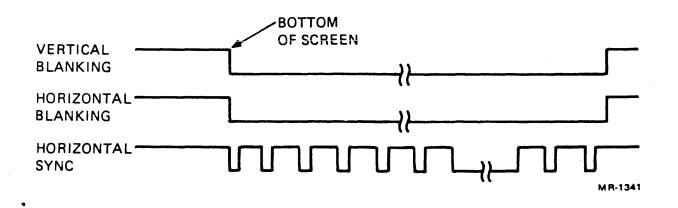

| 6- 3    | M7061 Horizontal Blanking and Sync Times 6-7           |

| 6- 4    | M7061 Blanking and Sync Relationship 6-7               |

| 6- 5    | Interlaced Scanning                                    |

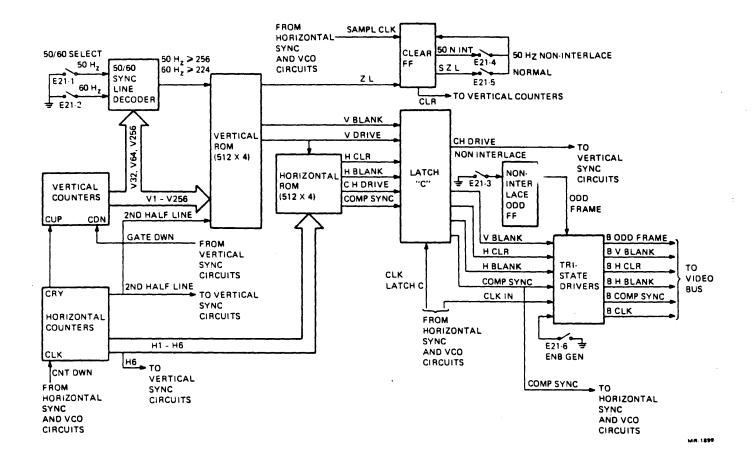

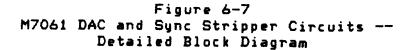

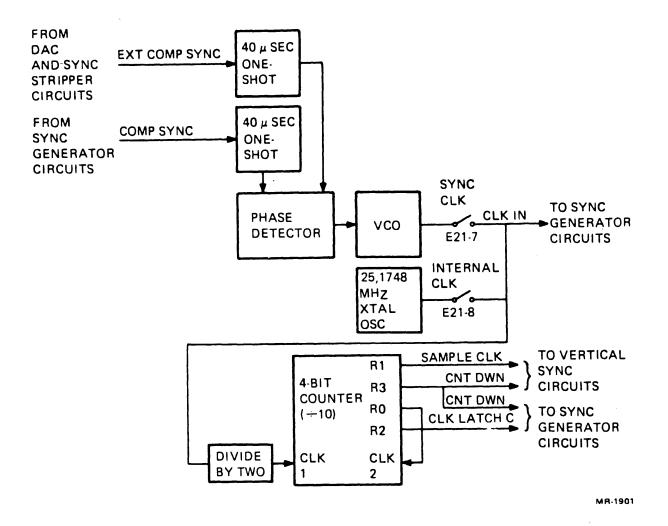

| 6- 6    | M7061 Sync Generator Circuits                          |

| 6- 7    | M7061 DAC and Sync Stripper Circuits                   |

| 6-8     | M7061 Horizontal Sync-Up and VCO Circuits 6-16         |

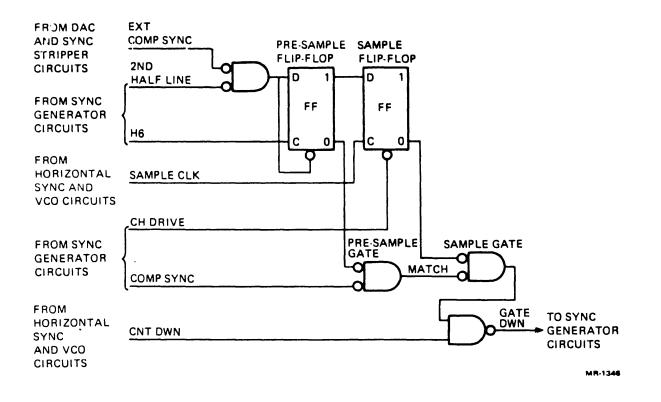

| 6- 9    | M7061 Vertical Sync Circuits                           |

|         | Vertical Sync Sample Times                             |

|         | Cursor Control Circuits (Control ROM & Memory) 6-21    |

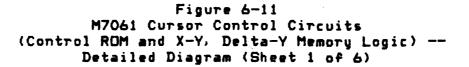

| 6-11(2) | Cursor Control Circuits (Intensity Control) 6-23       |

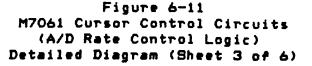

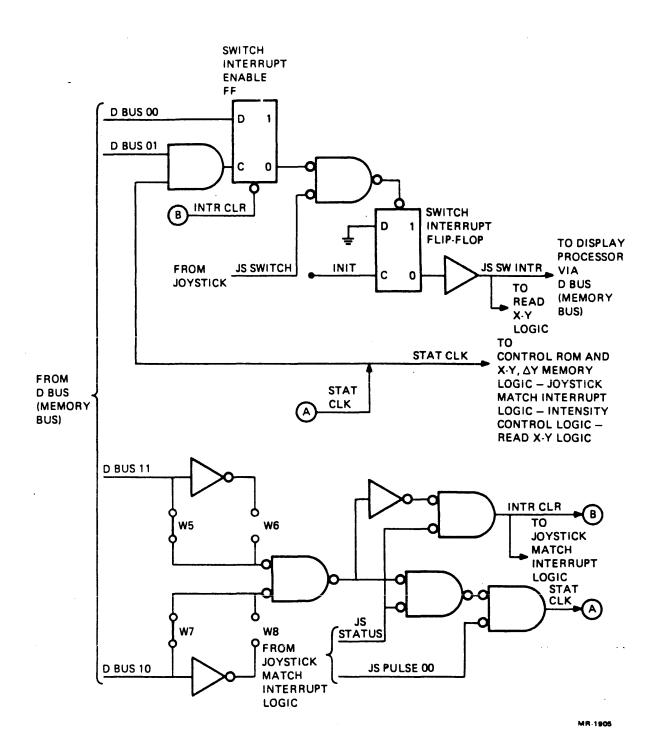

| 6-11(3) | Cursor Control Circuits (A/D Rate Control) 6-25        |

|         | Cursor Control Circuits (Address & Interrupt) 6-27     |

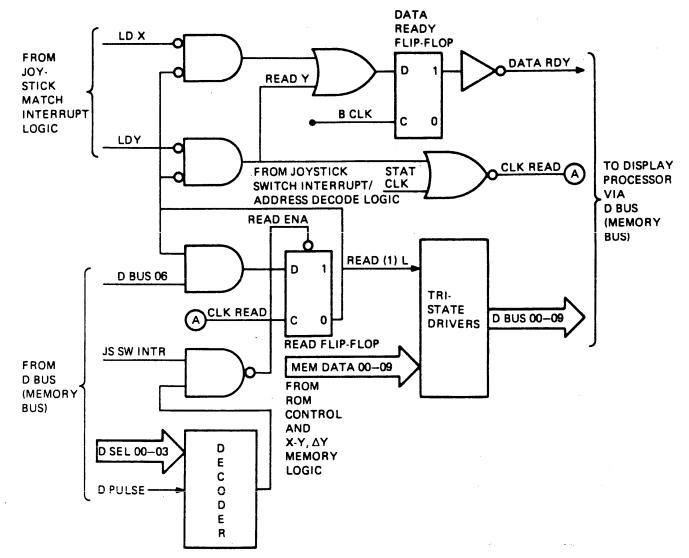

| 6-11(5) | Cursor Control Circuits (Read X/Y Logic) 6-29          |

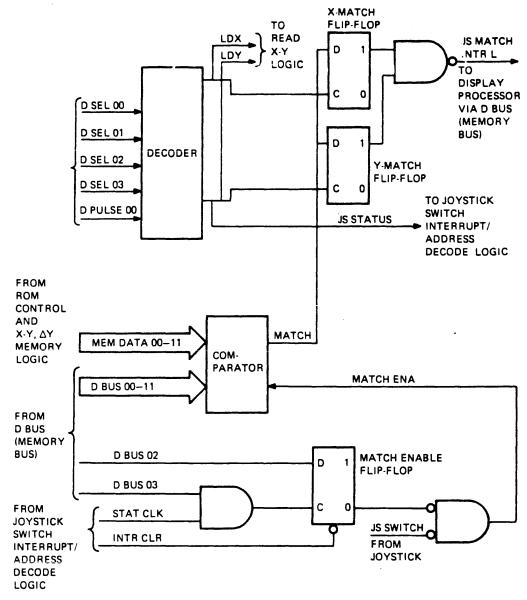

| 6-11(6) | Cursor Control Circuits (Match Interrupt Logic) . 6-31 |

| 6-12    | H3060 Joystick Circuits                                |

|         |                                                        |

.

.

•

Tables

| 1-1  | VSV11 and VS11 Graphics System Designations        | 1-7  |

|------|----------------------------------------------------|------|

| 1-2  | VSV11/VS11 Building Block Model Designations       | 1-8  |

| 1-3  | Related Publications                               | 1-17 |

| 2-1  | VT100-LA/LB Set-Up                                 | 2-7  |

| 2-2  | VRVO2-BA/BB Set-Up                                 | 2-9  |

| 2-3  | M7062 Switch Settings (Single Memory)              | 2-13 |

| 2-4  | M7062 Switch Settings (Dual Memory)                | 2-15 |

| 2- 5 | M7061 Switch/Jumper Setup for VSV11/VS11-AA        | 2-18 |

| 2- 6 | M7061 Switch/Jumper Setup for VSV11/VS11-AB        | 2-19 |

| 2-7  | M7061 Switch/Jumper Setup for VSV11/VS11-AC        |      |

| 2-8  | M7061 Switch/Jumper Setup for VSV11/VS11-AD        | 2-21 |

| 2-9  | M7061 Switch/Jumper Setup for VSV11/VS11-AE,-AP    | 2-22 |

| 2-10 | M7061 Switch/Jumper Setup for VSV11/VS11-AF,-AR .  | 2-23 |

| 2-11 | M7061 Switch/Jumper Setup for VSV11/VS11-AH,-AS .  |      |

| 2-12 | M7061 Switch/Jumper Setup for VSV11/VS11-AJ,-AT    | 2-25 |

| 2-13 | M7061 Sync Generator Switch/Jumper Functions       | 2-61 |

| 2-14 | M7062 Switch/Jumper Setup (2-Bit Interlaced)       | 2-63 |

| 2-15 | M7062 Switch/Jumper Setup (4-Bit Non-Interlaced) . | 2-66 |

| 3-1  | VSV11/VS11 Addressable Registers                   | 3-2  |

| 3- 2 | DSR Selection Codes                                | 3-6  |

| 3- 3 | DSR Register Bit Definitions                       | 3-8  |

| 3-4  | FLAGS Register Bit Definitions                     | 3-11 |

| 3- 5 | CSR Register Bit Definitions                       |      |

| 3- 6 | CSR Error Codes                                    |      |

| 3- 7 | Protection Mask Settings                           |      |

| 3- 9 | DXR Write Functions                                |      |

| 3-10 | DYR Write Functions                                |      |

| 3-11 | Interrupt Vectors                                  |      |

| 3-12 | VSV11/VS11 Instruction Set Summary                 |      |

| 3-13 | Set-Graphic-Mode Field Assignments                 |      |

| 3-14 | Character Data Word Field Assignments              | 3-44 |

| 3-15 | Short-Vector Data Word Field Assignments           |      |

| 3-16 | Long Vector Data Word Definitions                  |      |

| 3-17 | Absolute Point Data Word Definitions               |      |

| 3-18 | Graph/Histogram Data Word Definitions              |      |

| 3-19 | Graph/Histogram Y Data Word Definitions            |      |

| 3-20 | Relative-Point Data Word Field Assignments         |      |

| 3-21 | Run-Length Mode Instruction Word Definitions       |      |

| 3-22 | Run-Length Data Word Definitions                   |      |

| 3-23 | Joystick Status Instruction Bit Definitions        |      |

| 3-24 | Load Extended Joystick Control Instruction         |      |

| 3-25 | Write Cursor Coordinates Instruction               |      |

| 3-26 | Set Histogram Base Instruction                     |      |

| 3-27 | Set Character Base Instruction                     |      |

| 3-28 | Display Jump (DJUMP) Instruction                   |      |

| 3-29 | Display Jump to Subroutine (DJMS) Instruction      |      |

| 3-30 | Display POP Instruction Word Definitions           |      |

| 3-31 | DNOP Instruction Bit Definitions                   |      |

| 3-32 | Load Status A Instruction Bit Definitions          | 3-81 |

| 3-33 | Load Status Register C Bit Definitions             | 3-84 |

| 3-   | 34 Load Graphplot Increment Bit Definitions       | 3-86  |

|------|---------------------------------------------------|-------|

| 3-   | 35 Load Pixel Data Inhibit Bit Definitions        | 3-88  |

| 3-   | 36 Marker Instruction Field Definitions           | 3-89  |

| 3-   | 37 Bit-Map-O Instruction Bit Descriptions         | 3-94  |

| 3-   | 38 Bit-Map-1 Instruction Field Definitions        | 3-99  |

| 3-   | 39 DMA Pixel Readback Instruction Bit Definitions | 3-103 |

| 4-   | 1 2901A Register Assignments                      | 4-16  |

| 4-   | 2 2901A I Line Functions                          | 4-17  |

| 4-   | 3 ALU Destination Control                         | 4-18  |

| 4-   |                                                   | 4-19  |

| 4-   | 5 ALU Source Operand Control                      | 4-20  |

| 4-   |                                                   | 4-21  |

| -    | 7 Multiplexer Inputs                              | 4-24  |

| 4-   | 8 Scratchpad RAM Register Assignments             | 4-25  |

| 4-   | 9 DBUS Signal Line Functions                      | 4-29  |

| 4-   | 10 DBUS Control Register Bit Definitions          | 4-32  |

| 4-   |                                                   |       |

| 4-   | 12 2909 Sequencer Microword Control Bits          | 4-39  |

| . 4- | 13 Sequencer Control Bit Functions                | 4-40  |

| 4-   |                                                   | 4-41  |

| 4-   |                                                   | 4-43  |

| 4-   | 16 Conditional Sequencer Action                   | 4-45  |

| 5-   | 1 D Select Multiplexer Functions                  | 5-12  |

| 6-   | 1 M7061 Finger Pin Assignments                    | 6-35  |

| 7-   | 1 Basic Troubleshooting Chart                     | 7-5   |

| 7-   | 2 Video/VRVO2 Monitor Troubleshooting Chart       | 7-13  |

.

•

## CHAPTER 1

### INTRODUCTION

#### 1.1 GENERAL DESCRIPTION

The VSV11/VS11 is a video graphics system consisting of three quad-size modules and a joystick assembly. The system uses a high-speed microprocessor as the display processor, with а graphics instruction set that is based on the versatile VT11 instruction set. Included in the VSV11/VS11 instruction set are three bit map modes. An image memory is used in the VSV11/VS11 system to store the pixel data output of the display processor. The image memory is then continually "read" to the system monitor for the display of pixel information. The use of an image memory eliminates the need for display file refreshing and allows the display file to be changed after the first read pass. When the system is expanded with optional image memory, dynamic graphics can be run. The video output from the VSV11/VS11 system is EIA RS-170 compatible and can drive a black and white or RGB color composite video monitor. Either 50 Hz or 60 Hz, interlaced or noninterlaced scanning is provided.

the VSV11 There are two basic graphics systems available: for use with an LSI-11 CPU host, and the VS11 for use with a PDP-11 host. The difference between the two is that the VS11 system includes a DW11 UNIBUS-to-LSI-11 Bus Converter. Both systems employ three modules which plug into an "H9273-type" backplane. This type backplane has LSI-11 busing on the A-B slots and daisychain or video busing on the C-D slots. Since the VS11 system includes the DW11, a backplane (DDV11-CK) is supplied for mounting into PDP-11 mounting boxes. This backplane is compatible with the VSV11/VS11 modules. VSV11 systems are not supplied with a backplane. Operating power for the VSV11/VS11 modules is supplied by the power supplies in the host CPU.

The basic three-module VSV11/VS11 graphics system has a Display Processor module (M7064), one Image Memory module (M7062) and one Sync Generator/Cursor Control module (M7061). Optional Memory and Sync Generator modules can be used to expand the basic system for multi channel and/or multi monitor operation. One image memory module provides one memory channel with either 512 X 512 X 2 bits or 512 X 256 X 4 bits of pixel resolution and intensity. Additional image memory modules can be added to provide for:

- Single memory channel with 512 X 512 X 4 bits of pixel resolution and intensity for one system monitor, with no dynamic graphics,

- Two memory channels each with 512 X 256 X 4 bits of resolution and intensity for one monitor with dynamic graphics,

- 3. A four memory channel system, each channel having 512 X 512 X 2 bits of resolution and intensity; paired channels would drive separate monitors, each monitor could display independent dynamic graphics, and

- 4. Four separate channels, each channel having either 512 X 256 X 4 bits or 512 X 512 X 2 bits of resolution and intensity for four independent monitors with no dynamic graphics. Optional M7061 Sync Generator modules are required for each additional independent system monitor.

In summary, the VSV11/VS11 has the following features:

- VT11-type instructions including Vector, Point, Graphplot, Run-length, and Bitmap modes,

- LSI-11 Bus NPR capability, with 18-bit addressing,

- Modules operate in DDV11-CK & H9273 type backplane,

- Resolution of 512 X 256 X 4 bits or 512 X 512 X 2 bits, switch-selectable (with one memory),

- Outputs 4 or 16 grey levels, or 16 colors,

- Video output for VT100 (Maximum of one VT100 per VSV11/ VS11 subsystem),

- Can sync to an external RS-170 source having equal number of scan lines as Sync Generator,

- Mixes video from an external RS-170 source,

- Software- and Joystick-controlled cursor, supplied with a rate-type joystick; cursor size and intensity is jumper-selectable between two choices,

- Multi-channel and/or multi-monitor operation,

- Compatible with analog monochrome or RGB-COLOR monitors requiring EIA RS-170 composite sync,

- 50 Hz or 60 Hz, interlaced or noninterlaced operation,

- Software-controlled hardware blink.

#### 1.2 BASIC FUNCTIONAL DESCRIPTION

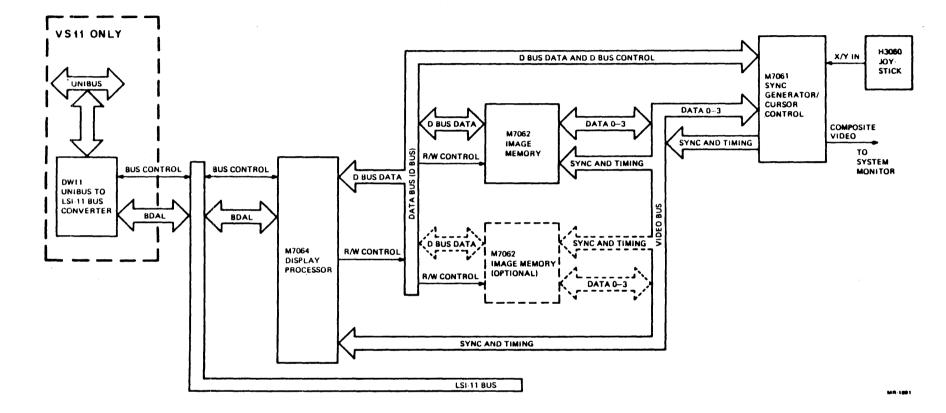

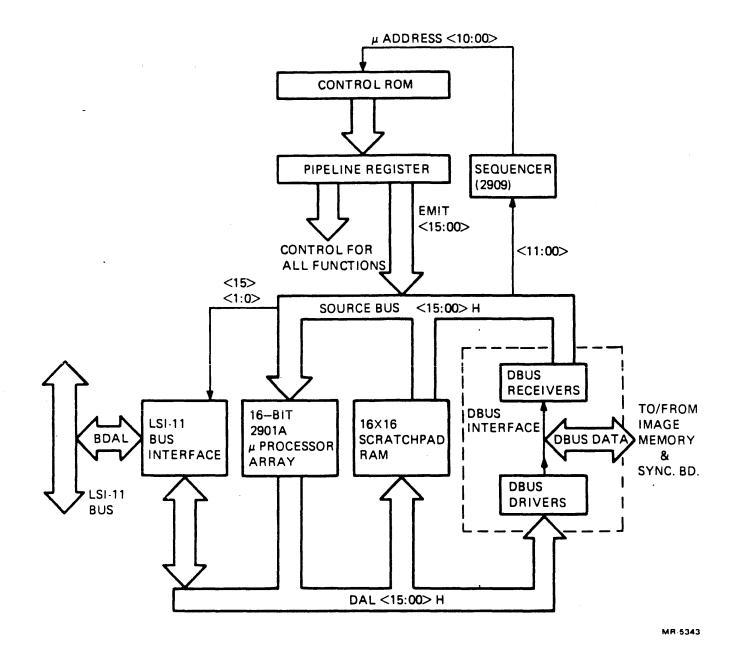

Figure 1-1 is a block diagram of the VSV11/VS11 graphics system. Three major functions appear on this diagram. These are:

- (1) the M7064 Display Processor (abbreviated DPU),

- (2) the M7062 Image Memory, and

- (3) the M7061 Sync Generator/Cursor Control.

These three major functions are the three modules of the VSV11/VS11 system. Figure 1-1 shows the optional additional M7062 Image Memory. The H3060 joystick is supplied with all systems, and the DW11 is used only with the VS11 system.

The system modules interface to each other by means of two internal buses. These buses are the DBUS (Memory Data Bus) and the VBUS (Video Bus). The DBUS is a three-state bus that carries data and control signals between the M7064 Display pixel Processor and the M7062 Image Memory, and between the Display the M7061 Sync Generator/Cursor Control. Processor and Physically, the DBUS is a 40-conductor ribbon cable with Berg-type connectors. The cable is connected from the AD-pin Berg-type connector on the Display Processor module to the 40-pin Berg-type connectors on each Memory and Sync modyle. The Video Bus is a three-state bus (only two-states are used) interfacing the Display Processor, Memory, and Sync modules. This bus carries sync and timing signals and video data. pixel Physically, the video bus is the daisy-chain wiring on the C-D slots of an H9273-type or the E-F slots of a DDV11-CK backplane. A complete description of the DBUS is presented in Chapter 5, while the Video Bus is detailed in Chapter 6.

The VSV11/VS11 system operates as a DMA device on either the LSI-11 or PDP-11 bus. After constructing a display file in the CPU memory, the starting address of the file is transferred to the Display Processor's Display Program Counter (DPC). The Display Processor then makes nonprocessor requests (NPRs) to gain use of the bus. Once bus master, the Display Processor has direct memory access (DMA) to the CPU memory for reading the display file. Display file instructions consist of Graphic, Control, and Data instructions (these are fully explained in Chapter 3). These instructions are processed by the Display Processor and set-up the graphic mode, status registers and control functions, and contain the pixel (picture element) information for display. Picture information processed by the Display Processor is sent to the Image Memory via the Memory Bus/DBUS for storage and eventual display on the system monitor. A detailed description of the Display Processor is presented in Chapter 4.

Figure 1-1 VSV11/VS11 Graphics System Block Diagram

٠

The Image Memory stores an "image" of the pixel information to be displayed on the system monitor. Pixel data received from the Display Processor is stored in thirty-two 16K Random Access Memories (RAMs) on the M7062. X and Y address lines to the RAMs control which pixel position is to be written or read. RAM X and Y addresses correspond to pixel X and Y coordinates on the screen of the system monitor. Digital data for display is read from the M7062 to the M7061 Sync Generator/Cursor Control via the Video Bus (VBUS). At the M7061, the digital data is converted to analog data. Because the Image Memory stores the picture to be displayed, the display file in the CPU memory is not required for refreshing the display and can be changed after its contents are transferred to the VSV11/VS11. Optional M7062 Image Memory modules can be added to the basic VSV11/VS11 system to increase pixel resolution, to run dynamic grahics, or for multi-monitor and/or multi-channel operation. Chapter 5 presents a detailed description of the M7062 Image Memory.

The M7061 Sync Generator/Cursor Control provides digital-to-analog conversion of the pixel data from the M7062 Image Memory for display on the system monitor. Sync and blanking pulses generated by the M7061 are used throughout the VSV11/VS11 system and are combined with the pixel video data to produce the EIA RS-170 composite video signal for the monitor. Cursor control circuits within the M7061 compute positions for display on the system monitor based on one of three data inputs. The joystick, PDP11 I/D, or display file primitive can all control the displayed cursor position. Match and Switch interrupts (explained in Chapter 3), originated by pressing the joystick interrupt switch or actuated by software, are controlled by logic on the M7061. Joystick position is read back to the Display Processor via the Memory Bus/DBUS during a switch interrupt. The joystick itself consists of an X-position and a Y-position potentiometer, and two interrupt switches wired in parallel. These components are mounted in an enclosure which connects to the M7061 module via a cable. The H3060 joystick is referred to as a rate-type joystick. That is, small movements of the joystick produce slow movements of the crosshairs. Large joystick movements cause the crosshairs to move rapidly. Detailed descriptions of the M7061 Sync Generator/Cursor Control module and the H3060 Joystick are provided in Chapter 6.

The DW11 UNIBUS-to-LSI-11 Bus Converter is supplied only with VS11 systems. The converter translates UNIBUS and LSI-11 Bus signals. This translation is required because the Display Processor is an LSI-11 Bus device, and VS11 systems are used with PDP-11 host CPUs. Complete details on the DW11 are presented in the DW11 UNIBUS to LSI-11 Bus Converter Installation Guide (EK-DW11A-IN).

#### 1. 3 OPTION DESIGNATIONS

Various standard VSV11 and VS11 option packages are available. The standard "packaged" units are based upon the VSV11-AA, which is a 3-module set containing one M7064 Display Processor, one M7061 Sync Generator/Cursor Control, and one M7062 Image Memory (also called a Frame Buffer). VSV11 systems, for LSI-11 Bus systems, plug directly into an LSI-11 Bus backplane (H9273-A or equivalent); the backplane is not supplied. VS11 systems, for PDP-11 and VAX UNIBUS systems, include a DW11-BK UNIBUS-to-LSI-11 Bus Converter, which includes a 4-slot backplane. The basic VSV11 or VS11 logic can be augmented with one addition M7062 Image Memory as part of the standard offering.

Some packages do not include a display monitor. Others include either a 12" Monochrome (Black & White) monitor (VT100-LA/LB) or a 19" Color monitor (VRVO2). Both types of monitors are based upon the VT100 terminal. The VT100-LA (120V/60Hz) or VT100-LB (240V/50Hz) is a standard VT100-AA with a P40 phosphor and anti-glare shield. The VRVO2-BA (120V/60Hz) or VRVO2-BB (240V/50Hz) are composed of two free-standing units plus a detachable keyboard. One of the units is a 19-inch (dizgenal measure) color CRT. The other is a Keyboard Interface containing standard VT100 logic and a power supply. Both type: of standard monitors can communicate with the host CPU over a standard serial line and can function as a standard terminal. The serial line does not connect to the VSV11/VS11 logic; the user must provide a standard interface for communications (DZ11, DF.11, etc.)

In addition to the standard units, VSV11/VS11 "building blocks" are available for constructing "extended" graphic systems. These extended systems can contain multiple Memory and Joystick channels, providing for high-resolution "dynamic" displays and/or attachment of multiple independent display monitors.

Table 1-1 lists the standard VSV11 and VS11 graphic systems designations. Table 1-2 lists the model designations of the VSV11/VS11 building blocks.

| DESIGNATION |           |           |           |                 |                  |

|-------------|-----------|-----------|-----------|-----------------|------------------|

| LSI-11 Bus  |           | UNIBUS    |           | No. of<br>Image |                  |

| 120V/60Hz : | 240V/50Hz | 120V/60Hz | 240V/50Hz | Memories        | Monitor          |

| VSV11-AA    | VSV11-AB  | VS11-AA   | VS11-AB   | 1               | None             |

| VSV11-AC    | VSV11-AD  | VS11-AC   | VS11-AD   | 2               | None             |

| VSV11-AE    | VSV11-AF  | VS11-AE   | VS11-AF   | 1               | VT100<br>(B&W)   |

| VSV11-AH    | VSV11-AJ  | VS11-AH   | VS11-AJ   | 2               | VT100<br>(B&W)   |

| VSV11-AP    | VSV11-AR  | VS11-AP   | VS11-AR   | 1               | VRVO2<br>(Color) |

| VSV11-AS    | VSV11-AT  | VS11-AS   | VS11-AT   | 2               | VRVO2<br>(Color) |

. .

Table 1-1VSV11 and VS11 Graphics System Designations

Υ.

### Table 1-2 VSV11/VS11 Building Block Model Designations

| DESIGNATION |          | DESCRIPTION                                                                                                                                                                                                                                                                                                                                             |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 60 Hz       | 50 Hz    |                                                                                                                                                                                                                                                                                                                                                         |

| VSV11-BA    | VSV11-BB | VSV11-AA/AB plus DDV11-DK 9-Slot<br>Backplane, Power Harness Adapter, Six<br>G7272 Grant Continuity Cards, Extended<br>DBUS Data Cable, and M9403 LSI-11 Bus<br>Connector with +15V to +12V Converter.                                                                                                                                                  |

| VS11-BA     | VS11-BB  | VSV11-AA/AB with DW11-EK UNIBUS to<br>LSI-11 Bus Converter. Equivalent to<br>VS11-AA/AB but with DDV11-DK 9-Slot<br>Backplane.                                                                                                                                                                                                                          |

| VS11-BC     |          | VSV11-AA/AB with DW11-A UNIBUS to<br>LSI-11 Bus Converter. The DW11-A<br>contains an M8217 bus converter module,<br>an M9401 bus connector, and two<br>BC05L-16 16-foot 40-conductor ribbon<br>cables. With the addition of an H9273-A<br>backplane and LSI-11 expansion box,<br>such as BA11-N, this building block can<br>be used on a UNIBUS system. |

| VSV1        |          | M7062 Image Memory Module                                                                                                                                                                                                                                                                                                                               |

| VSV11-SA    | VSV11-SB | M7061 Sync Generator/Cursor Control  <br>Module plus Video Cables                                                                                                                                                                                                                                                                                       |

| VSV11-SC    | VSV11-SD | M7061 Sync Generator/Cursor Control Module, Video Cables, and Joystick Pigtail Cable                                                                                                                                                                                                                                                                    |

| VSV11-SE    | VSV11-SF | M7061 Sync Generator/Cursor Control<br>Module, Video Cables, and Multi-Tap<br>Joystick Pigtail Cable (for connecting<br>a single H3060 Joystick to up to four<br>M7061 modules)                                                                                                                                                                         |

| H3060       |          | Joystick Assembly                                                                                                                                                                                                                                                                                                                                       |

| VT100-LA    | VT100-LB | Monochrome Monitor Terminal (same as<br>VT100-AA/AB but with P40 phosphor)                                                                                                                                                                                                                                                                              |

| VRVO2-AA    | VRV02-AB | 19-inch Color Monitor (with no Keyboard<br>or terminal logic)                                                                                                                                                                                                                                                                                           |

| VRV02-BA    | VRVO2-BB | 19-inch Color Monitor Terminal (with<br>Keyboard and terminal logic)                                                                                                                                                                                                                                                                                    |

+

#### 1.4 SPECIFICATIONS\*

1.4.1 Environmental Requirements

| Temperature<br>Storage<br>Operating | -40°to 66°C (-40°to 150°F)<br>5°to 50°C ( 40°to 120°F) |

|-------------------------------------|--------------------------------------------------------|

| Relative Humidity                   | 10% to 95% noncondensing                               |

1.4.2 Logic Power Requirements

|       |               | <u>Nominal</u>                                   | Max.                |

|-------|---------------|--------------------------------------------------|---------------------|

| M7064 | +5V           | 2.8 Amp                                          | 3.0 Amp             |

| M7062 | +5V           | 1.2 Amp                                          | 1.5 Amp             |

|       | -5V**<br>+12V | 0.006 Amp<br>0.45 Amp                            | 0.01 Amp<br>0.5 Amp |

| M7061 | +5V           | 1.2 Amp                                          | 1.5 Amp             |

|       | +12V          | 0.11 Amp                                         | 0.15 Amp            |

| VSV11 | +5V<br>+12V   | 5.2 Amp<br>0.56 Amp                              | 6.0 Amp<br>0.65 Amp |

| M8217 | +5V           | 2.5 Amp                                          | 3.0 Amp             |

| M9403 | +15V          | Equal to +12V<br>drawn by M706<br>M7062 modules. | t and               |

**\*\*** Supplied by M7061

1.4.3 Sync Generator (M7061)

(M7061 operating from crystal oscillator)

| Horizontal Frequency    | 15.734 kHz <u>+</u> 0.2% |

|-------------------------|--------------------------|

| Scan Lines Per Frame    |                          |

| 60HZ Interlaced         | 525                      |

| 60HZ Noninterlaced      | 525                      |

| 50HZ Interlaced         | 629                      |

| 50HZ Noninterlaced      | 629                      |

| Visible Lines Per Field |                          |

| 60HZ Interlaced         | 480 (2x240/Field)        |

| 60HZ Noninterlaced      | 240 (1x240/Field)        |

| 50HZ Interlaced         | 512 (2x256/Field)        |

| 50HZ Noninterlaced      | 256 (1x256/Field)        |

|                         |                          |

\* Specifications are subject to change without notice.

1.4.3.1 Video Output To VT100 -

| 1.4.3.1 Video Uutput lo VI100 -                                                                              |                                                                                                 |

|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| Output Video Voltage<br>Output Impedance<br>Video (Rise, Fall)<br>Sync (Rise, Fall Time)                     | 1.2Vp-p. <u>+</u> 20%<br>75 <u>+</u> 3%<br>23ns max<br>25ns max                                 |

| [Video signal derived from Monochrom<br>output, but without mixed video input.                               |                                                                                                 |

| 1.4.3.2 Monochrome/Green, Red, Blue V                                                                        | ideo Outputs —                                                                                  |

| (Red and Blue unconnected and untermin<br>VT-100 and the Monochrome/Green (C<br>provide 16 levels of video.) |                                                                                                 |

| <u>Monochrome operation with 16 grey shad</u><br>(Red and Blue unterminated)                                 | <u>es</u>                                                                                       |

| Monochrome(/Green) output<br>(From Composite Video Output)                                                   | EIA RS-170<br>compatible<br>Composite Sync<br>with 16 video<br>levels and mixed<br>video input. |

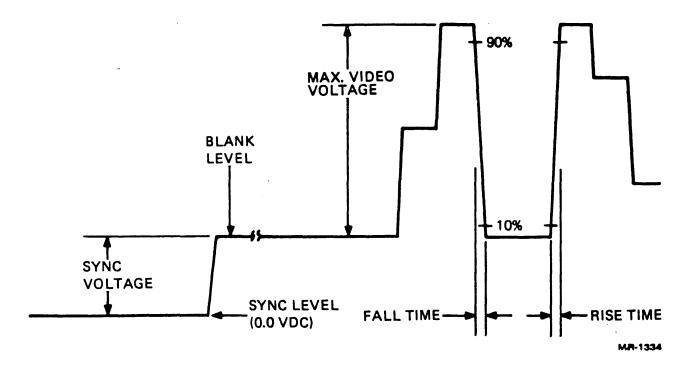

| Sync (Figure 1-2)                                                                                            | EIA RS-170<br>Compatible                                                                        |

| Sync Voltage                                                                                                 | 0.4V <u>+</u> 20%                                                                               |

| Video Voltage, max<br>(Figure 1-3)                                                                           | 1. 2VP-P <u>+</u> 20%                                                                           |

| Output Impedance                                                                                             | 75 ohms <u>+</u> 10%                                                                            |

| Signal Transition Times<br>(Figures 1-2 and 1-3)<br>Sync (Rise, Fall Time)<br>Video (Rise, Fall Time)        | 25ns max<br>25ns max                                                                            |

| Red output                                                                                                   | Unconnected and<br>Unterminated                                                                 |

| Blue output                                                                                                  | Unconnected and<br>Unterminated                                                                 |

+

### <u>RGB operation with 16 colors</u> (Red and Blue terminated by 75 ohms)

,

| (Monochrome/)Green Output<br>(from Composite Video Output)                                            | EIA RS-170<br>compatible<br>Composite Sync<br>with 4 video<br>levels, and<br>mixed video<br>input. |

|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Sync (Figure 1-2)                                                                                     | EIA RS-170<br>Compatible                                                                           |

| Sync Voltage                                                                                          | 0. 4V <u>+</u> 20%                                                                                 |

| Video Voltage, Max.<br>(Figure 1-3)                                                                   | 1. 2VP-P <u>+</u> 20%                                                                              |

| Output Impedance                                                                                      | 75 Ohms <u>+</u> 10%                                                                               |

| Signal Transition Times<br>(Figures 1-2 and 1-3)<br>Sync (Rise, Fall Time)<br>Video (Rise, Fall Time) | 25ns max<br>25ns max                                                                               |

| Red Output:<br>2 video levels                                                                         | Low = 0.21 V max<br>High = 0.93 V <u>+</u> 20%                                                     |

| Output Impedance<br>High State<br>Low State                                                           | 330 Ohms <u>+</u> 10%<br>30 Ohms mæx                                                               |

| Signal Transition Times<br>(Figures 1-2 and 1-3)<br>Video Risetime<br>Video Falltime                  | 50ns max<br>25ns max                                                                               |

| Blue Output:<br>2 video levels                                                                        | Low = 0.21 V max<br>High = 0.93 V <u>+</u> 20%                                                     |

| Output Impedance<br>High State<br>Low State                                                           | 330 Ohms <u>+</u> 10%<br>30 Ohms max                                                               |

| Signal Transition Times<br>(Figures 1-2 and 1-3)<br>Video Risetime<br>Video Falltime                  | 50ns max<br>25ns max                                                                               |

# 1.4.3.3 Video Input & Mixer Requirements -

| Video Input Waveform            | RS-170                      |

|---------------------------------|-----------------------------|

| Input Frequency Range           | 15.734 kHz <u>+</u> 1%      |

| Input Voltage Range             |                             |

| Sync (Negative)                 | 0.4V ± 30%                  |

| Video (Positive)                | 1. 04 $\pm$ 30%             |

| Input Impedance                 | 75 <u>+</u> 5%              |

| Bandwidth (Video Input          |                             |

| To Video Output)                | 10 MHz                      |

| Mixer Function                  | Video Input is OR'ed        |

|                                 | with internally             |

|                                 | generated signal.           |

|                                 | Result is fed out           |

|                                 | through Composite           |

|                                 | (Monochrome/Green)          |

|                                 | Output and does not         |

|                                 | appear on the VT100         |

|                                 | output.                     |

| Video Input Registration        | See Figure 1-4              |

| 1.4.4 Image Memory (M7062)      |                             |

| Image Memory Resolution         | 512x512x2 Bits or           |

|                                 | 512x256x4 Bits              |

| Output Pixel Rate               | 1 Pixel per 80 nsec.        |

| Bits Per Pixel                  | 2 or 4                      |

| Input Data Rate to Image Memory | 1 Pixel per 640 nsec<br>max |

| Pixel Timing, Per Line          | See Figure 1-4              |

| Visible Lines Timing            | See Figure 1-5              |

|                                 |                             |

•

## 1.4.5 Display Processor I/O (M7064)

.

4

| LSI-11 Bus NPR's |

|------------------|

| 1 Bus Load       |

| See Chapter 3    |

|                  |

#### 1.4.6 Monitor Specifications

## 1.4.6.1 VT100-LA/LB -

| Type                          | Monochrome (Black & White)                    |

|-------------------------------|-----------------------------------------------|

| Size                          | 12—inch, diagonal screen measure              |

| Phosphor                      | P40                                           |

| Power<br>VT100-LA<br>VT100-LB | 90-128 Vac ∉ 2.2 Amp<br>180-256 Vac ∉ 1.1 Amp |

### 1.4.6.2 VRV02-AA/AB -

| Type                          | Color, R-Q-B                                   |

|-------------------------------|------------------------------------------------|

| Size                          | 19—inch, diagonal screen measure               |

| Phosphor                      | Long-Persistence                               |

| Power<br>VRV02-AA<br>VRV02-AB | 108-132 Vac & 1.1 Amp<br>216-264 Vac & 0.6 Amp |

### 1.4.6.3 VRV02-BA/BB -

| Туре              | Color, R-O-B<br>w/ Keyboard & Interface |  |

|-------------------|-----------------------------------------|--|

| Size              | 19-inch, diagonal screen measure        |  |

| Phosphor          | Long-Persistence                        |  |

| Power<br>VRV02-AA | •<br>•                                  |  |

| CRT               | 108-132 Vac 😫 1.1 Amp                   |  |

| Keyboard Intf.    | 90-128 Vac 😫 1.5 Amp                    |  |

| VRVO2-AB          |                                         |  |

| CRT               | 216-264 Vac 🐔 0.6 Amp                   |  |

| Keyboard Intf.    |                                         |  |

.

Figure 1-2 Composite Video Output Waveform

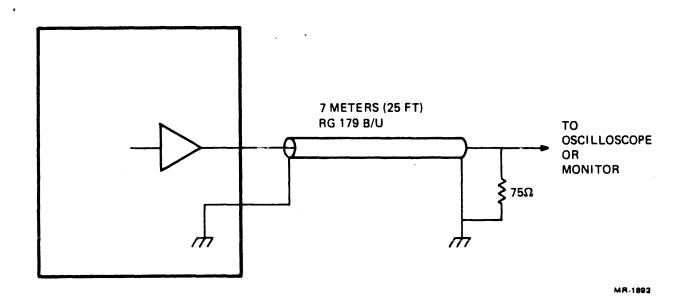

Figure 1-3 Composite Video Test Setup

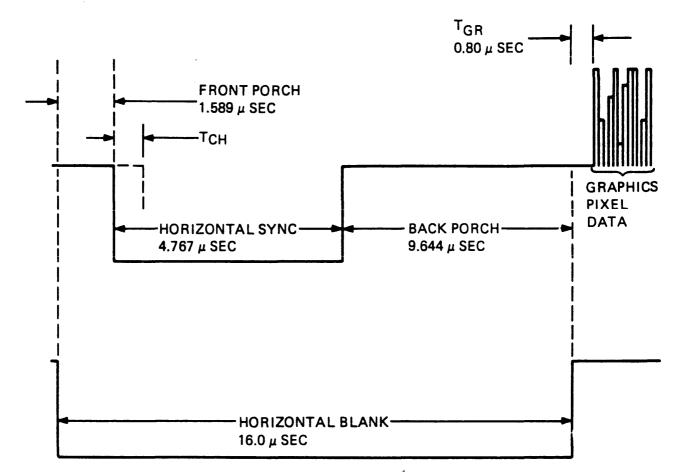

T<sub>CH</sub> = DELAY TIME BETWEEN LEADING EDGE OF GRAPHIC SYNC AND EXTERNAL SYNC APPLIED AT VIDEO MIXER INPUT.

T<sub>GR</sub><sup>=</sup> DELAY TIME BETWEEN LEADING EDGE OF H. BLANK TO LEADING EDGE OF FIRST GRAPHICS PIXEL.

MR-1336

Figure 1-4 External Video Input Registration

#### 1.5 RELATED DOCUMENTS

The publications listed in Table 1-3 supplement the information in this manual.

| Publication                                                                                        | Document Number<br> | l Remarks                                                             |

|----------------------------------------------------------------------------------------------------|---------------------|-----------------------------------------------------------------------|

| VSV11 Field<br>Maintenance<br>Print Set                                                            | B-TC-VSV11-0-1      | <br>  Shipped with<br>  Unit<br>                                      |

| VS11 Field<br>Maintenance<br>Print Set                                                             | B-TC-VS11-0-1       | Shipped with<br>  Unit                                                |

| VT100 User Guide                                                                                   | EK-VT100-UG         | Available in<br>  Hard Copy *⊀                                        |

| VT100 Technical<br>Manual                                                                          | EK-VT100-TM         | In Micrifiche<br>  Library;#<br> <br>  Available in<br>  Hard Copy ## |

| DW11 UNIBUS-to-<br>LSI-11 Bus<br>Converter<br>Installation<br>Guide                                | EK-DW11A-IN         | In Microfiche<br>Library;#<br>Available in<br>Hard Copy ##            |

| Installation,<br>Operation and<br>Maintenance<br>Manual for Model<br>HM-2719/2713<br>Color Monitor |                     | Hitachi<br>Publication.<br>Shipped with<br>Color Systems              |

Table 1-3 Related Publications

\* For information concerning microfiche libraries contact:

Digital Equipment Corporation 132 Parker Street Maynard, MA 01754

\*\*These documents can be ordered from:

Digital Equipment Corporation 444 Whitney Street Northboro, MA 01532

ATTN: Printing and Circulation Services (NR2/M15) Customer Services Section

### CHAPTER 2

## VSV11/VS11 INSTALLATION PROCEDURE

The procedures in this Chapter are provided to allow the Field Engineer to successfully install a VSV11 Graphic System on an LSI-11 computer system or a VS11 Graphic System on a PDP-11 or VAX-11 system.

The detailed step-by-step procedure given in the following paragraphs applies to all standard VSV11/VS11 models which contain only one M7061 Sync Generator module and one or two M7062 Image Memory modules. For special "extended" configurations, containing 2 or more Sync Generator modules or 3 or more Image Memory modules refer first to Paragraph 2.8. Installation of these extended configurations can be carried out one memory/sync channel at a time, using the detailed procedures given in Paragraphs 2.1 through 2.6.

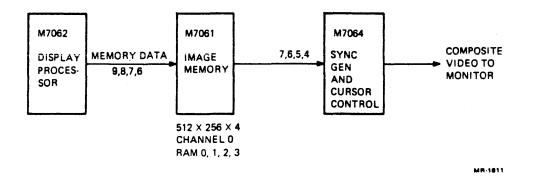

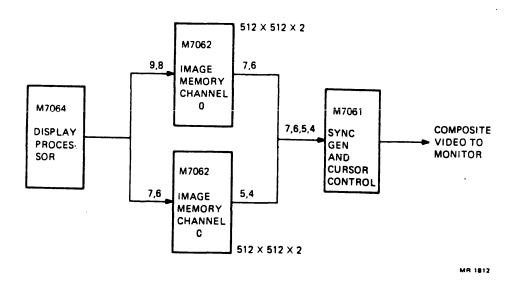

The procedures given below standardize the installation and setup of VSV11/VS11 systems such that any basic system, whether it uses one or two memory modules or must be set up to special customer requirements, contain one memory channel capable of will displaying 16 colors or intensities. For the case of a single Image Memory module, illustrated in the block diagram of Figure 2-1, the mode will be Non-Interlaced, with the memory supplying 4 bits of pixel data in a 512 x 256 array. With two image memory modules, shown in Figure 2-2, the mode will be Interlaced, with each memory module supplying 2 bits of the 4 bits of pixel data in a 512 x 512 pixel array. Furthermore, standard settings for rate, cursor size and color, and operating frequency are blink used during initial installation. After the system is successfully installed using the standard setups, various optional changes can be made to tailor the system to customer (Paragraph 2.6). The use of a standard initial setup will needs facilitate troubleshooting should trouble occur.

In order to install the standard units, the following steps are performed; they are covered in detail in the succeeding paragraphs:

1. Unpack and inventory the components.

- Inspect the computer system and verify that appropriate space and power are available; also determine device and vector addresses to be used.

- 3. Prepare the display monitor (if supplied) by verifying ac power selection. Then, use the keyboard SET-UP functions to set initial operating parameters.

- 4. Verify and/or set up the switches and jumpers on the logic modules to standard settings. (During initial installation, the system is set up to have one memory channel supplying 16 levels of color or intensity; standard settings are also used for Cursor size and color, and for Blink rate. After initial checkout, customer changes can be made.)

- 5. If the unit is a VS11, install the DDV11-CK backplane and UNIBUS-to-LSI-11 Bus Converter.

- 6. Perform initial shorts and power checks.

- 7. Install the logic modules and DBUS Data Cable.

- 8. Connect the Display Monitor and Joystick to the logic modules.

- Check out the system using the supplied diagnostic programs.

- 10. If necessary, perform customer-requested set-up of optional functions via reconfiguration of switches and jumpers on the logic modules; check these out using the diagnostic program.

- 11. Perform final routing of cables and secure mounting box covers.

- 12. Perform unit acceptance using the diagnostic program.

Perform the installation by executing in sequence each of the activities described in the following paragraphs. If trouble is encountered during any step, refer to the troubleshooting procedures in Chapter 7.

Figure 2-1 Single-Memory Non-Interlaced Installation Block Diagram

Figure 2-2 Two-Memory Interlaced Installation Block Diagram

#### 2.1 UNPACKING & INVENTORY

- A. Obtain the Shipping List for the VSV11 or VS11 model at hand and verify that it is what the customer ordered.

- B. Open each carton.

- C. Turn to Appendix A of this manual and find the Parts/Data sheet for the VSV11 or VS11 at hand; there is one sheet for each available VSV11 or VS11 model type.

- D. Unpack each carton and verify that all pieces have been received by comparing against the parts list in the appropriate Parts/Data sheet.

#### 2.2 SYSTEM INSPECTION

A. Installation Site Considerations

The following items must be considered before the VSV11 or VS11 option can be installed:

- 1. Physical and Electrical placement on the bus (LSI-11 Bus or UNIBUS), with respect to:

- (a) System Compatibility (LSI-11 Bus) -- the VSV11 cannot be installed on an LSI-11 system that has options which require the use of External Memory Refresh.

- (b) NPR Priority --- place VSV11/VS11 toward end of bus if possible.

- (c) Option mounting space requirements -- refer to the appropriate Parts/Data sheet in Appendix A for physical space requirements. For example, a VSV11 option requires 3 or 4 adjacent slots in an LSI-11 Bus backplane, while a VS11 option requires a quad-height SPC slot on the UNIBUS plus space for a 4-slot, hex-height DDV11-CK backplane in the same mounting box as the aforementioned SPC slot.

- 2. Device Address and Interrupt Vector Address -- The VSV11 or VS11 requires assignment of four consecutive device addresses (words) in the LSI-11 Bus or UNIBUS I/O Page. It requires a block of 4 interrupt vectors (8 words total) beginning on an address evenly divisible by 16 (20 octal, having bits 3-0 = 0).

The "standard" VSV11/VS11 device address, assigned by Digital Equipment Corporation, is 772000 for the first unit, 772010 for the second unit, etc. The VSV11/VS11

2-4

interrupt vectors are officially assigned to the "floating" address space with a rank of 17.

If, on computer systems running software designed to "Auto-configure" the interrupt vector addresses (such as VAX-VMS), a device is placed at its standard device address, the interrupt vector addresses of all other devices with lower rank in the floating vector space must be moved to higher addresses. For example, if the VS11 is added to a VAX system at its standard address (772000), the vectors on any DZ11's on the system must be moved. Therefore, in order to simplify installation it is recommended that the VS11 device registers be placed at a non-standard address. The following are recommended (if they are not already being used):

> DEVICE ADDRESS (DPC) = 767010 (octal) 1st INTERRUPT VECTOR = 720 (octal)

- 3. Power Requirements

- (a) DC Power -- Refer to the appropriate Parts/Data Sheet in Appendix A.

- (b) AC Power -- The display monitor (CRT screen and associated equipment) requires a source of primary ac power with <u>GROUND</u> and <u>NEUTRAL</u> the same as the <u>mainframe</u> <u>computer</u> <u>sustem</u>. Refer to the appropriate Parts/Data Sheet in Appendix A for outlet supply requirements.

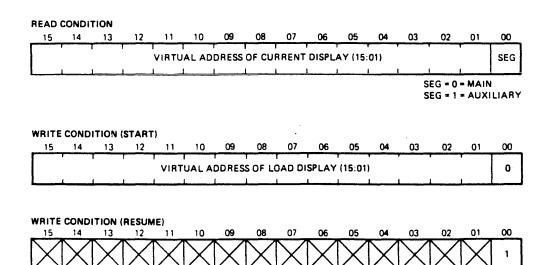

- 4. Monitor Placement The placements of the display monitor and joystick with respect to the VSV11/VS11 logic in the host computer is limited by the length of Monitor (Video) and Joystick cables supplied. Refer to the Field Maintenance Print Set to determine the length of cable supplied (typically 25 feet). Of this length, allow about 7 feet for routing of the cable within the cabinet. For example, with a 25 foot cable, the monitor can be placed up to 18 feet from the host mainframe.