1 -

# pop 04/34/45/55 processor handbook

DIGITAL EQUIPMENT CORPORATION, Corporate Headquarters: Maynard, Massachusetts 01754, Telephone: (617) 897-5111 SALES AND SERVICE OFFICES

UNITED STATES—ALABAMA, Huntsville • ARIZONA, Phoenix and Tucson • CALIFORNIA, El Segundo, Los Angeles, Oakland, Ridgecrest, San Diego, San Francisco (Mountain View), Santa Ana, Santa Clara, Stanford, Sunnyvale and Woodland Hills • COLORADO, Englewood • CONNECTICUT, Fairfield and Meriden • DIS-TRICT OF COLUMBIA, Washington (Lanham, MD) • FLORIDA, Ft. Lauderdale and Orlando • GEORGIA, Atlanta • HAWAII, Honolulu • ILLINOIS, Chicago (Rolling Meadows) • INDIANA, Indianapolis • IOWA, Bettendorf • KENTUCKY, Louisville • LOUISIANA, New Orleans (Metairie) • MARYLAND, Odenton • MASSACHUSETTS, Marlborough, Waltham and Westfield • MICHIGAN, Detroit (Farmington Hills) • MINNESOTA, Minneapolis • MISSOURI, Kansas City (Independence) and St. Louis NEW HAMPSHIRE, Manchester

NEW JERSEY, Cherry Hill, Fairfield, Metuchen and Princeton • NEW MEXICO, Albuquerque • NEW YORK, Albany, Buffalo (Cheektowaga), Long Island (Huntington Station), Manhattan, Rochester and Syracuse • NORTH CAROLINA, Durham/Chapel Hill

OHIO, Cleveland (Euclid), Columbus and Dayton • OKLAHOMA, Tulsa • OREGON, Eugene and Portland • PENNSYLVANIA, Allentown, Philadelphia (Bluebell) and Pittsburgh • SOUTH CAROLINA, Columbia • TENNESSEE, Knoxville and Nashville • TEXAS, Austin, Dallas and Houston • UTAH, Salt Lake City • VIRGINIA, Richmond • WASHINGTON, Bellevue • WISCONSIN, Milwaukee (Brookfield) .

INTERNATIONAL – ARGENTINA, Buenos Aires • AUSTRALIA, Adelaide, Brisbane, Canberra, Melbourne, Perth and Sydney • AUSTRIA, Vienna • BELGIUM, Brussels • BOLIVIA, La Paz • BRAZIL, Rio de Janeiro and Sao Paulo • CANADA, Calgary, Edmonton, Halifax, London, Montreal, Ottawa, Toronto, Vancouver and Winnipeg • CHILE, Santiago • DENMARK, Copenhagen • FINLAND, Helsinki • FRANCE, Grenoble and Paris • GERMAN FEDERAL REPUBLIC, Cologne, Frankfurt, Hamburg, Hannover, Munich, Stuttgart and West Berlin • HONG KONG • INDIA, Bombay • INDONESIA, Djakarta • IRELAND, Dublin • ITALY, Milan, Rome and Turin • IRAN, Tehran • JAPAN, Osaka and Tokyo • MALAYSIA, Kuala Lumpur • MEXICO, Mexico City • NETHERLANDS, Utrecht • NEW ZEALAND, Auckland and Christchurch • NORWAY, Oslo • PUERTO RICO, Santurce • SINGAPORE • SWEDEN, Gothenburg and Stockholm • SWITZERLAND, Geneva and Zurich • UNITED KINGDOM, Birmingham, Bristol, Edinburgh, Leeds, London, Manchester and Reading •

digital equipment corporation

Copyright © 1976, by Digital Equipment Corporation DEC, PDP, UNIBUS are registered trademarks of Digital Equipment Corporation

# CONTENTS

## CHAPTER 1 INTRODUCTION

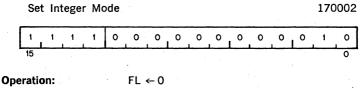

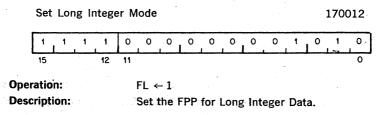

| 1.1 | PDP-11 FAMILY       | · · · · · · · · · · · · · · · · · · · |

|-----|---------------------|---------------------------------------|

| 1.2 | SCOPE               |                                       |

| 1.3 | COMPUTERS           |                                       |

|     | 1.3.1 PDP-11/04     | •••••                                 |

|     |                     |                                       |

|     | 1.3.3 PDP-11/45     |                                       |

|     | 1.3.4 PDP-11/55     |                                       |

| 1.4 | PERIPHERALS/OPTIONS |                                       |

| 1.5 | SOFTWARE            |                                       |

| 1.6 | NUMBER SYSTEMS      |                                       |

# CHAPTER 2 SYSTEM ARCHITECTURE

| 2.1 | UNIBU | JS                        | 2-1 |

|-----|-------|---------------------------|-----|

|     | 2.1.1 | Bidirectional Lines       | 2-1 |

|     | 2.1.2 | Master-Slave Relation     | 2-1 |

|     | 2.1.3 | Interlocked Communication | 2-2 |

| 2.2 | CENT  | RAL PROCESSOR             | 2-2 |

|     |       | General Registers         |     |

|     | 2.2.2 | Instruction Set           | 2-3 |

|     | 2.2.3 | Processor Status Word     | 2-4 |

|     | 2.2.4 | Stacks                    | 2-5 |

| 2.3 | MEMO  | DRY                       | 2-6 |

| 2.4 | AUTO  | MATIC PRIORITY INTERRUPTS | 2-7 |

# CHAPTER 3 ADDRESSING MODES

| 3.1     | SINGLE OPERAND ADDRESSING                | 3-2  |

|---------|------------------------------------------|------|

| 3.2     | DOUBLE OPERAND ADDRESSING                | 3-2  |

| 3.3     | DIRECT ADDRESSING                        | 3-4  |

|         | 3.3.1 Register Mode                      | 3-4  |

|         | 3.3.2 Auto-increment Mode                | 3-5  |

|         | 3.3.3 Auto-decrement Mode                | 3-7  |

| . · · · | 3.3.4 Index Mode                         | 3-8  |

| 3.4     | DEFERRED (INDIRECT) ADDRESSING           | 3-10 |

| 3.5     | USE OF THE PC AS A GENERAL REGISTER      | 3-12 |

|         | 3.5.1 Immediate Mode                     | 3-13 |

|         | 3.5.2 Absolute Addressing                | 3-13 |

|         | 3.5.3 Relative Addressing                | 3-14 |

|         | 3.5.4 Relative Deferred Addressing       | 3-15 |

| 3.6     | USE OF STACK POINTER AS GENERAL REGISTER | 3-16 |

| 3.7     | SUMMARY OF ADDRESSING MODES              | 3-16 |

|         | 3.7.1 General Register Addressing        | 3-16 |

|         | 3.7.2 Program Counter Addressing         | 3-18 |

|         |                                          |      |

# CHAPTER 4 INSTRUCTION SET

| 4.1 | INTRODUCTION   |        |       | 4-1 |

|-----|----------------|--------|-------|-----|

| 4.2 | INSTRUCTION FO | DRMATS | ····· | 4-2 |

| 4.3 | LIST OF INSTRUCTIONS         | 4-4  |

|-----|------------------------------|------|

|     | SINGLE OPERAND INSTRUCTIONS  | 4-6  |

| 4.5 | DOUBLE OPERAND INSTRUCTIONS  | 4-24 |

| 4.6 | PROGRAM CONTROL INSTRUCTIONS | 4-34 |

| 4.7 | MISCELLANEOUS                | 4-72 |

# CHAPTER 5 PROGRAMMING TECHNIQUES

| 5.1 | THE STACK |                              | 5-1  |

|-----|-----------|------------------------------|------|

| 5.2 |           | DUTINE LINKAGE               | 5-5  |

|     | 5.2.1     | Subroutine Calls             | 5-5  |

|     | 5.2.2     | Argument Transmission        | 5-6  |

|     | 5.2.3     | Subroutine Return            | 5-9  |

|     | 5.2.4     | PDP-11 Subroutine Advantages | 5-9  |

| 5.3 | INTER     | RUPTS                        | 5-9  |

|     | 5.3.1     | General Principles           | 5-9  |

|     | 5.3.2     | Nesting                      | 5-10 |

| 5.4 | REEN      | FRANCY                       | 5-13 |

| 5.5 |           | ION INDEPENDENT CODE-PIC     | 5-15 |

| 5.6 |           | UTINES                       | 5-16 |

| 5.7 | PROCE     | ESSOR TRAPS                  | 5-17 |

|     | 5.7.1     | Power Failure                | 5-17 |

|     | 5.7.2     |                              | 5-17 |

|     | 5.7.3     | Time-Out Errors              | 5-17 |

|     | 5.7.4     | Reserved Instructions        | 5-17 |

|     | 5.7.5     | Trap Handling                | 5-17 |

# CHAPTER 6 PDP-11/04

| 6.1 | DESCRIPTION                  | 6-1 |

|-----|------------------------------|-----|

| 6.2 | PDP-11/04 OPTIONS            | 6-2 |

| 6.3 | SPECIFICATIONS               | 6-3 |

| 6.4 | OPERATOR'S CONSOLE OPERATION | 6-4 |

# CHAPTER 7 PDP-11/34

| 7.1  | DESCRIPTION                             | 7-1  |

|------|-----------------------------------------|------|

| 7.2  | SPECIFICATIONS                          | 7-2  |

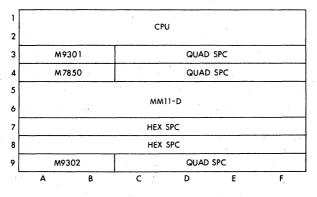

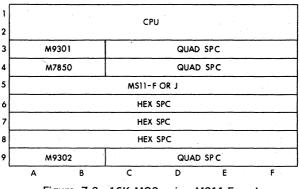

|      | 7.2.1 Processor Backplane Configuration | 7-3  |

|      | 7.2.2 Chassis Configuration             | 7-5  |

| 7.3  | MOS & CORE MEMORY                       | 7-6  |

| 7.4  | BATTERY BACKUP                          | 7-6  |

| 7.5  | M9301 MODULE                            | 7-6  |

| 7.6  | M9302 MODULE                            | 7-7  |

| 7.7  | DL11-W (M7856)                          | 7-8  |

| 7.8  | OPERATOR'S CONSOLE                      | 7-8  |

| 7.9  | CONSOLE EMULATION                       | 7-10 |

| 7.10 | EIS ARITHMETIC OPERATION                | 7-14 |

# CHAPTER 8 PDP-11/34 MEMORY MANAGEMENT

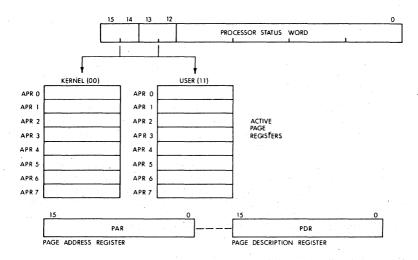

| 8.1 | GENE | RAL               | 8-1 |

|-----|------|-------------------|-----|

|     |      | Memory Management | 8-1 |

|     | 8.1.2 Programming                              | 8-1  |

|-----|------------------------------------------------|------|

|     | 8.1.3 Basic Addressing                         | 8-2  |

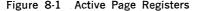

|     | 8.1.4 Active Page Registers                    | 8-2  |

|     | 8.1.5 Capabilities Provided By Memory          |      |

|     | Management                                     | 8-3  |

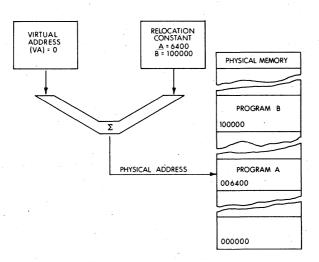

| 8.2 | RELOCATION                                     | 8-3  |

|     | 8.2.1 Virtual Addressing                       | 8-3  |

|     | 8.2.2 Program Relocation                       | 8-4  |

| 8.3 | PROTECTION                                     | 8-6  |

|     | 8.3.1 Inaccessible Memory                      | 8-6  |

|     | 8.3.2 Read-Only Memory                         | 8-6  |

|     | 8.3.3 Multiple Address Space                   | 8-7  |

| 8.4 | ACTIVE PAGE REGISTERS                          | 8-7  |

|     | 8.4.1 Page Address Registers (PAR)             | 8-8  |

|     | 8.4.2 Page Descriptor Registers (PDR)          | 8-8  |

| 8.5 | VIRTUAL AND PHYSICAL ADDRESSES                 | 8-13 |

|     | 8.5.1 Construction of a Physical Address       | 8-13 |

|     | 8.5.2 Determining the Program Physical Address | 8-14 |

| 8.6 | STATUS REGISTERS                               | 8-15 |

|     | 8.6.1 Status Registers 0 (SR0)                 | 8-15 |

|     | 8.6.2 Status Register 2 (SR2)                  | 8-17 |

| 8.7 | INSTRUCTIONS                                   | 8-17 |

|     |                                                |      |

# CHAPTER 9 PDP-11/55, 11/45

| 9.1   | DESC  | RIPTION                            |

|-------|-------|------------------------------------|

| 9.2   | MEMO  | RY                                 |

| 9.3   | PROCI | ESSOR TRAPS                        |

| 9.4   |       | IPROGRAMMING                       |

| 9.5   | SPECI | FICATIONS                          |

| 9.6   | CONS  | OLE OPERATION                      |

|       | 9.6.1 | Console Elements                   |

|       | 9.6.2 | System Power Switch                |

|       | 9.6.3 | Central Processor State Indicators |

|       | 9.6.4 | Address Display Register           |

|       | 9.6.5 | Addressing Error Display           |

|       | 9.6.6 | Data Display Register              |

|       | 9.6.7 | Switch Registers                   |

| , · . | 9.6.8 | Control Switches                   |

2

# CHAPTER 10 PDP-11/55, 11/45 MEMORY MANAGEMENT

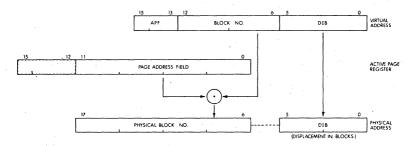

| 10.1 | PDP-11 FAMILY BASIC ADDRESSING LOGIC  | 10-1  |

|------|---------------------------------------|-------|

| 10.2 | VIRTUAL ADDRESSING                    | 10-2  |

| 10.3 | INTERRUPT CONDITIONS UNDER MEMORY     |       |

|      | MANAGEMENT CONTROL                    | 10-3  |

| 10.4 | CONSTRUCTION OF A PHYSICAL ADDRESS    | 10-3  |

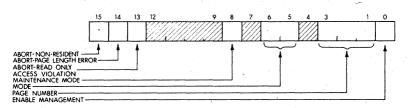

| 10.5 | MANAGEMENT REGISTERS                  | 10-5  |

|      | 10.5.1 Page Address Registers (PAR)   | 10-6  |

|      | 10.5.2 Page Descriptor Register (PDR) | 10-6  |

| 10.6 | FAULT RECOVERY REGISTERS              | 10-8  |

|      | 10.6.1 Status Register #0 (SR0)       | 10-8  |

|      | 10.6.2 Status Register #1 (SR1)       | 10-11 |

| 10 C 2 Status Deviator #2                   | 10-11 |

|---------------------------------------------|-------|

| 10.6.3 Status Register #2                   |       |

| 10.6.4 Status Register #3                   | 10-11 |

| 10.6.5 Instruction Back-Up/Restart Recovery |       |

| 10.6.6 Clearing Status Registers Following  |       |

| Trap/Abort                                  | 10-12 |

| 10.7 EXAMPLES                               | 10-12 |

| 10.7.1 Normal Usage                         | 10-12 |

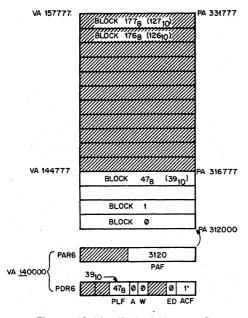

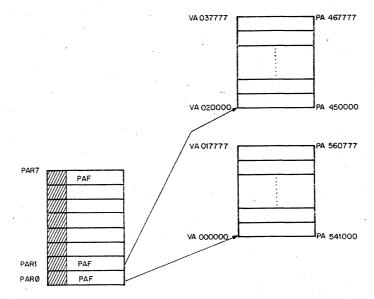

| 10.7.2 Typical Memory Page                  | 10-13 |

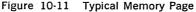

| 10.7.3 Non-Consecutive Memory Pages         | 10-15 |

| 10.7.4 Stack Memory Pages                   | 10-15 |

| 10.8 TRANSPARENCY                           | 10-17 |

| 10.9 INSTRUCTIONS                           | 10-17 |

| 10.10 MEMORY MANAGEMENT UNIT-REGISTER MAP   | 10-21 |

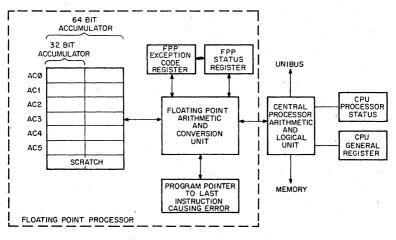

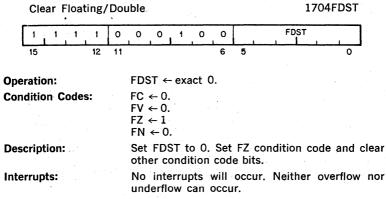

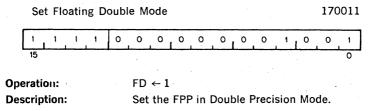

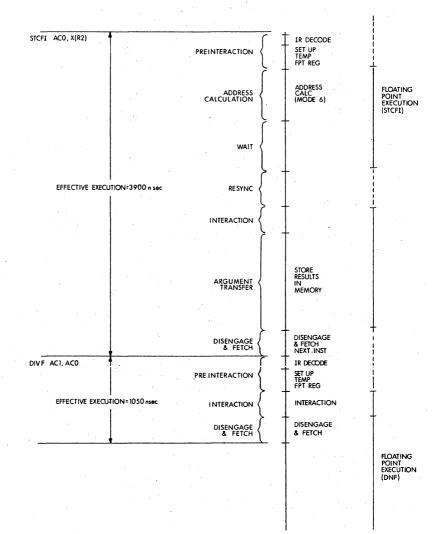

## CHAPTER 11 FLOATING POINT PROCESSOR

| 11.1 | INTRODUCTION                                | 11-1  |

|------|---------------------------------------------|-------|

| 11.2 | OPERATION                                   | 11-1  |

| 11.3 | ARCHITECTURE                                | 11-2  |

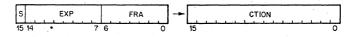

| 11.4 | FLOATING POINT DATA FORMATS                 | 11-3  |

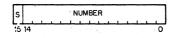

|      | 11.4.1 Non-Vanishing Floating Point Numbers | 11-3  |

|      | 11.4.2 Floating Point Zero                  | 11-3  |

|      | 11.4.3 The Undefined Variable               | 11-3  |

|      | 11.4.4 Floating Point Data                  | 11-4  |

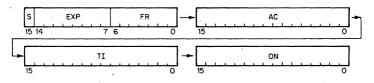

| 11.5 | FLOATING POINT UNIT STATUS REGISTER         |       |

|      | (FPS REGISTER)                              | 11-5  |

| 11.6 | FLOATING EXCEPTION CODE AND                 |       |

|      | ADDRESS REGISTERS                           | 11-9  |

| 11.7 | FLOATING POINT PROCESSOR INSTRUCTION        | . •   |

|      |                                             | 11-10 |

| 11.8 | ACCURACY                                    | 11-10 |

| 11.9 | FLOATING POINT INSTRUCTIONS                 | 11-12 |

|      |                                             |       |

# APPENDIX A UNIBUS ADDRESSES

| A.1 | INTERRUPT AND TRAP VECTORS | A-1 |

|-----|----------------------------|-----|

| A.2 | FLOATING VECTORS           | A-2 |

| A.3 | FLOATING ADDRESSES         | A-3 |

| A.4 | DEVICE ADDRESSES           | A-3 |

## APPENDIX B INSTRUCTION TIMING

| B.1 PDP-11/04 CENTRAL PROCESSOR         | B-1  |

|-----------------------------------------|------|

| B.2 PDP-11/34 CENTRAL PROCESSOR         | B-3  |

| B.3 FP11-A FLOATING POINT PROCESSOR     | B-8  |

| B.4 PDP-11/55, 11/45 CENTRAL PROCESSORS | B-12 |

| B.5 FP11-C FLOATING POINT PROCESSOR     |      |

| INSTRUCTION EXECUTION TIME              | B-21 |

| APPENDIX C INSTRUCTION INDEX            | C-1  |

# **CHAPTER 1**

# INTRODUCTION

#### 1.1 PDP-11 FAMILY

The PDP-11 family includes several central processor units (CPU's), a large number of peripheral devices and options, and extensive software. New equipment will be compatible with existing family members. The user can choose the system which is most suitable for his application, but as needs change, he can easily add or change hardware.

All PDP-11 computers discussed in this Handbook have the following features:

- 16-bit word (two 8-bit bytes) direct addressing of 32K 16-bit words or 64K 8-bit bytes (K = 1024)

- Word or byte processing very efficient handling of 8-bit characters without the need to rotate, swap, or mask

- Asynchronous operation system components run at their highest possible speed, replacement with faster subsystems means faster operation without other hardware or software changes

- Modular component design extreme ease and flexibility in configuring systems

- Stack processing hardware sequential memory manipulation makes it easy to handle structured data, subroutines, and interrupts

- Direct Memory Access (DMA) inherent in the architecture is direct memory access for multiple devices

- 8 internal general-purpose registers used interchangeably for accumulators or address generation

- Automatic Priority Interrupt

- four-line, multi-level system permits grouping of interrupt lines according to response requirements

- Vectored interrupts fast interrupt response without device polling

- Single & double operand instructions powerful and convenient set of programming instructions

- Power Fail & Automatic Restart hardware detection and software protection for fluctuations in the AC power

#### 1.2 SCOPE

This Handbook describes the following computers designed and manufactured by Digital Equipment Corporation.

PDP-11/04 PDP-11/34 PDP-11/45 PDP-11/55

The intent is to provide extensive information on operation of the computers in general, performance and features of the computers, and basic programming. This Handbook is not intended to be the sole reference for the computers. More comprehensive and detailed information is available in Processor Manuals, Maintenance Manuals, and Programming Manuals.

#### **1.3 COMPUTERS**

#### 1.3.1 PDP-11/04

The PDP-11/04 computer uses MOS semiconductor memory, and is housed in a  $5\frac{1}{4}$ " high assembly. Between 4K and 28K words of memory can be implemented within the basic assembly unit, which includes expansion space and DC power for adding options.

The PDP-11/04 is a full-fledged computer that can execute all the basic PDP-11 instructions. It enjoys the advantage of being able to use all the extensive developed software and peripheral equipment. If there is ever a need to upgrade to a more powerful central processor, the PDP-11/04 can simply be replaced by a different PDP-11 CPU, and software and peripherals remain the same in the system.

The minimum PDP-11/04 includes:

- 4K words of MOS memory Increased processing speed at a lower cost per bit.

- Automatic bootstrap loader Automatic starts from a variety of peripheral devices.

- Self-test feature

ROM hardware automatically performs diagnostics on the CPU and memory. Pinpoints failures to the circuit board level, thereby reducing maintenance costs.

Operator's front panel

Allows complete control of the computer via any ASCII terminal. All front panel functions are key entries on the terminal either local or remote, thereby eliminating the need and cost of a programmer's console.

The following optional equipment is available:

Battery backup Programmer's console Line frequency clock Serial communications line interface The PDP-11/04 is prewired to accept extra memory, communication interfaces, and standard peripheral device controllers. The included CPU power supply has sufficient excess capacity to handle optional internal equipment.

## 1.3.2 PDP-11/34

The PDP-11/34 is a systems level computer that includes increased memory expansion to 124K words, memory relocation and protection, faster processing speeds, and hardware multiply and divide instructions. The computer system is mounted in a  $5^{1}/_{4}$ " or  $10^{1}/_{2}$ " chassis that mounts in a standard 19." cabinet. The PDP-11/34 processor is prewired to accept additional memory (parity core or MOS) and standard peripheral device controllers including communications interfaces, mass storage controllers, etc. Additional mounting space is provided within the  $10^{1}/_{2}$ " computer supply within the chassis is capable of powering the optional internal devices.

The PDP-11/34 computer, as a member of the PDP-11 family, has the following features:

- Single & double operand instructions powerful and convenient set of programming instructions

- Hardware implemented multiply and divide instructions

- 16-bit word (two 8-bit bytes) direct addressing of 32K words or 64K bytes (K = 1024)

- Parity detection on each 8-bit byte

- Hardware address expansion and protection allowing memory addressing to 124K words

- Word or byte processing very efficient handling of 8-bit data without the need to rotate, swap, or mask

- Asynchronous operation system components run at their highest possible speed, replacement with faster subsystems means faster operation without other hardware or software changes

- Modular component design extreme ease and flexibility in configuring systems

- Stack processing hardware sequential memory manipulation makes it easy to handle structured data, subroutines, and interrupts

- Direct Memory Access (DMA) inherent in the architecture is direct memory access for multiple devices

- 8 internal general-purpose registers used interchangeably for accumulators or address generation

- Automatic Priority Interrupt four-line, multi-level system permits grouping of interrupt lines according to response requirements

- Vectored interrupts fast interrupt response without device polling

- Power Fail & Automatic Restart Hardware detection and software protection for fluctuations in the AC power

The minimum PDP-11/34 includes:

- · Parity MOS or core memory

- Memory management Program protection and relocation for memory expansion to 124K 16bit words

- Automatic bootstrap loader Automatic starts from a variety of peripheral devices

- Self-test feature ROM hardware automatically performs diagnostics on the CPU and memory

- Operator's front panel Allows complete control of the computer via any ASCII terminal. All front panel functions are key entries on the terminal, thereby eliminating the need and cost of a programmer's lights and switches console.

The following optional equipment is available:

- Battery backup for MOS memory

- Programmer's console

- Serial communications line interface and line frequency clock

- Large variety of standard PDP-11 peripherals

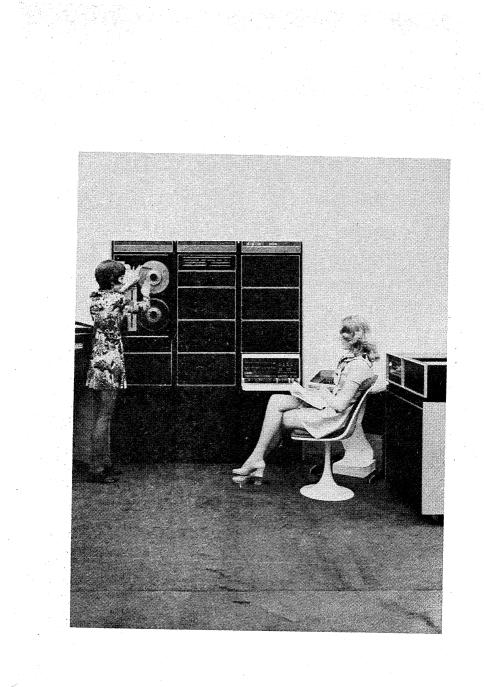

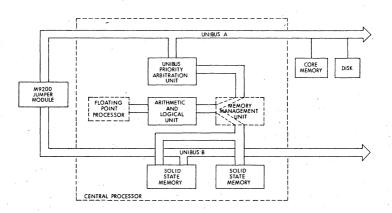

#### 1.3.3 PDP-11/45

The PDP-11/45 is a powerful 16-bit computer designed as a powerful computational tool for high-speed real-time applications and for large multi-user, multi-task applications requiring up to 124K words of addressable memory space. It will operate with solid state and core memories, and includes many features not normally associated with 16-bit computers. Among its major features are a fast central processor with choices of 300 or 495 nanosecond memory, an advanced Floating Point Processor, and a sophisticated memory management scheme.

Included with the basic PDP-11/45 are:

- 16K words of memory

- · Choice of bipolar, and core memory

- Programmer console

- Cabinet

- Prewired mounting space to accept Floating Point and Memory Management hardware

The PDP-11/45 features include:

- Memory expandable to 256K bytes.

- Memory segmentation, protection, and relocation.

- Optional FP11-C Floating Point Processor with advanced features and high-speed operation.

- Reliable core memory.

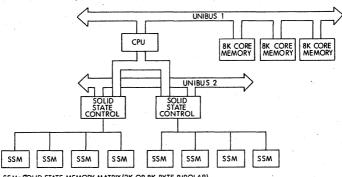

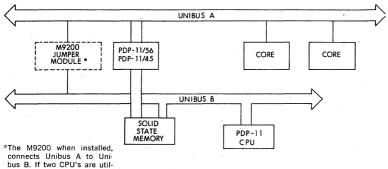

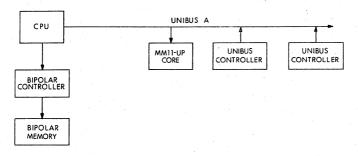

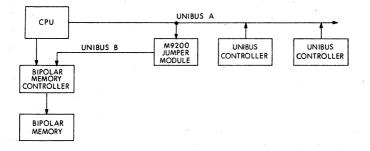

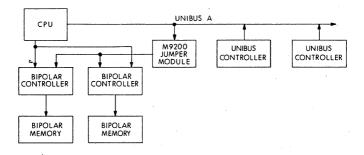

- Fast secondary bus between processor and solid state memory which operates in parallel with Unibus.

- Powerful instruction set providing over 400 commands.

- Powerful I/O structure provides easy interfacing and simplifies the construction of multiprocessor or shared peripheral configurations.

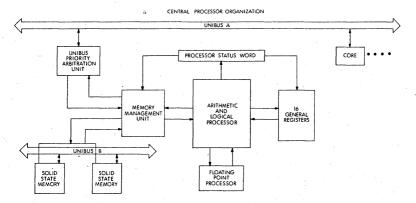

#### 1.3.4 PDP-11/55

The PDP-11/55 is a completely functional computer system especially designed to accelerate FORTRAN compiled tasks, whether for critical process control, simulation lab experiments, engineering and scientific applications, etc.

PDP-11/55 features include:

- 300 nanosecond, dual-ported bipolar memory

- High speed floating point processor with 46 hardwired instructions

- · Internal micro-instruction cycle time of 150 nanoseconds

- Instruction execution time of 300 nanoseconds

- Instruction pipelining allows the fetch of the next program instruction to be overlapped with the instruction currently in execution.

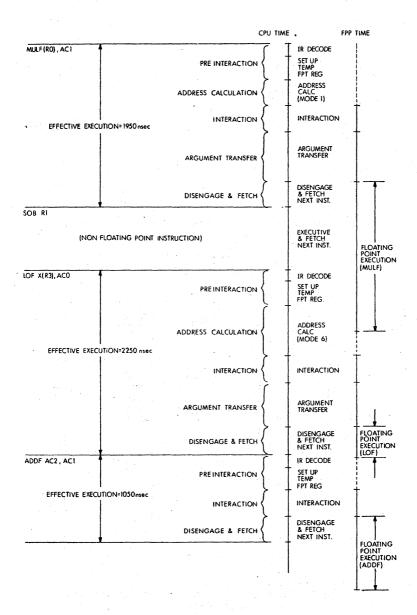

- Floating point calculation can be performed independent of central processor operations, freeing the CPU to simultaneously perform nonfloating point computations.

- Dual bus structure allows direct memory access without cycle stealing on the UNIBUS.

- Up to 256K bytes of combined bipolar and core memory (up to 64K bytes bipolar alone).

- Three CPU operating modes (kernel, supervisor, and user) which enhance system operating efficiency and program protection.

- Hardware memory management, with three sets of memory management registers—one set per CPU operating mode.

- Two sets of eight general purpose registers which, coupled with three CPU operating modes, eliminate the need for saving register contents in a real-time applications environment.

- Direct memory access.

- · Power fail/auto restart.

#### 1.4 PERIPHERALS/OPTIONS

Digital Equipment Corporation designs and manufactures many of the peripheral devices offered with PDP-11's. As a designer and manufacturer of peripherals, DIGITAL can offer extremely reliable equipment, lower prices, more choice and quantity discounts.

#### I/O Devices

All PDP-11 systems can use a Teletype as the basic I/O device. However, I/O capabilities can be increased with high-speed paper tape readerpunches, line printers, card readers or alphanumeric display terminals. The LA36 DECwriter, a totally designed and built teleprinter, can serve as an alternative to the Teletype. It has several advantages over standard electromechanical typewriter terminals, including higher speed, fewer mechanical parts and very quiet operation.

PDP-11 devices include:

Cassette, TA11 Floppy disk, RX01 DECterminal alphanumeric display, VT50 DECwriter teleprinter, LA36 High Speed Line Printers, LS11, LP11, LV11 High Speed Paper Tape Reader and Punch, PC11 Teletypes, LT33 Card Readers, CR11, CD11, CM11 Graphics Terminal, GT40 Synchronous and Asynchronous Communications Interfaces

## Storage Devices

Storage devices range from convenient, small-reel magnetic tape (DECtape) units to mass storage magnetic tapes and disk memories. With the UNIBUS, a large number of storage devices, in any combination, may be connected to a PDP-11 system. TU56 DECtapes, highly reliable tape units with small tape reels, designed and built by DEC, are ideal for applications with modest storage requirements. Each DECtape provides storage for 144K 16-bit words. For applications which require handling of large volumes of data, DEC offers the industry compatible TU16 Magtape.

Disk storage include fixed-head disk units and moving-head removable cartridge and disk pack units. These devices range from the 256K word RS03 fixed head disk, to the RP04 Disk Pack which can store up to 44 million words.

#### 1.5 SOFTWARE

The PDP-11 family of central processors and peripherals is supported by a comprehensive family of licensed software products. This software family includes support for small stand-alone configurations, disk based real-time and program development systems, large multi-programming and time-sharing systems, and many diverse dedicated applications. Some examples of general purpose operating systems and standard high level language processors are:

- PAPER TAPE SYSTEM (PTS-11)—A core only high-speed paper tape system with program development in assembly language. Editor, debugger, and linker are supplied along with a relocating assembler.

- CASSETTE PROGRAMMING SYSTEM (CAPS-11)—A small program development system with a core based monitor, utilizing dual magnetic tape cassettes as file structured media. Complete program development utilities such as a relocating assembler, linker, editor, debugger, and file interchange program are included.

- SINGLE USER ON-LINE PROGRAM DEVELOPMENT SYSTEM (RT-11)— A small, powerful, easy-to-use disk (or DECtape) based system for program development or fast on-line (real-time) applications. A Foreground/Background version can accommodate simultaneous program development in the background with on-line applications in the foreground. A MACRO assembler, linker, editor, debugger, and file utility programs are included.

- MULTI-TASKING PROCESS CONTROL SYSTEM (RSX-11M)—An efficient multi-tasking system suitable for controlling many processes simultaneously, in a protected environment with concurrent development of new programs. Utilities include a MACRO assembler, task builder (linker), editor, debugger, and file utility programs.

- COMPREHENSIVE MULTI-PROGRAMMING SYSTEM (RSX-11D)—The total job operating system. As a compatible extension of RSX-11M, the system allows concurrent fully hardware protected execution of multiple on-line jobs, with BATCH program development. Complete utilities include a MACRO assembler, task builder (linker), editor, debugger, and file utility programs.

- EXTENDED RESOURCE TIME SHARING SYSTEM (RSTS/E)—A diskbased time-sharing system implementing BASIC-PLUS, an enriched version of the popular BASIC language. Up to 32 simultaneous users share system resource via interactive terminals. Additional features such as output spooling, and comprehensive file protection are included.

- INTERACTIVE APPLICATION SYSTEM (IAS)—A multifunction operating system executing on the larger PDP-11 hardware configurations. It can handle a mix of time-sharing, batch, and real-time applications concurrently. It is also a multi-lingual system, allowing users to choose the high-level language most appropriate for the particular problem at hand.

#### Languages

- BASIC-11—An extended version of Dartmouth Standard BASIC is available for PTS-11, CAPS-11 and RT-11. Many applications, such as signal processing and graphics are accessed by the user through extensions to this simple, yet powerful, language. A multiuser version is available under PTS-11 and RT-11.

- PDP-11 FORTRAN IV—An extended version of ANSI standard FOR-TRAN is supplied with RSX-11M and RSX-11D, and available under RT-11. As an optimizing compiler, FORTRAN IV is designed for fast compilation, yet requires very little main memory, and generates highly efficient code without sacrificing execution speed. Under RT-11,

FORTRAN IV features the same signal-processing and graphics extensions as BASIC-11.

- FORTRAN-IV PLUS—A compatible extension to PDP-11 FORTRAN IV, this system uses sophisticated optimizations to achieve the fastest possible execution speed of the generated code. FORTRAN IV-PLUS requires a PDP-11/55 or 11/45 and Floating Point Processor hardware, in addition to the RSX-11D operating system.

- PDP-11 COBOL—To supplement the business data processing needs often associated with large scale PDP-11 system applications, an ANSI-74 COBOL language is available under RSX-11D. Running as a BATCH job, COBOL enhances the RSX-11D total job computing system, where some business data processing is required.

In addition to the above mentioned general purpose licensed software products, DIGITAL offers a great number of optional and applications oriented products. A wide range of educational, consulting, and maintenance services are also offered, to ensure full utility of any PDP-11 system. For a complete and detailed listing of DIGITAL software products and services, consult the latest CATALOG OF SOFTWARE PRODUCTS and SERVICES.

#### 1.6 NUMBER SYSTEMS

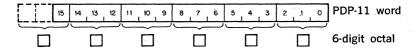

Throughout this Handbook, 3 number systems will be used; octal, binary, and decimal. So as not to clutter all numbers with subscripted bases, the following general convention will be used:

- Octal—for address locations, contents of addresses, and operation codes for instructions; in most cases there will be words of 6 octal digits

- Binary—for describing a single binary element; when referring to a PDP-11 word it will be 16 bits long

Decimal-for all normal referencing to quantities

#### **Octal Representation**

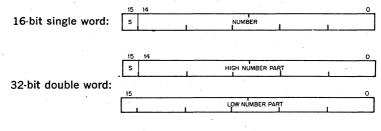

The 16-bit PDP-11 word can be represented conveniently as a 6-digit octal word. Bit 15, the Most Significant Bit (MSB), is used directly as the Most Significant Digit of the octal word. The other 5 octal digits are formed from the corresponding groups of 3 bits in the binary word.

When an extended address of 18 bits is used (shown later in the Handbook), the Most Significant Digit of the octal word is formed from bits 17, 16, and 15. For unsigned numbers, the correspondence between decimal and octal is:

| Decimal              | Uclai  |                |

|----------------------|--------|----------------|

| 0                    | 000000 |                |

| $(2^{16}-1)=65,535$  | 177777 | (16-bit limit) |

| $(2^{18}-1)=262,143$ | 777777 | (18-bit limit) |

#### 2's Complement Numbers

In this system, the first bit (bit 15) is used to indicate the sign;

0=positive 1=negative

D - - !-- - 1

For positive numbers, the other 15 bits represent the magnitude directly; for negative numbers, the magnitude is the 2's complement of the remaining 15 bits. (The 2's complement is equal to the 1's complement plus one.) The ordering of numbers is shown below:

| Decimal                  | Decimal 2's Complement (Octal |                |  |

|--------------------------|-------------------------------|----------------|--|

|                          | Sign Bit                      | Magnitude Bits |  |

| largest positive +32,767 | 0                             | 77777          |  |

| +32,766                  | 0                             | 77776          |  |

| +1                       | 0                             | 00001          |  |

| 0                        | 0                             | 00000          |  |

| -1                       | 1                             | 77777          |  |

| <b>—2</b>                | 1                             | 77776          |  |

| -32,767                  | 1                             | 00001          |  |

| most negative -32,768    | 1                             | 00000          |  |

# **CHAPTER 2**

# SYSTEM ARCHITECTURE

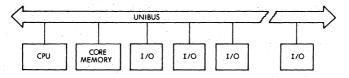

#### 2.1 UNIBUS

Most computer system components and peripherals connect to and communicate with each other on a single high-speed bus known as the UNIBUS— a key to the PDP-11's many strengths. Addresses, data, and control information are sent along the 56 lines of the bus.

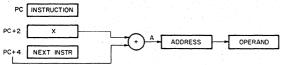

#### Figure 2-1 PDP-11 System Simplified Block Diagram

The form of communication is the same for every device on the UNIBUS. The processor uses the same set of signals to communicate with memory as with peripheral devices. Peripheral devices also use this set of signals when communicating with the processor, memory or other peripheral devices. Each device, including memory locations, processor registers, and peripheral device registers, is assigned an address on the UNIBUS. Thus, peripheral device registers may be manipulated as flexibly as core memory by the central processor. All the instructions that can be applied to data in core memory can be applied equally well to data in peripheral device registers. This is an especially powerful feature, considering the special capability of PDP-11 instructions to process data in any memory location as though it were an accumulator.

#### 2.1.1 Bidirectional Lines

With bidirectional and asynchronous communications on the UNIBUS, devices can send, receive, and exchange data independently without processor intervention. For example, a cathode ray tube (CRT) display can refresh itself from a disk file while the central processor unit (CPU) attends to other tasks. Because it is asynchronous, the UNIBUS is compatible with devices operating over a wide range of speeds.

#### 2.1.2 Master-Slave Relation

Communication between two devices on the bus is in the form of a master-slave relationship. At any point in time, there is one device that has control of the bus. This controlling device is termed the "bus master." The master device controls the bus when communicating with another device on the bus, termed the "slave." A typical example of this relationship is the processor, as master, fetching an instruction from memory (which is always a slave). Another example is the disk, as

master, transferring data to memory, as slave. Master-slave relationships are dynamic. The processor, for example, may pass bus control to a disk. The disk, as master, could then communicate with a slave memory bank.

Since the UNIBUS is used by the processor and all I/O devices, there is a priority structure to determine which device gets control of the bus. Every device on the UNIBUS which is capable of becoming bus master is assigned a priority. When two devices, which are capable of becoming a bus master, request use of the bus simultaneously, the device with the higher priority will receive control.

#### 2.1.3 Interlocked Communication

Communication on the UNIBUS is interlocked so that for each control signal issued by the master device, there must be a response from the slave in order to complete the transfer. Therefore, communication is independent of the physical bus length (as far as timing is concerned) and the timing of each transfer is dependent only upon the response time of the master and slave devices. The asynchronous operation precludes the need for synchronizing with, and waiting for, clock impulses. Thus, each system is allowed to operate at its maximum possible speed.

Input/output devices transferring directly to or from memory are given highest priority and may request bus mastership and steal bus and memory cycles during instruction operations. The processor resumes operation immediately after the memory transfer. Multiple devices can operate simultaneously at maximum direct memory access (DMA) rates by "stealing" bus cycles.

Full 16-bit words or 8-bit bytes of information can be transferred on the bus between a master and a slave. The information can be instructions, addresses, or data. This type of operation occurs when the processor, as master, is fetching instructions, operands, and data from memory, and storing the results into memory after execution of instructions. Direct data transfers occur between a peripheral device control and memory.

#### 2.2 CENTRAL PROCESSOR

The central processor, connected to the UNIBUS as a subsystem, controls the time allocation of the UNIBUS for peripherals and performs arithmetic and logic operations and instruction decoding. It contains multiple high-speed general-purpose registers which can be used as accumulators, address pointers, index registers, and other specialized functions. The processor can perform data transfers directly between I/O devices and memory without disturbing the processor registers; does both single- and double-operand addressing and handles both 16-bit word and 8-bit byte data.

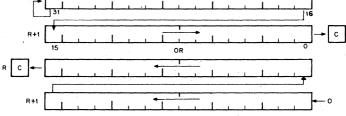

#### 2.2.1 General Registers

The central processor contains 8 general registers which can be used for a variety of purposes. (The PDP-11/55, 11/45 contains 16 general

registers.) The registers can be used as accumulators, index registers, autoincrement registers, autodecrement registers, or as stack pointers for temporary storage of data. Chapter 3 on Addressing describes these uses of the general registers in more detail. Arithmetic operations can be from one general register to another, from one memory or device register to another, or between memory or a device register and a general register. Refer to Figure 2-2.

Fgure 2-2 The General Registers

R7 is used as the machine's program counter (PC) and contains the address of the next instruction to be executed. It is a general register normally used only for addressing purposes and not as an accumulator for arithmetic operations.

The R6 register is normally used as the Stack Pointer indicating the last entry in the appropriate stack (a common temporary storage area with "Last-in First-Out" characteristics).

#### 2.2.2 Instruction Set

The instruction complement uses the flexibility of the general-purpose registers to provide over 400 powerful hard-wired instructions-the most comprehensive and powerful instruction repertoire of any computer in the 16-bit class. Unlike conventional 16-bit computers, which usually have three classes of instructions (memory reference instructions, operate or AC control instructions and I/O instructions) all operations in the PDP-11 are accomplished with one set of instructions. Since peripheral device registers can be manipulated as flexibly as core memory by the central processor, instructions that are used to manipulate data in core memory may be used equally well for data in peripheral device registers. For example, data in an external device register can be tested or modified directly by the CPU, without bringing it into memory or disturbing the general registers. One can add data directly to a peripheral device register, or compare logically or arithmetically. Thus all PDP-11 instructions can be used to create a new dimension in the treatment of computer I/O and the need for a special class of I/O instructions is eliminated.

The basic order code of the PDP-11 uses both single and double operand address instructions for words or bytes. The PDP-11 therefore performs

very efficiently in one step, such operations as adding or subtracting two operands, or moving an operand from one location to another.

| · · ·                  | PDP-11 Approach                                                             |

|------------------------|-----------------------------------------------------------------------------|

| ADD A,B                | ;add contents of location A to loca-<br>tion B, store results at location B |

|                        | Conventional Approach                                                       |

| LDA A                  | load contents of memory location A into AC                                  |

| ADD B                  | ;add contents of memory location B to AC                                    |

| STA Base of the second | ;store result at location B                                                 |

PDP.11 Approach

#### Addressing

Much of the power of the PDP-11 is derived from its wide range of addressing capabilities. PDP-11 addressing modes include sequential addressing forwards or backwards, addressing indexing, indirect addressing, 16-bit word addressing, 8-bit byte addressing, and stack addressing. Variable length instruction formating allows a minimum number of bits to be used for each addressing mode. This results in efficient use of program storage space.

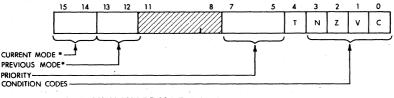

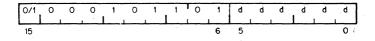

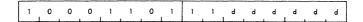

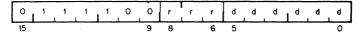

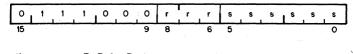

#### 2.2.3 Processor Status Word

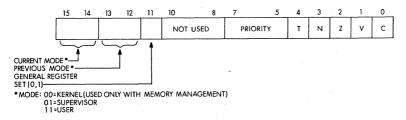

\* MODE } USED ONLY ON PDP-11/55, & 11/45 WITH MEMORY MANAGEMENT

#### Figure 2-3 Processor Status Word

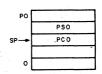

The Processor Status word (PS), at location 777776, contains information on the current status of the PDP-11. This information includes the current processor priority: current and previous operational modes; the condition codes describing the results of the last instruction; and an indicator for detecting the execution of an instruction to be trapped during program debugging.

#### Processor Priority

The Central Processor operates at any one of eight levels of priority, 0-7. When the CPU is operating at level 7 an external device cannot interrupt it with a request for service. The Central Processor must be operating at a lower priority than the external device's request in order for the interruption to take effect. The current priority is maintained in the processor status word (bits 5-7). The 8 processor levels provide an effective interrupt mask.

#### Condition Codes

The condition codes contain information on the result of the last CPU operation.

The bits are set as follows:

- Z = 1, if the result was zero

- N = 1, if the result was negative

- C = 1, if the operation resulted in a carry from the MSB

- V = 1, if the operation resulted in an arithmetic overflow

#### Trap

The trap bit (T) can be set or cleared under program control. When set, a processor trap will occur through location 14 on completion of instruction execution and a new Processor Status Word will be loaded. This bit is especially useful for debugging programs as it provides an efficient method of installing breakpoints.

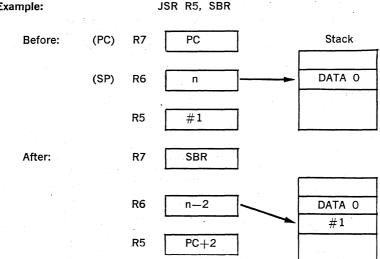

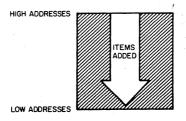

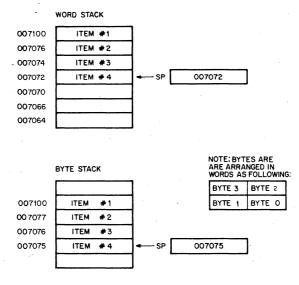

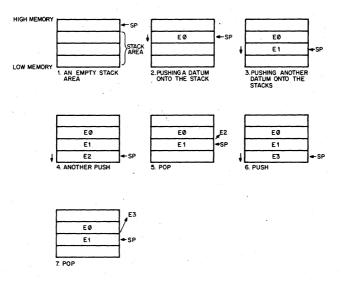

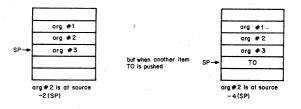

#### 2.2.4 Stacks

In the PDP-11, a stack is a temporary data storage area which allows a program to make efficient use of frequently accessed data. A program can add or delete words or bytes within the stack. The stack uses the "last-in, first-out" concept: that is, various items may be added to a stack in sequential order and retrieved or deleted from the stack in reverse order. On the PDP-11, a stack starts at the highest location reserved for it and expands linearly downward to the lowest address as items are added. The stack is used automatically by program interrupts, subroutine calls, and trap instructions. When the processor is interrupted, the central processor status word and the program counter are saved (pushed) onto the stack area, while the processor services the interrupting device. A new status word is then automatically acquired from an area in core memory which is reserved for interrupt instructions (vector area). A return from the interrupt instruction restores the original processor status and returns to the interrupted program without software intervention.

#### 2.3 MEMORY

نۍ

#### **Memory Organization**

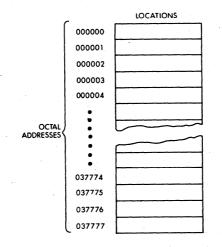

A memory can be viewed as a series of locations, with a number (address) assigned to each location. Thus an 8,192-word PDP-11 memory could be shown as in Figure 2-4.

Figure 2-4 Memory Addresses

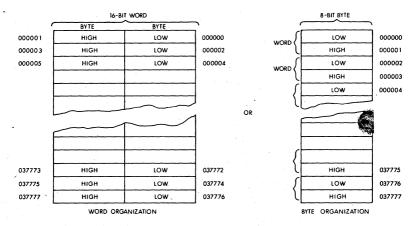

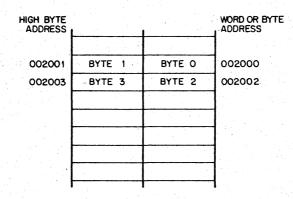

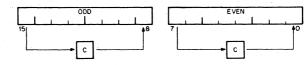

Because PDP-11 memories are designed to accommodate both 16-bit words and 8-bit bytes, the total number of addresses does not correspond to the number of words. An 8K-word memory can contain 16K bytes and consist of 037777 octal locations. Words always start at even-numbered locations.

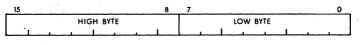

A PDP-11 word is divided into a high byte and a low byte as shown in Figure 2-5.

Figure 2-5 High & Low Byte

Low bytes are stored at even-numbered memory locations and high bytes at odd-numbered memory locations. Thus it is convenient to view the PDP-11 memory as shown in Figure 2-6.

Figure 2-6 Word and Byte Addresses

Certain memory locations have been reserved by the system for interrupt and trap handling, processor stacks, general registers, and peripheral device registers. Addresses from 0 to  $370_{\rm g}$  are always reserved and those to  $777_{\rm g}$  are reserved on large system configurations for traps and interrupt handling.

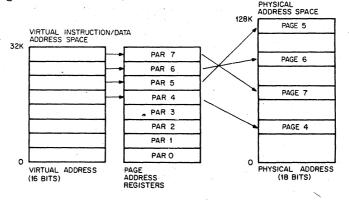

A 16-bit word used for byte addressing can address a maximum of 32K words. However, the top 4,096 word locations are reserved for peripheral and register addresses and the user therefore has 28K of core to program. With the PDP-11/55 and 11/45, the user can expand above 28K with the Memory Management. This device provides an 18-bit effective memory address which permits addressing up to 124K words of actual memory.

If the Memory Management option is not used, an octal address between 160 000 and 177 777 is interpreted as 760 000 to 777 777. That is, if bit 15, 14 and 13 are 1's, then bits 17 and 16 (the extended address bits) are considered to be 1's, which relocates the last 4K words (8K bytes) to become the highest locations accessed by the UNIBUS.

## 2.4 AUTOMATIC PRIORITY INTERRUPTS

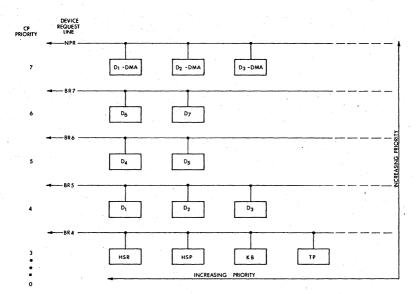

The multi-level automatic priority interrupt system permits the processor to respond automatically to conditions outside the system. Any number of separate devices can be attached to each level.

Figure 2-7 UNIBUS Priority

Each peripheral device in the PDP-11 system has a pointer to its own pair of memory words (one points to the devices's service routine, and the other contains the new processor status information). This unique identification eliminates the need for polling of devices to identify an interrupt, since the interrupt service hardware selects and begins executing the appropriate service routine after having automatically saved the status of the interrupted program segment.

The devices' interrupt priority and service routine priority are independent. This allows adjustment of system behavior in response to real-time conditions, by dynamically changing the priority level of the service routine.

The interrupt system allows the processor to continually compare its own programmable priority with the priority of any interrupting devices and to acknowledge the device with the highest level above the processor's priority level. The servicing of an interrupt for a device can be interrupted in order to service an interrupt of a higher priority. Service to the lower priority device is resumed automatically upon completion of the higher level servicing. Such a process, called nested interrupt servicing, can be carried out to any level without requiring the software to save and restore processor status at each level.

When a device (other than the central processor) is capable of becoming bus master and requests use of the bus, it is generally for one of two purposes:

1. To make a non-processor transfer of data directly to or from memory

2. To interrupt a program execution and force the processor to go to a specific address where an interrupt service routine is located.

#### Direct Memory Access

All PDP-11's provide for direct access to memory. Any number of DMA devices may be attached to the UNIBUS. Maximum priority is given to DMA devices, thus allowing memory data storage or retrieval at memory cycle speeds. Response time is minimized by the organization and logic of the UNIBUS, which samples requests and priorities in parallel with data transfers.

Direct memory or direct data transfers can be accomplished between any two peripherals without processor supervision. These non-processor request transfers, called NPR level data transfers, are usually made for Direct Memory Access (memory to/from mass storage) or direct device transfers (disk refreshing a CRT display).

#### **Bus Requests**

Bus requests from external devices can be made on one of five request lines. Highest priority is assigned to non-processor request (NPR). These are direct memory access type transfers, and are honored by the processor between bus cycles of an instruction execution.

The processor's priority can be set under program control to one of eight levels using bits 7, 6, and 5 in the processor status register. These bits set a priority level that inhibits granting of bus requests on lower levels or on the same level. When the processor's priority is set to a level, for example PS6, all bus requests on BR6 and below are ignored.

When more than one device is connected to the same bus request (BR) line, a device nearer the  $ce^{p^*}$  processor has a higher priority than a device farther away. Any number of devices can be connected to a given BR or NPR line.

Thus the priority system is two-dimensional and provides each device with a unique priority. Each device may be dynamically, selectively enabled or disabled under program control.

Once a device other than the processor has control of the bus, it may do one of two types of operations: data transfers or interrupt operations.

#### NPR Data Transfers

NPR data transfers can be made between any two peripheral devices without the supervision of the processor. Normally, NPR transfers are between a mass storage device, such as a disk, and core memory. The structure of the bus also permits device-to-device transfers, allowing customer-designed peripheral controllers to access other devices, such as disks, directly.

An NPR device has very fast access to the bus and can transfer at high data rates once it has control. The processor state is not affected by the transfer; therefore the processor can relinquish control while an instruction is in progress. This can occur at the end of any bus cycles except in between a read-modify-write sequence. An NPR device in control of the bus may transfer 16-bit words from memory at memory speed.

#### **BR Transfers**

Devices that gain bus control with one of the Bus Request lines (BR 7-BR4) can take full advantage of the Central Processor by requesting an interrupt. In this way, the entire instruction set is available for manipulating data and status registers.

When a service routine is to be run, the current task being performed by the central processor is interrupted, and the device service routine is initiated. Once the request has been satisfied, the Processor returns to its former task.

#### Interrupt Procedure

Interrupt handling is automatic in the PDP-11. No device polling is required to determine which service routine to execute. The operations required to service an interrupt are as follows:

- 1. Processor relinquishes control of the bus, priorities permitting.

- 2. When a master gains control, it sends the processor an interrupt command and an unique memory address which contains the address of the device's service routine, called the interrupt vector address. Immediately following this pointer address is a word (located at vector address +2) which is to be used as a new Processor Status Word.

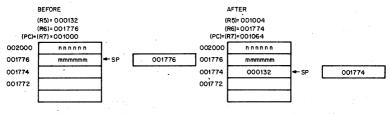

- 3. The processor stores the current Processor Status (PS) and the current Program Counter (PC) into CPU temporary registers.

- 4. The new PC and PS (interrupt vector) are taken from the specified address. The old PS and PC are then pushed onto the current stack. The service routine is then initiated.

- 5. The device service routine can cause the processor to resume the interrupted process by executing the Return from Interrupt instruction, described in Chapter 4, which pops the two top words from the current processor stack and uses them to load the PC and PS registers.

A device routine can be interrupted by a higher priority bus request any time after the new PC and PS have been loaded. If such an interrupt occurs, the PC and PS of the service routine are automatically stored in the temporary registers and then pushed onto the new current stack, and the new device routine is initiated.

#### Interrupt Servicing

Every hardware device capable of interrupting the processor has a unique set of locations (2 words) reserved for its interrupt vector. The first word contains the location of the device's service routine, and the second, the Processor Status Word that is to be used by the service routine. Through proper use of the PS, the programmer can switch the operational mode of the processor, and modify the Processor's Priority level to mask out lower level interrupts.

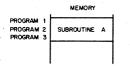

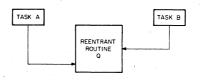

#### Reentrant Code

Both the interrupt handling hardware and the subroutine call hardware facilitate writing reentrant code for the PDP-11. This type of code allows a single copy of a given subroutine or program to be shared by more than one process or task. This reduces the amount of core needed for multi-task applications such as the concurrent servicing of many peripheral devices.

#### Power Fail and Restart

Whenever AC power drops below 95 volts for 110v power (190 volts for 220v) or outside a limit of 47 to 63 Hz, as measured by DC power, the power fail sequence is initiated. The Central Processor automatically traps to location 24 and the power fail program has 2 msec. to save all volatile information (data in registers), and to condition peripherals for power fail.

When power is restored the processor traps to location 24 and executes the power up routine to restore the machine to its state prior to power failure.

2-12

## **CHAPTER 3**

# ADDRESSING MODES

Data stored in memory must be accessed, and manipulated. Data handling is specified by a PDP-11 instruction (MOV, ADD etc.) which usually indicates:

the function (operation code)

a general purpose register to be used when locating the source operand and/or a general purpose register to be used when locating the destination operand.

an addressing mode (to specify how the selected register(s) is/are to be used)

Since a large portion of the data handled by a computer is usually structured (in character strings, in arrays, in lists etc.), the PDP-11 has been designed to handle structured data efficiently and flexibly. The general registers may be used with an instruction in any of the following ways:

as accumulators. The data to be manipulated resides within the register.

as pointers. The contents of the register are the address of the operand, rather than the operand itself.

as pointers which automatically step through core locations. Automatically stepping forward through consecutive core locations is known as autoincrement addressing; automatically stepping backwards is known as autodecrement addressing. These modes are particularly useful for processing tabular data.

as index registers. In this instance the contents of the register, and the word following the instruction are summed to produce the address of the operand. This allows easy access to variable entries in a list.

PDP-11's also have instruction addressing mode combinations which facilitate temporary data storage structures for convenient handling of data which must be frequently accessed. This is known as the "stack."

In the PDP-11 any register can be used as a "stack pointer" under program control, however, certain instructions associated with subroutine linkage and interrupt service automatically use Register 6 as a "hardware stack pointer". For this reason R6 is frequently referred to as the "SP".

R7 is used by the processor as its program counter (PC). It is recommended that R7 not be used as a stack pointer.

An important PDP-11 feature, which must be considered in conjunction with the addressing modes, is the register arrangement;

Six general purpose registers, (R0-R5)

A hardware Stack Pointer (SP), register (R6)

A Program Counter (PC), register (R7).

Instruction mnemonics and address mode symbols are sufficient for writing machine language programs. The programmer need not be concerned about conversion to binary digits; this is accomplished automatically by the PDP-11 MACRO Assembler.

## 3.1 SINGLE OPERAND ADDRESSING

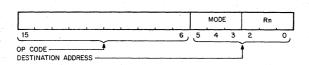

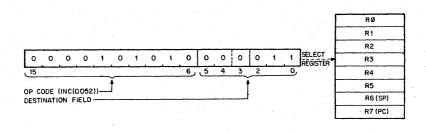

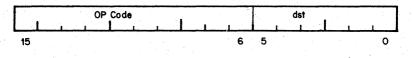

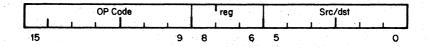

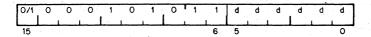

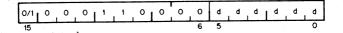

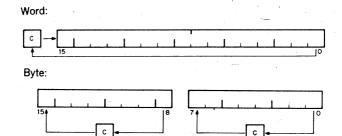

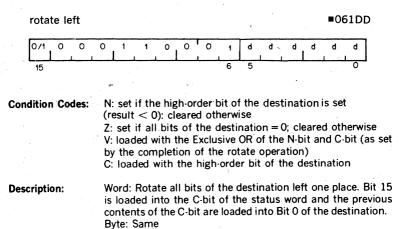

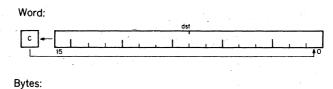

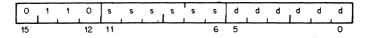

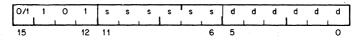

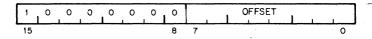

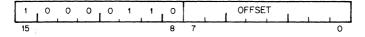

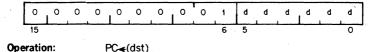

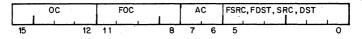

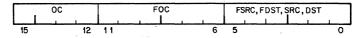

The instruction format for all single operand instructions (such as clear, increment, test) is:

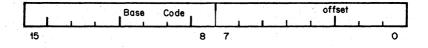

Bits 15 through 6 specify the operation code that defines the type of instruction to be executed.

Bits 5 through 0 form a six-bit field called the destination address field. This consists of two subfields:

- a) Bits 0 through 2 specify which of the eight general purpose registers is to be referenced by this instruction word.

- b) Bits 3 through 5 specify how the selected register will be used (address mode). Bit 3 is set to indicate deferred (indirect) addressing.

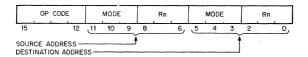

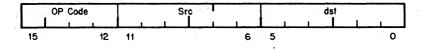

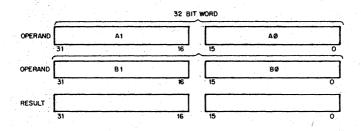

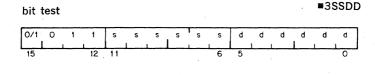

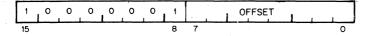

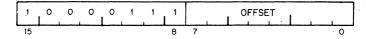

## 3.2 DOUBLE OPERAND ADDRESSING

Operations which imply two operands (such as add, subtract, move and compare) are handled by instructions that specify two addresses. The first operand is called the source operand, the second the destination operand. Bit assignments in the source and destination address fields may specify different modes and different registers. The Instruction format for the double operand instruction is:

The source address field is used to select the source operand, the first operand. The destination is used similarly, and locates the second operand and the result. For example, the instruction ADD A, B adds the contents (source operand) of location A to the contents (destination operand) of location B. After execution B will contain the result of the addition and the contents of A will be unchanged.

Examples in this section and further in this chapter use the following sample PDP-11 instructions:

| Mnemonic                        | Description                                                                                                                              | Octal Code |  |  |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|

| CLR                             | clear (zero the specified destination)                                                                                                   | 0050DD     |  |  |

| CLRB                            | clear byte (zero the byte in the specified destination)                                                                                  | 1050DD     |  |  |

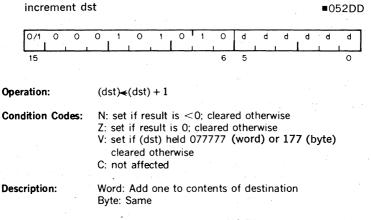

| INC                             | increment (add 1 to contents of destination)                                                                                             | 0052DD     |  |  |

| INCB                            | increment byte (add 1 to the contents of destination byte)                                                                               | 1052DD     |  |  |

| СОМ                             | complement (replace the contents of the destination by their logical complement; each 0 bit is set and each 1 bit is cleared)            | 0051DD     |  |  |

| СОМВ                            | complement byte (replace the contents of the destination byte by their logical complement; each 0 bit is set and each 1 bit is cleared). | 1051DD     |  |  |

| ADD                             | add (add source operand to destination operand and store the result at destination address)                                              | 06SSDD     |  |  |

| DD = destination field (6 bits) |                                                                                                                                          |            |  |  |

| SS = source field (6 bits)      |                                                                                                                                          |            |  |  |

() = contents of

## **3.3 DIRECT ADDRESSING**

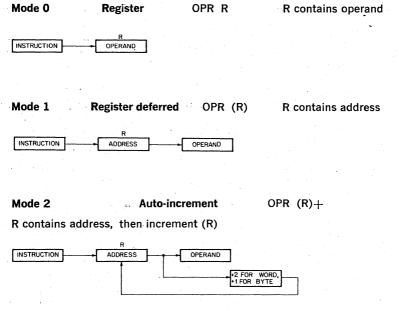

The following table summarizes the four basic modes used with direct addressing. DIRECT MODES

| Mode | Name          | Assembler<br>Syntax | Function                                                                                           |

|------|---------------|---------------------|----------------------------------------------------------------------------------------------------|

| 0    | Register      | Rn                  | Register contains operand                                                                          |

| 2    | Autoincrement | (Rn) +              | Register is used as a pointer to sequential data then incremented                                  |

| 4    | Autodecrement | –(Rn)               | Register is decremented and then used as a pointer.                                                |

| 6    | Index         | X(Rn)               | Value X is added to (Rn) to pro-<br>duce address of operand. Nei-<br>ther X nor (Rn) are modified. |

#### 3.3.1 Register Mode

## OPR Rn

With register mode any of the general registers may be used as simple accumulators and the operand is contained in the selected register. Since they are hardware registers, within the processor, the general registers arate at high speeds and provide speed advantages when used for operating on requently-accessed variables. The PDP-11 assembler interprets and assembles instructions of the form OPR Rn as register mode operations. Rn represents a general register name or number and OPR is used to represent a general instruction mnemonic. Assembler syntax requires that a general register be defined as follows:

R0 = %0 (% sign indicates register definition)

R1 = %1

R2 = %2, etc.

Registers are typically referred to by name as R0, R1, R2, R3, R4, R5, R6 and R7. However R6 and R7 are also referred to as SP and PC, respectively.

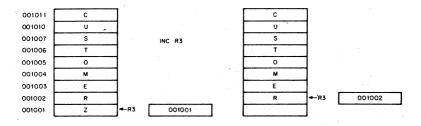

Register Mode Examples (all numbers in octal)

|        | Symbolic | Octal Code | Instruction Name                 |

|--------|----------|------------|----------------------------------|

| 1.     | INC R3   | 005203     | Increment                        |

| Operat | ion:     | Add one to | the contents of general register |

· 3

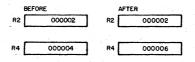

### 2. ADD R2,R4 060204 Add

Operation:

Add the contents of R2 to the contents of R4.

3. COMB R4

105104

Complement Byte

**Operation:**

One's complement bits 0-7 (byte) in R4. (When gener ' registers are used, byte instructions only opera on bits 0-7; i.e. byte 0 of the register)

#### 3.3.2 Autoincrement Mode

OPR (Rn) +

This mode provides for automatic stepping of a pointer through sequential elements of a table of operands. It assumes the contents of the selected general register to be the address of the operand. Contents of registers are stepped (by one for bytes, by two for words, always by two for R6 and R7) to address the next sequential location. The autoincrement mode is especially useful for array processing and stacks. It will access an element of a table and then step the pointer to address the next operand in the table. Although most useful for table handling, this mode is completely general and may be used for a variety of purposes.

#### Autoincrement Mode Examples

Symbolic Octal Code Instruction Name

1. CLR (R5) + 005025 Clear

**Operation:**

Use contents of R5 as the address of the operand. Clear selected operand and then increment the contents of R5 by two.

105025

2. CLRB (R5) +

Clear Byte

Operation:

Use contents of R5 as the address of the operand. Clear selected byte operand and then increment the contents of R5 by one.

3. ADD (R2) + ,R4

062204 Add

Operation:

The contents of R2 are used as the address of the operand which is added to the contents of R4. R2 is then incremented by two.

3-6

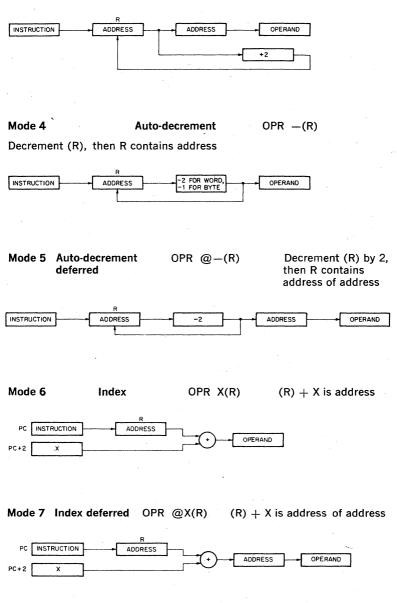

#### 3.3.3 Autodecrement Mode

#### OPR-(Rn)

This mode is useful for processing data in a list in reverse direction. The contents of the selected general register are decremented (by two for word instructions, by one for byte instructions) and then used as the address of the operand. The choice of postincrement, predecrement features for the PDP-11 were not arbitrary decisions, but were intended to facilitate hardware/software stack operations.

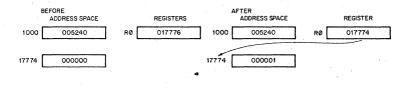

#### Autodecrement Mode Examples Symbolic Octal Code Instruction Name INC-(R0) 1. 005240 Increment Operation: The contents of R0 are decremented by two and used as the address of the operand. The operand is increased by one.

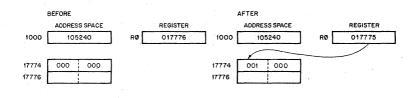

#### 2. INCB-(RO)

#### 105240

#### Increment Byte

Operation:

The contents of R0 are decremented by one then used as the address of the operand. The operand byte is increased by one.

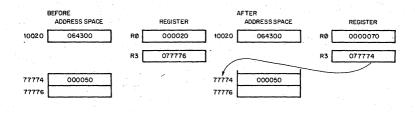

### 3.

# ADD-(R3),R0

064300 Add

Operation:

The contents of R3 are decremented by 2 then used as a pointer to an operand (source) which is added to the contents of RO (destination operand).

### 3.3.4 Index Mode

# OPR X(Rn)

The contents of the selected general register, and an index word following the instruction word, are summed to form the address of the operand. The contents of the selected register may be used as a base for calculating a series of addresses, thus allowing random access to elements of data structures. The selected register can then be modified by program to access data in the table. Index addressing instructions are of the form OPR X(Rn) where X is the indexed word and is located in the memory location following the instruction word and Rn is the selected general register.

# **Index Mode Examples**

Symbolic

CLR 200(R4)

1.

Octal Code Instruction Name 005064 Clear 000200

Operation:

The address of the operand is determined by adding 200 to the contents of R4. The location is then cleared.

#### 2.

COMB 200(R1)

105161

#### Complement Byte

**Operation:**

The contents of a location which is determined by adding 200 to the contents of R1 are one's complemented. (i.e. logically complemented)

З.

# ADD 30(R2),20(R5) 066265 000030 000020

Add

Operation:

The contents of a location which is determined by adding 30 to the contents of R2 are added to the contents of a location which is determined by adding 20 to the contents of R5. The result is stored at the destination address, i.e. 20(R5)

### 3.4 DEFERRED (INDIRECT) ADDRESSING

The four basic modes may also be used with deferred addressing. Whereas in the register mode the operand is the contents of the selected register, in the register deferred mode the contents of the selected register is the address of the operand.

In the three other deferred modes, the contents of the register selects the address of the operand rather than the operand itself. These modes are therefore used when a table consists of addresses rather than operands. Assembler syntax for indicating deferred addressing is "@"(or "()" when this is not ambiguous). The following table summarizes the deferred versions of the basic modes:

| Mode | Name                   | Assembler<br>Syntax | Function                                                                                                                                                                                                    |

|------|------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Register Deferred      | @Rn or (R           | n)<br>Register contains the address of<br>the operand                                                                                                                                                       |

| 3    | Autoincrement Deferred | @(Rn) +             | Register is first used as a pointer to a word containing the address of the operand, then incremented (always by 2; even for byte instructions).                                                            |

| 5    | Autodecrement Deferred | @-(Rn)              | Register is decremented (always<br>by two; even for byte instruc-<br>tions) and then used as a<br>pointer to a word containing the<br>address of the operand                                                |

| 7    | Index Deferred         | @X(Rn)              | Value X (stored in a word follow-<br>ing the instruction) and (Rn) are<br>added and the sum is used as a<br>pointer to a word containing the<br>address of the operand. Neither<br>X nor (Rn) are modified. |

Since each deferred mode is similar to its basic mode counterpart, separate descriptions of each deferred mode are not necessary. However, the following examples illustrate the deferred modes.

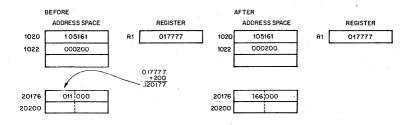

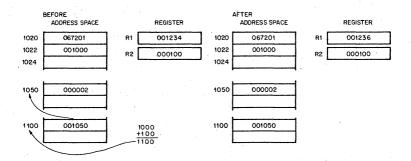

# Register Deferred Mode Example Symbolic Symbolic Octal Code Instruction Name CLR @R5 005015 Clear Operation: The contents of location specified in R5 are cleared. BEFORE AFTER

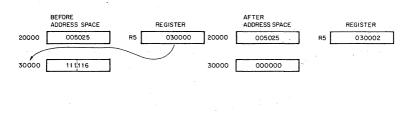

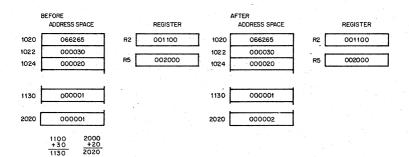

# **Autoincrement Deferred Mode Example**

| Symbolic   | Octal Code | Instruction Name |

|------------|------------|------------------|

| INC@(R2) + | 005232     | Increment        |

Operation:

The contents of R2 are used as the address of the address of the operand.

Operand is increased by one. Contents of R2 is incremented by 2.

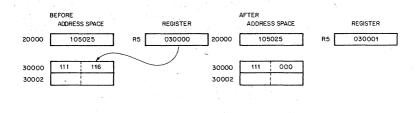

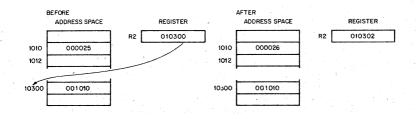

### Autodecrement Deferred Mode Example

| Symbolic   | Octal Code | Complement |  |

|------------|------------|------------|--|

| COM @-(R0) | 005150     |            |  |

Operation:

The contents of RO are decremented by two and then used as the address of the address of the operand. Operand is one's complemented. (i.e. logically complemented)

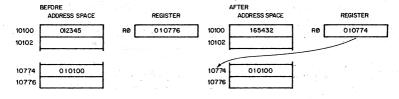

### **Index Deferred Mode Example**

Symbolic and

Octal Code Instruction Name

Add

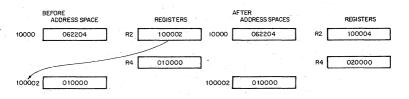

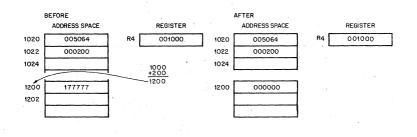

ADD @ 1000(R2),R1

067201 001000

**Operation:**

1000 and contents of R2 are summed to produce the address of the address of the source operand the contents of which are added to contents of R1; the result is stored in R1.

### 3.5 USE OF THE PC AS A GENERAL REGISTER

Although Register 7 is a general purpose register, it doubles in function as the Program Counter for the PDP-11. Whenever the processor uses the program counter to acquire a word from memory, the program counter is automatically incremented by two to contain the address of the next word of the instruction being executed or the address of the next instruction to be executed. (When the program uses the PC to locate byte data, the PC is still incremented by two.)

The PC responds to all the standard PDP-11 addressing modes. However, there are four of these modes with which the PC can provide advantages for handling position independent code (PIC - seeChapter 5) and unstructured data. When regarding the PC these modes are termed immediate, absolute (or immediate deferred), relative and relative deferred, and are summarized below:

| Mode | Name              | Assemble<br>Syntax | r Function                                                                                                                  |

|------|-------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------|

| 2    | Immediate         | # n                | Operand follows instruction                                                                                                 |

| 3    | Absolute          | @#A                | Absolute Address follows in-<br>struction                                                                                   |

| 6    | Relative          | Α                  | Relative Address (index value)<br>follows the instruction.                                                                  |

| 7    | Relative Deferred | @A                 | Index value (stored in the<br>word following the instruction)<br>is the relative address for the<br>address of the operand. |

The reader should remember that the special effect modes are the same as modes described in 3.3 and 3.4, but the general register selected is R7, the program counter.

When a standard program is available for different users, it often is helpful to be able to load it into different areas of core and run it there. PDP-11's can accomplish the relocation of a program very efficiently through the use of position independent code (PIC) which is written by using the PC addressing modes. If an instruction and its objects are moved in such a way that the relative distance between them is not altered, the same offset relative to the PC can be used in all positions in memory. Thus, PIC usually references locations relative to the current location. PIC is discussed in more detail in Chapter 5.

The PC also greatly facilitates the handling of unstructured data. This is particularly true of the immediate and relative modes.

#### 3.5.1 Immediate Mode

OPR #n,DD

Immediate mode is equivalent to using the autoincrement mode with the PC. It provides time improvements for accessing constant operands by including the constant in the memory location immediately following the instruction word.

| Immediate Mode Example<br>Symbolic | Octal Code       | Instruction Name |   |

|------------------------------------|------------------|------------------|---|

| ADD #10,R0                         | 062700<br>000010 | Add              | • |

Operation:

The value 10 is located in the second word of the instruction and is added to the contents of R0. Just before this instruction is fetched and executed, the PC points to the first word of the instruction. The processor fetches the first word and increments the PC by two. The source operand mode is 27 (autoincrement the PC). Thus, the PC is used as a pointer to fetch the operand (the second word of the instruction) before being incremented by two to point to the next instruction.

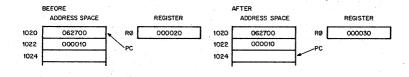

# 3.5.2 Absolute Addressing

OPR @#A

This mode is the equivalent of immediate deferred or autoincrement deferred using the PC. The contents of the location following the instruction are taken as the address of the operand. Immediate data is interpreted as an absolute address (i.e., an address that remains constant no matter where in memory the assembled instruction is executed).

| Absolute | Mode Examples<br>Symbolic | Octal Code       | Instruction Name |

|----------|---------------------------|------------------|------------------|

| 1.       | CLR @ #1100               | 005037<br>001100 | Clear            |

Operation:

Clear the contents of location 1100.

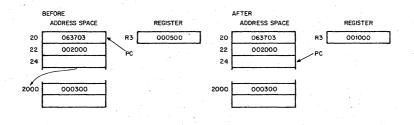

ADD @ # 2000,R3 063703 002000

Operation:

2.

Add contents of location 2000 to R3.

# 3.5.3 Relative Addressing

OPR A or OPR X(PC) where X is the location of A relative to the instruction.

This mode is assembled as index mode using R7. The base of the address calculation, which is stored in the second or third word of the instruction, is not the address of the operand, but the number which, when added to the (PC), becomes the address of the operand. This mode is useful for writing position independent code (see Chapter 5) since the location referenced is always fixed relative to the PC. When instructions are to be relocated, the operand is moved by the same amount.

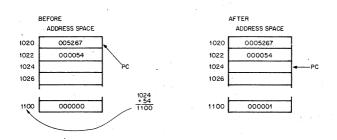

#### **Relative Addressing Example**

Symbolic

Octal Code Instruction Name

INC A

Increment

#### Operation:

To increment location A, contents of memory location immediately following instruction word are added to (PC) to produce address A. Contents of A are increased by one.

005267

000054

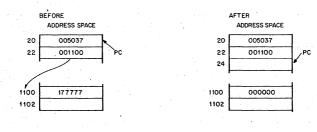

#### 3.5.4 Relative Deferred Addressing

OPR@A or

OPR@X(PC), where x is location containing address of A, relative to the instruction.

This mode is similar to the relative mode, except that the second word of the instruction, when added to the PC, contains the address of the address of the operand, rather than the address of the operand.

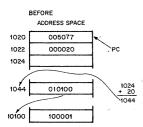

#### Relative Deferred Mode Example Symbolic Oc

Octal Code Instruction Name

Clear

CLR @A

005077

Operation:

Add second word of instruction to PC to produce address of address of operand. Clear operand.

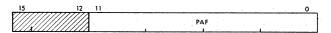

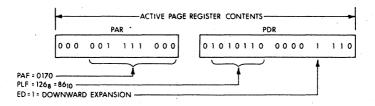

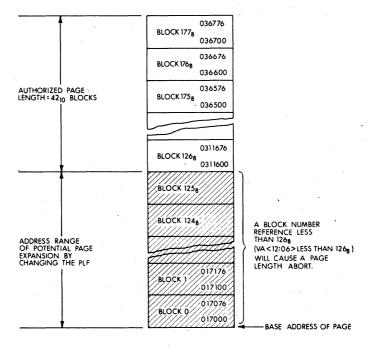

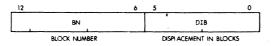

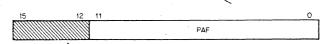

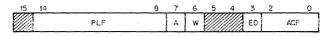

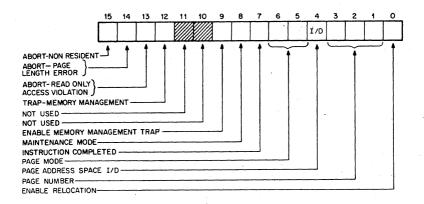

# 3.6 USE OF STACK POINTER AS GENERAL REGISTER