# VT11 graphic display processor

## VT11 graphic display processor

## Copyright © 1973, 1974 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC

PDP

**FLIP CHIP**

**FOCAL**

**DIGITAL**

**COMPUTER LAB**

**UNIBUS**

## **CONTENTS**

|           | Page                                          |

|-----------|-----------------------------------------------|

| CHAPTER 1 | INTRODUCTION                                  |

| 1.1       | PURPOSE AND SCOPE                             |

| 1.2       | GENERAL DESCRIPTION                           |

| 1.3       | PHYSICAL DESCRIPTION                          |

| 1.4       | VT11 SPECIFICATIONS                           |

| CHAPTER 2 | THEORY OF OPERATION                           |

| 2.1       | INTRODUCTION                                  |

| 2.2       | VT11 DISPLAY PROCESSOR                        |

| 2.2.1     | Introduction                                  |

| 2.2.2     | Initialization                                |

| 2.2.3     | Starting the Display Processor                |

| 2.2.4     | Address Selection                             |

| 2.2.4.1   | Reading Status                                |

| 2.2.5     | NPR Data Requests                             |

| 2.2.6     | Timing                                        |

| 2.2.7     | Display Processor Mode Control                |

| 2.2.8     | Control Instructions                          |

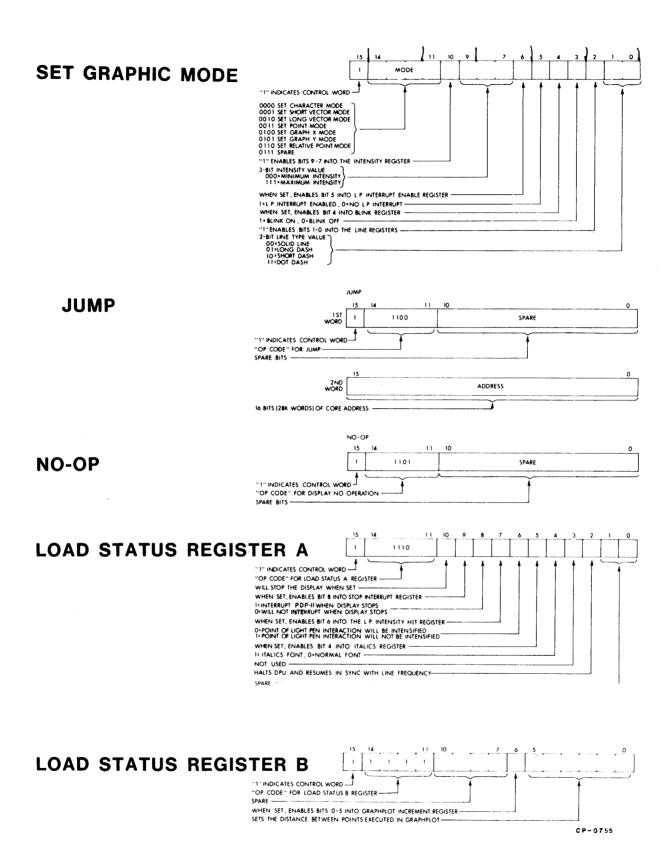

| 2.2.8.1   | Load Status Register A                        |

| 2.2.8.2   | Load Status Register B                        |

| 2.2.8.3   | Jump Instruction                              |

| 2.2.8.4   | No-Op Instruction                             |

| 2.2.8.5   | Set Graphic Mode Instruction                  |

| 2.2.9     | Data Words                                    |

| 2.2.9.1   | Data Word Functions                           |

| 2.2.10    | Vector Generation                             |

| 2.2.10.1  | General Description                           |

| 2.2.10.2  | Normalization                                 |

| 2.2.10.3  | Binary Rate Multipliers                       |

| 2.2.10.4  | Vector Generator Synchronization              |

| 2.2.11    | Point Intensification                         |

| 2.2.12    | Character Generation                          |

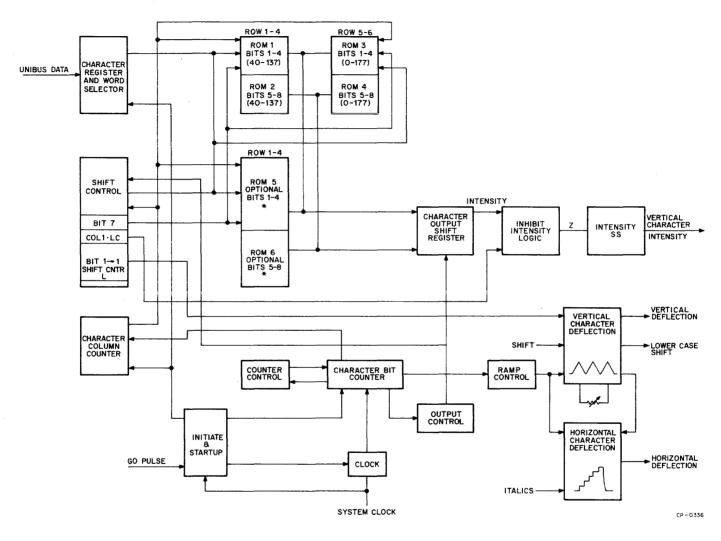

| 2.2.12.1  | General Description                           |

| 2.2.12.2  | Character Bit Counter and Decoder             |

| 2.2.12.3  | Character Column Counter and Decoder          |

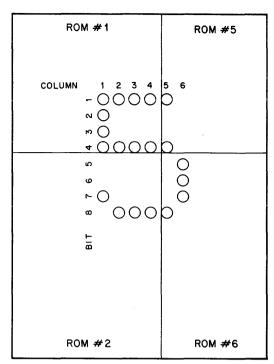

| 2.2.12.4  | ROM Organization                              |

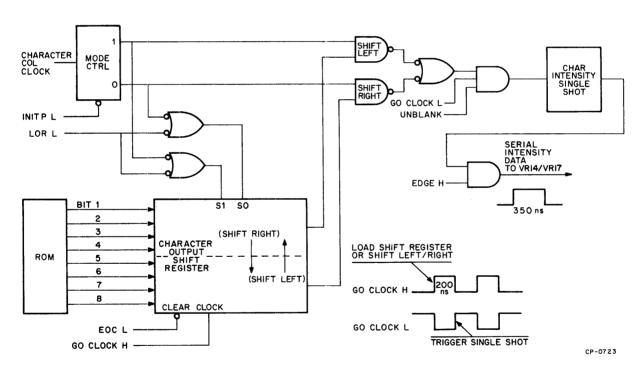

| 2.2.12.5  | Intensity Output and Control                  |

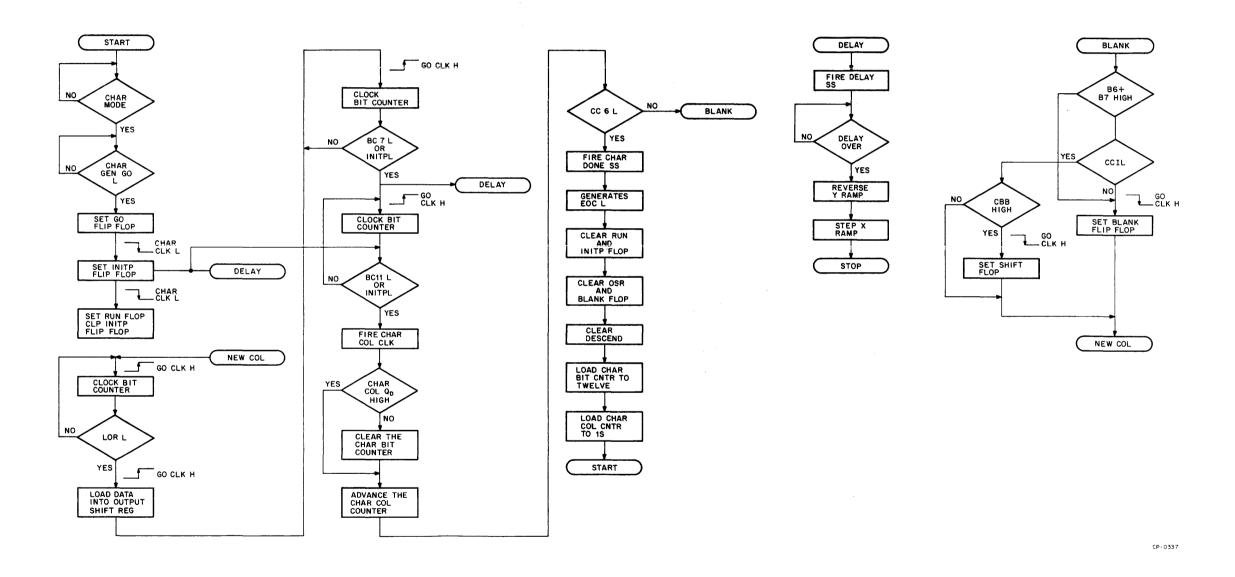

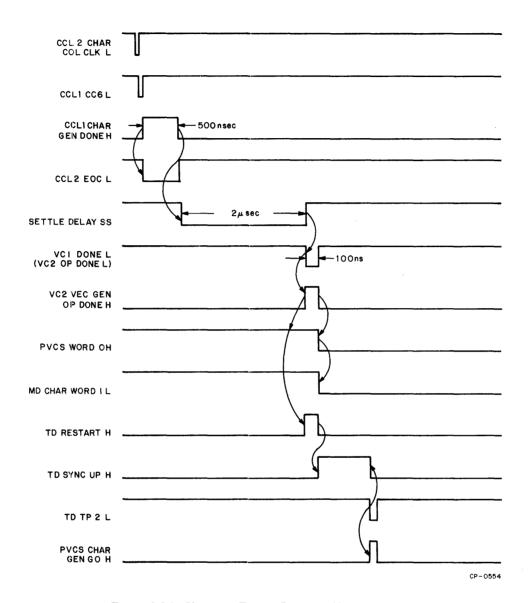

| 2.2.12.6  | Operational Sequence                          |

| 2.2.12.7  | Character Spacing                             |

| 2.2.12.8  | Descending Characters                         |

| 2.2.12.9  | Y Axis Ramp Generator                         |

| 2.2.12.10 | X Axis Ramp Generator                         |

| 2.2.12.11 | Italics Switch                                |

| 2.2.13    | Analog Circuits                               |

| 2.2.13.1  | General Description                           |

| 2.2.13.2  | Voltage Regulators                            |

| 2.2.13.3  | Digital-to-Analog Converters (DAC)            |

| 2.2.13.4  | X and Y Vector Deflection Generators          |

| 2.2.13.5  | X and Y Summing Amplifiers and Output Drivers |

## CONTENTS (Cont)

|              | Pa                                                               | ge  |

|--------------|------------------------------------------------------------------|-----|

| CHAPTER 3    | MAINTENANCE                                                      |     |

| 3.1          | VT11 DISPLAY PROCESSOR ADJUSTMENTS                               | 3-1 |

| 3.1.1        | Character Display Adjustments                                    | 3-1 |

| 3.1.2        | - · · ·                                                          | 3-4 |

| 3.2          | • • •                                                            | 3-4 |

| 3.2.1        |                                                                  | 3-5 |

| 3.2.2        | · · · · · · · · · · · · · · · · · · ·                            | 3-6 |

| 3.2.3        |                                                                  | 3-7 |

| 3.2.4        | Operational Programming                                          |     |

| 3.2.4.1      | Display Large Rectangle                                          |     |

| 3.2.4.2      | Display Large Rectangle with Vector                              |     |

| 3.2.4.3      | Display Large Rectangle with Vector and Graphic Data             |     |

| 3.2.4.3      | Display Large Rectangle with Vector, Graphic, and Graphplot Data |     |

| 3.3          | VT11 TROUBLESHOOTING PROCEDURES                                  |     |

| 3.3.1        |                                                                  |     |

|              | No CRT Picture                                                   |     |

| 3.3.2        | Faulty Pictures                                                  |     |

| 3.3.3        | Light Pen Malfunction                                            | 17  |

| CHAPTER 4    | VT11 ENGINEERING DRAWINGS AND RELATED DOCUMENTS                  |     |

| 4.1          | APPLICABLE ENGINEERING DRAWINGS                                  | 1-1 |

| 4.2          | DRAWING CODE                                                     | 1-1 |

| 4.3          | VT11 ENGINEERING DRAWINGS                                        | 1-1 |

| 4.4          | RELATED DOCUMENTATION                                            | 1-2 |

| APPENDIX A   | CHARACTER CODES                                                  |     |

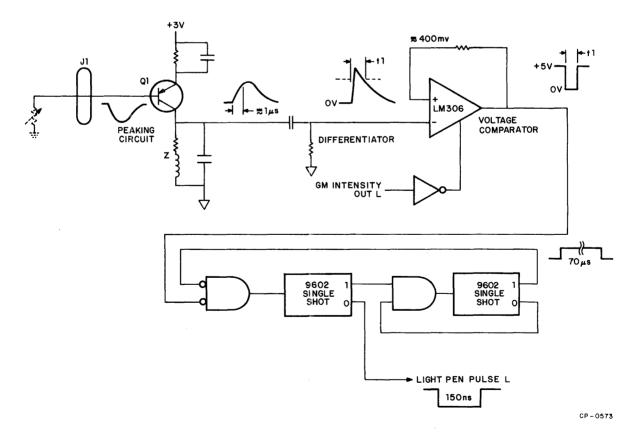

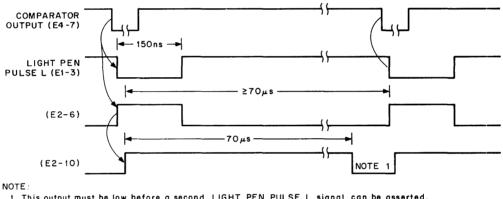

| APPENDIX B   | LIGHT PEN AMPLIFICATION                                          |     |

|              | ILLUSTRATIONS                                                    |     |

| Figure No.   | Title Pa                                                         | ıge |

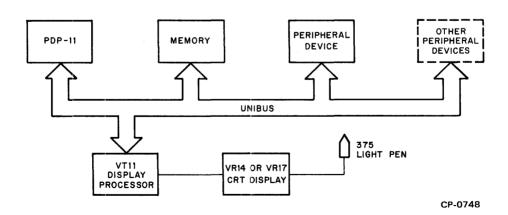

| 1-1          | VT11 Graphic Display Processor in System Configuration           | -1  |

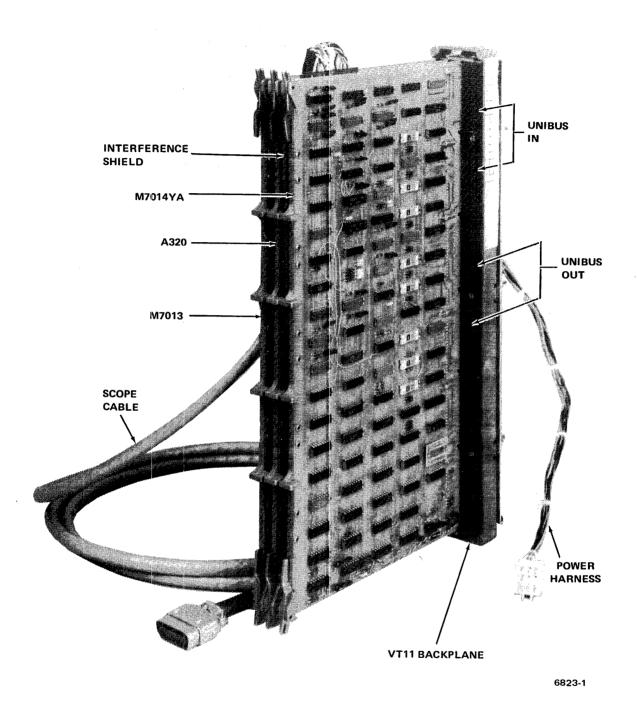

| 1-2          | VT11 Graphic Display Processor                                   | 3   |

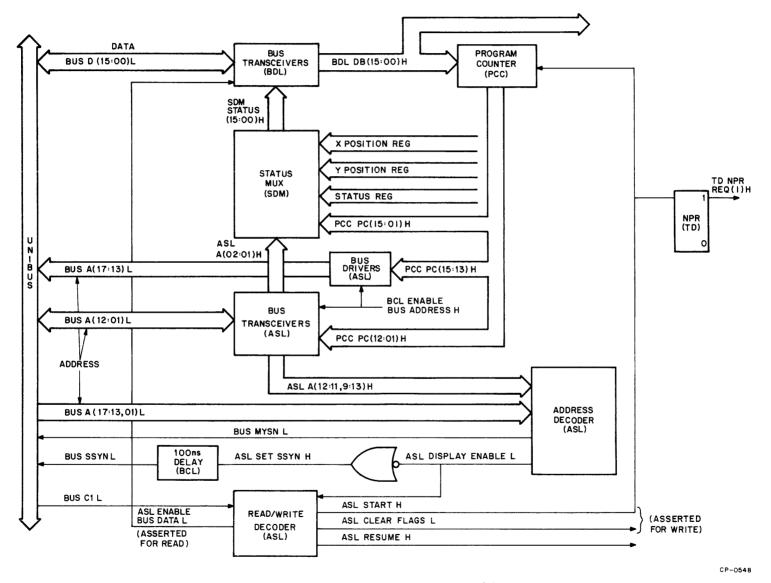

| 2-1          | Unibus Address and Data, Block Diagram                           | 2-4 |

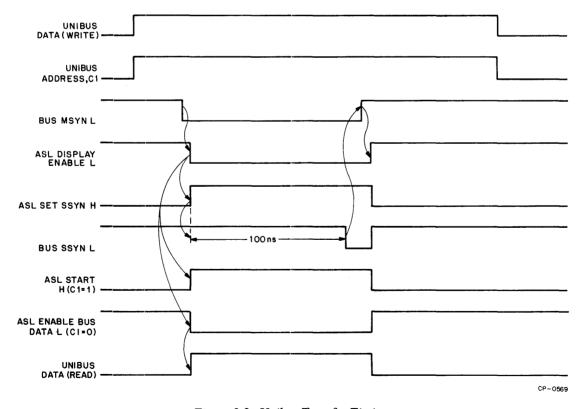

| 2-2          | Unibus Transfer Timing                                           | 2-5 |

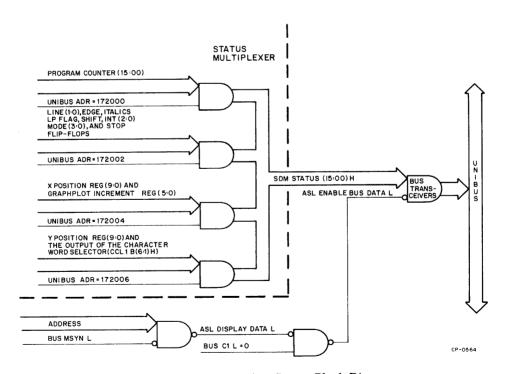

| 2-3          |                                                                  | 2-6 |

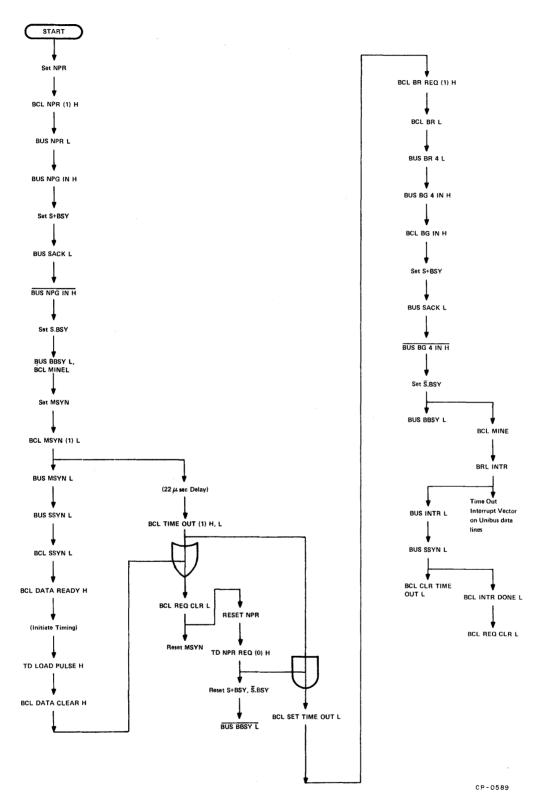

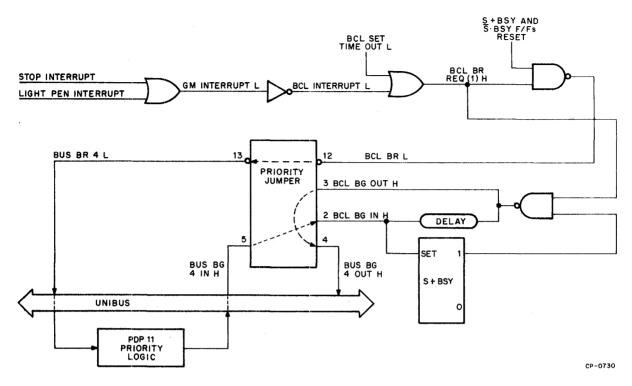

| 2-4          | NPR/Time Out Interrupt, Flow Diagram                             | 2-7 |

| 2-5          |                                                                  | 2-9 |

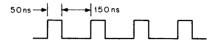

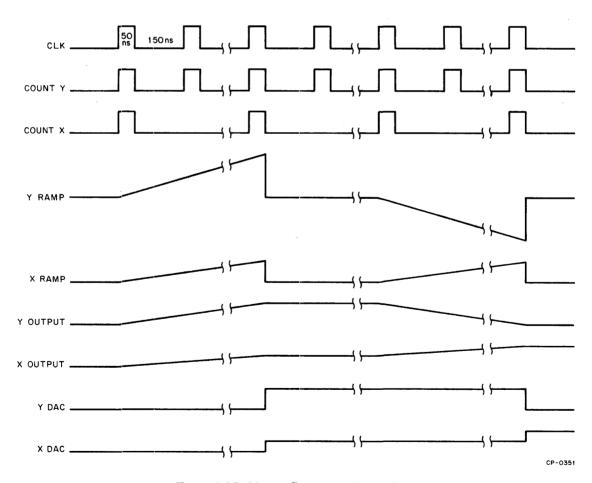

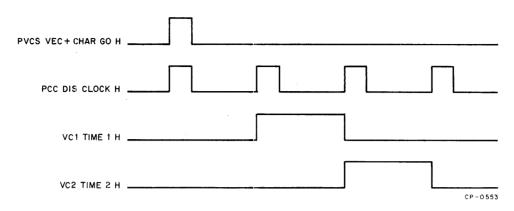

| 2-6          | Display Processor Timing Diagram – M7013 Module                  | 11  |

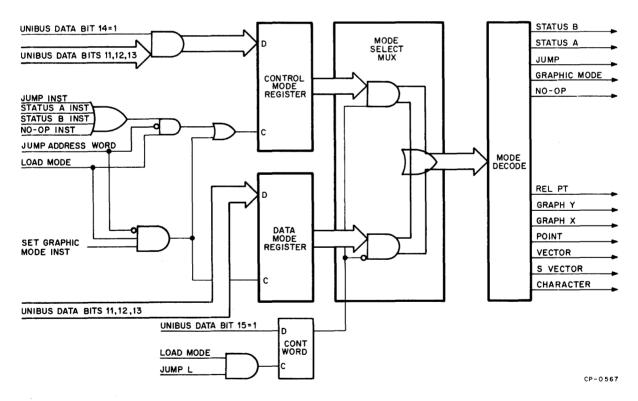

| 2-7          | Mode Control                                                     |     |

| 2-8          | Instruction Word Functions                                       |     |

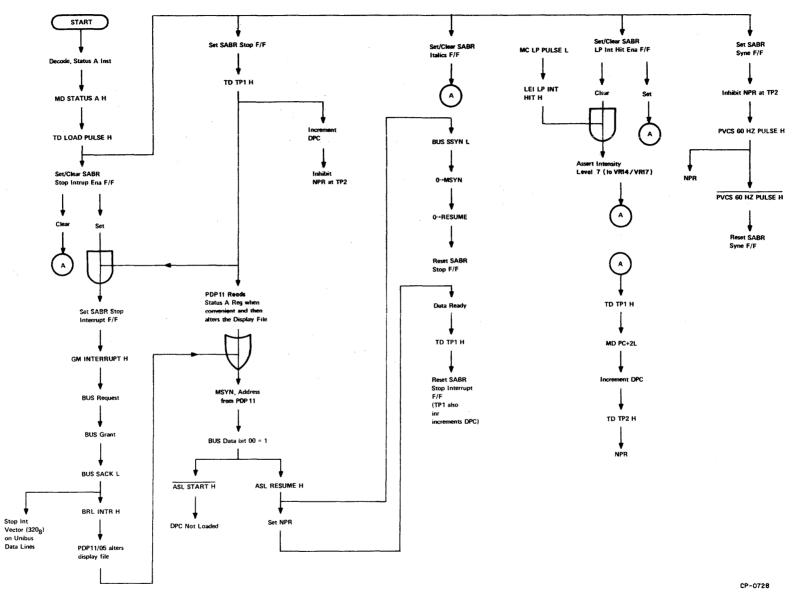

| 2-9          | Status A Instruction Flow Diagram                                |     |

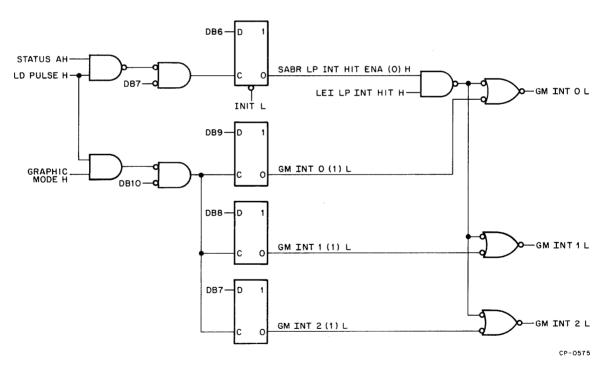

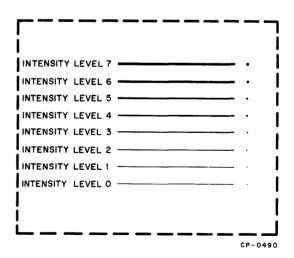

| 2-10         | M7013 Intensity Level Control                                    |     |

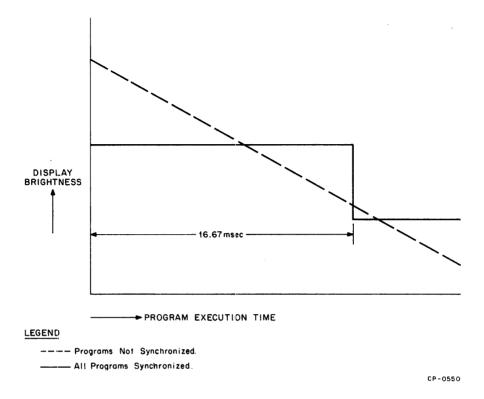

| 2-10         | Relationship of CRT Brightness to Program Length                 |     |

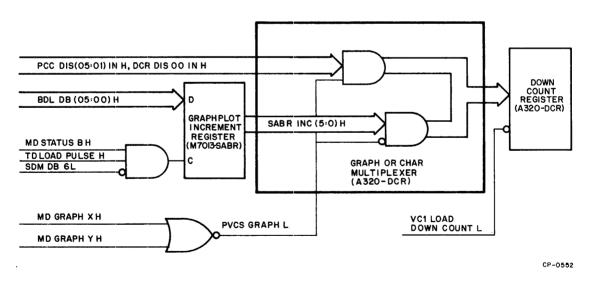

| 2-11         | Graphplot Logic                                                  |     |

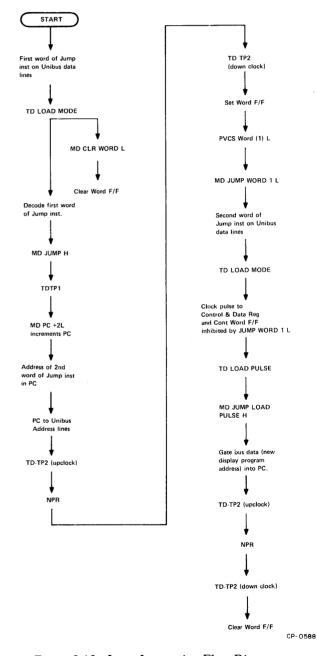

| 2-12<br>2-13 | Jump Instruction Flow Diagram                                    |     |

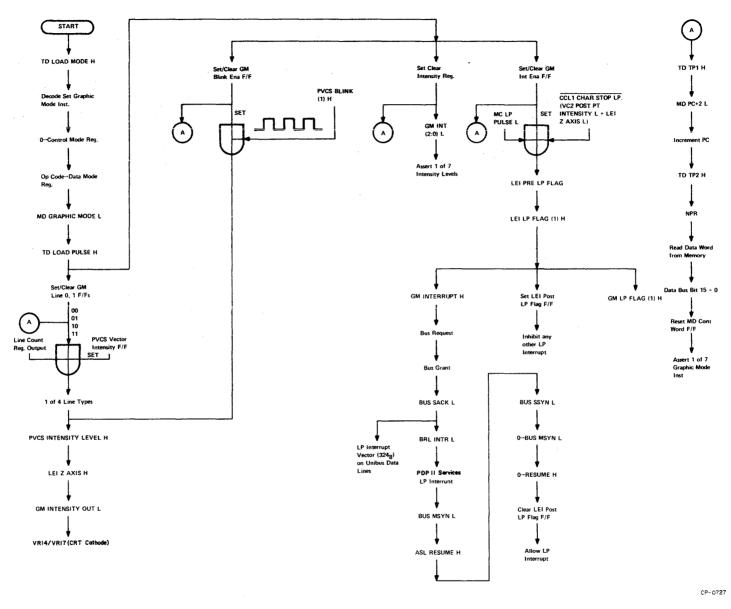

| 2-13<br>2-14 | Set Graphic Mode Instruction Flow Diagram                        |     |

| Z-14         | Set Graphic mode instruction flow Diagram                        | 41  |

## ILLUSTRATIONS (Cont)

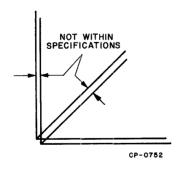

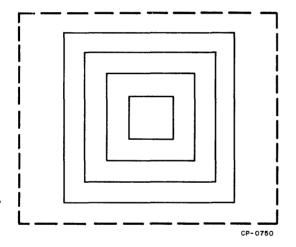

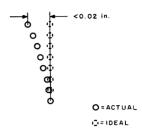

| 3-5       Maintenance Switches, M7013 Module       3-5         3-6       Display Pattern 0       3-7         3-7       Display Pattern 7       3-7         3-8       Repeatability Display Pattern       3-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Figure No. | Title                                                    | Page |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------------------------------------------------|------|

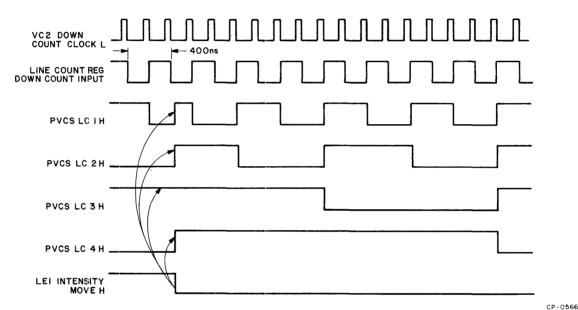

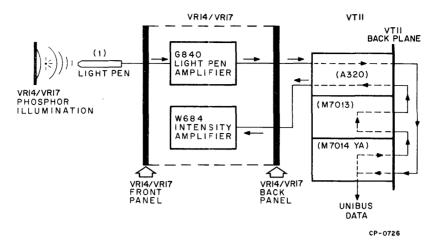

| 2-17         Light Pen Signal Path         2-2:           2-18         Data Word Formats         -2-2:           2-19         Data Word Storage         2-2:           2-20         Display Examples         2-3:           2-21         Vector Instructions and Examples         2-3:           2-21         Vector Generator, Block Diagram         2-3:           2-23         Vector Generator, Block Diagram         2-3:           2-24         Relationship of Clock Frequency to Ramp Generator Output         2-3:           2-25         Vector Generator, Timing Diagram         2-3:           2-26         Absolute and Normalized Magnitude         2-3:           2-27         Point Instruction (Termination), Timing Diagram         2-3:           2-28         Path of Electron Beam as Influenced by X and Y Deflection Signals         2-3:           2-29         Character Generator, Flow Diagram         2-3:           2-30         Character Generator, Flow Diagram         2-4:           2-31         ROM/Character Relationship         2-4:           2-32         ROM/Character Relationship         2-4:           2-33         Generation of Intensity Data to the VR14/VR17         2-4:           2-34         Word Selection and ROM Addressing, Timing Diagram                                                                                                                   | 2-15       | Line Count Register, Timing Diagram                      | 2-23 |

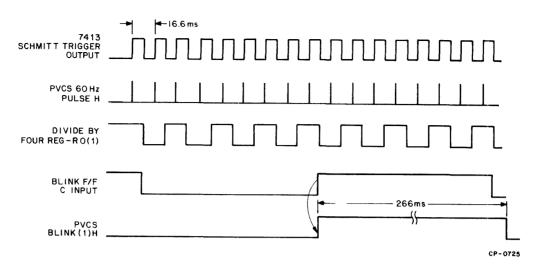

| 2-18         Data Word Formats         2-24           2-19         Data Word Storage         2-22           2-20         Display Examples         2-3           2-21         Vector Instructions and Examples         2-3           2-22         Cut-Off Vector Displays         2-3           2-23         Vector Generator, Block Diagram         2-3           2-24         Relationship of Clock Frequency to Ramp Generator Output         2-3           2-25         Vector Generator, Timing Diagram         2-3           2-26         Absolute and Normalized Magnitude         2-3           2-27         Point Instruction (Termination), Timing Diagram         2-3           2-28         Path of Electron Beam as Influenced by X and Y Deflection Signals         2-3           2-29         Character Generator, Block Diagram         2-3           2-30         Character Generator, Block Diagram         2-4           2-31         ROM/Character Relationship         2-4           2-32         ROM/Character Relationship         2-4           2-33         Generation of Intensity Data to the VR14/VR17         2-4           2-34         Word Selection and ROM Addressing, Timing Diagram         2-4           2-35         Character Bit Timing         2-4                                                                                                                              | 2-16       | Blink Timing Diagram                                     | 2-24 |

| 2.19       Data Word Storage       2.26         2.20       Display Examples       2.33         2.21       Vector Instructions and Examples       2.33         2.22       Cut-Off Vector Displays       2.33         2.23       Vector Generator, Block Diagram       2.33         2.24       Relationship of Clock Frequency to Ramp Generator Output       2.34         2.25       Vector Generator, Timing Diagram       2.33         2.26       Absolute and Normalized Magnitude       2.32         2.27       Point Instruction (Termination), Timing Diagram       2.32         2.28       Path of Electron Beam as Influenced by X and Y Deflection Signals       2.33         2.29       Character Generator, Block Diagram       2.34         2.30       Character Generator, Block Diagram       2.42         2.31       ROM/Character Relationship       2.44         2.32       ROM/Character Relationship       2.44         2.33       Generation of Intensity Data to the VR14/VR17       2.45         2.34       Word Selection and ROM Addressing, Timing Diagram       2.44         2.35       Character Bit Timing       2.44         2.36       Character Timing Between Characters in a Single Data Word       2.47         2.37       In                                                                                                                                                          | 2-17       |                                                          |      |

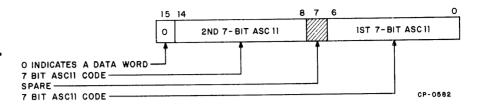

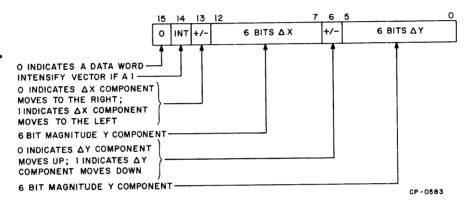

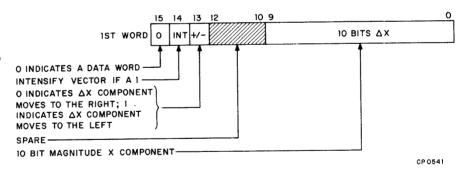

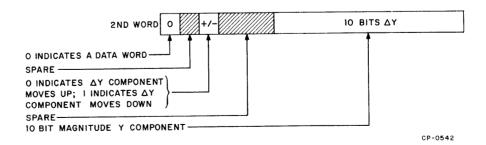

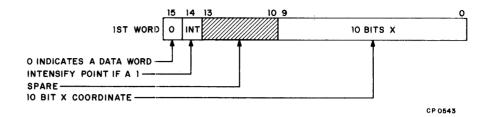

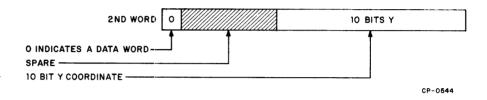

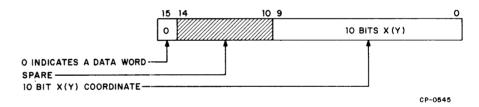

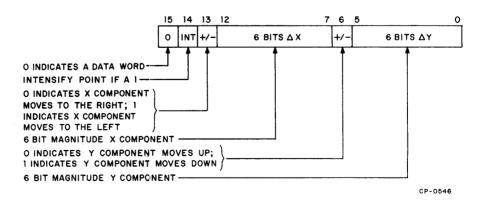

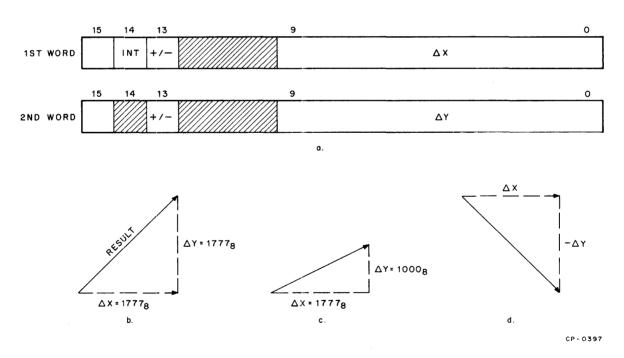

| 2-20         Display Examples         2-30           2-21         Vector Instructions and Examples         2-3           2-22         Cut-Off Vector Displays         2-3           2-23         Vector Generator, Block Diagram         2-3           2-24         Relationship of Clock Frequency to Ramp Generator Output         2-3           2-25         Vector Generator, Timing Diagram         2-3           2-26         Absolute and Normalized Magnitude         2-3           2-27         Point Instruction (Termination), Timing Diagram         2-3           2-28         Path of Electron Beam as Influenced by X and Y Deflection Signals         2-3           2-29         Character Generator, Block Diagram         2-3           2-30         Character Generator, Flow Diagram         2-4           2-31         ROM/Character Relationship         2-4           2-32         ROM/Character Relationship         2-4           2-33         Generation of Intensity Data to the VR14/VR17         2-4           2-34         Word Selection and ROM Addressing, Timing Diagram         2-4           2-35         Character Bit Timing         2-4           2-36         Character Bit Timing         2-4           2-37         Intercharacter Timing Between Characters in a Single                                                                                                      | 2-18       | Data Word Formats                                        | 2-26 |

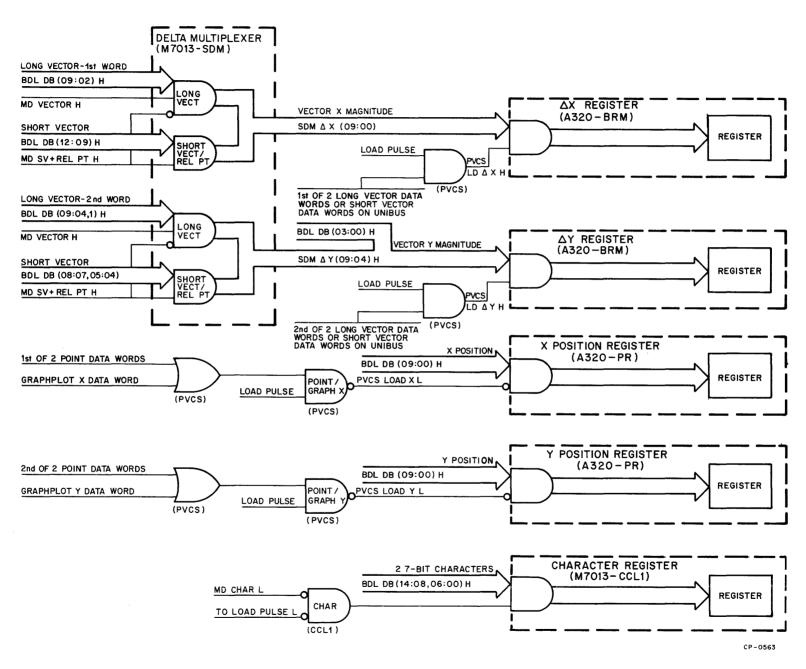

| 2-21       Vector Instructions and Examples       2-3         2-22       Cut-Off Vector Displays       2-3         2-23       Vector Generator, Block Diagram       2-3         2-24       Relationship of Clock Frequency to Ramp Generator Output       2-3         2-25       Vector Generator, Timing Diagram       2-3         2-26       Absolute and Normalized Magnitude       2-3         2-27       Point Instruction (Termination), Timing Diagram       2-3         2-28       Path of Electron Beam as Influenced by X and Y Deflection Signals       2-3         2-29       Character Generator, Flook Diagram       2-3         3-30       Character Generator, Flook Diagram       2-4         2-31       ROM/Character Relationship       2-4         2-32       ROM/Character Relationship       2-4         2-33       Generation of Intensity Data to the VR14/VR17       2-4         2-34       Word Selection and ROM Addressing, Timing Diagram       2-4         2-35       Character Bit Timing       2-4         2-36       Character Bit Timing between Characters in a Single Data Word       2-4         2-37       Intercharacter X Position Update, Flow Diagram       2-4         2-38       Time Shift Register, Timing Diagram (M7014YA-VC1)       2-4                                                                                                                                | 2-19       | Data Word Storage                                        | 2-28 |

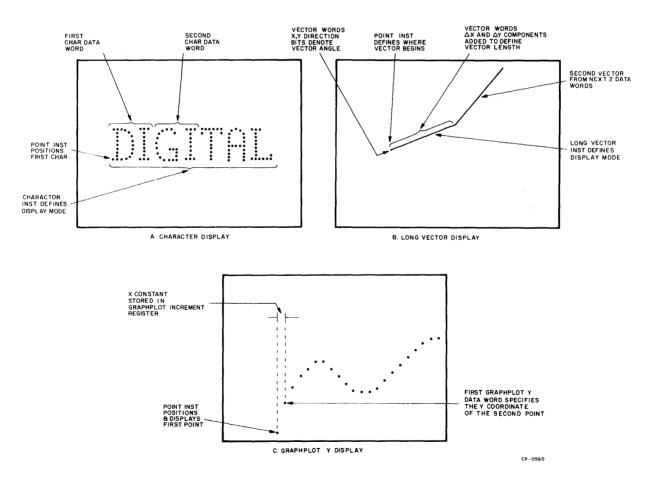

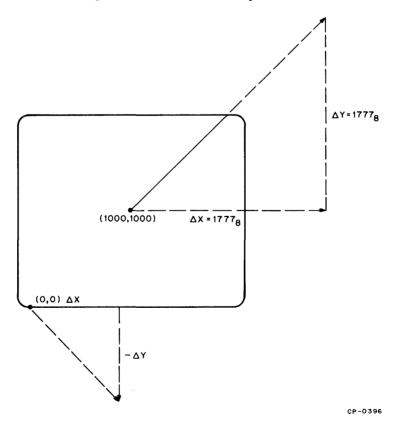

| 2-22         Cut-Off Vector Displays         2-3           2-23         Vector Generator, Block Diagram         2-3           2-24         Relationship of Clock Frequency to Ramp Generator Output         2-3           2-25         Vector Generator, Timing Diagram         2-3           2-26         Absolute and Normalized Magnitude         2-3           2-27         Point Instruction (Termination), Timing Diagram         2-3           2-28         Path of Electron Beam as Influenced by X and Y Deflection Signals         2-3           2-29         Character Generator, Block Diagram         2-3           2-30         Character Generator, Flow Diagram         2-4           2-31         ROM/Character Relationship         2-4           2-32         ROM/Character Relationship         2-4           2-33         Generation of Intensity Data to the VR14/VR17         2-4           2-34         Word Selection and ROM Addressing, Timing Diagram         2-4           2-35         Character Bit Timing         2-4           2-36         Character Bit Timing         2-4           2-37         Intercharacter X Position Update, Flow Diagram         2-4           2-38         Time Shift Register, Timing Diagram (M7014YA-VC1)         2-4           2-39         Descen                                                                                                      | 2-20       | Display Examples                                         | 2-30 |

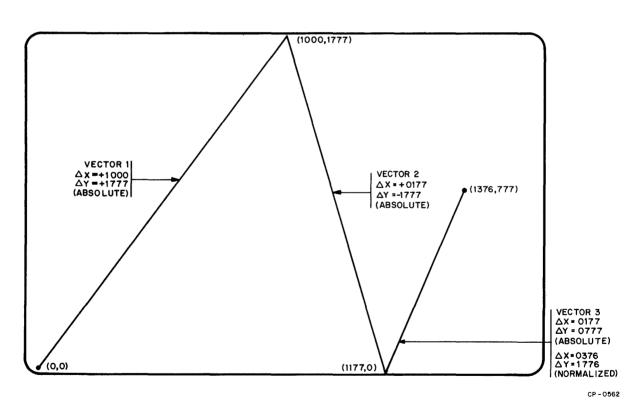

| 2-23         Vector Generator, Block Diagram         2-32           2-24         Relationship of Clock Frequency to Ramp Generator Output         2-3           2-25         Vector Generator, Timing Diagram         2-3           2-26         Absolute and Normalized Magnitude         2-3           2-27         Point Instruction (Termination), Timing Diagram         2-3           2-28         Path of Electron Beam as Influenced by X and Y Deflection Signals         2-3           2-29         Character Generator, Block Diagram         2-3           2-30         Character Generator, Flow Diagram         2-4           2-31         ROM/Character Relationship         2-4           2-32         ROM/Character Relationship         2-4           2-33         Generation of Intensity Data to the VR14/VR17         2-4           2-34         Word Selection and ROM Addressing, Timing Diagram         2-4           2-35         Character Timing Between Characters in a Single Data Word         2-4           2-36         Character Timing Between Characters in a Single Data Word         2-4           2-37         Intercharacter X Position Update, Flow Diagram         2-4           2-38         Time Shift Register, Timing Diagram (M7014YA-VC1)         2-4           2-39         Descending Character (Ex: Lower Ca                                                          | 2-21       | Vector Instructions and Examples                         | 2-31 |

| 2-24         Relationship of Clock Frequency to Ramp Generator Output         2-3           2-25         Vector Generator, Timing Diagram         2-3           2-26         Absolute and Normalized Magnitude         2-3           2-27         Point Instruction (Termination), Timing Diagram         2-3           2-28         Path of Electron Beam as Influenced by X and Y Deflection Signals         2-3           2-29         Character Generator, Block Diagram         2-3           2-30         Character Generator, Flow Diagram         2-4           2-31         ROM/Character Relationship         2-4           2-32         ROM/Character Relationship         2-4           2-33         Generation of Intensity Data to the VR14/VR17         2-4           2-34         Word Selection and ROM Addressing, Timing Diagram         2-4           2-35         Character Timing Between Characters in a Single Data Word         2-4           2-36         Character Timing Between Characters in a Single Data Word         2-4           2-37         Intercharacter X Position Update, Flow Diagram         2-4           2-38         Time Shift Register, Timing Diagram (M7014YA-VC1)         2-4           2-39         Descending Character (Ex: Lower Case Q)         2-5           2-40         Positive Current Source <td>2-22</td> <td>Cut-Off Vector Displays</td> <td>2-32</td> | 2-22       | Cut-Off Vector Displays                                  | 2-32 |

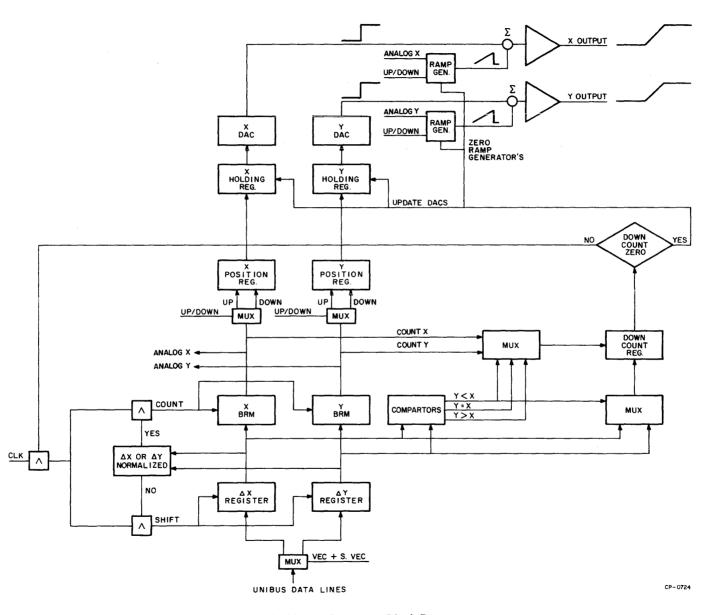

| 2-25         Vector Generator, Timing Diagram         2-3           2-26         Absolute and Normalized Magnitude         2-3           2-27         Point Instruction (Termination), Timing Diagram         2-3           2-28         Path of Electron Beam as Influenced by X and Y Deflection Signals         2-3           2-29         Character Generator, Block Diagram         2-4           2-30         Character Generator, Flow Diagram         2-4           2-31         ROM/Character Relationship         2-4           2-32         ROM/Character Relationship         2-4           2-33         Generation of Intensity Data to the VR14/VR17         2-4           2-34         Word Selection and ROM Addressing, Timing Diagram         2-4           2-35         Character Bit Timing         2-4           2-36         Character Bit Timing         2-4           2-37         Intercharacter X Position Update, Flow Diagram         2-4           2-38         Time Shift Register, Timing Diagram (M7014YA-VC1)         2-4           2-39         Descending Character (Ex: Lower Case Q)         2-5           2-40         Positive Current Source         2-5           2-41         Negative Current Source         2-5           2-42         LM302 Diagram                                                                                                                        | 2-23       | Vector Generator, Block Diagram                          | 2-33 |

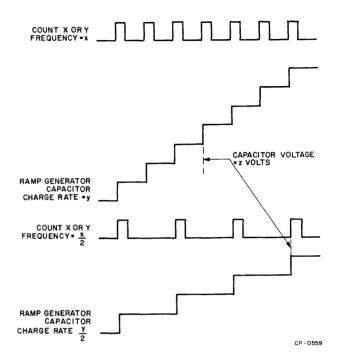

| 2-26       Absolute and Normalized Magnitude       2-36         2-27       Point Instruction (Termination), Timing Diagram       2-3         2-28       Path of Electron Beam as Influenced by X and Y Deflection Signals       2-3         2-29       Character Generator, Block Diagram       2-3         2-30       Character Generator, Flow Diagram       2-4         2-31       ROM/Character Relationship       2-4         2-32       ROM/Character Relationship       2-4         2-33       Generation of Intensity Data to the VR14/VR17       2-4         2-34       Word Selection and ROM Addressing, Timing Diagram       2-4         2-35       Character Bit Timing       2-4         2-36       Character Timing Between Characters in a Single Data Word       2-4         2-37       Intercharacter X Position Update, Flow Diagram       2-4         2-38       Time Shift Register, Timing Diagram (M7014YA-VC1)       2-4         2-39       Descending Character (Ex: Lower Case Q)       2-5         2-40       Positive Current Source       2-5         2-41       Negative Current Source       2-5         2-42       LM302 Diagram       2-5         2-43       Italics Control Circuit       2-5         2-44       Analog Circ                                                                                                                                                          | 2-24       | Relationship of Clock Frequency to Ramp Generator Output | 2-34 |

| 2-27         Point Instruction (Termination), Timing Diagram         2-3           2-28         Path of Electron Beam as Influenced by X and Y Deflection Signals         2-3           2-29         Character Generator, Block Diagram         2-4           2-30         Character Generator, Flow Diagram         2-4           2-31         ROM/Character Relationship         2-4           2-32         ROM/Character Relationship         2-4           2-33         Generation of Intensity Data to the VR 14/VR17         2-4           2-34         Word Selection and ROM Addressing, Timing Diagram         2-4           2-35         Character Bit Timing         2-4           2-36         Character Timing Between Characters in a Single Data Word         2-4           2-37         Intercharacter X Position Update, Flow Diagram         2-4           2-38         Time Shift Register, Timing Diagram (M7014YA-VC1)         2-4           2-39         Descending Character (Ex: Lower Case Q)         2-5           2-40         Positive Current Source         2-5           2-41         Negative Current Source         2-5           2-42         LM 302 Diagram         2-5           2-43         Italics Control Circuit         2-5           2-44         Analog Circuit, Block                                                                                                      | 2-25       | Vector Generator, Timing Diagram                         | 2-35 |

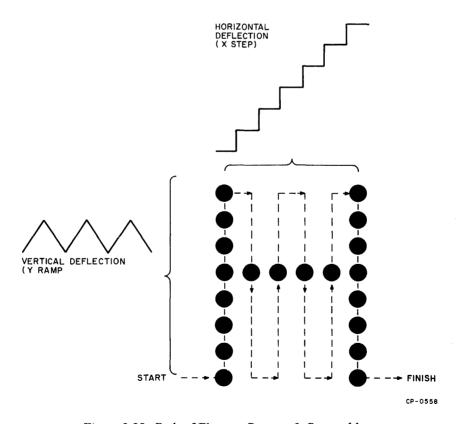

| 2-28         Path of Electron Beam as Influenced by X and Y Deflection Signals         2-36           2-29         Character Generator, Block Diagram         2-31           2-30         Character Generator, Flow Diagram         2-41           2-31         ROM/Character Relationship         2-42           2-32         ROM/Character Relationship         2-42           2-33         Generation of Intensity Data to the VR14/VR17         2-42           2-34         Word Selection and ROM Addressing, Timing Diagram         2-44           2-35         Character Bit Timing         2-44           2-36         Character Timing Between Characters in a Single Data Word         2-44           2-37         Intercharacter X Position Update, Flow Diagram         2-44           2-38         Time Shift Register, Timing Diagram (M7014YA-VC1)         2-49           2-39         Descending Character (Ex: Lower Case Q)         2-50           2-40         Positive Current Source         2-50           2-41         Negative Current Source         2-51           2-42         LM302 Diagram         2-51           2-43         Italics Control Circuit         2-52           2-44         Analog Circuit, Block Diagram         2-52           2-45         Typical Current Summing                                                                                                       | 2-26       | Absolute and Normalized Magnitude                        | 2-36 |

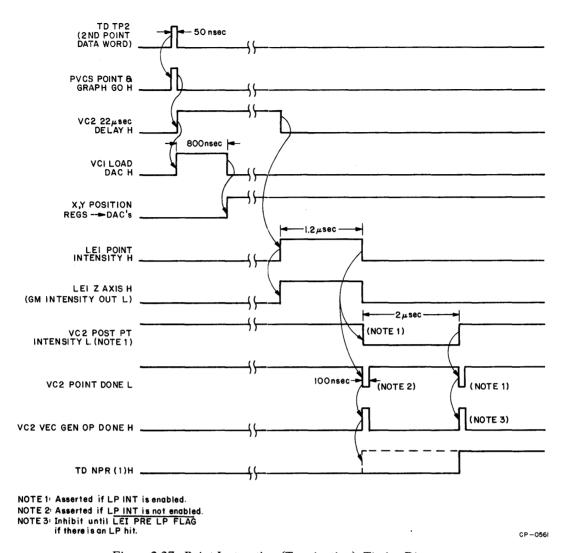

| 2-28         Path of Electron Beam as Influenced by X and Y Deflection Signals         2-36           2-29         Character Generator, Block Diagram         2-31           2-30         Character Generator, Flow Diagram         2-41           2-31         ROM/Character Relationship         2-42           2-32         ROM/Character Relationship         2-42           2-33         Generation of Intensity Data to the VR14/VR17         2-42           2-34         Word Selection and ROM Addressing, Timing Diagram         2-44           2-35         Character Bit Timing         2-44           2-36         Character Timing Between Characters in a Single Data Word         2-44           2-37         Intercharacter X Position Update, Flow Diagram         2-44           2-38         Time Shift Register, Timing Diagram (M7014YA-VC1)         2-49           2-39         Descending Character (Ex: Lower Case Q)         2-50           2-40         Positive Current Source         2-50           2-41         Negative Current Source         2-51           2-42         LM302 Diagram         2-51           2-43         Italics Control Circuit         2-52           2-44         Analog Circuit, Block Diagram         2-52           2-45         Typical Current Summing                                                                                                       | 2-27       | Point Instruction (Termination), Timing Diagram          | 2-37 |

| 2-29         Character Generator, Block Diagram         2-39           2-30         Character Generator, Flow Diagram         2-4           2-31         ROM/Character Relationship         2-4           2-32         ROM/Character Relationship         2-4           2-33         Generation of Intensity Data to the VR14/VR17         2-4           2-34         Word Selection and ROM Addressing, Timing Diagram         2-4           2-35         Character Bit Timing         2-4           2-36         Character Timing Between Characters in a Single Data Word         2-4           2-37         Intercharacter X Position Update, Flow Diagram         2-4           2-38         Time Shift Register, Timing Diagram (M7014YA-VC1)         2-4           2-39         Descending Character (Ex: Lower Case Q)         2-5           2-40         Positive Current Source         2-5           2-41         Negative Current Source         2-5           2-42         LM302 Diagram         2-5           2-43         Italics Control Circuit         2-5           2-44         Analog Circuit, Block Diagram         2-5           2-45         Typical Current Summing Ladder         2-5           2-46         Summing Amplifier Congiguration         2-5 <tr< td=""><td>2-28</td><td>· · · · · · · · · · · · · · · · · · ·</td><td></td></tr<>                                                | 2-28       | · · · · · · · · · · · · · · · · · · ·                    |      |

| 2-30       Character Generator, Flow Diagram       2-4         2-31       ROM/Character Relationship       2-4         2-32       ROM/Character Relationship       2-4         2-33       Generation of Intensity Data to the VR14/VR17       2-4         2-34       Word Selection and ROM Addressing, Timing Diagram       2-4         2-35       Character Bit Timing       2-4         2-36       Character Timing Between Characters in a Single Data Word       2-4         2-37       Intercharacter X Position Update, Flow Diagram       2-4         2-38       Time Shift Register, Timing Diagram (M7014YA-VC1)       2-4         2-39       Descending Character (Ex: Lower Case Q)       2-5         2-40       Positive Current Source       2-5         2-41       Negative Current Source       2-5         2-42       LM302 Diagram       2-5         2-43       Italics Control Circuit       2-5         2-44       Analog Circuit, Block Diagram       2-5         2-45       Typical Current Summing Ladder       2-5         2-46       Summing Amplifier Congiguration       2-5         3-1       Adjustment Locations, A320 Module       3-         3-2       Y Character Ramp       3-         3-                                                                                                                                                                                             | 2-29       |                                                          |      |

| 2-31       ROM/Character Relationship       2-42         2-32       ROM/Character Relationship       2-42         2-33       Generation of Intensity Data to the VR14/VR17       2-43         2-34       Word Selection and ROM Addressing, Timing Diagram       2-42         2-35       Character Bit Timing       2-46         2-36       Character Timing Between Characters in a Single Data Word       2-47         2-37       Intercharacter X Position Update, Flow Diagram       2-48         2-38       Time Shift Register, Timing Diagram (M7014YA-VC1)       2-49         2-39       Descending Character (Ex: Lower Case Q)       2-50         2-40       Positive Current Source       2-50         2-41       Negative Current Source       2-50         2-42       LM302 Diagram       2-50         2-43       Italics Control Circuit       2-51         2-44       Analog Circuit, Block Diagram       2-52         2-44       Analog Circuit, Block Diagram       2-52         2-45       Typical Current Summing Ladder       2-53         2-46       Summing Amplifier Congiguration       2-57         3-1       Adjustment Locations, A320 Module       3-6         3-2       Y Character Ramp       3-7 <t< td=""><td>2-30</td><td><u> </u></td><td></td></t<>                                                                                                                                  | 2-30       | <u> </u>                                                 |      |

| 2-32       ROM/Character Relationship       2-4/2         2-33       Generation of Intensity Data to the VR14/VR17       2-4/2         2-34       Word Selection and ROM Addressing, Timing Diagram       2-4/2         2-35       Character Bit Timing       2-4/2         2-36       Character Timing Between Characters in a Single Data Word       2-4/2         2-37       Intercharacter X Position Update, Flow Diagram       2-4/2         2-38       Time Shift Register, Timing Diagram (M7014YA-VC1)       2-4/2         2-39       Descending Character (Ex: Lower Case Q)       2-5/2         2-40       Positive Current Source       2-5/2         2-41       Negative Current Source       2-5/2         2-42       LM302 Diagram       2-5/2         2-43       Italics Control Circuit       2-5/2         2-44       Analog Circuit, Block Diagram       2-5/2         2-45       Typical Current Summing Ladder       2-5/2         2-46       Summing Amplifier Congiguration       2-5/2         3-1       Adjustment Locations, A320 Module       3-/2         3-2       Y Character Ramp       3-/2         3-3       Rubout Display Pattern       3-/2         3-4       Incorrect Character Display       3-/2 <td></td> <td></td> <td></td>                                                                                                                                                  |            |                                                          |      |

| 2-33       Generation of Intensity Data to the VR14/VR17       2-42         2-34       Word Selection and ROM Addressing, Timing Diagram       2-43         2-35       Character Bit Timing       2-46         2-36       Character Timing Between Characters in a Single Data Word       2-47         2-37       Intercharacter X Position Update, Flow Diagram       2-48         2-38       Time Shift Register, Timing Diagram (M7014YA-VC1)       2-49         2-39       Descending Character (Ex: Lower Case Q)       2-50         2-40       Positive Current Source       2-50         2-41       Negative Current Source       2-50         2-42       LM302 Diagram       2-50         2-43       Italics Control Circuit       2-50         2-44       Analog Circuit, Block Diagram       2-50         2-45       Typical Current Summing Ladder       2-50         2-46       Summing Amplifier Congiguration       2-50         3-1       Adjustment Locations, A320 Module       3-6         3-2       Y Character Ramp       3-6         3-3       Rubout Display Pattern       3-6         3-4       Incorrect Character Display       3-7         3-5       Maintenance Switches, M7013 Module       3-7                                                                                                                                                                                             |            | ,                                                        |      |

| 2-34       Word Selection and ROM Addressing, Timing Diagram       2-45         2-35       Character Bit Timing       2-46         2-36       Character Timing Between Characters in a Single Data Word       2-47         2-37       Intercharacter X Position Update, Flow Diagram       2-48         2-38       Time Shift Register, Timing Diagram (M7014YA-VC1)       2-49         2-39       Descending Character (Ex: Lower Case Q)       2-50         2-40       Positive Current Source       2-50         2-41       Negative Current Source       2-50         2-42       LM 302 Diagram       2-50         2-43       Italics Control Circuit       2-50         2-44       Analog Circuit, Block Diagram       2-50         2-45       Typical Current Summing Ladder       2-50         2-46       Summing Amplifier Congiguration       2-50         3-1       Adjustment Locations, A320 Module       3-6         3-2       Y Character Ramp       3-6         3-3       Rubout Display Pattern       3-6         3-4       Incorrect Character Display       3-7         3-5       Maintenance Switches, M7013 Module       3-6         3-6       Display Pattern 7       3-7         3-8       R                                                                                                                                                                                                      |            |                                                          |      |

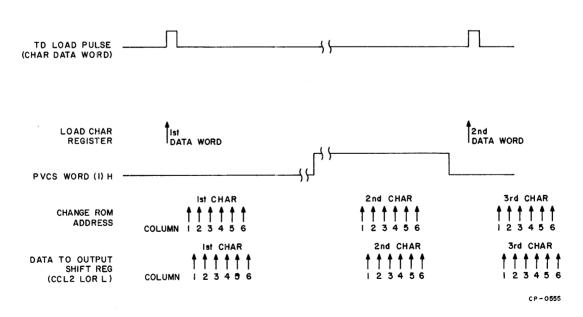

| 2-35       Character Bit Timing       2-46         2-36       Character Timing Between Characters in a Single Data Word       2-47         2-37       Intercharacter X Position Update, Flow Diagram       2-48         2-38       Time Shift Register, Timing Diagram (M7014YA-VC1)       2-49         2-39       Descending Character (Ex: Lower Case Q)       2-50         2-40       Positive Current Source       2-50         2-41       Negative Current Source       2-50         2-42       LM302 Diagram       2-50         2-43       Italics Control Circuit       2-50         2-44       Analog Circuit, Block Diagram       2-50         2-45       Typical Current Summing Ladder       2-50         2-46       Summing Amplifier Congiguration       2-50         3-1       Adjustment Locations, A320 Module       3-6         3-2       Y Character Ramp       3-6         3-3       Rubout Display Pattern       3-6         3-4       Incorrect Character Display       3-6         3-5       Maintenance Switches, M7013 Module       3-6         3-6       Display Pattern 0       3-7         3-7       Display Pattern 7       3-7         3-8       Repeatability Display Pattern                                                                                                                                                                                                             |            | · · · · · · · · · · · · · · · · · · ·                    |      |

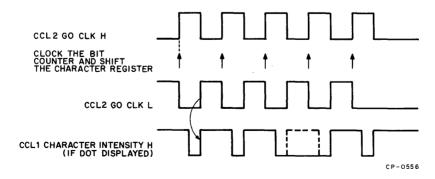

| 2-36       Character Timing Between Characters in a Single Data Word       2-47         2-37       Intercharacter X Position Update, Flow Diagram       2-48         2-38       Time Shift Register, Timing Diagram (M7014YA-VC1)       2-49         2-39       Descending Character (Ex: Lower Case Q)       2-50         2-40       Positive Current Source       2-50         2-41       Negative Current Source       2-50         2-42       LM302 Diagram       2-50         2-43       Italics Control Circuit       2-50         2-44       Analog Circuit, Block Diagram       2-50         2-45       Typical Current Summing Ladder       2-50         2-46       Summing Amplifier Congiguration       2-50         3-1       Adjustment Locations, A320 Module       3-6         3-2       Y Character Ramp       3-6         3-3       Rubout Display Pattern       3-6         3-4       Incorrect Character Display       3-6         3-5       Maintenance Switches, M7013 Module       3-7         3-6       Display Pattern 0       3-7         3-7       Display Pattern 7       3-7         3-8       Repeatability Display Pattern       3-6                                                                                                                                                                                                                                                      |            |                                                          |      |

| 2-37       Intercharacter X Position Update, Flow Diagram       2-48         2-38       Time Shift Register, Timing Diagram (M7014YA-VC1)       2-49         2-39       Descending Character (Ex: Lower Case Q)       2-50         2-40       Positive Current Source       2-50         2-41       Negative Current Source       2-50         2-42       LM302 Diagram       2-50         2-43       Italics Control Circuit       2-50         2-44       Analog Circuit, Block Diagram       2-50         2-45       Typical Current Summing Ladder       2-50         2-46       Summing Amplifier Congiguration       2-50         3-1       Adjustment Locations, A320 Module       3-60         3-2       Y Character Ramp       3-60         3-3       Rubout Display Pattern       3-60         3-4       Incorrect Character Display       3-60         3-5       Maintenance Switches, M7013 Module       3-60         3-6       Display Pattern       3-60         3-7       Display Pattern       3-60         3-8       Repeatability Display Pattern       3-60                                                                                                                                                                                                                                                                                                                                          |            |                                                          |      |

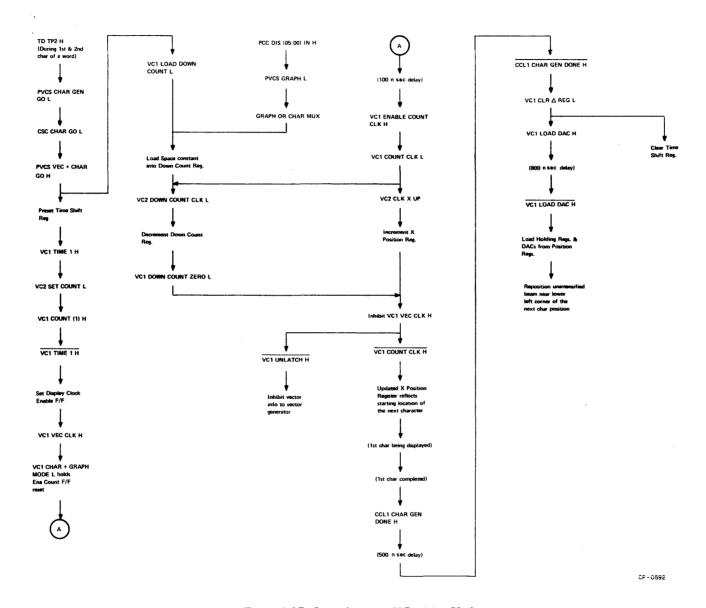

| 2-38       Time Shift Register, Timing Diagram (M7014YA-VC1)       2-49         2-39       Descending Character (Ex: Lower Case Q)       2-50         2-40       Positive Current Source       2-50         2-41       Negative Current Source       2-51         2-42       LM302 Diagram       2-51         2-43       Italics Control Circuit       2-52         2-44       Analog Circuit, Block Diagram       2-52         2-45       Typical Current Summing Ladder       2-52         2-46       Summing Amplifier Congiguration       2-57         3-1       Adjustment Locations, A320 Module       3-6         3-2       Y Character Ramp       3-7         3-3       Rubout Display Pattern       3-7         3-4       Incorrect Character Display       3-7         3-5       Maintenance Switches, M7013 Module       3-7         3-6       Display Pattern 0       3-7         3-7       Display Pattern 7       3-7         3-8       Repeatability Display Pattern       3-9                                                                                                                                                                                                                                                                                                                                                                                                                           |            |                                                          |      |

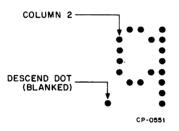

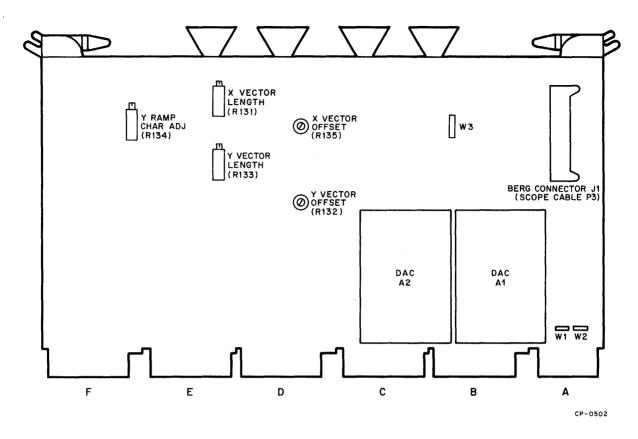

| 2-39       Descending Character (Ex: Lower Case Q)       2-50         2-40       Positive Current Source       2-50         2-41       Negative Current Source       2-51         2-42       LM302 Diagram       2-52         2-43       Italics Control Circuit       2-52         2-44       Analog Circuit, Block Diagram       2-52         2-45       Typical Current Summing Ladder       2-52         2-46       Summing Amplifier Congiguration       2-57         3-1       Adjustment Locations, A320 Module       3-2         3-2       Y Character Ramp       3-3         3-3       Rubout Display Pattern       3-3         3-4       Incorrect Character Display       3-3         3-5       Maintenance Switches, M7013 Module       3-3         3-6       Display Pattern 0       3-3         3-7       Display Pattern 7       3-3         3-8       Repeatability Display Pattern       3-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |                                                          |      |

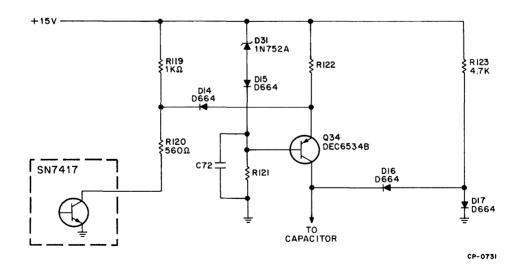

| 2-40       Positive Current Source       2-50         2-41       Negative Current Source       2-51         2-42       LM302 Diagram       2-52         2-43       Italics Control Circuit       2-52         2-44       Analog Circuit, Block Diagram       2-52         2-45       Typical Current Summing Ladder       2-52         2-46       Summing Amplifier Congiguration       2-57         3-1       Adjustment Locations, A320 Module       3-7         3-2       Y Character Ramp       3-7         3-3       Rubout Display Pattern       3-7         3-4       Incorrect Character Display       3-7         3-6       Display Pattern 0       3-7         3-7       Display Pattern 7       3-7         3-8       Repeatability Display Pattern       3-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |                                                          |      |

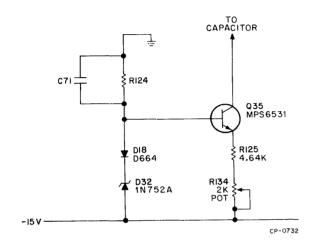

| 2-41       Negative Current Source       2-5         2-42       LM302 Diagram       2-5         2-43       Italics Control Circuit       2-5         2-44       Analog Circuit, Block Diagram       2-5         2-45       Typical Current Summing Ladder       2-5         2-46       Summing Amplifier Congiguration       2-5         3-1       Adjustment Locations, A320 Module       3-         3-2       Y Character Ramp       3-         3-3       Rubout Display Pattern       3-         3-4       Incorrect Character Display       3-         3-5       Maintenance Switches, M7013 Module       3-         3-6       Display Pattern 0       3-         3-7       Display Pattern 7       3-         3-8       Repeatability Display Pattern       3-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |                                                          |      |

| 2-42       LM302 Diagram       2-5         2-43       Italics Control Circuit       2-5         2-44       Analog Circuit, Block Diagram       2-5         2-45       Typical Current Summing Ladder       2-5         2-46       Summing Amplifier Congiguration       2-5         3-1       Adjustment Locations, A320 Module       3-         3-2       Y Character Ramp       3-         3-3       Rubout Display Pattern       3-         3-4       Incorrect Character Display       3-         3-5       Maintenance Switches, M7013 Module       3-         3-6       Display Pattern 0       3-         3-7       Display Pattern 7       3-         3-8       Repeatability Display Pattern       3-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |                                                          |      |

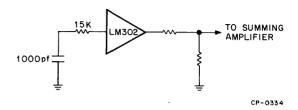

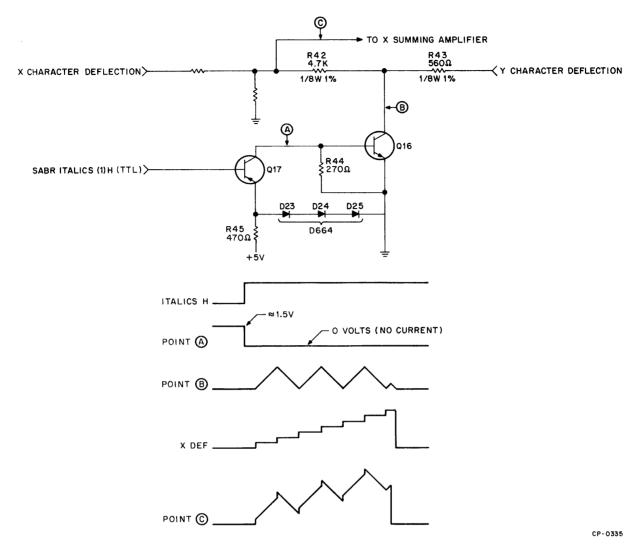

| 2-43       Italics Control Circuit       2-52         2-44       Analog Circuit, Block Diagram       2-52         2-45       Typical Current Summing Ladder       2-52         2-46       Summing Amplifier Congiguration       2-57         3-1       Adjustment Locations, A320 Module       3-7         3-2       Y Character Ramp       3-7         3-3       Rubout Display Pattern       3-7         3-4       Incorrect Character Display       3-7         3-6       Display Pattern 0       3-7         3-7       Display Pattern 7       3-7         3-8       Repeatability Display Pattern       3-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2-42       |                                                          |      |

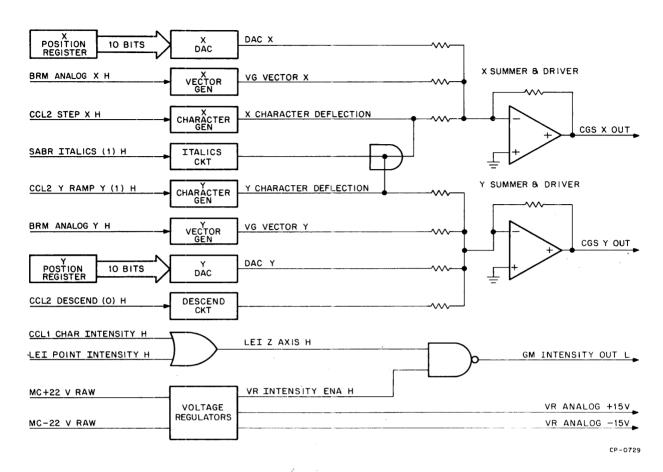

| 2-44       Analog Circuit, Block Diagram       2-53         2-45       Typical Current Summing Ladder       2-54         2-46       Summing Amplifier Congiguration       2-57         3-1       Adjustment Locations, A320 Module       3-4         3-2       Y Character Ramp       3-5         3-3       Rubout Display Pattern       3-6         3-4       Incorrect Character Display       3-6         3-5       Maintenance Switches, M7013 Module       3-6         3-6       Display Pattern 0       3-7         3-7       Display Pattern 7       3-7         3-8       Repeatability Display Pattern       3-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            | · · · · · · · · · · · · · · · · · · ·                    |      |

| 2-45       Typical Current Summing Ladder       2-54         2-46       Summing Amplifier Congiguration       2-57         3-1       Adjustment Locations, A320 Module       3-2         3-2       Y Character Ramp       3-3         3-3       Rubout Display Pattern       3-3         3-4       Incorrect Character Display       3-3         3-5       Maintenance Switches, M7013 Module       3-3         3-6       Display Pattern 0       3-3         3-7       Display Pattern 7       3-3         3-8       Repeatability Display Pattern       3-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |                                                          |      |

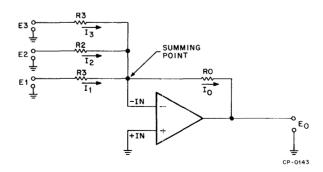

| 2-46       Summing Amplifier Congiguration       2-57         3-1       Adjustment Locations, A320 Module       3-7         3-2       Y Character Ramp       3-7         3-3       Rubout Display Pattern       3-7         3-4       Incorrect Character Display       3-7         3-6       Display Pattern 0       3-7         3-7       Display Pattern 7       3-7         3-8       Repeatability Display Pattern       3-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-45       |                                                          |      |

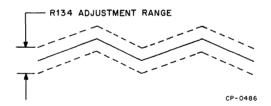

| 3-1       Adjustment Locations, A320 Module       3-3         3-2       Y Character Ramp       3-3         3-3       Rubout Display Pattern       3-3         3-4       Incorrect Character Display       3-3         3-5       Maintenance Switches, M7013 Module       3-3         3-6       Display Pattern 0       3-3         3-7       Display Pattern 7       3-3         3-8       Repeatability Display Pattern       3-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |                                                          |      |

| 3-2       Y Character Ramp       3-3         3-3       Rubout Display Pattern       3-3         3-4       Incorrect Character Display       3-3         3-5       Maintenance Switches, M7013 Module       3-5         3-6       Display Pattern 0       3-7         3-7       Display Pattern 7       3-7         3-8       Repeatability Display Pattern       3-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |                                                          |      |

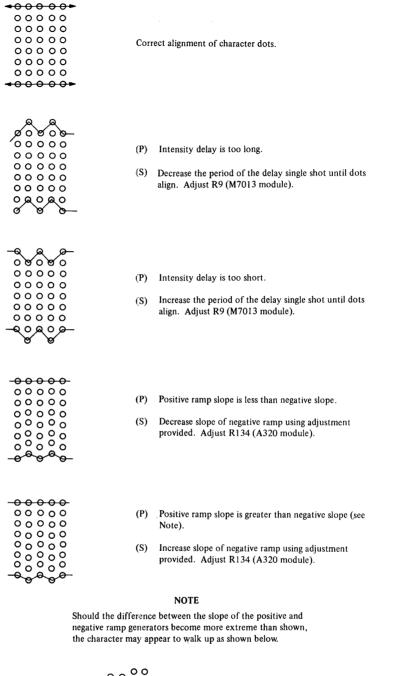

| 3-3       Rubout Display Pattern       3-3         3-4       Incorrect Character Display       3-3         3-5       Maintenance Switches, M7013 Module       3-3         3-6       Display Pattern 0       3-3         3-7       Display Pattern 7       3-3         3-8       Repeatability Display Pattern       3-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |                                                          |      |

| 3-4 Incorrect Character Display 3-3 3-5 Maintenance Switches, M7013 Module 3-5 3-6 Display Pattern 0 3-7 3-7 Display Pattern 7 3-7 3-8 Repeatability Display Pattern 3-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |                                                          |      |

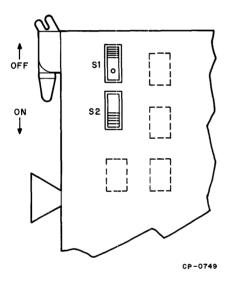

| 3-5       Maintenance Switches, M7013 Module       3-5         3-6       Display Pattern 0       3-7         3-7       Display Pattern 7       3-7         3-8       Repeatability Display Pattern       3-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |                                                          |      |

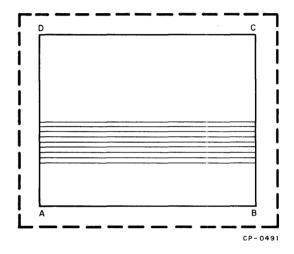

| 3-6       Display Pattern 0       3-         3-7       Display Pattern 7       3-         3-8       Repeatability Display Pattern       3-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            | Maintenance Switches, M7013 Module                       | 3-5  |

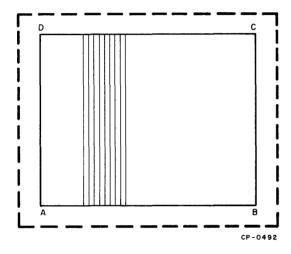

| 3-7 Display Pattern 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |                                                          |      |

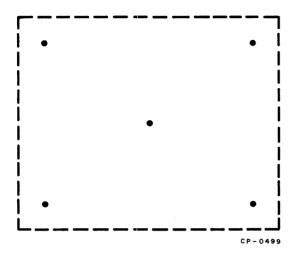

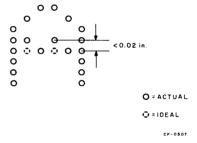

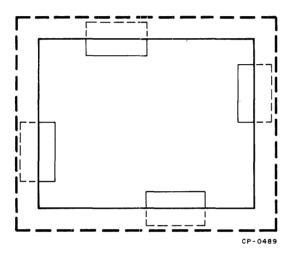

| 3-8 Repeatability Display Pattern                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            | • •                                                      |      |

| <u>.                                      </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            | • •                                                      |      |

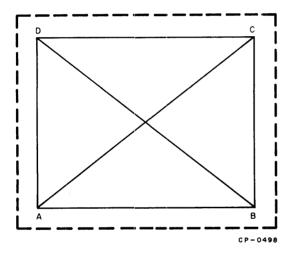

| 3-9 Box with X Display Pattern                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            | - · · · · · · · · · · · · · · · · · · ·                  |      |

| 1 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            | m v                                                      |      |

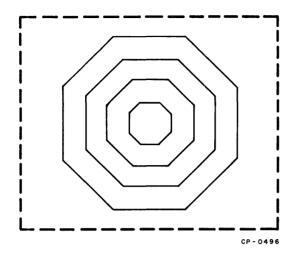

| 3-11 Octagons Display Pattern                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |                                                          |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |                                                          |      |

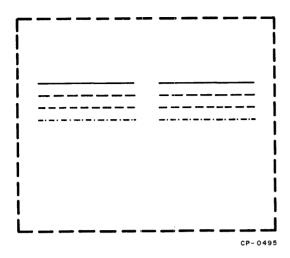

| 3-13 Dash Lines and Blink Display Pattern                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |                                                          |      |

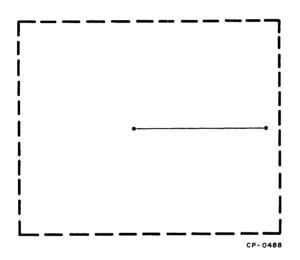

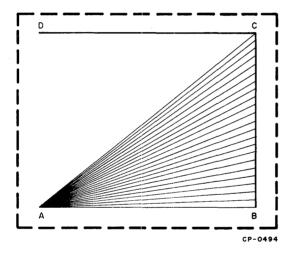

| 3-14 Horizontal Vector Length Display Pattern                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            | <u></u>                                                  |      |

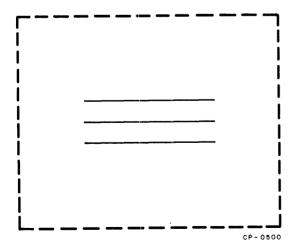

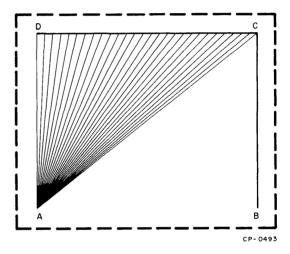

| 3-15 Vertical Vector Length Display Pattern                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            | • • •                                                    |      |