INTRODUCTION TO PROGRAMMING

the

C. J. Karyman

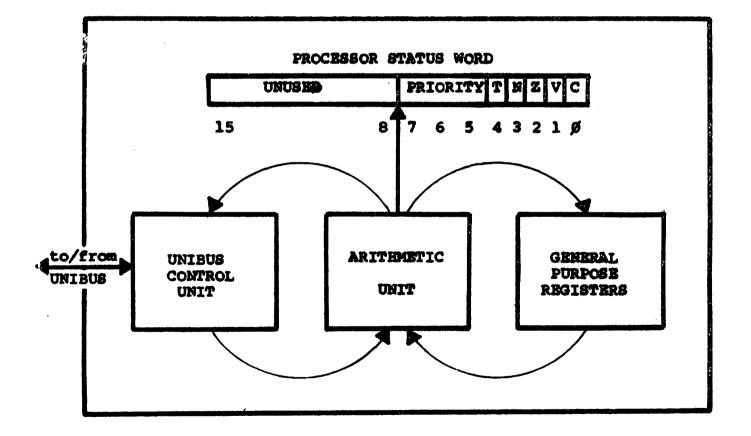

PDP-11

The reproduction in part or whole is strictly prohibited. For copy information contact the Digital Educational Services Department in Maynard, Massachusetts 01754.

C. J. Karyman

,

INTRODUCTION TO PROGRAMMING

the

PDP-11

Donald S. Lawrence, Jr.

3

8

DIGITAL EQUIPMENT CORPORATION

Copyright © 1974 by Digital Equipment Corporation Printed in the U.S.A.

· · ·

.

6

ø

ŧ,

.

.

.

Preliminary Printing, May, 1973

(Chapters I-III)

### NOTE

This handbook is for information purposes and is subject to change without notice

Associated Documents:

- PDP-11 Processor Handbook

- PDP-11 Peripherals and Interfacing Handbook

PDP-11 Paper Tape Software Programming Handbook

Trademarks of Digital Equipment Corporation include:

| DEC            | PDP-11  |

|----------------|---------|

| DECtape        | RSTS-11 |

| DIGITAL (logo) | RSX-11  |

| COMTEX-11      | UNIBUS  |

•

. . . . . **.**

#### PREFACE

The primary purpose of this book is to serve as an introduction to the PDP-11 family of computers, although it will meet the needs of a general readership as well. It assumes little or no previous computer experience on the parce of the reader, and thus contains introductory information of a general nature and discussion of fundamental concepts in addition to supplying material pertinent to the PDP-11.

It is intended to provide an understanding of computers in general and the PDP-11 family in particular, and to serve as a prelude to more advanced documentation.

> Donald S. Lawrence, Jr. May, 1973

> > ċ

## TABLE OF CONTENTS

| Ch <b>apte</b> i | R                                                                                                                                                                              | PAGE |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| I.               | INTRODUCTION TO COMPUTERS                                                                                                                                                      | 1-1  |

|                  | 1.1 PERSPECTIVE                                                                                                                                                                | 1-1  |

|                  | 1.2 DEFINITION                                                                                                                                                                 | 1-2  |

|                  | 1.3 CLASSIFICATION                                                                                                                                                             | 1-6  |

|                  | 1.4 APPLICATION                                                                                                                                                                | 1-8  |

| II.              | NUMBERS AND OTHER STUFF                                                                                                                                                        | 2-1  |

|                  | 2.1 INTRODUCTION                                                                                                                                                               | 2-1  |

|                  | 2.2 NUMBER SYSTEMS                                                                                                                                                             | 2-2  |

|                  | 2.2.1 Basic Principles<br>2.2.2 Decimal Number System<br>2.2.3 Binary Number System<br>2.2.4 Octal Number System                                                               |      |

|                  | 2.3 CONVERSIONS                                                                                                                                                                | 2-23 |

|                  | 2.3.1 Introduction<br>2.3.2 Decimal to Binary<br>2.3.3 Binary to Decimal<br>2.3.4 Decimal to Octal<br>2.3.5 Octal to Decimal<br>2.3.6 Binary to Octal<br>2.3.7 Octal to Binary |      |

|                  | 2.4 ARITHMETIC OPERATIONS                                                                                                                                                      | 2-35 |

|                  | 2.4.1 Introduction<br>2.4.2 Addition<br>2.4.3 Direct Subtraction<br>2.4.4 Complementary Addition                                                                               |      |

|                  | 2.5 LOGIC OPERATIONS                                                                                                                                                           | 2-55 |

|                  | 2.5.1 Introduction<br>2.5.2 AND<br>2.5.3 Inclusive OR<br>2.5.4 Exclusive OR                                                                                                    |      |

2.6 EXERCISES

2-63

q

\$

(And the second

•

•

-----

9

Ţ

(

9

,

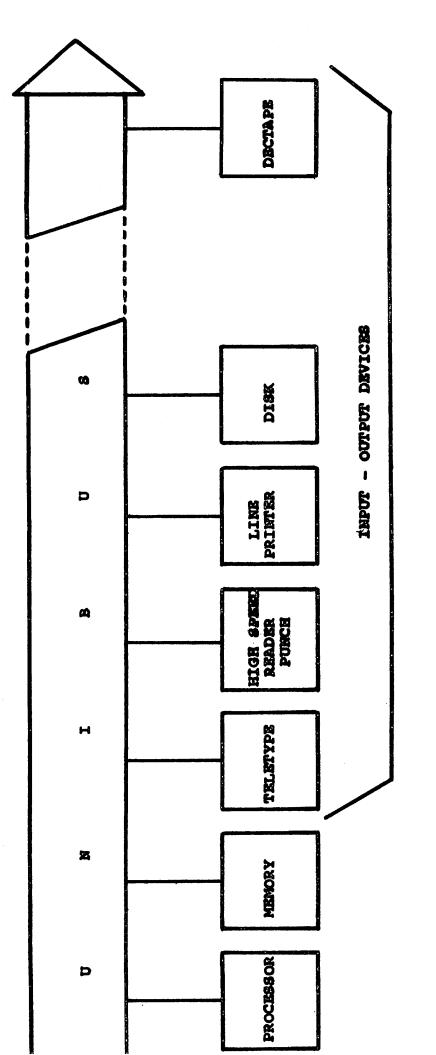

| III. | THE PDP-11                                                                                                                 | 3-1  |

|------|----------------------------------------------------------------------------------------------------------------------------|------|

|      | 3.1 SYSTEM ORGANIZATION                                                                                                    | 3-1  |

|      | 3.1.1 Introduction<br>3.1.2 The UNIBUS<br>3.1.3 Memory<br>3.1.4 Central Processor<br>3.1.5 Input-Output Devices            |      |

|      | 3.2 ADDRESSING MODES                                                                                                       | 3-19 |

|      | 3.2.1 Introduction<br>3.2.2 General Register Addressing Modes<br>3.2.3 Program Counter Addressing Modes<br>3.2.4 Exercises |      |

|      | 3.3 INSTRUCTION SET                                                                                                        | 3-49 |

|      | 3.4 SYSTEM OPERATION (FORTHCOMING)                                                                                         |      |

| IV.  | FUNDAMENTALS OF PROGRAMMING                                                                                                |      |

|      | 4.1 THE PROGRAM                                                                                                            |      |

|      | 4.2 LANGUAGES                                                                                                              |      |

4.3 CONCEPTS AND TECHNIQUES

4.4 EXAMPLES

#

## station and the

#

#

,

#### Chapter 1

#### INTRODUCTION TO COMPUTERS

#### 1.1 PERSPECTIVE

8

The transition from man's first desire to count and measure to your PDP-ll computer is indeed a great one, and the reader is heartily encouraged to pursue the fascinating topic of computer history. For the purpose of this text, it is sufficient to say that the development and continuing evolution of the computer has brought about a dramatic change in our lives and promises even greater change in the years to come.

During the last twenty years especially, there has been an explosive proliferation of computing machines designed to meet a vast range of applications. Perhaps of even more importance than the ever-improving developmental technology is the unceasing discovery of new ways in which we may use computers. In fact, it would seem that we have reached the point where the machine capability and the task are present, and it is only our lack of applicational insight that limits us.

#### 1.2 DEFINITION

The majority of everyday users, as well as the novice, view the computer as a "black box." That is to say, they know what is done (the performance characteristics) but not how it is done (the components and/or means of operation). Though this knowledge is superficial, it is often sufficient; rarely is anyone required to fully comprehend all the details of any computer system. It is in fact customary for the individual to accept a "black box" description of a computer or computer function at some level, and then deepen his understanding when motivated by desire or necessity. As indicated in the preface, this text assumes that you presently regard the computer itself as a "black box," and will attempt to bring you beyond that level.

The computer may be defined as <u>a machine</u>, <u>devised and used</u> by man because (like other machines) it can perform certain tasks better than man himself.

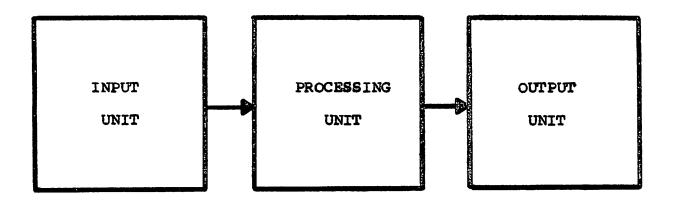

Technically, it is an electronic device capable of accepting information, applying prescribed processes to that information, and supplying the results of those processes. Very basically then, the computer can:

(1) accept INPUT (information to be processed)

(2) PROCESS the information (manipulate it in a prescribed way)

(3) produce OUTPUT (the results)

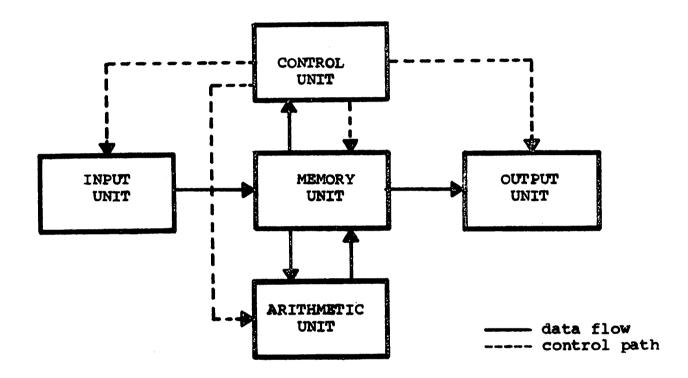

Based on this definition, we may represent the computer by means of the following block diagram (Figure 1-1):

Figure 1-1 Simplified Computer Block Diagram

At this point, our definition and diagram might well encompass other devices, such as the electric adding machine and desk calculator. To differentiate, we will note that the computer posseses two additional (and distinctive) characteristics:

(1) It is capable of manipulating a variety of symbols, and is not restricted to numbers only. It processes data.

(2) It processes automatically, with only initial human intervention required. The sequence of operations to be performed (called the program) is first stored in the computer.

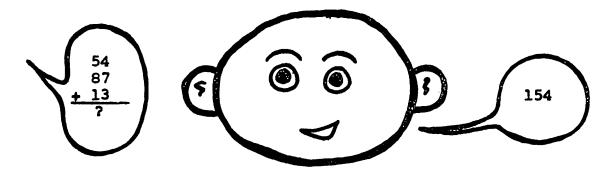

A deeper observation of computer operation will help illustrate these aspects of your Programmed Data Processor. Let us approach this more detailed representation by using you as an example. You are given the verbal directive, "Mentally add the numbers fifty-four, eighty-seven, and thirteen." After an individually dependent computational pause, you orally respond, "The sum is one hundred and fifty-four."

Figure 1-2 Analogous Computer Block Diagram

What has happened? Your aural and vocal anatomy has served as the means of INPUT and OUTPUT respectively; your brain has been used to PROCESS the information. For the present, the terms INPUT and OUTPUT sufficiently describe the operations performed, but the term PROCESS appears to be somewhat obscure. Let us examine what has taken place here a little more closely.

(1) You remembered the values given and called upon skills previously learned and retained - therefore, MEMORY was required

(2) The operations were ordered, with the values being manipulated in a prescibed manner - thus, some element of CONTROL was present

(3) A mathematical calculation was performed - hence, an ARITHMETIC function was involved

We may directly associate these features with units in the basic computer block diagram (Figure 1-3) to complete this general definition.

Ý.

Figure 1-3 Basic Computer Block Diagram

<u>INPUT UNIT</u> - Under the direction of the CONTROL UNIT, it supplies the computer with all the information needed to accomplish a given task; the values to be operated upon (data) and the operations to be performed upon those values (program)

<u>MEMORY UNIT</u> - Contains information for the CONTROL UNIT (program) and the ARITHMETIC UNIT (data); holds intermediate and final results <u>CONTROL UNIT</u> - Directs the entire process by specifying to the ARITHMETIC UNIT what operations are to be performed, in which order they are to be performed, and where to get/put the data involved

ARITHMETIC UNIT - Under the direction of the CONTROL UNIT, it performs the actual operations; the "working area"

<u>OUTPUT UNIT</u> - Under the direction of the CONTROL UNIT, it records the results of computer operations

#### 1.3 CLASSIFICATION

As specified by the characteristics in Table 1-1, every computer may be basically categorized as either ANALOG or DIGITAL (there are <u>hybrid</u> computers that have both analog and digital properties). We have been discussing (and will continue to discuss) only the <u>digital</u> computer, for your PDP-11 belongs to that class. This comparison is made for reasons of completeness and further definition.

Table 1-1 Comparison of Analog and Digital Computers

| ANALOG                                                                                        | DIGITAL                                                 |

|-----------------------------------------------------------------------------------------------|---------------------------------------------------------|

| (1) Variable electrical or<br>mechanical quantities<br>used to represent data                 | (1) Discrete numerical values<br>used to represent data |

| (2) Varying and continuous level<br>of input yields varying and<br>continuous level of output |                                                         |

| (3) Calculates by means of a measuring process                                                | (3) Calculates by means of a counting process           |

| (4) Example: speedometer                                                                      | (4) Example: odometer                                   |

We may also categorize computers according to their design capability as being either SPECIAL PURPOSE or GENERAL PURPOSE, terms that are very self-explanatory. The special purpose machine is constructed to perform one task, or a closely related group of tasks. The single sequence of operations it is to perform (its program) is "built in." If ever a program change becomes necessary, a hardware modification (physical restructuring) is required. Conversely, the general purpose machine is designed to be capable of performing many varied tasks. The many possible operation sequences (programs) are kept in the memory unit of the general purpose computer, and for this reason it is sometimes game ferred to as a stored program machine. To perform a given task, the user simply calls upon the appropriate program. The change from one task to another is accomplished by selecting another program already in the memory or entering it by means of the input unit.

It should be apparent that previous discussion has been of the <u>general purpose</u> computer, and we will continue to confine ourselves to this type. Your PDP-11 is classed as both <u>digital</u> and <u>general purpose</u>.

Now that you have a basic understanding of what the computer is, let us generally discuss why and in what manner it is used.

Ω.

#### 1.4 APPLICATION

If given unlimited time to complete a task, factors such as volume of data, complexity of calculation, and degree of accuracy become immaterial. For example, you alone could certainly process the payroll of a large corporation or perform all the calculations necessary to launch a missile. The chance of you accurately doing either in a matter of hours or minutes, however, is rather remote. It is then speed of operation which is the ultimate consideration in both cases. This element of <u>speed</u>, coupled with accuracy and reliability, is the underlying advantage of the computer; it is the major reason for its existence and use.

ġ.

We have said that the computer is used because it performs certain tasks "better" than man. The interpretation of this term is dependent upon the task, and may imply any combination of the following features: speed, accuracy, precision, reliability, economy, efficiency, feasibility. Where then is the computer to be used? Wherever its attributes enable the task to be done "better."

To list the wide and ever-expanding range of specific applications would be an arduous chore (surely requiring the use of a computer!). If, by way of example, the results of a PDP-11 applicational survey were immediately available to be given here, the variety of response would easily fill the remainder of the book. And this would be for only one computer model of one corporation! Keeping this in mind, we may denote four general areas of applica-

tion:

<u>Business</u> - Computers used in business applications are usually involved with record keeping; automating the many tedious, repetitious tasks associated with classifying, processing, and maintaining information of all kinds. As a rule, the business computer is required to perform only a few simple calculations, but it must be capable of handling a great volume of data.

Þ

<u>Scientific</u> - In the scientific application, the computer is primarily used for problem solving; the repeated evaluation of expressions with different values. It has made practical the extrapolation of immensely complex algorithms. In contrast to the business computer, there is usually a small amount of data involved, but a great deal of calculation.

<u>Control</u> - The capability of the computer to make precise calculations and evaluations at a high rate of speed causes it to be used in control environments ranging from national defense to the industrial production line. Here the computer receives information, uses it in calculations, and based upon the result "decides" what to do as an appropriate response.

<u>Simulation</u> - Any given task may be too dangerous, costly, or intricate for man to attempt. It may not be feasible for him at all. In such situations, the computer is used to simulate all conditions and interactions, yielding knowledge without risk.

ġ

懮

#### Chapter 2

#### NUMBERS AND OTHER STUFF

#### 2.1 INTRODUCTION

In writing a book such as this, it is very often desirable to explain several things simultaneously. This is one of those times!

The first chapter has defined the general purpose digital computer, and shown that it manipulates data according to a program of instructions. A logical continuation could therefore be a detailed look at the PDP-11 in terms of organization and unit interaction. On the other hand, since we have mentioned the program and indicated its significance, fundamentals of programming could just as reasonably follow. Then too, a discussion of programming languages and data representation might serve as a likely sequel.

In developing any of these topics, however, there is an inescapable involvement with number concepts. Numerical references must be made in describing the PDP-11 and its operation; program instructions and data are ultimately represented in numerical code. This chapter will then concern itself with those number concepts and operations required for you to fully appreciate subsequent discussion of programming the PDP-11.

The subject of computer math, numbers and "other stuff," is interruptive regardless of when it is introduced. For this reason, the reader may wish to move past it for the present and make backward references where necessary.

3

\$

#### 2.2 NUMBER SYSTEMS

#### 2.2.1 Basic Principles

Man's earliest form of notation was the tally mark, where there existed a one-to-one correspondence between the marker and the object to be counted. The aggregate of the scratch marks, pebbles, or notches was the "number" he wished to record. This principle of repetition proved cumbersome for even moderately large numbers, however, and so there evolved various number systems to meet the increasing demands of civilization.

- 1

The number system is a standard means of representing quantity. It consists of a finite set of symbols, called numerals or digits, and rules which specify how the symbols are arranged to form numbers. The early number systems offered an improvement over recording each unit in that they combined unique quantities of units into groups and assigned discrete symbols to represent those groups. They featured the principle of addition, where the value of an entire number is determined by adding the values of the individual symbols that comprise it, irrespective of position. (MMMCCCDOXIII = 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 1000 + 100 The positional number systems which followed contain two additional and distinctive features which greatly simplify the operations needed to manipulate numbers: the concept of position and the inclusion of the zero symbol. Like their early counterparts, these systems have discrete symbols with unique values and follow the principles of addition and multiplication. The major distinction is the principle of place value, which specifies that there is not only a unique value for the symbol but also a unique value for the position. Thus the value associated with a symbol is determined by both its absolute value and the value of its relative position within the number  $(3333 = 30^{0}0^{0}+30^{0}+3^{0}+3 = 3333)$ .

The importance of the zero symbol in a positional number system is illustrated by the application of the count and carry (or regrouping) principle. For example, we count from zero to ten in the familiar decimal system as follows:

Ø123456789Ø

Þ

ø

Å

We cycle through the digits to nine, but do not create another symbol in counting an additional unit. We instead carry the one to the next (tens) place, and record it there. To indicate that there are no units, and to "hold" the units place, we record a zero in that position. The three number systems that we will discuss in some detail are presented in Table 2-1. These are all positional number systems which demonstrate the principles we have previously mentioned; addition, multiplication, place value, count and carry.

8

3

Table 2-1 Digits and Bases of Selected Number Systems

| NUMBER SYSTEM | DIGI <b>TS</b>      | BASE |

|---------------|---------------------|------|

| Decimal       | Ø,1,2,3,4,5,6,7,8,9 | 1ø   |

| Binary        | Ø,1                 | 2    |

| Octal         | Ø,1,2,3,4,5,6,7     | 8    |

The term base, introduced in the Table, is commonly used to name or describe a number system. The decimal system, for example, is often referred to as the base ten system. For any positional number system, the base (or radix) is the number of digits it contains.

#### 2.2.2 Decimal Number System

ġ.

One of the few assumptions made in this text is that you are familiar with the decimal number system. It is the mathematical language of the "real world;" a language that you use on a daily basis. You have memorized the rules and operational procedures to the point that they are automatically applied, and performing any calculation is straightforward. The purpose of this chapter is to have you become equally well acquainted with the binary and octal systems. We will briefly reintroduce the decimal system here in relation to our previous discussion of basic principles, and later reference it to help illustrate those aspects it has in common with the less familiar systems.

The decimal or <u>base ten</u> number system is comprised of the digits zero through nine  $(\emptyset, 1, 2, 3, 4, 5, 6, 7, 8, 9)$ . It is a positional number system, so that in progressing from right to left within a decimal number, the value associated with each position is an increasing power or multiple of the base. This place value principle is presented in Table 2-<sup>3</sup>.

## Table 2-2 Powers of Ten

.

2

-

Table 2-3 Positional Notation with Powers of Ten

## Powers of Ten

| 6           | 5       | 4      | 3     | 2   | 1  | ø  |

|-------------|---------|--------|-------|-----|----|----|

| 1Ø          | 1ø      | 1ø     | 1Ø    | 1ø  | 1ø | 1ø |

| 1 ,øøø ,øøø | 1øø,øøø | 10,000 | 1,øøø | løø | 1ø | 1  |

Place Values

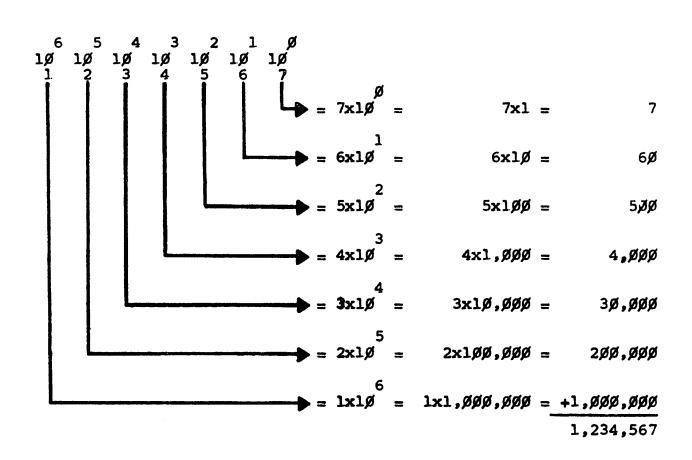

As shown in Table 2-4, determining the total value of a decimal number is accomplished by applying the principles of place value, multiplication, and addition: multiplying the discrete value of the digit by the value of the position in which it is placed, and then adding the resulting products.

Table 2-4 Decimal Number as the Sum of Powers

<u>.</u>

The count and carry principle, to be examined in more detail when we later discuss arithmetic operations, can be simply illustrated by counting or addition. As evidenced by the example below, presented earlier in discussing basic principles of positional number systems, we see that the terms count and carry are quite self-descriptive; <u>count</u> until the base is equaled, and carry that indication to the next column.

ē.

When performing addition, the procedure is as follows: (1) Add the digits in the column, (2) If the base is neither equaled nor exceeded, record the sum; (3) If the base is equaled or exceeded, divide by the base, record the remainder, and carry the quotient to the next column.

Note the presence of the zero symbol in the sum, indicating "no hundreds" and "no thousands," and also "holding" those places within the number.

#### 2.2.3 Binary Number System

ġ

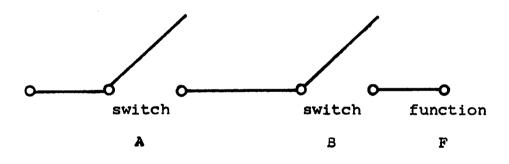

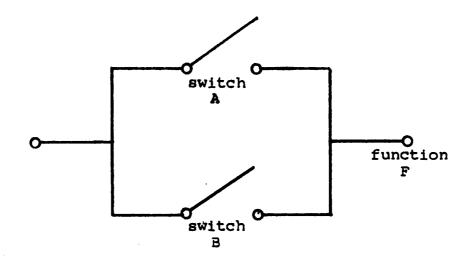

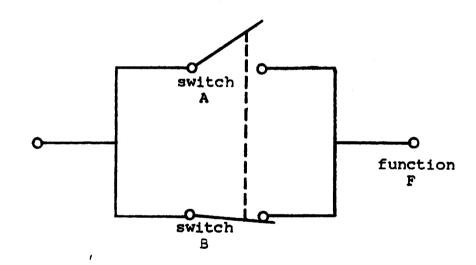

The binary or <u>base two</u> number system is comprised of only two digits, zero and one, commonly referred to as bits (<u>binary digits</u>). As illustrated in Figure 2-1, this system is capable of representing but two conditions, and thus lends itself to the decision-making process; ideally practical for the computer.

Figure 2-1 Popular Binary Device in Action

Since physical and electrical entities have but two states (i.e., switch open/switch closed, current/no current), internal components of a computer can be easily designed to accommodate data in binary form. Computers have been built to operate with other number systems, but the increased number of digits along with the proportionally increased number of possible conditions make these computers overly complex in design and difficult to manufacture. For this reason, the PDP-11 and a majority of computers operate with the binary number system, considered the "language of the computer." Though the computer works internally with the binary number system, this does not mean that all information input must be so represented. In fact, rarely is the data initially in binary form. If strictly numerical, it is generally octal or decimal, but it is even more commonly expressed in one of many alphanumeric computer languages. As we will later discuss, there are several methods by which information in any of these forms is converted to binary before it is processed by the computer.

È,

We noted earlier that the binary or <u>base two</u> number system is comprised of the digits zero and one  $(\emptyset,1)$ . Like the decimal system, it too is a positional number system. Progressing from right to left within a binary number, the value associated with each position is an increasing power or multiple of the base. This place value principle for the binary system is presented in Table 2-6.

## Table 2-5 Powers of Two

| ø<br>2  | 8 | 1                                      | =  | 1              |

|---------|---|----------------------------------------|----|----------------|

| 1<br>2  | = | 2                                      | =  | 2              |

| 2<br>2  | = | 2x2                                    | =  | 4              |

| 3<br>2  | = | 2x2x2                                  | =  | 8              |

| 4<br>2  | = | 2x2x2x2                                | IJ | 16             |

| 5<br>2  | H | 2x2x2x2x2                              | =  | 32             |

| 6<br>2  | = | 2x2x2x2x2x2                            | =  | 64             |

| 7<br>2  | = | 2x2x2x2x2x2x2x2                        | =  | 128            |

| 8<br>2  | = | 2x2x2x2x2x2x2x2x2x2                    | =  | 256            |

| 9<br>2  | = | <b>2x2x2x2x2x2x2x2x2x2</b>             | =  | 512            |

| 1ø<br>2 | Ŧ | 2x2x2x2x2x2x2x2x2x2x2x2x2x2x2x2x2x2x2x | =  | 1 <b>,</b> Ø24 |

| 11<br>2 | = | 2x2x2x2x2x2x2x2x2x2x2x2x2x2x2x2x2x2x2x | =  | 2 <b>,</b> ø48 |

| 12<br>2 |   | 2x2x2x2x2x2x2x2x2x2x2x2x2x2x2x2x2x2x2x | =  | 4 <b>,</b> ø96 |

| 13<br>2 | = | 2x2x2x2x2x2x2x2x2x2x2x2x2x2x2x2x2x2x2x | 8  | 8,192          |

| 14<br>2 | 8 | 0000000000000                          |    | -              |

| 15<br>2 | = | 2x2x2x2x2x2x2x2x2x2x2x2x2x2x2x2x2x2x2x | =  | 32,768         |

|         |   |                                        |    |                |

Ę

ĕ

4

ø

ę

Table 2-6 Positional Notation with Powers of Two

| Powers | of | Two |

|--------|----|-----|

|--------|----|-----|

| 15     | 14     | 13    | 12            | 11    | 1Ø    | 9   | 8   | 7   | 6 | 5  | 4  | 3 | 2 | 1 | ø |

|--------|--------|-------|---------------|-------|-------|-----|-----|-----|---|----|----|---|---|---|---|

| 2      | 2      | 2     | 2             | 2     | 2     | .2  | 2   | 2   | 2 | 2  | 2  | 2 | 2 | 2 | 2 |

| 32,768 | 16,384 | 8,192 | <b>4</b> ,ø96 | 2,ø48 | 1,ø24 | 512 | 256 | 128 |   | 32 | 16 | 8 | 4 | 2 | 1 |

•

.....

Place Values

**3**-

P

Since the binary system is a positional number system, the rules are identical to those of the decimal and octal systems. The only difference, of course, is that the base is <u>two</u> rather than ten or eight.

臣

Determining the total value of any binary number is then accomplished in the same manner used for the decimal system: applying the principles of place value, multiplication, and addition. The discrete value of the digit ( $\emptyset$  or 1) is multiplied by the value of the position in which it is placed, and the resulting products are added.

This operation is presented in Table 2-7.

15 14 13 12 11 ø 1ø 9 8 7 6 5 4 3 2 2 2 2 2 2 2 2 2 Ø |x| =1 h = 1x2=  $\emptyset x2 =$ ø  $= \emptyset x 2$ = 2 1x4 =4 = 1x2= 3 1x8 =8 = 1x2= 4 Øx16 = ø  $= \emptyset x 2$ = 5 1x32 =32 = 1x2= 6 Øx64 = ø = % x2 = 7 px128 =ø  $\mathbf{b} = \mathbf{\emptyset} \mathbf{x} \mathbf{2}$ = 8 1x256 =256 = 1x2= 9 = 1x21x512 =512 = 1ø  $= \emptyset x 2$ = Øx1,Ø24 = ø 11  $= 1x2, \emptyset 48 =$ 2,048 = 1x212 **→** = Øx2 = Øx4,Ø96 = ø 13  $= \emptyset x 2$ = Øx8,192 = ø 14  $= 1x^2$  $= 1 \times 16,384 = 16,384$ 15 = 1x2 $= 1 \times 32,768 = +32,768$ 52,Ø13

ø

Table 2-7 Binary Number as the Sum of Powers

, for

The count and carry principle also applies to the binary number system, and can be simply illustrated by counting or addition. In fact, one advantage of binary notation is the simplicity of operation. Since the system consists of only the symbols zero and one, all the digits are used merely counting to one! Counting an additional unit equals the base, and is represented as 10 (read as "one zero," not "ten"). You have <u>counted</u> until the base was equaled, and then <u>carried</u> to the next column. As shown in Table 2-8, this occurs quite often in the binary number system!

$\mathbf{N}$

લુ

Table 2-8 Counting in Binary with Decimal Equivalents

| Binary         | Decimal Equivalents |

|----------------|---------------------|

| ø              | ø                   |

| 1              | 1                   |

| 1ø             | 2                   |

| 11             | 3                   |

| 1øø            | 4                   |

| 1.Ø1           | 5                   |

| 1.1 <i>ø</i>   | 6                   |

| 111            | 7                   |

| 1øøø           | 8                   |

| 1øø1           | 9                   |

| lølø           | lø                  |

| 1ø11           | 11                  |

| 11øø           | 12                  |

| 11ø1           | 13                  |

| 111ø           | 14                  |

| 1111           | 15                  |

| 1 <i>øøøø</i>  | 16                  |

| 1 <i>øøø</i> 1 | 17                  |

| 1øø1ø          | 18                  |

| 1øø11          | 19                  |

| løløø          | 2ø                  |

Binary addition illustrates both the count and carry principle and the operational simplicity of the system. As shown in Figure 2-2, there are only four possible individual conditions.

| Addend | Addend | Sum | Carry |

|--------|--------|-----|-------|

| ø      | ø      | ø   | ø     |

| ø      | 1      | 1   | ø     |

| 1      | Ø      | 1   | ø     |

1

1

Figure 2-2 The Four Possible Conditions for Binary Addition

| ø         | ø         | 1         | 1. |

|-----------|-----------|-----------|----|

| <u>+Ø</u> | <u>+1</u> | <u>+Ø</u> | +1 |

| ø         | 1         | 1         | lø |

Ø

The procedure followed in the addition operation is the same as that followed for the decimal system: (1) Add the digits in the column, (2) If the base is neither equaled nor exceeded, record the sum; (3) If the base is equaled or exceeded, divide by the base, record the remainder, and carry the quotient to the next column.

Note the importance of recording the zero remainders in the example below, "holding" those places within the sum.

| carries: | 14- | יין <sub>זי</sub> ן <sub>זי</sub> ן |    |   |   | 1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1 <th>14</th> <th colspan="5">ףי די ו</th> |   |   |   |   | 14 | ףי די ו |   |   |   |   |

|----------|-----|-------------------------------------|----|---|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|----|---------|---|---|---|---|

|          | ø   | ø                                   | 1  | 1 | ø | ø                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1 | ø | 1 | ø | ø  | ø       | ø | 1 | 1 | 1 |

|          | +Ø  | 1 '                                 | 1  | ø | ø | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1 | 1 | ø | ø | ø  | 1       | 1 | 1 | ø | ø |

|          | 1   | Lø                                  | Lø | 1 | 1 | Lø                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ø | 1 | 1 | ø | 1  | Lø      | ø | ø | 1 | 1 |

### 2.2.4 Octal Number System

We may call the decimal number system the "numerical language of the real world" because much computer input and output data is in this form. The binary number system is considered the "numerical language of the computer" because the majority of computers are designed to work with this notation. For the machine language and assembly language user, the octal number system provides an easily handled bridge between these two, and may be called the "numerical language of the programmer."

As noted earlier, the binary system is most commonly used with computers because its simplicity yields hardware advantages; the components can be fast, yet relatively simple and inexpensive to manufacture. Computers, however, don't have to "look" at the binary numbers they manipulate, and due to speed of operation, work with them one at a time. To the programmer who must work with many cumbersome groupings, the length of the numbers and the similarity of digits makes the binary system far from ideal. As we will discuss shortly, there exists a quick and direct conversion between the binary and octal systems, and for reasons given any numerical work at the machine language or assembly language level is done with the latter system. The octal or <u>base eight</u> number system is comprised of the digits zero through seven  $(\emptyset, 1, 2, 3, 4, 5, 6, 7)$ . Like the decimal and binary systems, it too is a positional number system. Progressing from right to left within an octal number, the value associated with each position is an increasing power or multiple of the base. This place value principle for the octal system is presented in Table 2-1 $\emptyset$ . 6

| ø<br>8 | = | 1                | Ħ | 1.             |

|--------|---|------------------|---|----------------|

| 1<br>8 | 8 | 8                | = | 8              |

| 2<br>8 | = | 8x8              | = | 64             |

| 3<br>8 | = | 8x8x8            | 8 | 512            |

| 4<br>8 | = | 8 <b>x8x8x</b> 8 | = | 4 <b>,</b> Ø96 |

| 5<br>8 | = | 8x8x8x8x8        | = | 32,768         |

-

ş

Table 2-9 Powers of Eight

1

Table  $2-1\emptyset$  Positional Notation with Fowers of Eight

# Powers of Eight

| <b>5</b> | 4              | 3   | 2  | 1 | ø |

|----------|----------------|-----|----|---|---|

| 8        | 8              | 8   | 8  | 8 | 8 |

| 32,768   | 4 <b>,</b> ø96 | 512 | 64 | 8 |   |

Place Values

Since the octal system is a positional number system, the rules are identical to those of the decimal and binary systems. The only difference, of course, is that the base is <u>eight</u> rather than ten or two.

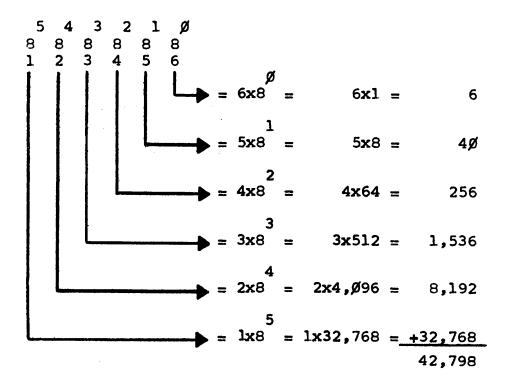

As presented in Table 2-11, determining the total value of any octal number is accomplished in the same manner used for the decimal and binary systems: applying the principles of place value, multiplication, and addition. The discrete value of the digit is multiplied by the value of the position in which it is placed, and the resulting products are added.

Table 2-11 Octal Number as the Sum of Powers

The count and carry principle also applies to the octal number system, and can be simply illustrated by counting or addition. As shown in Table 2-12, you <u>count</u> until the base is equaled, and then <u>carry</u> to the next column.

Table 2-12 Counting in Octal with Decimal Equivalents

ą

9

5

| Octal                                | Decimal Equivalents                                                          |

|--------------------------------------|------------------------------------------------------------------------------|

| ø                                    | ø                                                                            |

| 1                                    | 1                                                                            |

| 2                                    | 2                                                                            |

| 3                                    | 3                                                                            |

| 4                                    | 4                                                                            |

| 5                                    | 5                                                                            |

| Ø<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | Ø<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>1Ø<br>11<br>12<br>13<br>14 |

| 10                                   | /<br>Q                                                                       |

| שעב.<br>דו                           | с;<br><b>9</b>                                                               |

| 1Ø<br>11<br>12                       | ומ                                                                           |

| 13                                   | 11                                                                           |

| 14                                   | 12                                                                           |

| 15                                   | 13                                                                           |

| 16                                   | 14                                                                           |

| 17                                   | 15                                                                           |

| 2Ø                                   | 16                                                                           |

| •                                    | •                                                                            |

| зø                                   | 24                                                                           |

| Sø                                   | 24                                                                           |

| •                                    | •                                                                            |

| 4ø                                   | 32                                                                           |

| •                                    | •                                                                            |

| •                                    | •                                                                            |

| 5Ø                                   | 4 <i>Ø</i>                                                                   |

| •                                    | •                                                                            |

| бø                                   | 48                                                                           |

| ср                                   |                                                                              |

| •                                    | •                                                                            |

| 7ø                                   | 56                                                                           |

| •                                    | •                                                                            |

| •                                    | •                                                                            |

| løø                                  | 64                                                                           |

The procedure followed for addition is the same as that followed for the decimal and binary systems: (1) Add the digits in the column, (2) If the base is neither equaled nor exceeded, record the sum; (3) If the base is equaled or exceeded, divide by the base, record the remainder, and carry the quotient to the next column.

4

3

carries:

$$1^{4}$$

$1^{4}$   $1^{4}$   $1^{4}$   $1^{4}$

1 2 3 4 5 6

$+7 \not 0 6 1 5 2$

1  $\not 0 3 - 1 6 - 3 \not 0$

Again note the importance of the zero remainders recorded in the sum, "holding" those places within the number.

#### 2.3 CONVERSIONS

ι.

### 2.3.1 Introduction

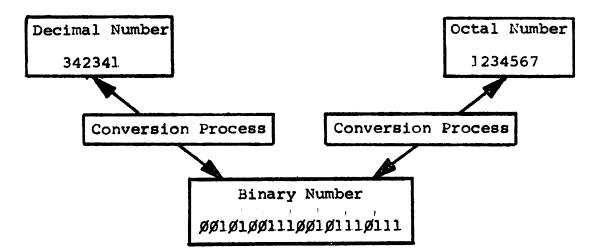

It should by now be established that the binary number system is good for computers, but little else! Therefore, numerical data written in decimal or octal form must first be converted to binary so that it can be processed by the computer, and then the results converted back from binary to decimal or octal so that they can be readily interpreted. This process is represented by Figure 2-3.

As noted earlier, these conversion processes are usually performed by programs previously written and stored in the computer. Specific conversion examples follow to provide an understanding of the processes.

### 2.3.2 Binary to Decimal Conversion

There are two commonly used methods for converting binary numbers to decimal equivalents: the Place Value method and the Double Dabble method.

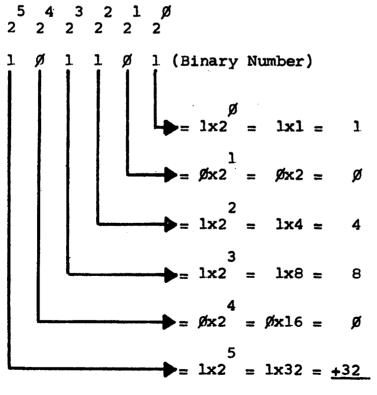

The Place Value method is simply the procedure used in representing a binary number as the sum of powers. The discrete value of each digit is multiplied by the value of the position in which it is placed, and the resulting products are added. An example of this method is presented in Table 2-13.

Table 2-13 Place Value Binary to Decimal Conversion

45 (Decimal Equivalent)

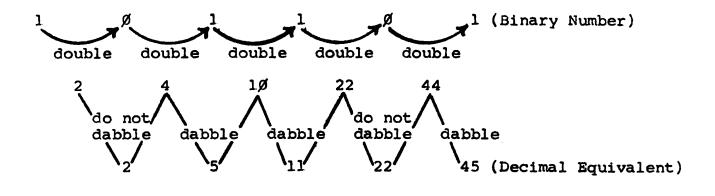

To convert binary numbers to decimal equivalents by means of the Double Dabble method, begin with the most significant bit (left-most one bit) of the binary number. <u>Double</u> that bit, and if the next lower order bit is a one, <u>dabble</u> (add one). If the next lower order bit is a zero, do not dabble. Moving from left to right within the binary number, repeat this process (doubling the sum if the next bit is zero, doubling the sum and dabbling if the next bit is one) until there are no more digits. An example of this method is presented in Table 2-14.

Table 2-14 Double Dabble Binary to Decimal Conversion

# 2.3.3 Decimal to Binary Conversion

There are two commonly used methods for converting decimal numbers to binary equivalents: the Subtraction of Powers method and the Division method.

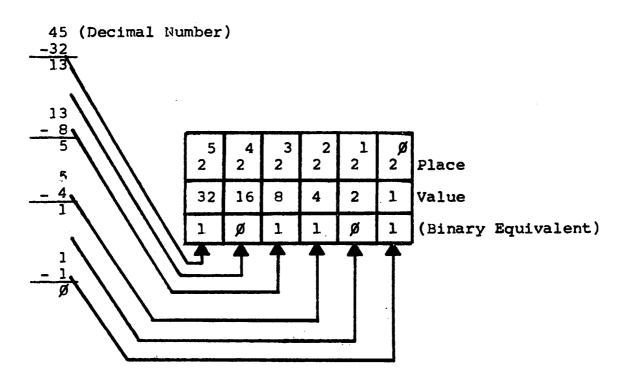

The procedure for the Subtraction of Powers method is as follows: (1) Subtract the highest possible power of two from the decimal number, and record a one in the apporpriate place within the partially completed binary equivalent, (2) Repeat this subtraction process with the resulting differences and descending powers of two (recording a one if that power can be subtracted, recording a zero if it cannot be subtracted) until the decimal number is reduced to zero. An example of this method is presented in Table 2-15.

а

Table 2-15 Subtraction of Powers Decimal to Binary Conversion

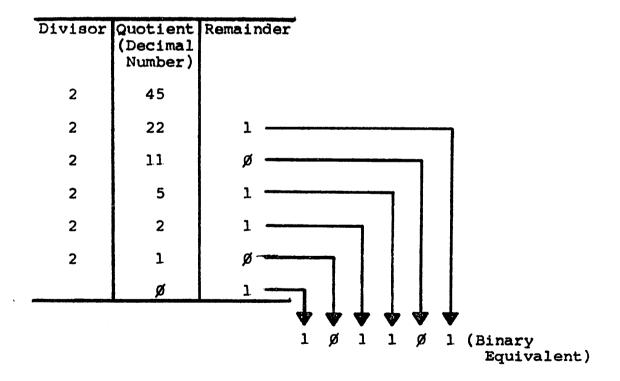

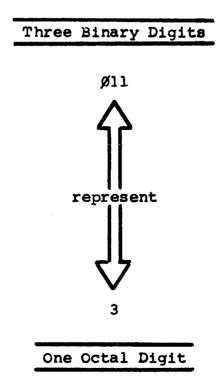

The procedure for the Division method of decimal to binary conversion is as follows: (1) Divide the decimal number by two; the remainder is the LSD (Least Significant Digit) of the binary equivalent, (2) Repeat this division process with the resulting quotients (recording remainders right to left within the binary equivalent) until the quotient becomes zero. An example of this method is presented in Table 2-16.

Ġ

Ê,

### 2.3.4 Octal to Decimal Conversion

There are two commonly used methods for converting octal numbers to decimal equivalents: the Place Value method, and a method similar in principle and procedure to the Double Dabble method for binary to decimal conversion.

æ

The Place Value method is simply the procedure used in representing an octal number as the sum of powers. The discrete value of each digit is multiplied by the value of the position in which it is placed, and the resulting products are added. An example of this method is presented in Table 2-17.

Table 2-17 Place Value Octal to Decimal Conversion

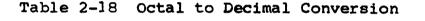

The octal to decimal conversion method that is similar to the Double Dabble method also begins with the MSD (Most Significant Digit). The procedure is as follows: (1) Record the MSD, (2) Multiply the MSD by eight, (3) Add the next octal digit, (4) Repeat steps two and three until the last digit of the octal number has been added. An example of this method is presented in Table 2-18.

### 2.3.5 Decimal to Octal Conversion

There are two commonly used methods for converting decimal numbers to octal equivalents: the Subtraction of Powers method and the Division method.

Using the Subtraction of Powers method for decimal to binary conversion simply required subtracting powers of two from the decimal number. The additional digits of the octal system create the need for more work when using this method for decimal to octal conversion. We may subtract not only a power of eight, but up to <u>seven times</u> that power of eight from the decimal number. The procedure is then as follows: (1) Subtract the highest possible value of the form <u>a8</u> (where  $\underline{a} = \emptyset$ -7) from the decimal number, and record the value of  $\underline{a}$  in the appropriate place within the partially completed octal equivalent, (2) Repeat this subtraction process with the resulting differences and descending powers of eight (recording the value of  $\underline{a}$ ) until the decimal number is zero. An example of this method is presented in Table 2-19.

Table 2-19 Subtraction of Powers Decimal to Octal Conversion

3267 (Decimal Number)

63Ø3 (Octal Equivalent)

| <u>-3ø72</u><br>195 | = | 6x512 | = | 3<br>6x8 |  |

|---------------------|---|-------|---|----------|--|

| <u>- 192</u>        | = | 3x64  | = | 2<br>3x8 |  |

| Ø                   | = | Øx8   | = | 1<br>Øx8 |  |

| <u>- 3</u>          | = | 3x1   | = | ø<br>3x8 |  |

The procedure for the Division method of decimal to octal conversion is as follows: (1) Divide the decimal number by eight; the remainder is the LSD (Least Significant Digit) of the octal equivalent, (2) Repeat this division process with the resulting quotients (recording remainders right to left within the octal equivalent) until the quotient becomes zero. An example of this method is presented in Table 2-2 $\emptyset$ .

Table 2-2Ø Division Method Decimal to Octal Conversion

| Divisor | Quotient<br>(Decimal<br>Number) | Remainder                                                                                                             |

|---------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| 8       | 3267                            |                                                                                                                       |

| 8       | 4ø8                             | 3                                                                                                                     |

| 8       | 51.                             | ø                                                                                                                     |

| 8       | 6                               | 3 ———                                                                                                                 |

|         | ø                               | 6                                                                                                                     |

|         |                                 | $ \begin{array}{cccc} \bullet & \bullet & \bullet & \bullet \\ 6 & 3 & \emptyset & 3 (Octal Equivalent) \end{array} $ |

ŝ

# 2.3.6 Binary to Octal to Binary Conversion

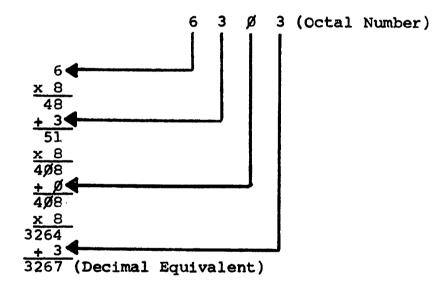

As the numerical language of the machine language and assembly language programmer, the octal number system serves as a convenient "shorthand" notation for the binary number system, numerical language of the computer. The unwieldy strings of binary ones and zeros are converted to the more workable octal notation by inspection, with no calculation required, because eight is an integral power of two (8=2). As illustrated by Figure 2-4, three binary digits are the direct equivalent of one octal digit; one octal digit is the direct equivalent of three binary digits.

Figure 2-4 Binary to Octal to Binary Conversion

Knowing the binary and octal equivalents (Table 2-21), we can then represent any binary number as an octal number by means of the following steps: (1) Beginning with the LSD of the binary number, group the bits by threes (filling in leading zeros if necessary), (2) Convert these three bit groupings to their octal equivalents. An example of this procedure is given below:

111,010,110, ø 1 1 1 7 2 6 3 5

Table 2-21 Binary and Octal Equivalents

| Binary | Octal |

|--------|-------|

| øøø    | ø     |

| øø1.   | 1     |

| Ølø    | 2     |

| Ø11    | 3     |

| 1øø    | 4     |

| 1ø1    | 5     |

| 11ø    | 6     |

| 111    | 7     |

2

As noted earlier, existing programs are available for all conversion processes, but there may be several occasions when you will need to make the binary to octal and octal to binary conversion directly:

8

13

# (1) Interpreting reference texts and instruction lists

Texts will often call upon the reader to make these conversions when describing the computer, illustrating the contents of various registers, and explaining instruction formats.

# (2) Manually loading and verifying programs

While the machine language programmer must always do this, it should be noted that even the most advanced computer systems usually have short preparatory programs that must be so entered and/or checked.

## (3) Avoiding binary notation

You may be involved in situations where you must work directly with numbers. If any of the notation is binary, convert to octal, operate, and if necessary convert the results back to binary.

#### 2.4 ARITHMETIC OPERATIONS

### 2.4.1 Introduction

No matter how complex the arithmetic problem, it is eventually reduced to one of the four fundamental operations: Addition, subtraction, multiplication, division (Figure 2-5).

Figure 2-5 Four Fundamental Arithmetic Operations

As with the programs available to handle any conversion process, there exist several arithmetic "packages" that the computer user may call upon to perform his calculations. It is important to keep in mind, however, that any of these packages is a program comprised of instructions which are essentially the four fundamental operations. It is the program which "breaks down" the complex problem; the computer receives only the simplest of instructions. Many computers, including the PDP-11, reduce the four fundamental arithmetic operations to one; addition. For reasons of hardware simplicity and efficiency, <u>comple-</u> mentary (negative) addition is performed rather than direct subtraction. Though we will later examine other methods (rotating and shifting) when we later discuss the PDP-11 instruction set, multiplication can be accomplished by means of repeated addition; division by means of repeated complementary addition (subtraction).

U.

We will therefore limit our discussion of arithmetic operations to the following topics: Addition, complementary addition, and (for comparision) direct subtraction. Examples in the decimal, binary, and octal number systems will be given for each operation.

### 2.4.2 Addition

Our discussions on the count and carry principle of positional number systems have also provided the steps required to perform decimal, binary, or octal addition. To review, the procedure is as follows: (1) Add the digits in the column, (2) If the base is neither equaled nor exceeded, record the sum; (3) If the base is equaled or exceeded, divide by the base, record the remainder, and carry the quotient to the next column.

This procedure works with any positional number system, and once the addition facts for the systems are learned (see Tables 2-22, 2-23, 2-24), binary or octal addition becomes as automatic as decimal addition.

An addition problem is solved below in the decimal, binary and octal systems. Note that when working with more than one number system, the base number is subscripted to differentiate.

1 1 1 1 1 1 111 1 1 1 carries:  $\emptyset \emptyset 1 1 1 \emptyset 1 1 1 (2)$ 1 1 8(]Ø) 1 6 7(8) +11111911(2)<u>+7 6 7(8)</u> <u>+5</u> ø  $\frac{2}{10}$  $1 \not g \not g 1 1 g 1 1 1 g_{(2)}$ 6  $1156_{(8)}$ 2  $\emptyset_{(10)}$

# Table 2-22 Binary Addition

| +  | ø | 1  |

|----|---|----|

| ø  | ø | 1  |

| 1. | 1 | 1ø |

3

**3**

Table 2-23 Octal Addition

| + | ø  | 1  | 2  | 3  | 4  | 5   | 6   | 7   |

|---|----|----|----|----|----|-----|-----|-----|

| ø | ø  | 1  | 2  | 3  | 4  | 5   | 6   | 7   |

| 1 | 1. | 2  | 3  | 4  | 5  | 6   | 7   | 1ø  |

| 2 | 2  | 3  | 4  | 5  | 6  | 7   | 1ø  | 11  |

| 3 | 3  | 4  | 5  | 6  | 7  | 1ø  | 11  | 12  |

| 4 | 4  | 5  | 6  | 7  | 1ø | 11  | 12  | 1.2 |

| 5 | 5  | 6  | 7  | 1ø | 11 | 12  | 13  | 14  |

| 6 | 6  | 7  | 1ø | 11 | 12 | 13  | 1.4 | 15  |

| 7 | 7  | 1ø | 11 | 12 | 13 | 1.4 | 15  | 16  |

Table 2-24 Decimal Addition

| + | ø | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9   |

|---|---|----|----|----|----|----|----|----|----|-----|

| ø | ø | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9   |

| 1 | 1 | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 1ø  |

| 2 | 2 | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 1ø | 11  |

| 3 | 3 | 4  | 5  | 6  | 7  | 8  | 9  | 1ø | 11 | 12  |

| 4 | 4 | 5  | 6  | 7  | 8  | 9  | 1ø | 11 | 12 | 1.3 |

| 5 | 5 | 6  | 7  | 8  | 9  | 1ø | 11 | 12 | 13 | 14  |

| 6 | 6 | 7  | 8  | 9  | 1ø | 11 | 12 | 13 | 14 | 15  |

| 7 | 7 | 8  | 9  | 1ø | 11 | 12 | 13 | 14 | 15 | 16  |

| 8 | 8 | 9  | 1ø | 11 | 12 | 13 | 14 | 15 | 16 | 17  |

| 9 | 9 | 1ø | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18  |

### 2.4.3 Direct Subtraction

The operation of direct subtraction is performed in the same manner for all positional number systems, regardless of the base. The procedure is as follows: (1) For each column, subtract the subtrahend from the minuend (if the subtrahend is greater than the minuend, "borrow" a power of the base from the next column and then subtract), (2) Record the difference.

As with addition, binary or octal subtraction should become as automatic for you as decimal subtraction. The only difference is the base, and you should keep this in mind; that when you "borrow," you borrow a power of <u>that</u> base. Reference the example problems below.

borrows:

$$\frac{3}{4} \frac{42}{7} \frac{4}{2} (10)$$

$$= \frac{2}{1} \frac{3}{9} \frac{4}{8} (10)$$

$$= \frac{2}{1} \frac{3}{9} \frac{4}{8} (10)$$

borrows:

$$\begin{array}{c} \phi & 1 \phi & 1 \\ \chi & \eta & 1 \end{array} \begin{array}{c} \phi & 1 & 1 \\ \chi & \eta & 1 \end{array} \begin{array}{c} \phi & 1 & 1 \\ \chi & \eta & 1 \end{array} \begin{array}{c} \phi & 1 & 1 \\ \chi & \eta & 1 \end{array} \begin{array}{c} \phi & 1 \\ \chi & \eta & 1 \end{array} \begin{array}{c} \phi & 1 \\ \chi & \eta & \eta \end{array} \begin{array}{c} \phi & 1 \\ \chi & \eta & \eta \end{array} \begin{array}{c} \phi & 1 \\ \chi & \eta & \eta \end{array} \begin{array}{c} \phi & 1 \\ \chi & \eta & \eta \end{array} \begin{array}{c} \phi & 1 \\ \chi & \eta & \eta \end{array} \begin{array}{c} \phi & 1 \\ \chi & \eta & \eta \end{array} \begin{array}{c} \phi & 1 \\ \chi & \eta \end{array}$$

borrows:

## 2.4.4 Complementary Addition

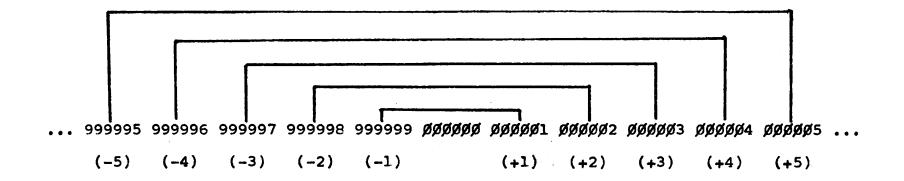

To understand complements, and thus the way in which negative numbers are commonly handled in the computer, consider again the odometer of the automobile. If the mileage indicator is rotated backwards, it will eventually approach and pass through zero, as shown below.

| ø | ø | ø | ø      | ø | 3 |

|---|---|---|--------|---|---|

| ø | ø | ø | ø      | ø | 2 |

| ø | ø | ø | ø      | ø | 1 |

| ø | ø | ø | ø      | ø | ø |

| 9 | 9 | 9 | 9      | 9 | 9 |

| 9 | 9 | 9 | 9      | 9 | 8 |

| 9 | 9 | 9 | 9      | 9 | 7 |

|   |   |   | ,<br>, |   |   |

Considering zero to be a "boundary," we see that the number 999998 corresponds to -2. Applying this relational concept to the operation of complementary addition, we add the numbers 5 and 999998.

|   |   | øøøøø5        |

|---|---|---------------|

|   | ± | 999998        |

| 1 |   | <i>øøøø</i> 3 |

If we ignore the last generated carry, we have effectively performed the operation of subtraction (5-2=3). The number 999998 in the above example is referred to as the <u>ten's complement</u> of 2. For the complementary addition operation, the term <u>radix complement</u> is defined as either of two numbers which when added will result in a sum or zero (last generated carry disregarded). This concept is illustrated by the example below and by Table 2-25. (It should be noted that the term radix complement can by definition apply to either a positive or negative number, but that it is most commonly used to describe the negative quantity.)

# 999998 + ØØØØØ2 L ØØØØØØ

We can thus do away with direct subtraction; instead of subtracting a positive number, we add the negative representation of that number. In using a system of complements, however, we omit the minus sign, and must therefore establish what is and what is not a negative number. For example, is 123456 a positive 123456 or a negative 8765447 With the odometer as an arbitrary example, we have the ability to represent one million numbers ( $\emptyset$  to 999999), and it would be reasonable to use half for positive and half for negative. Thus, by convention, we would regard  $\emptyset$  to 499999 as positive and  $5\emptyset\emptyset\emptyset\emptyset\emptyset$  to 999999 as negative. And this in fact is exactly what is done with the computer; with a finite range of binary numbers to represent, half are designated as positive and half as negative. Table 2-25 Radix Complements for the Decimal System

We have established the following points concerning the radix complement:

- (1) It is the negative representation of a positive number.

- (2) It is used because complementary notation can be efficiently and simply handled by the computer. All numbers can be treated alike (added) in arithmetic operations; complementary addition (add the negative) rather than subtraction (subtract the positive) can be performed.

- (3) Signs are not required. The computer works with a finite range of binary numbers, and a convention can be established such that the number itself designates whether it is positive or negative.

We will examine the radix complement, the radix minus one complement, and the complementary addition operation first with the familiar decimal system, and then with the languages of the computer (binary) and programmer (octal). The radix complement, which commonly takes the name of the base, is called the  $\underline{10's}$  complement in the decimal system. The procedure for radix (10's) complement addition is as follows: (1) Subtract the subtrahend from the next highest power of the base; the difference is the radix (10's) complement, (2) Add the radix (10's) complement to the minuend, (3) Record the sum, (4) Disregard the last generated carry (the next highest power of the base was introduced in step one and is "tossed out" here); this is the final result. Two examples are presented below.

| $ \begin{array}{c} 237 (1 \emptyset) \\ - 125 (1 \emptyset) \\ 112 (1 \emptyset) \end{array} $ | direct subtraction<br>(as a check)                                                                                        | <sup>84</sup> (1Ø)<br><u>- 59</u> (1Ø)<br><sup>25</sup> (1Ø) |

|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| 1ØØØ (1Ø)<br>- <u>125</u> (1Ø)<br>875 (1Ø)                                                     | subtract the subtrahend from<br>next highest power of the base<br>the difference is the radix<br>(1Ø's) complement        | <sup>1ØØ</sup> (1Ø)<br><u>- 59</u> (1Ø)<br>41 (1Ø)           |

| <sup>875</sup> (1ø)<br><u>+ 237</u> (1ø)<br>(1) 112(1ø)                                        | add the lø's complement to the<br>minuend and record the sum<br>disregard the last generated<br>carry; this is the result | 41 (10) + 84 (10) (1) 25 (10)                                |

The radix minus one complement in the decimal system is called the <u>9's complement</u>. The procedure for radix minus one (9's) complement addition is as follows: (1) Subtract the subtrahend from the next highest power of the base minus one; the difference is the radix minus one (9's) complement, (2) Add the radix minus one (9's) complement to the minuend, (3) Record the sum, (4) Bring the last generated carry around to the least significant digit position and add it to the sum; this is the final result. The same examples worked with the radix (10's) complement are repeated below using the radix minus one (9's) complement.

| 237(1ø)<br><u>- 125</u> (1ø)<br>112(1ø) | (as a check)                                                                                                                             | 84 (1¢)<br><u>- 59</u> (1ø)<br>25 (1ø)                                                                  |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| $-\frac{125}{10}(10)$                   | subtract the subtrahend from<br>next highest power of the base<br>minus one<br>the difference is the radix<br>minus one (9's) complement | 99(1ø)<br><u>- 59</u> (1ø)<br>4ø(1ø)                                                                    |

| + 237(10)                               | bring the last generated carry<br>around to the LSD position and<br>add it to the sum;<br>this is the result                             | $4\emptyset(1\emptyset) \\ + 84(1\emptyset) \\ (1) 24(1\emptyset) \\ + 1(1\emptyset) \\ 25(1\emptyset)$ |

The radix complement in the binary (base 2) number system is called the <u>2's complement</u>. But before we take up the subject of 2's complement addition, let's relate our previous discussion to the PDP-11 and the binary number system.

8

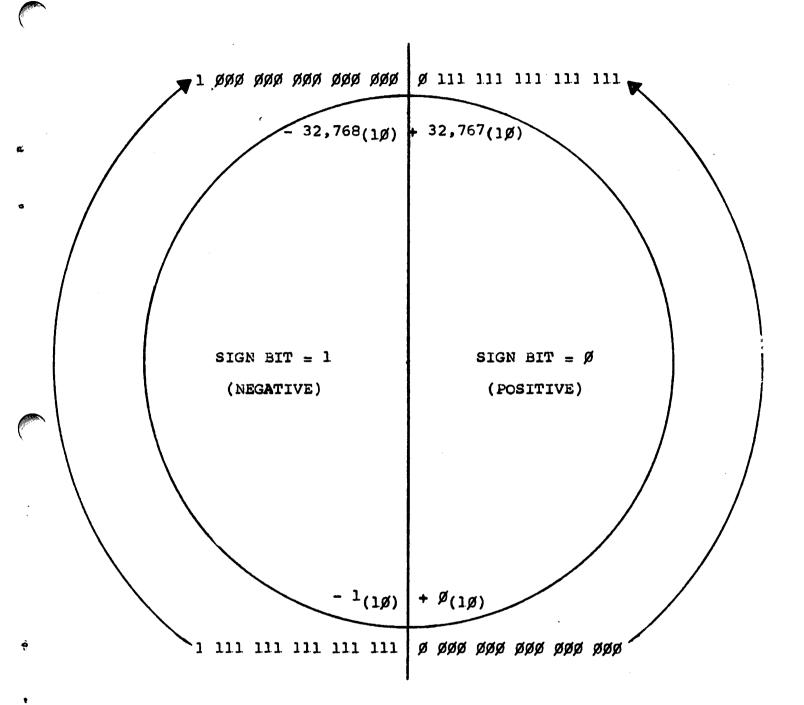

The PDP-11 is a <u>variable word length</u> machine, capable of handling both 16 bit words and 8 bit bytes. For the purpose of our discussion, let us consider it to be like many other computers, a <u>fixed word length</u> machine. This means that all data processed by the computer will be in the form of words (binary numbers) of the same length. It should be noted that from the programmer's standpoint words may be in varied formats and lengths; we are here veiwing words as the computer will ultimately receive them - in the form of fixed length binary numbers.

Viewing the PDP-11 as a 16 bit fixed word length machine, it has a binary number range of

Ø ØØØ ØØØ ØØØ ØØØ ØØØ<sub>(2)</sub> to 1 111 111 111 111 111<sub>(2)</sub>.

|    |  |  | • |  |  | <br> | 3 | <br> |  |

|----|--|--|---|--|--|------|---|------|--|

| SB |  |  |   |  |  |      |   |      |  |

By convention, half of these numbers are designated as positive ( $\emptyset \ \emptyset \emptyset \emptyset \ - \emptyset \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111 \ 111$

Now that we know the application, let's look at the operation. The procedure for radix (2's) complement addition is as follows: (1) Subtract the subtrahend from the next highest power of the base; the difference is the radix (2's) complement, (2) Add the radix (2's) complement to the minuend, (3) Record the sum, (4) Disregard the last generated carry (the next highest power of the base was introduced in step one and is "tossed out" here); this is the final result. An example is given below.

| Ø ØØØ Ø11 1ØØ 11Ø ØØ1 <sub>(2)</sub><br><u>– Ø ØØØ Ø1Ø ØØØ 1ØØ 1Ø1</u> (2)<br>Ø ØØØ ØØ1 1ØØ ØØ1 1ØØ <sub>(2)</sub>    | direct subtraction<br>(as a check)                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| 10 ØØØ ØØØ ØØØ ØØØ ØØØ <sub>(2)</sub><br>- <u>Ø ØØØ Ø1Ø ØØØ 1ØØ 1Ø1</u> (2)<br>1 111 1Ø1 111 Ø11 Ø11 <sub>(2)</sub>   | subtract the subtrahend from<br>next highest power of the base<br>the difference is the radix<br>(2's) complement        |

| 1 111 1ø1 111 ø11 ø11 <sub>(2)</sub><br><u>+ ø øøø ø11 1øø 11ø øø1(2)</u><br>(1) ø øøø øø1 1øø øø1 1øø <sub>(2)</sub> | add the 2's complement to the<br>minuend and record the sum<br>disregard the last generated<br>carry; this is the result |

The radix minus one complement in the binary system is called the <u>l's complement</u>. The procedure for radix minus one (l's) complement addition is as follows: (l) Subtract the subtrahend from the next highest power of the base minus one; the difference is the radix minus one (l's) complement, (2) Add the radix minus one (l's) complement to the minuend, (3) Record the sum, (4) Bring the last generated carry around to the least significant digit position and add it to the sum; this is the final result. The example worked with the radix (2's) complement is repeated below using the radix minus one (l's) complement.

a

| Ø ØØØ Ø11 1ØØ 11Ø ØØ1 (2)<br>- <u>Ø ØØØ Ø1Ø ØØØ 1ØØ 1Ø1</u> (2)<br>Ø ØØØ ØØ1 1ØØ ØØ1 1ØØ (2)                                      | direct subtraction<br>(as a check)                                                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 111 111 111 111 111 (2)<br><u>- Ø ØØØ Ø1Ø ØØØ 1ØØ 1Ø1</u> (2)<br>1 111 1Ø1 111 Ø11 Ø1Ø (2)                                      | subtract the subtrahend from<br>next highest power of the base<br>minus one<br>the difference is the radix<br>minus one (1's) complement                                    |

| 1 111 1Ø1 111 Ø11 Ø1Ø (2)<br>+ Ø ØØØ Ø11 1ØØ 11Ø ØØ1 (2)<br>(1) Ø ØØØ ØØ1 1ØØ ØØ1 Ø11 (2)<br>+ 1 (2)<br>Ø ØØØ ØØ1 1ØØ ØØ1 1ØØ (2) | add the l's complement to the<br>minuend and record the sum<br>bring the last generated carry<br>around to the LSD position and<br>add it to the sum;<br>this is the result |

Have you noticed something unsettling about our complementary addition processes? The reason given for the use of complementary addition was that direct subtraction could not be performed with the PDP-11, and yet direct subtraction was used in all previous cases to obtain the complements! Let's see how the computer gets around this.

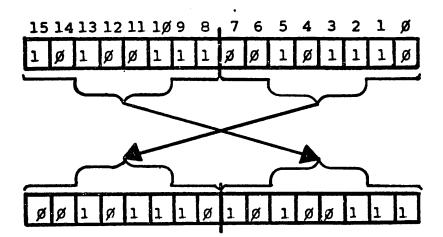

Note below that the <u>bit patterns for any binary number</u> and its 1's complement are exact opposites, and that the <u>2's complement is equal to the 1's complement plus 1</u>.

ø øøl ølø øll løø løl (binary number)

8

- ø øøi øiø øii iøø iøi

1 11Ø 1Ø1 1ØØ Ø11 Ø1Ø 1 11Ø 1Ø1 1ØØ Ø11 Ø1Ø (1's complement)

19 999 999 999 999 999

- Ø ØØI ØIØ ØII 1ØØ 1ØI

1 11ø 1ø1 1øø ø11 ø11 1 11ø 1ø1 1øø ø11 ø11 (2's complement)

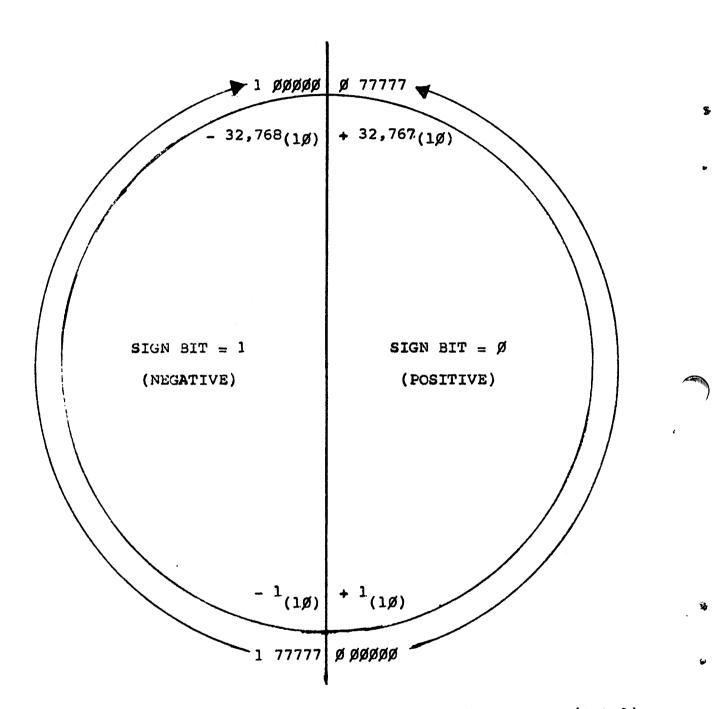

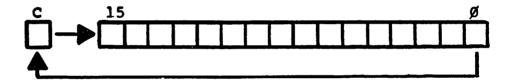

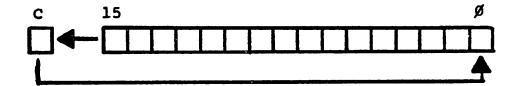

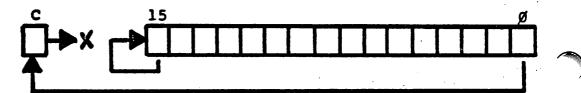

The PDP-11 performs 2's complement addition, and therefore all negative numbers must be represented in 2's complement form. The PDP-11 2's complements any binary number without direct subtraction; it obtains the 1's complement by simply changing all bits to their opposites and then adds 1. In the octal (base 8) number system, the radix complement is called the <u>8's complement</u> and the radix minus one complement is called the <u>7's complement</u>. Here too, the octal system serves the programmer as shorthand notation for the binary system; the 1's complement is to the 7's complement as the 2's complement is to the 8's complement. Again it should be stressed that the programmer rarely works in the binary number system; that any numerical work he must perform is done in the octal system and only if necessary converted to binary. If the 2's complement is required, for example, the programmer obtains the 8's complement (or the 7's complement plus 1) and then converts to binary.

2

Using the direct conversion that exists between the binary and octal number systems, the 16 bit FDP-11 word may be represented by 6 octal digits.