# TA79, TU79, TA78, TU78 Magnetic Tape Subsystem

**Technical Manual**

# TA79, TU79, TA78, TU78 Magnetic Tape Subsystem

**Technical Manual**

Prepared by Educational Services of Digital Equipment Corporation 1st Edition, March 1988

Digital Equipment Corporation 1988.

All Rights Reserved.

Printed in U.S.A.

The reproduction of this material, in part or whole, is strictly prohibited. For copy information, contact the Educational Services Department, Digital Equipment Corporation, Maynard, Massachusetts 01754.

The information in this document is subject to change without notice. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

LEGAL NOTICE: TMSCP and STI protocols and documentation are the proprietary information of Digital Equipment Corporation. UNIBUS/Q-BUS/ BI-BUS port drivers and documentation for MSCP/TMSCP products are also proprietary information of Digital Equipment Corporation.

FCC NOTICE: This equipment generates, uses, and may emit radio frequency energy. The equipment has been type tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such radio frequency interference when operated in a commercial environment. Operation of this equipment in a residential area may cause interference in which case the user at his own expense may be required to take measures to correct the interference.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts.

| digital   | MASSBUS      | Rainbow | VAXstation     |

|-----------|--------------|---------|----------------|

| DEC       | PDP          | RSTS    | VAX station II |

| DECmate   | P/OS         | RSX     | VMS            |

| DECUS     | Professional | RT      | VT             |

| DECwriter | Q-Bus        | UNIBUS  | Work Processor |

| DIBOL     | Q22-Bus      | VAX     |                |

Mate-N-Lok is a trademark of AMP, Inc.

# Contents

| CHAPTER 1 — GENERAL DESCRIPTION                                  |     |

|------------------------------------------------------------------|-----|

| 1.1 INTRODUCTION.                                                | 1-1 |

| 1.2 SPECIFICATIONS.                                              | 1-1 |

| 1.3 RELATED DOCUMENTS                                            | 1-4 |

| 1.4 TAPE FORMATS                                                 | 1-4 |

| 1.4.1 PE Format (1600 bits/in)                                   | 1-6 |

| 1.4.2 GCR Format (6250 bits/in)                                  | 1-9 |

| 1.5 SYSTEM-LEVEL DESCRIPTION 1                                   | -19 |

| 1.5.1 Formatter Functional Components                            | -19 |

| 1.5.2 Formatter System Microcomputer Function and Architecture 1 | -21 |

| 1.5.2.1 Microcomputer Function                                   | -21 |

| 1.5.2.2 Microcomputer Architecture                               | -22 |

| 1.5.3 Operational Microcode Firmware                             | -23 |

| 1.5.3.1 Microcode Overview                                       | -23 |

| 1.5.3.2 Polled Versus Interrupt-Driven Functions                 | -25 |

| 1.5.4 Formatter System Reliability/Integrity                     | -26 |

| 1.5.5 Formatter Internal Communication                           | -26 |

| 1.5.6 Interface-Level Description                                | 28  |

| 1.5.6.1 Subsystem Command Execution                              | -28 |

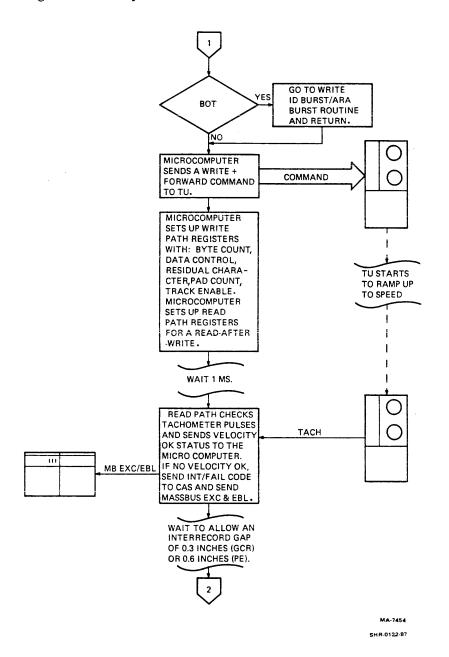

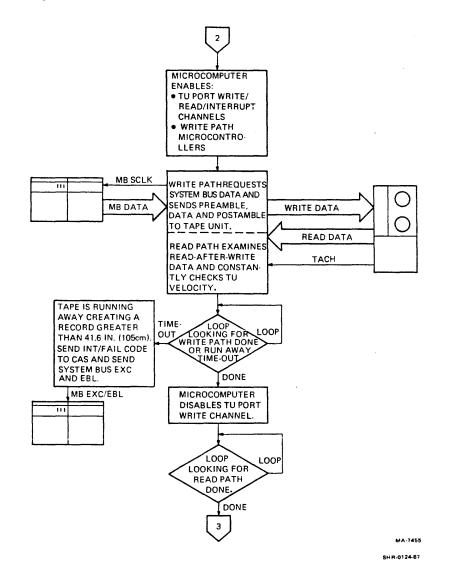

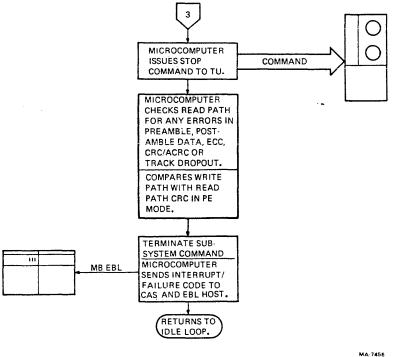

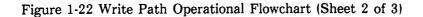

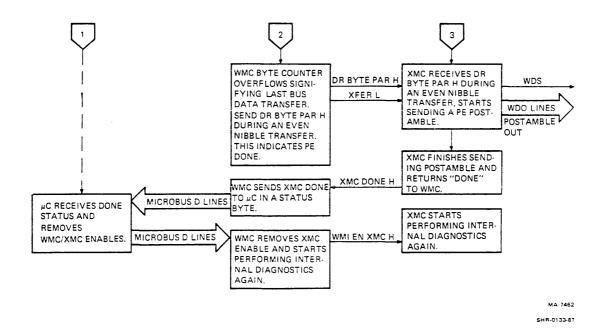

| 1.5.6.2 Write Path Description                                   | -36 |

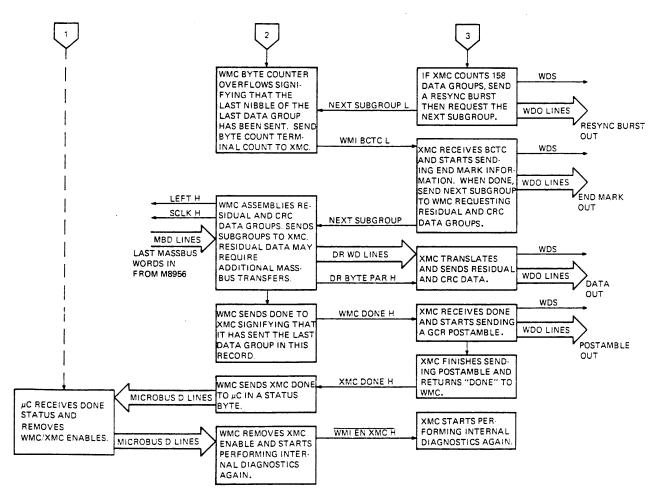

| 1.5.6.3 Read Path Description                                    | -45 |

| 1.6 UNIT-LEVEL DESCRIPTION                                       | -50 |

| 1.6.1 Tape Unit Bus Description                                  | -50 |

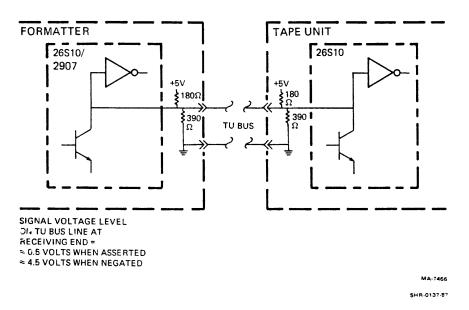

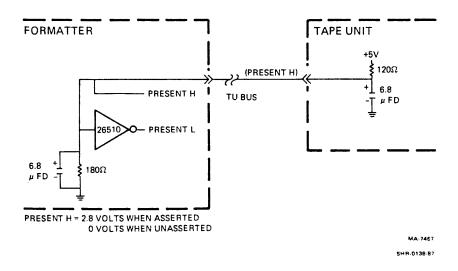

| 1.6.1.1 Electrical Characteristics                               | 52  |

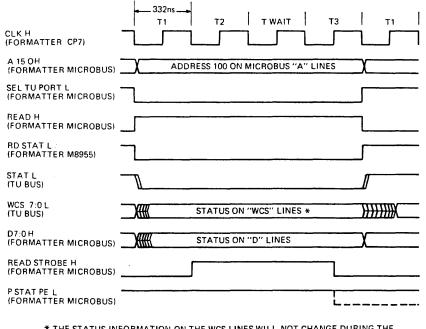

| 1.6.1.2 Timing                                                   | 53  |

| CHAPTER 2 — FORMATTER TECHNICAL DESCRIPTION                      |     |

| 2.1 INTRODUCTION                                                 | 2-1 |

|                                                                  |     |

| 2.2 FUNCTIONAL DESCRIPTION               | 2-1  |

|------------------------------------------|------|

| 2.3 STI BUS INTERFACE                    | 2-9  |

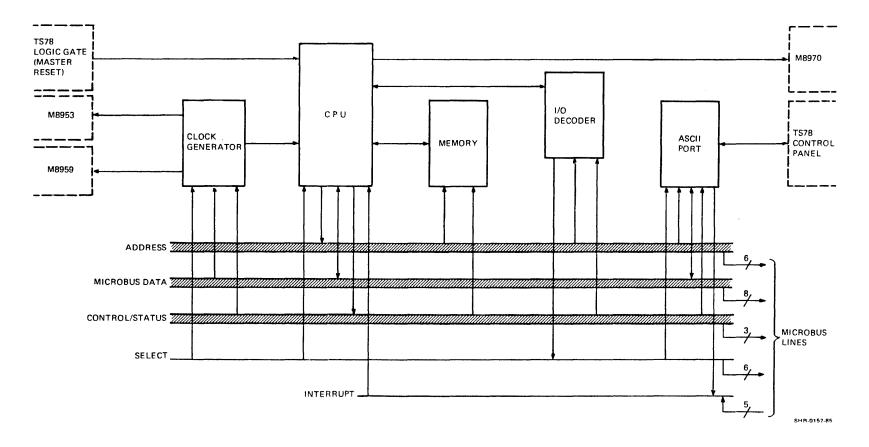

| 2.3.1 M8972 Microcomputer                | 2-9  |

| 2.3.2 M8970 STI Protocol Microcontroller | 2-24 |

| 2.3.3 M8971 STI Interface                | !-50 |

| 2.3.4 M8973 Extended Memory              | ?-58 |

| 2.4 | 4 MASSBUS INTERFACE                          |

|-----|----------------------------------------------|

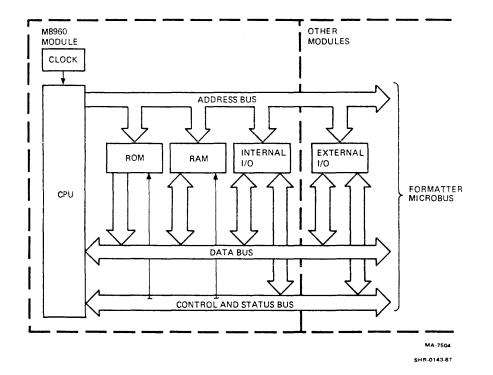

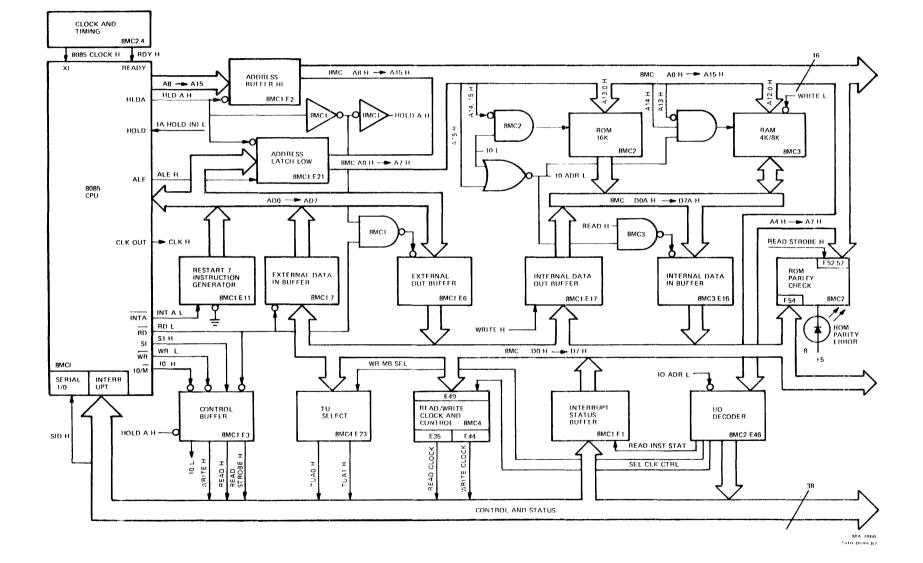

|     | 2.4.1 M8960 Microcomputer (8MC)              |

|     | 2.4.2 M8957 Common Address Space Module      |

|     | 2.4.3 M8956 Massbus Data Module (MBD)        |

| 2.5 | 5 FORMATTER                                  |

|     | 2.5.1 M8950 Read Channel (RC)                |

|     | 2.5.2 M8951 Error Correcting Code            |

|     | 2.5.3 M8952 Cyclic Redundancy Checker (CRC)  |

|     | 2.5.4 M8953 Read Path Controller Module (RP) |

|     | 2.5.5 M8955 Tape Unit Port (TUP)             |

|     | 2.5.6 M8958 Translator (XMC)                 |

|     | 2.5.7 M8959 Write Microcontroller (WMC)      |

| 2.6 | <b>5 FORMATTER POWER SUPPLY SYSTEM</b>       |

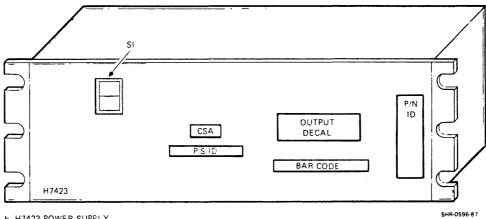

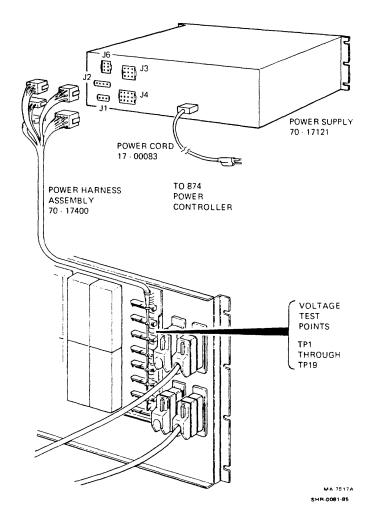

|     | 2.6.1 Mechanical Description                 |

|     | 2.6.2 Output Power Specifications            |

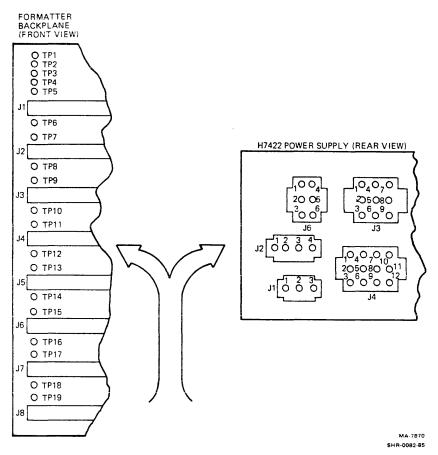

|     | 2.6.3 Power/Signal Distribution              |

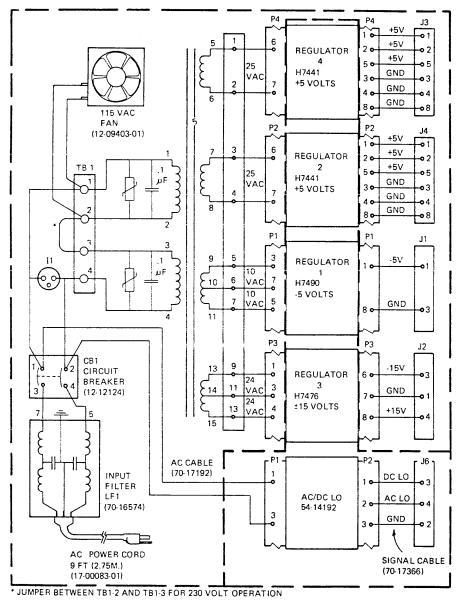

|     | 2.6.4 Power Supply Functional Description    |

|     | 2.6.4.1 H7423 Power Supply                   |

|     | 2.6.4.2 H7422 Power Supply Chassis           |

|     | 2.6.4.3 H7490 Regulator Assembly             |

|     | 2.6.4.4 54-14192 AC/DC LO Module             |

|     | 2.6.5 54-14174 Maintenance Panel             |

|     |                                              |

# CHAPTER 3 - TAPE DRIVE, THEORY OF OPERATION

| 3.1 GENERAL                                  | -1 |

|----------------------------------------------|----|

| 3.2 FUNCTIONAL DESCRIPTION                   | -1 |

| 3.2.1 Capstan Servo Subsystem                | •1 |

| 3.2.2 Reel Servo Subsystems                  | -3 |

| 3.2.3 Pneumatic Subsystem                    | -3 |

| 3.2.4 Read/Write Subsystem                   | -4 |

| 3.2.5 Control Logic and Manual Controls      | -4 |

| 3.2.6 MIA Interface                          | -4 |

| 3.2.7 Power Supply and Distribution 3-       | -4 |

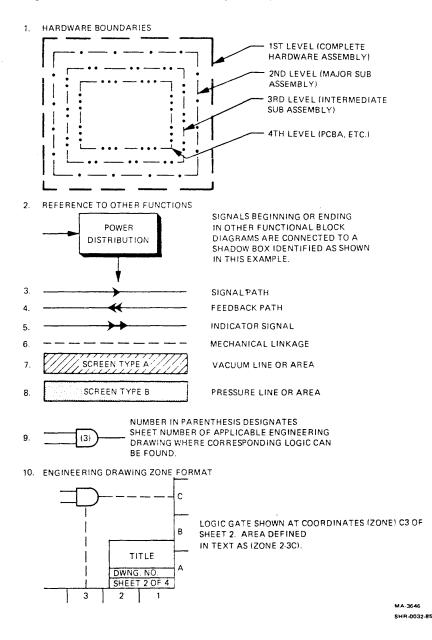

| 3.3 THEORY OF OPERATION SYMBOLOGY 3-         | -5 |

| 3.3.1 Functional Block Diagram Symbology 3-  | -5 |

| 3.3.2 Schematic Diagram Symbology            | -6 |

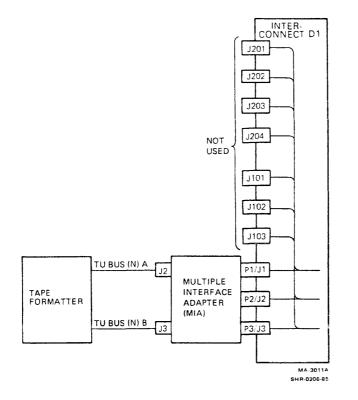

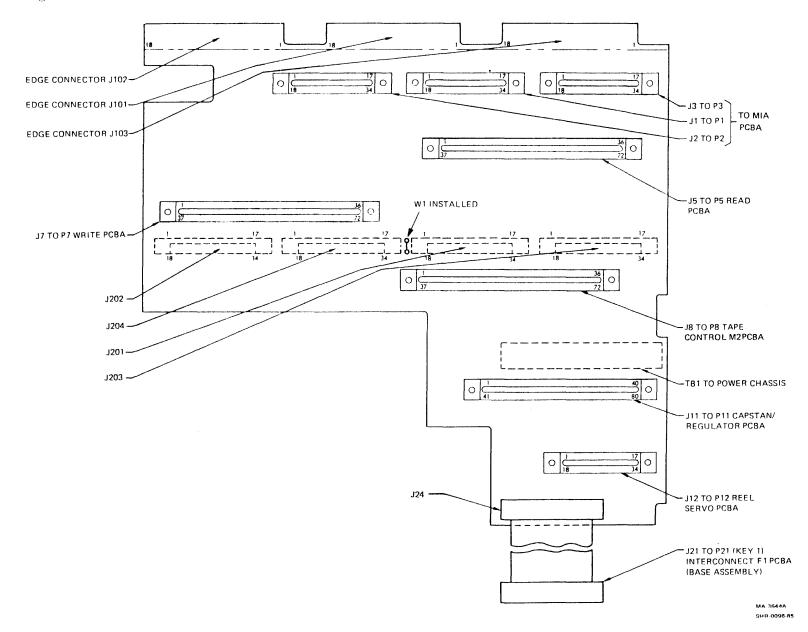

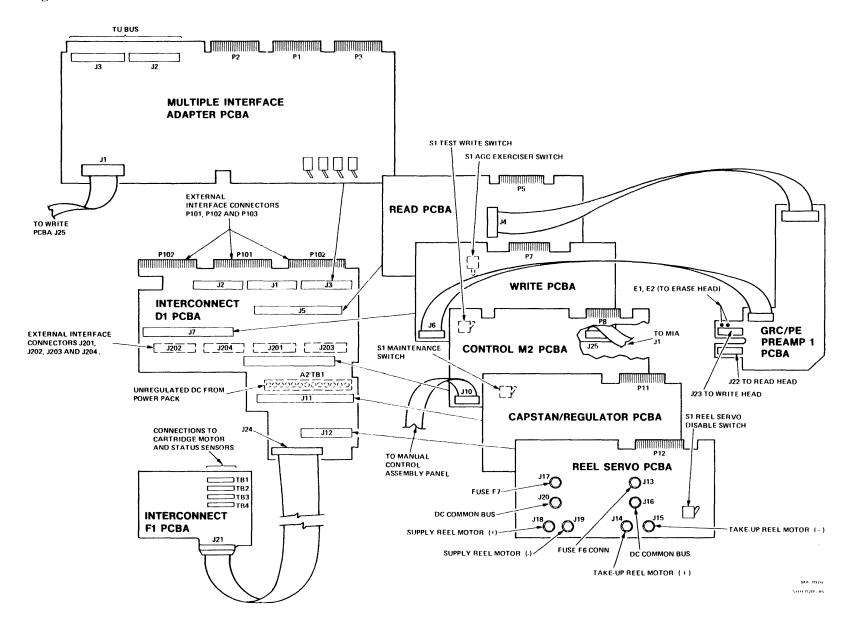

| 3.4 CABLING/INTERCONNECTIONS                 | -7 |

| 3.4.1 Input/Output Cabling and Connectors    | -7 |

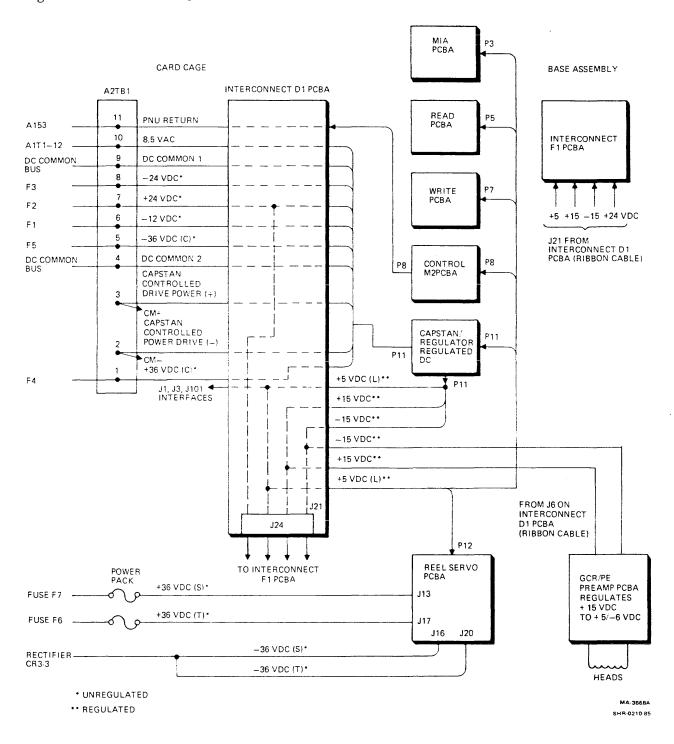

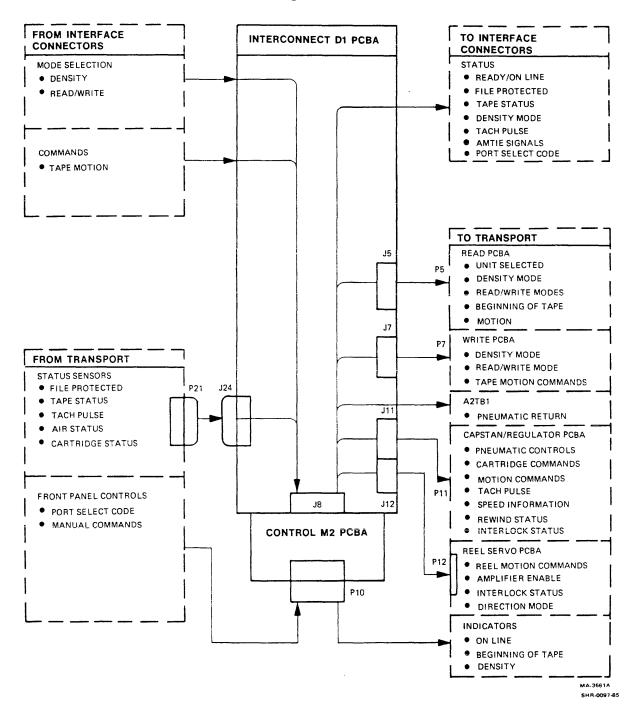

| 3.4.2 Interconnect D1 PCBA                   | -9 |

| 3.4.3 Interconnect F1 PCBA 3-                | -9 |

| 3.4.4 Internal Interconnections              | -9 |

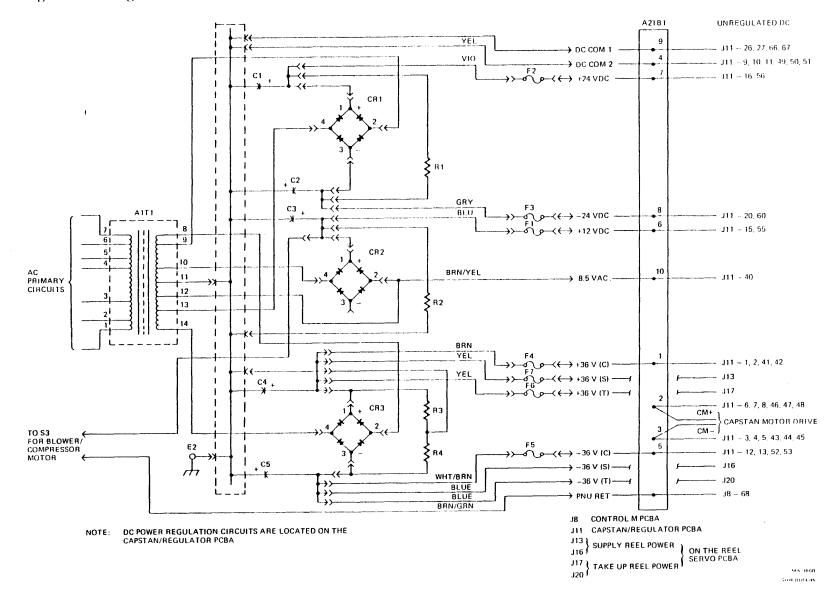

| 3.5 POWER SUPPLY AND DISTRIBUTION            | -9 |

| 3.5.1 Primary Power Connections and Controls | 2  |

| 3.5.2 Blower/Compressor Motor Power          | 12 |

| 3.5.3 AC Power                               | 12 |

| 3.5.4 Unregulated DC Power Supplies          | 15 |

|                                              |    |

| 3.5.5 DC Power Regulation                                     | . 3-15 |

|---------------------------------------------------------------|--------|

| 3.5.5.1 + 5 Vdc Regulator                                     |        |

| 3.5.5.2 15 Vdc                                                |        |

| 3.5.5.3 +5/6 Vdc                                              |        |

| 3.5.5.4 +/                                                    |        |

| 3.5.5.5 +/                                                    |        |

| 3.5.5.6 + -36 Vdc (T)                                         |        |

| 3.5.6 Regulated Power Distribution                            |        |

| 3.5.7 Power Reset (NPORST), Enable (ENBL, NENBLE), and Master | . 0-10 |

| Reset Pulse (NMRSTP) Generation                               | 2 10   |

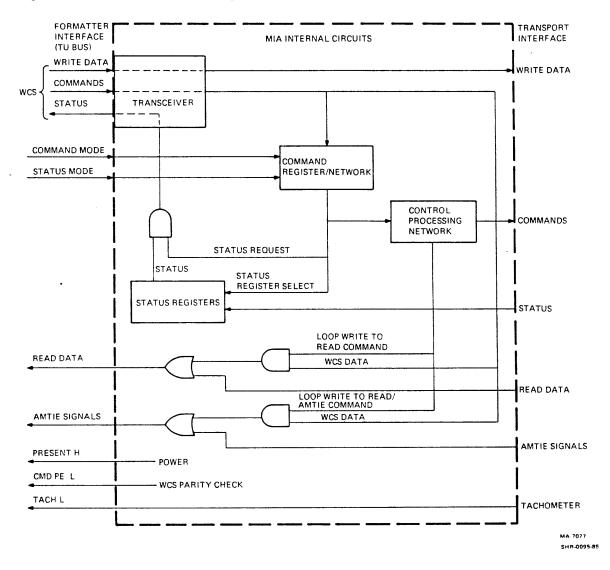

| 3.6 INTERFACING AND THE MULTIPLE INTERFACE ADAPTER (MIA)      |        |

| PCBA                                                          |        |

|                                                               |        |

| 3.6.1 General.                                                |        |

| 3.6.2 Physical Description                                    |        |

| 3.6.3 Interface Connections                                   |        |

| 3.6.3.1 Formatter to MIA Interface (TU Bus) Signals           |        |

| 3.6.3.2 Transport to MIA Interface Signals                    |        |

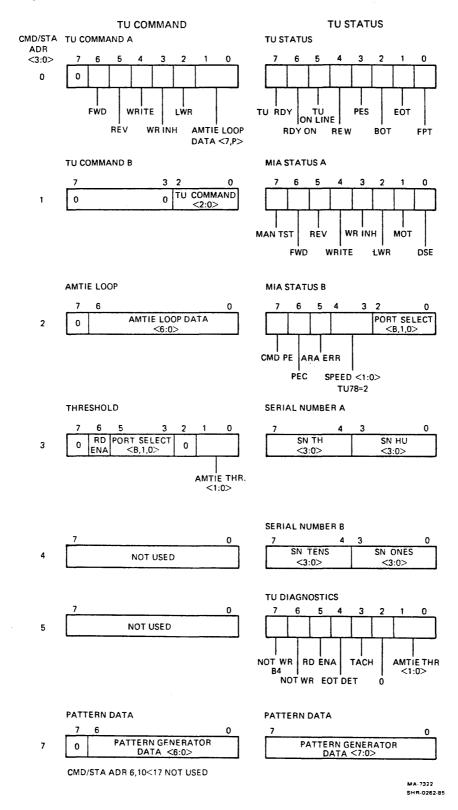

| 3.6.4 Command/Status Register Descriptions                    | . 3-26 |

| 3.6.5 Circuit Description                                     |        |

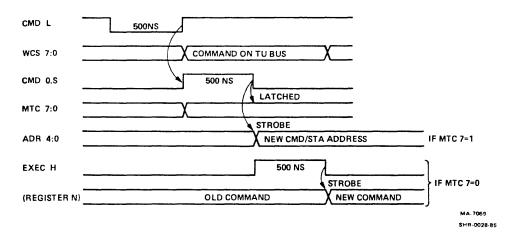

| 3.6.5.1 Commands and Command Timing                           | . 3-28 |

| 3.6.5.2 Status                                                | . 3-29 |

| 3.6.5.3 Write Data                                            | . 3-30 |

| 3.6.5.4 Read Data                                             | . 3-30 |

| 3.6.5.5 Amplitude Track in Error (AMTIE) Bits                 | . 3-30 |

| 3.6.5.6 Diagnostic Loops                                      |        |

| 3.6.5.7 Switches and Indicators                               |        |

| 3.6.5.8 Test Pattern Generation                               |        |

| 3.7 SYSTEM CONTROL.                                           |        |

| 3.7.1 Control System Overview.                                |        |

| 3.7.2 Manual Controls                                         |        |

| 3.7.3 LED Status Indicators.                                  |        |

| 3.7.4 Control System Inputs/Outputs                           |        |

| 3.7.5 General Modes of Operation                              |        |

| 3.7.6 Control M2 PCBA                                         |        |

| 3.7.6.1 Control System Timing.                                |        |

| 3.7.6.2 Normal/Test Mode Selection.                           |        |

| 3.7.6.3 Modes of Operation                                    |        |

| •                                                             |        |

| 3.7.6.4 Reset/Preset State.                                   |        |

| 3.7.6.5 Interlock State.                                      |        |

| 3.8 AIR LOAD/CONTROL.                                         |        |

| 3.9 TAPE LOAD, UNLOAD, AND REWIND OPERATION.                  |        |

| 3.9.1 Load/Unload Sequences                                   |        |

| 3.9.1.1 Tape Load                                             |        |

| 3.9.1.2 Tape Unload                                           |        |

| 3.9.2 Load/Unload/Rewind Circuit Operation                    |        |

| 3.10 REEL SERVOS                                              |        |

| <b>3.10.1 Reel Servo Overview</b>                             |        |

| 3.11 CAPSTAN SERVO                                            | . 3-49 |

| 3.12 DATA PATHS                                    | 3-52 |

|----------------------------------------------------|------|

| 3.12.1 Introduction                                | 3-52 |

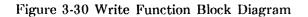

| 3.12.2 Write Function                              | 3-54 |

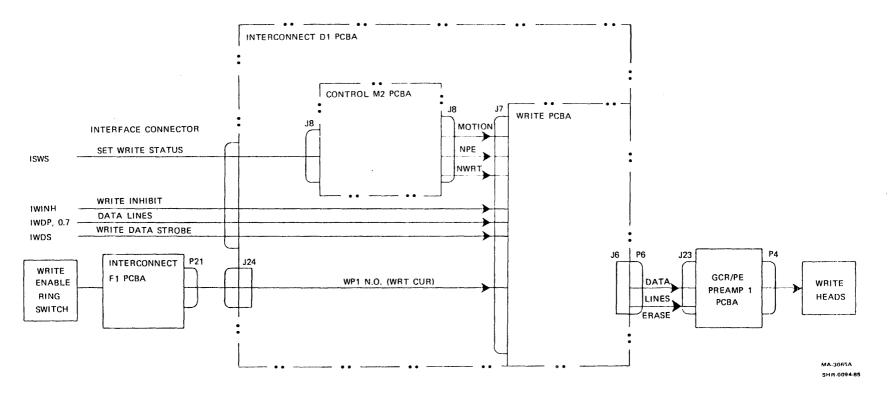

| 3.12.3 Read Function                               | 3-56 |

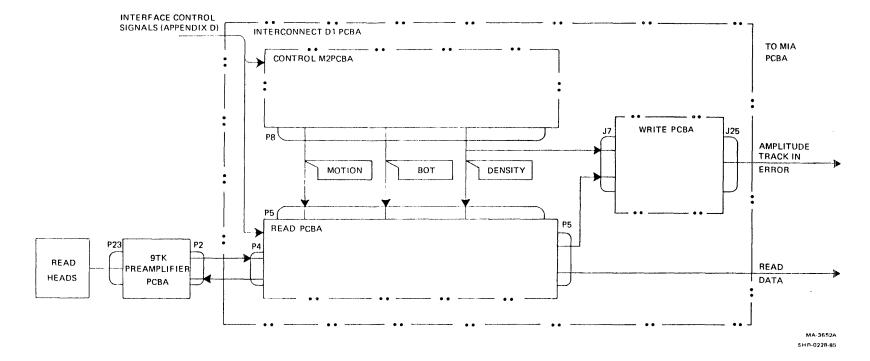

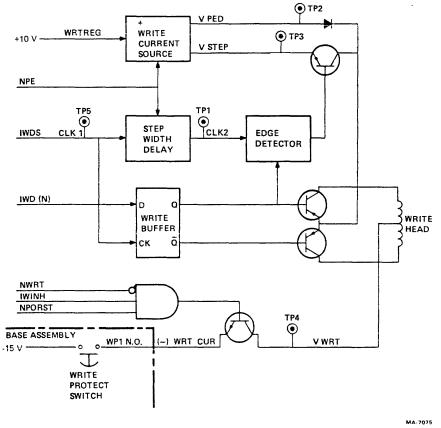

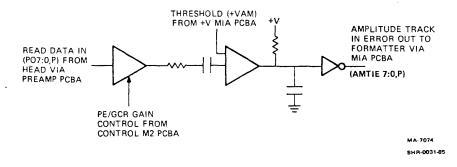

| 3.12.4 Write PCBA                                  | 3-56 |

| 3.12.4.1 Write Circuitry                           | 3-60 |

| 3.12.4.2 Amplitude Track In Error (AMTIE) Circuits | 3-60 |

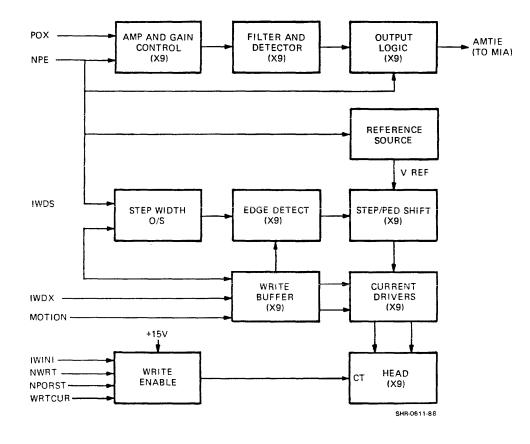

| 3.12.5 Redesigned Write PCBA                       | 3-62 |

| 3.12.5.1 Interconnections                          | 3-62 |

| 3.12.5.2 Control Inputs                            | 3-64 |

| 3.12.5.3 Input Data                                | 3-64 |

| 3.12.5.4 Reference Voltage                         | 3-64 |

| 3.12.5.5 Step-Pedestal Generation                  | 3-65 |

| 3.12.5.6 Current Source/Head Driver                | 3-65 |

| 3.12.5.7 Erase Circuit                             | 3-66 |

| 3.12.5.8 AMTIE Circuits                            | 3-66 |

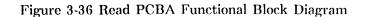

| 3.12.6 Read PCBA                                   | 3-67 |

### APPENDIX A — GLOSSARY OF TERMS AND MNEMONICS

| A.1 GENERAL NOTES |  | A-1 |

|-------------------|--|-----|

|-------------------|--|-----|

# APPENDIX B — STI BUS AND MASSBUS REGISTER DESCRIPTIONS

| B.1 INTRODUCTION E                | 5-1 |

|-----------------------------------|-----|

| B.2 STI BUS REGISTER DESCRIPTIONS | 3-1 |

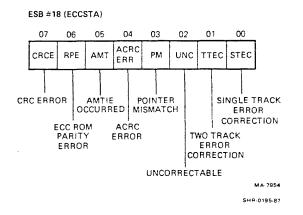

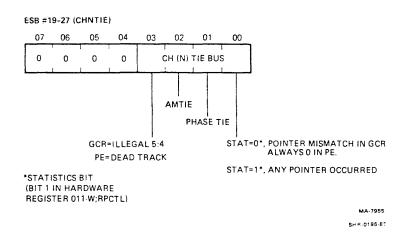

| B.2.1 Extended Drive Status       | 3-2 |

| B.2.2 Extended Formatter Status   | 30  |

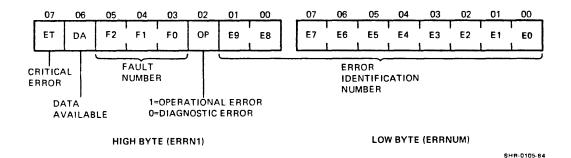

| B.2.3 Error Number                | 58  |

| B.3 MASSBUS REGISTER DESCRIPTIONS | 59  |

APPENDIX C — TM78 TAPE UNIT COMMAND/STATUS ADDRESSES AND BIT DESCRIPTIONS

APPENDIX D — TM78 EXTENDED SENSE COMMAND (73) DATA BYTES

APPENDIX E — TM78 INTERNAL I/O REGISTERS

APPENDIX F — INTERFACE WIRE LIST AND TRANSPORT INTERCONNECTIONS

#### FIGURES

٦.

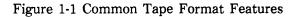

| 1-1 Common Tape Format Features                     | 1-5  |

|-----------------------------------------------------|------|

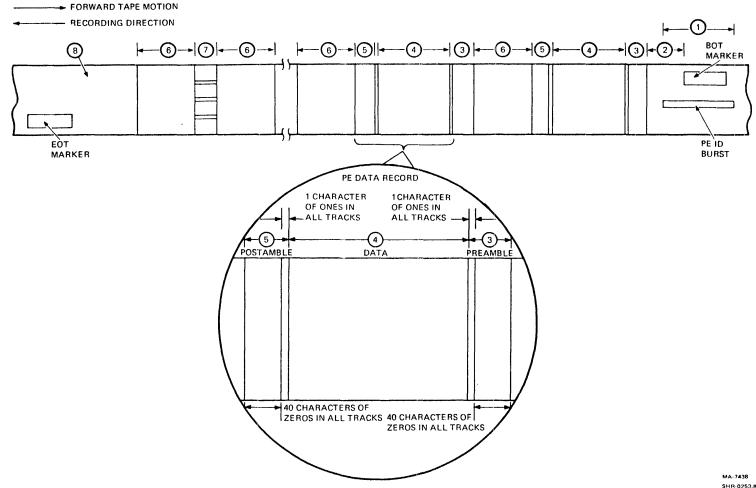

| 1-2 PE Recording Format (1600 Characters per Inch)  | 1-6  |

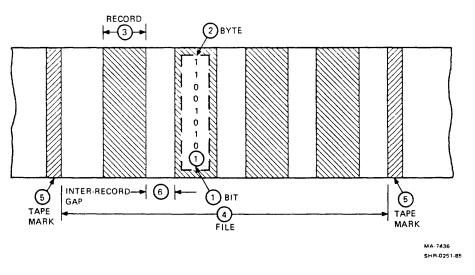

| 1-3 PE Tape Format                                  | 1-7  |

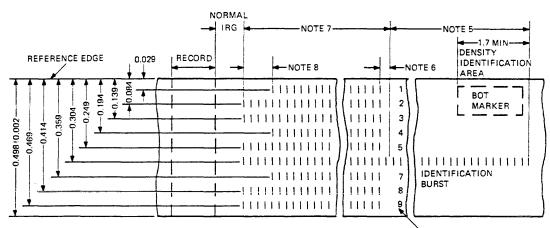

| 1-4 GCR Recording Format (6250 Characters per Inch) | 1-9  |

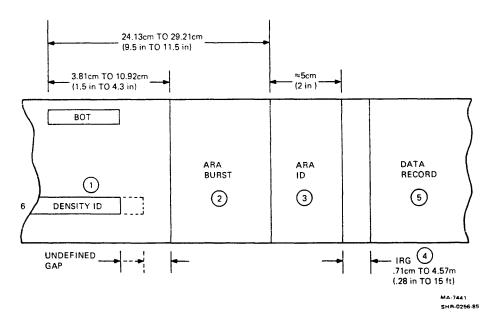

| 1-5 GCR Tape Format                                 | 1-10 |

| 1-6 GCR ID Area                                     | 1-11 |

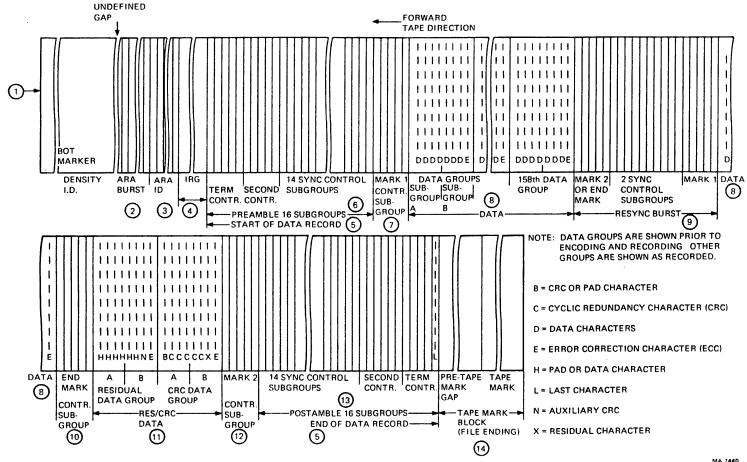

| 1-7 GCR Preamble and Data                                     | . 1-13         |

|---------------------------------------------------------------|----------------|

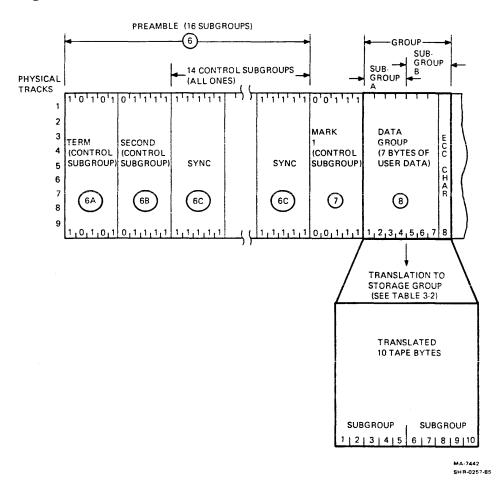

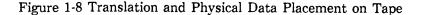

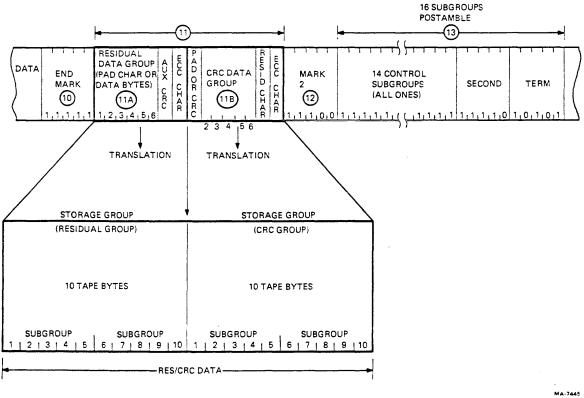

| 1-8 Translation and Physical Data Placement on Tape           |                |

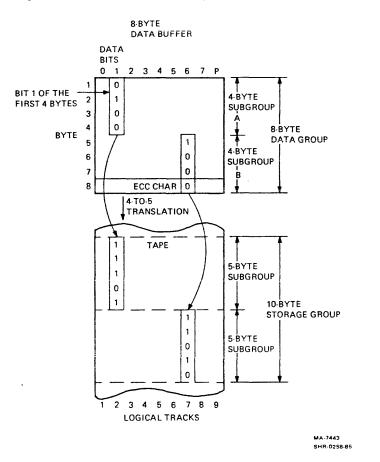

| 1-9 Resynchronization Burst Format                            |                |

| 1-10 End Data and Postamble                                   |                |

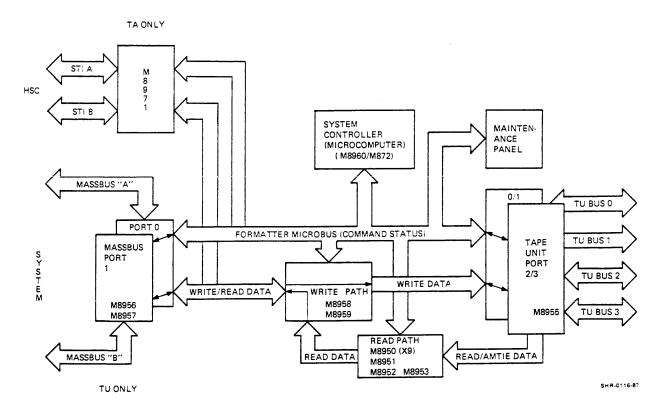

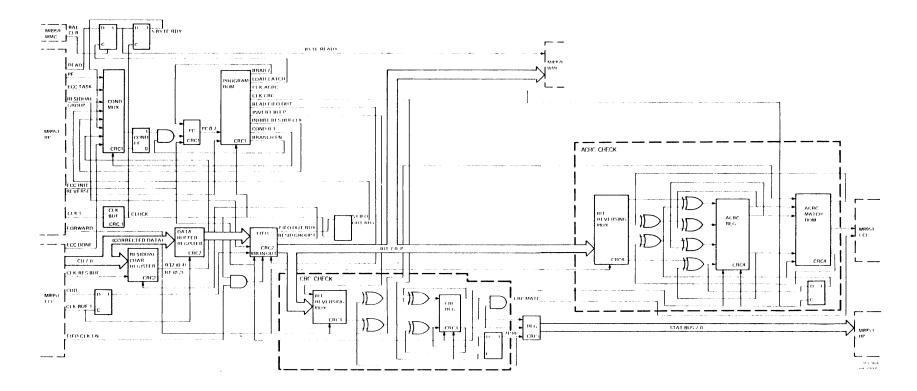

| 1-11 Formatter Internal System Block Diagram                  |                |

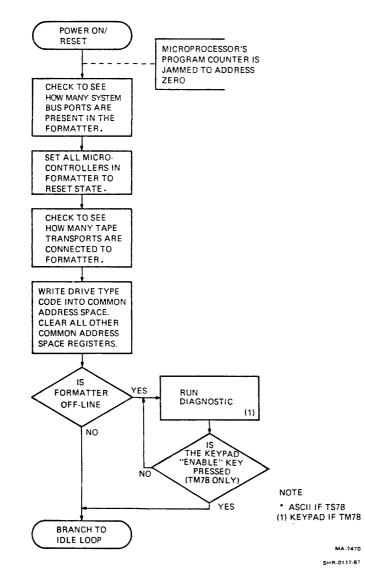

| 1-12 Power On/Reset Flowchart                                 | . 1-23         |

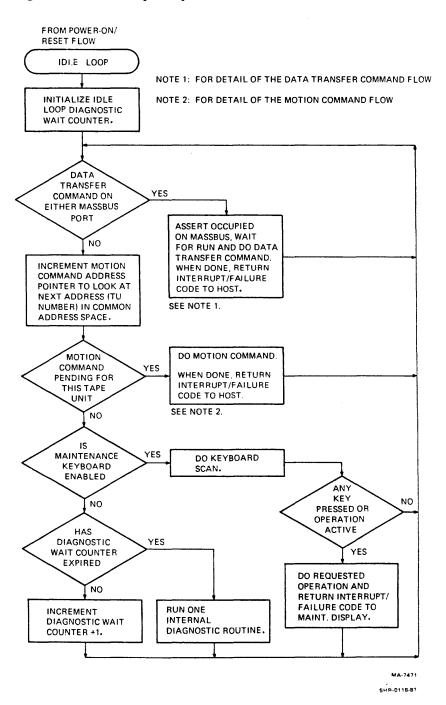

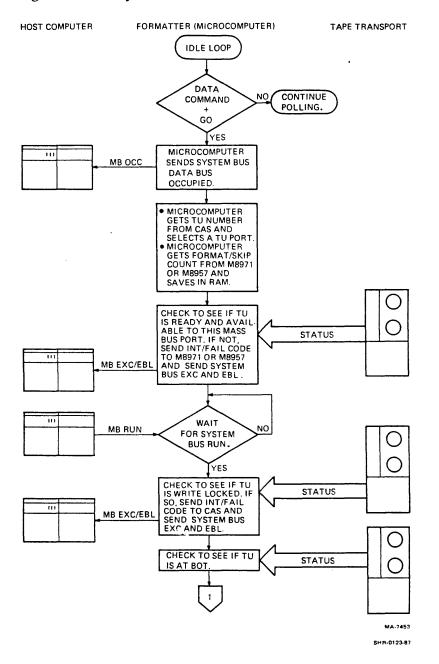

| 1-13 Idle Loop Simplified Flowchart                           |                |

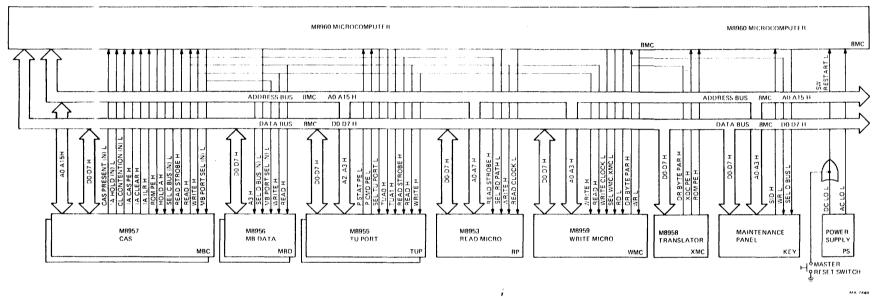

| 1-14 TM78 Microbus System Interconnection.                    |                |

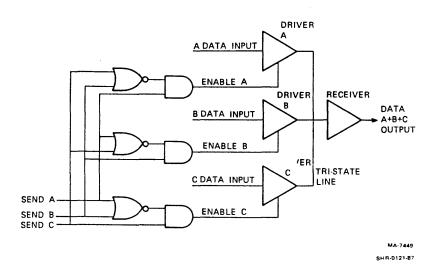

| 1-15 Typical Tri-State-DRNEW Line (Decoding Scheme)           |                |

| 1-16 Subsystem Data Transfer Command                          |                |

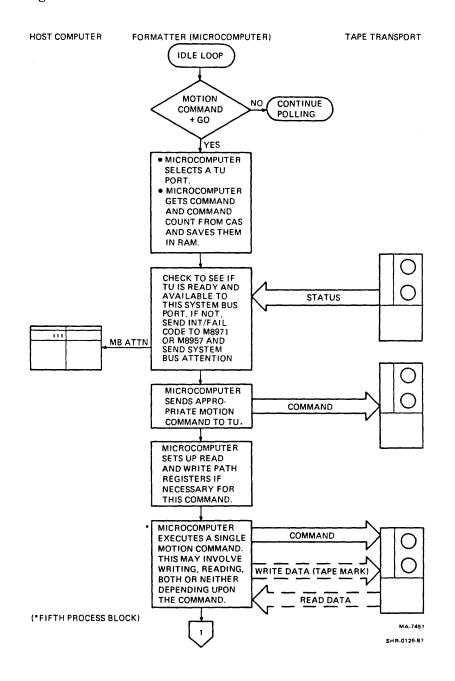

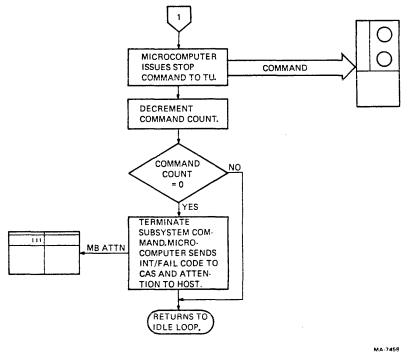

| 1-17 Motion Command                                           |                |

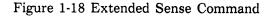

| 1-18 Extended Sense Command                                   |                |

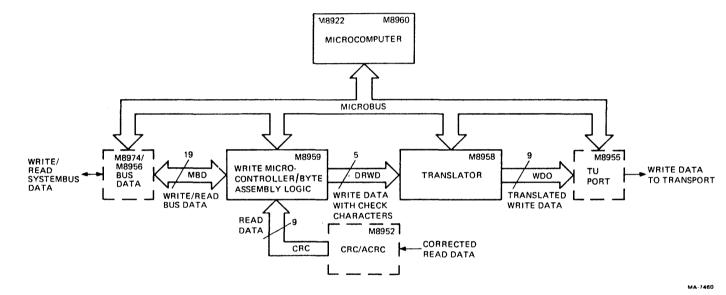

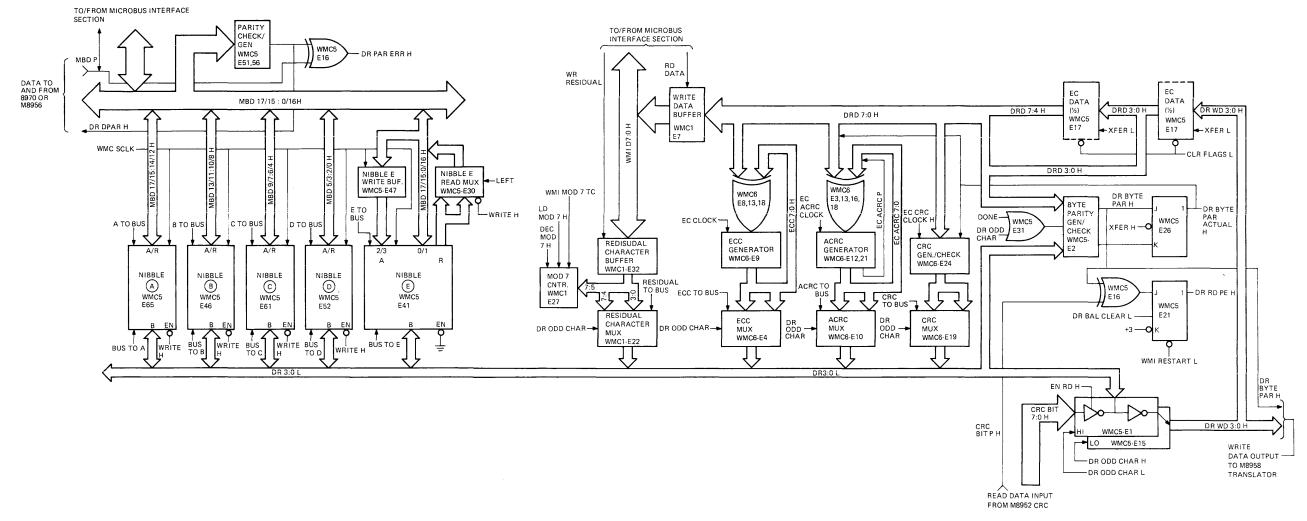

| 1-19 Basic Write Logic Block Diagram.                         |                |

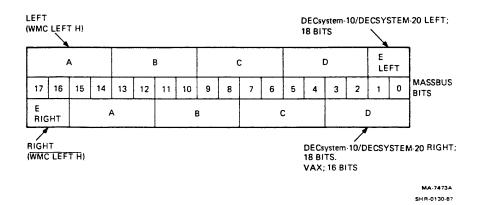

| 1-20 Massbus to Write Microcontroller Nibble                  |                |

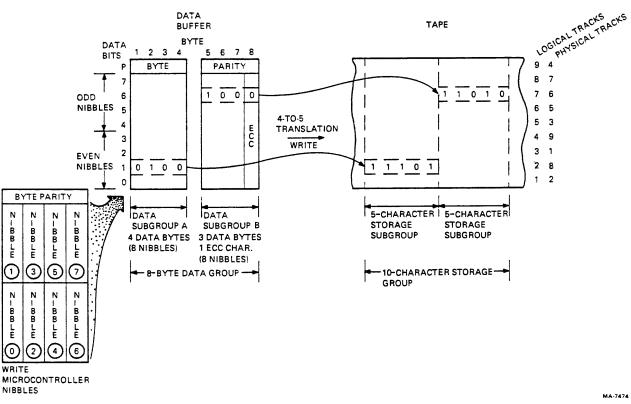

| 1-21 Translation and Physical Data Placement on Tape (Detail) |                |

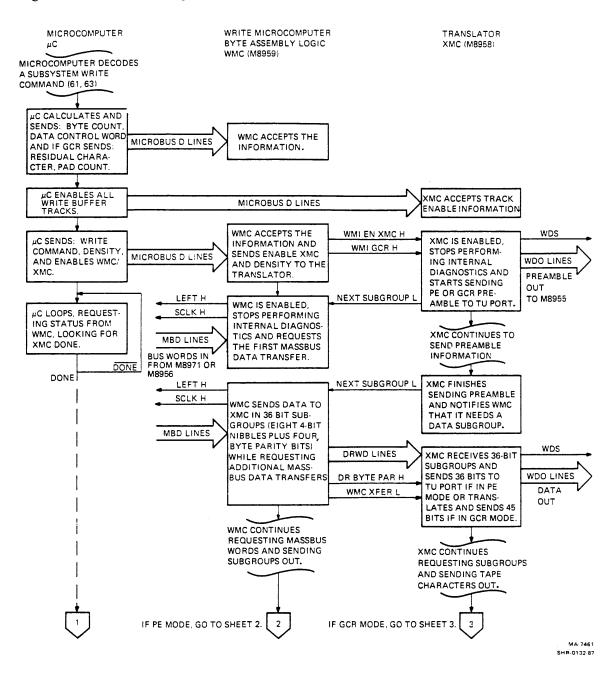

| 1-22 Write Path Operational Flowchart                         |                |

| 1-23 Basic Read Logic Block Diagram                           |                |

|                                                               |                |

| 1-24 Tape Unit Bus Signals                                    |                |

| 1-25 Tape Unit Bus Signal Line Pair                           |                |

| 1-26 Tape Unit Bus Present H Signal Line                      |                |

| 1-27 Tape Unit Bus Command Transfer Timing                    |                |

| 1-28 Tape Unit Bus Status Transfer Timing                     |                |

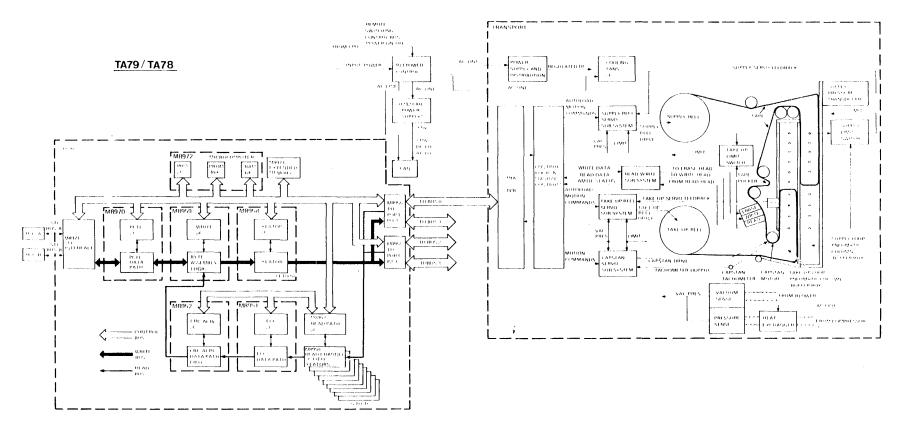

| 2-1 Magnetic Tape Subsystem Functional Block Diagram          |                |

| 2-2 M8972 Block Diagram                                       |                |

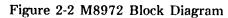

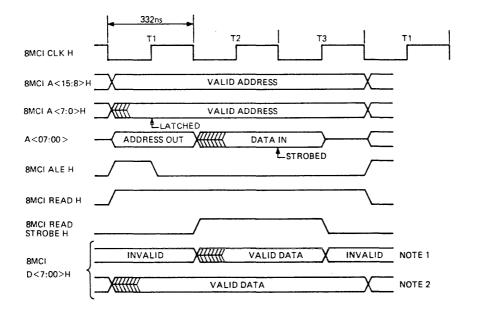

| 2-3 Write Data Transfer Timing.                               |                |

| 2-4 Read Data Transfer Timing                                 |                |

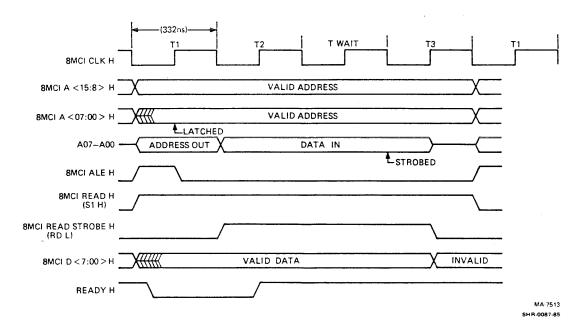

| 2-5 Extended Read Data Transfer                               |                |

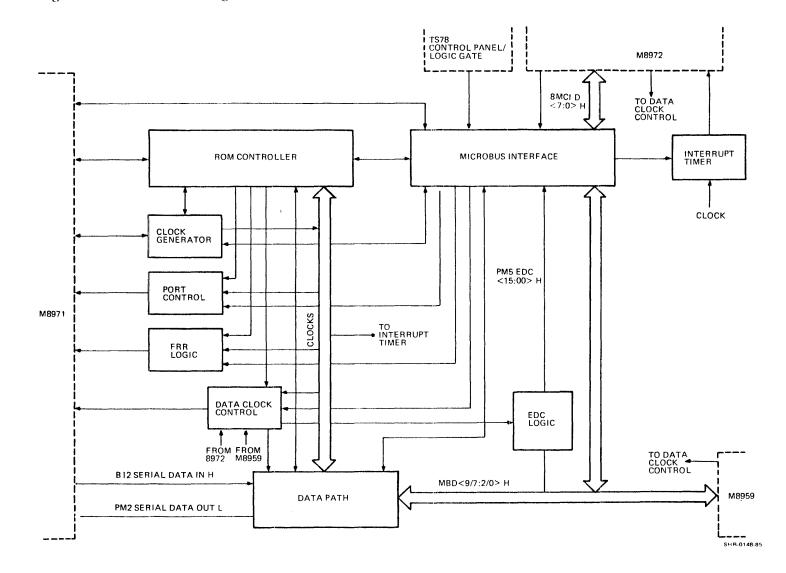

| 2-6 M8970 Block Diagram                                       |                |

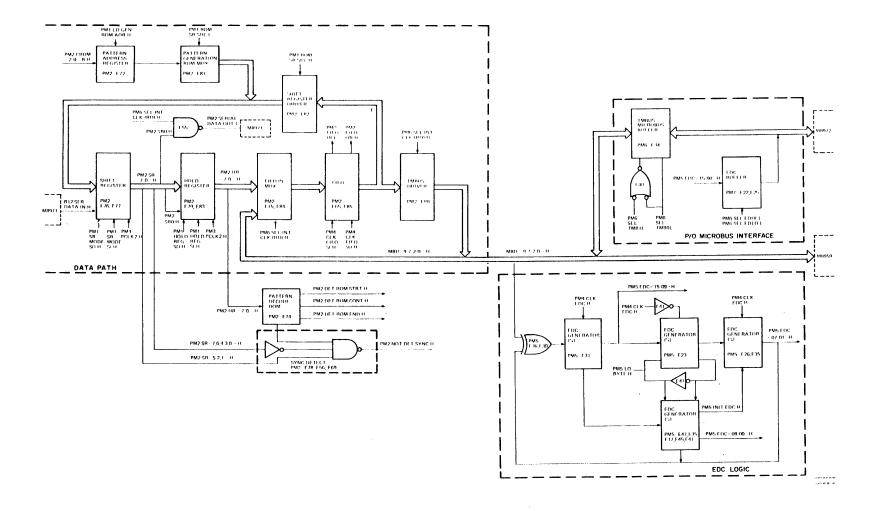

| 2-7 M8970 Data Path and EDC Logic                             |                |

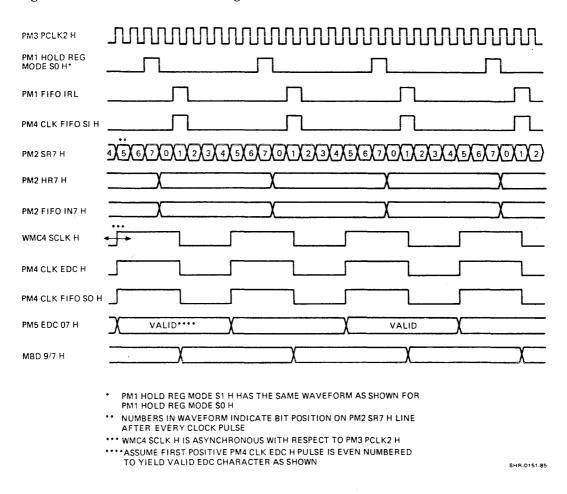

| 2-8 Write Data Flow Timing (M8970 Data Path)                  |                |

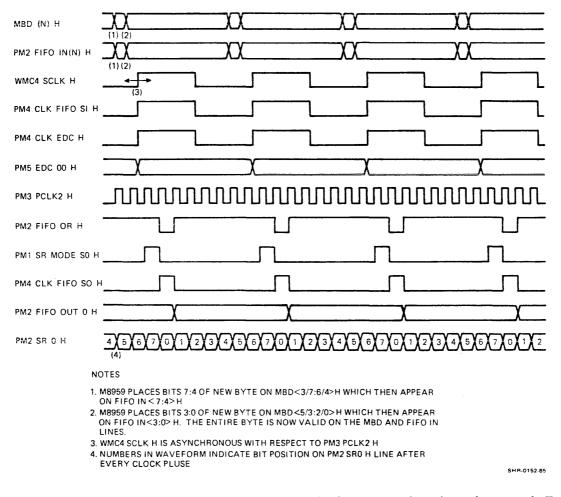

| 2-9 Read Data Flow Timing (M8970 Data Path)                   |                |

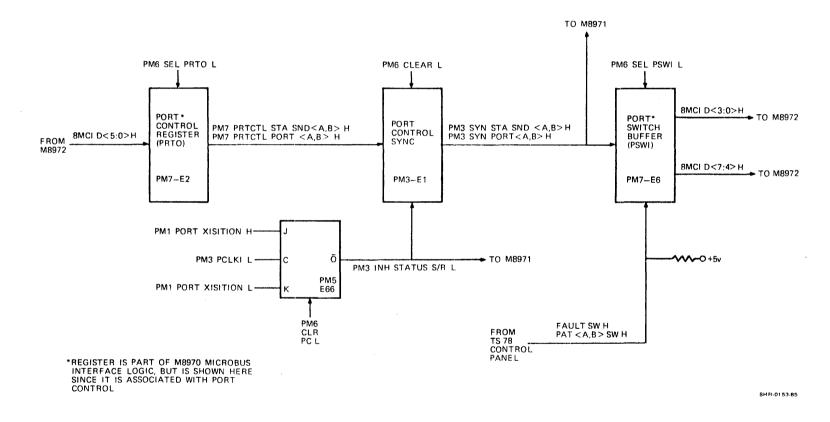

| 2-10 M8970 Port Control Logic and Associated Registers        |                |

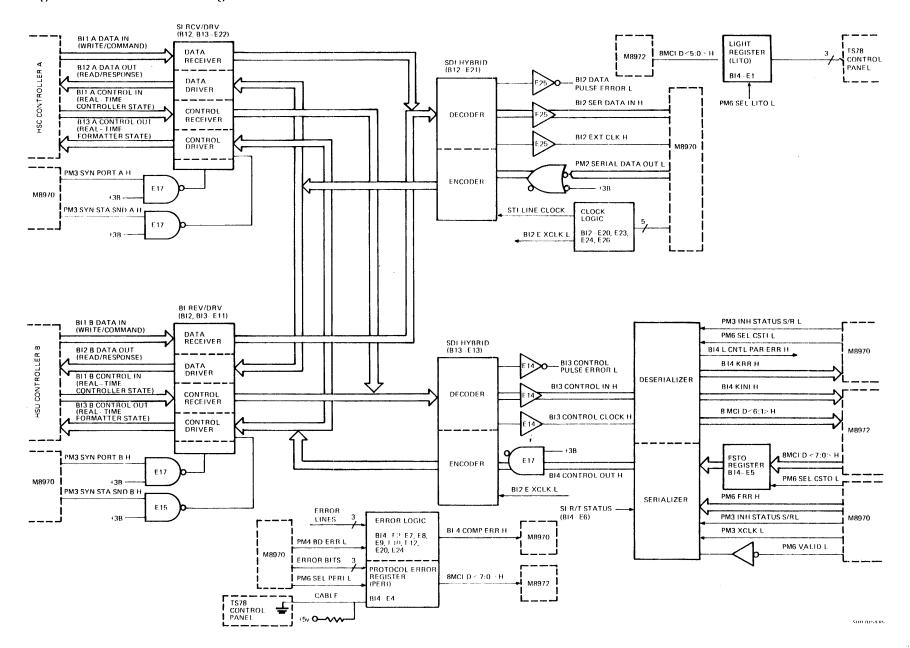

| 2-11 M8971 Block Diagram                                      |                |

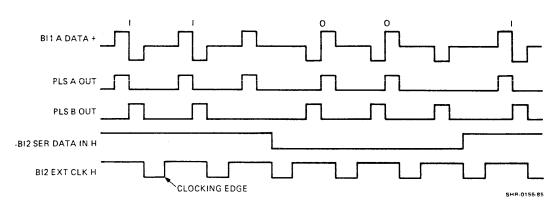

| 2-12 Waveform Accessing of Received Information               |                |

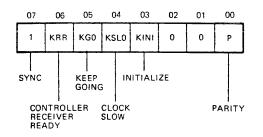

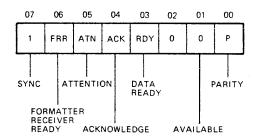

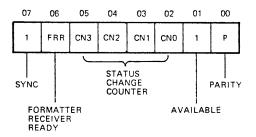

| 2-13 Controller/Formatter State Bit Assignments               |                |

| 2-14 M8960 Microcomputer Functional Areas                     |                |

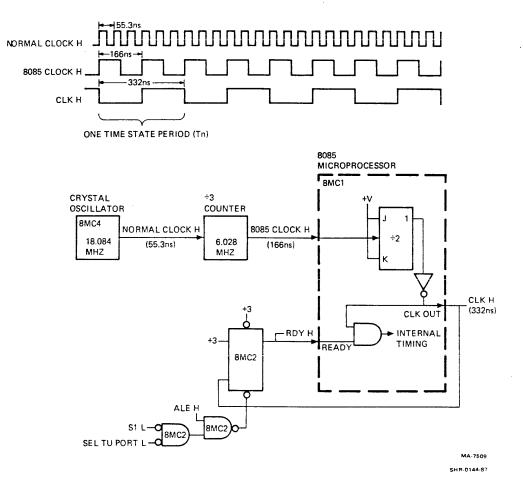

| 2-15 M8960 Block Diagram                                      | . <b>2-6</b> 1 |

| 2-16 Microcomputing Timing                                    | . 2-65         |

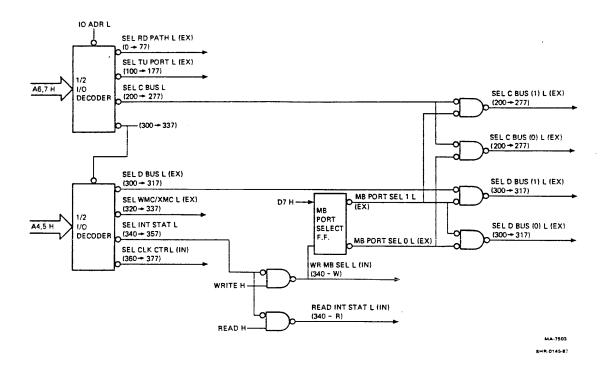

| 2-17 I/O Decode Logic                                         | . 2-67         |

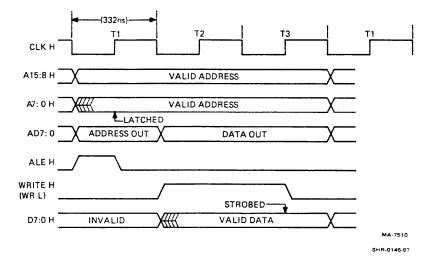

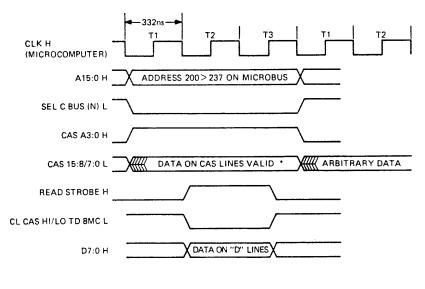

| 2-18 Typical Microbus Write Cycle                             | . 2-69         |

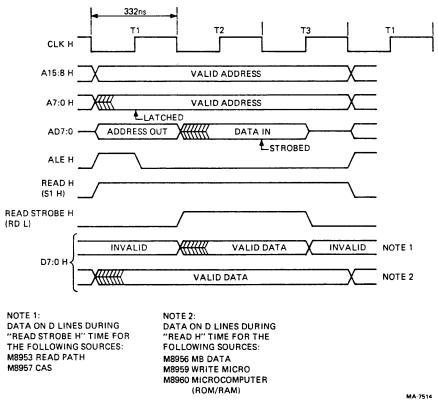

| 2-19 Typical Microbus Read Cycle                              | . 2-69         |

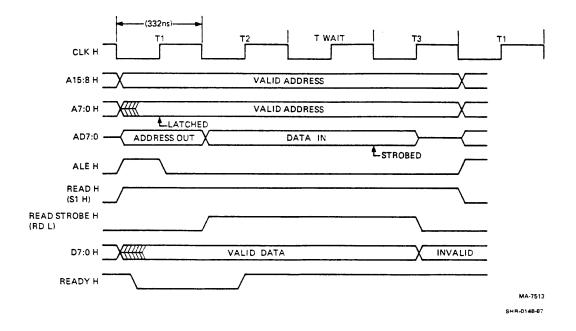

| 2-20 Microbus Read Cycle from TU Port                         | . 2-70         |

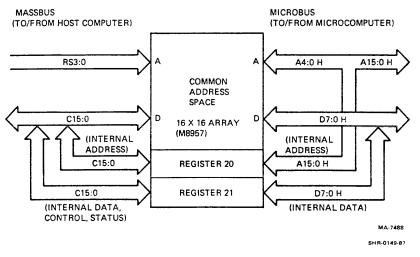

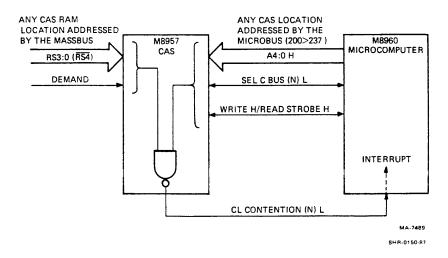

| 2-21 CAS Dual-Ported RAM                                      | . 2-71         |

| 2-22 CAS Addressing Contention Error                          | . 2-71         |

| 2-23 CAS Data Paths                                           | . 2-73         |

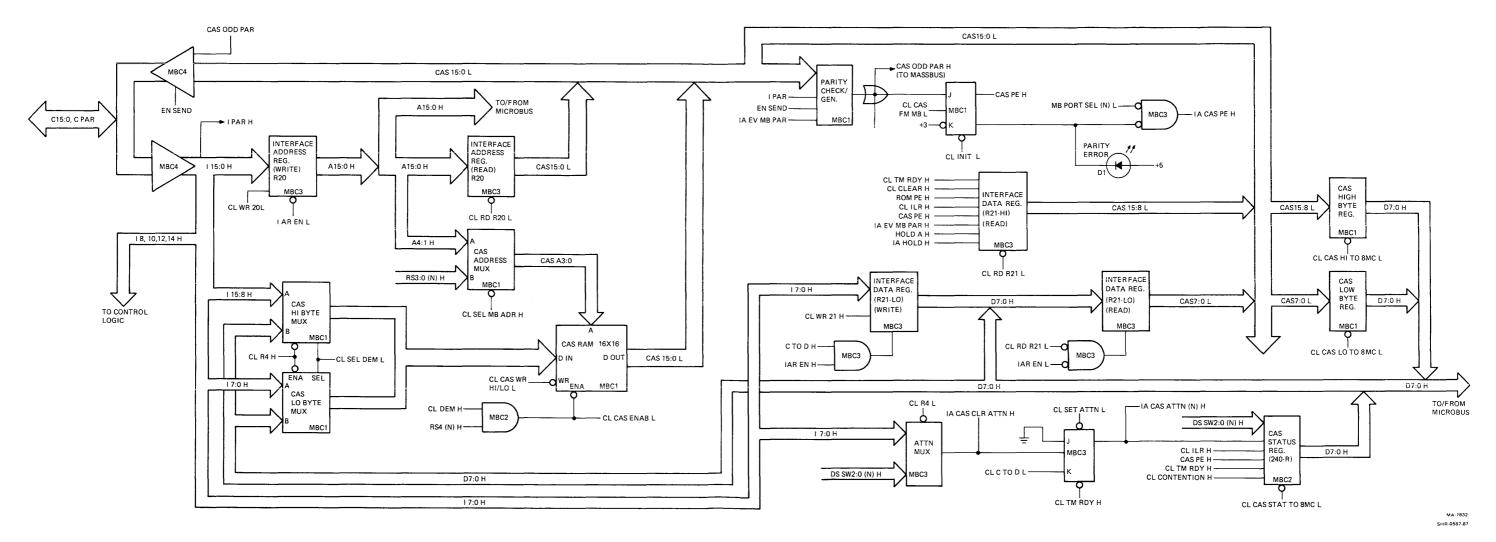

| 2-24 CAS Massbus Control Logic                                | . 2-76         |

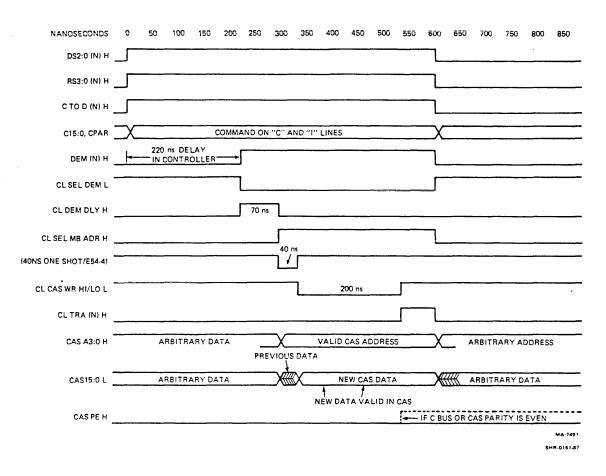

| 2-25 Timing for Massbus Write to CAS                          |                |

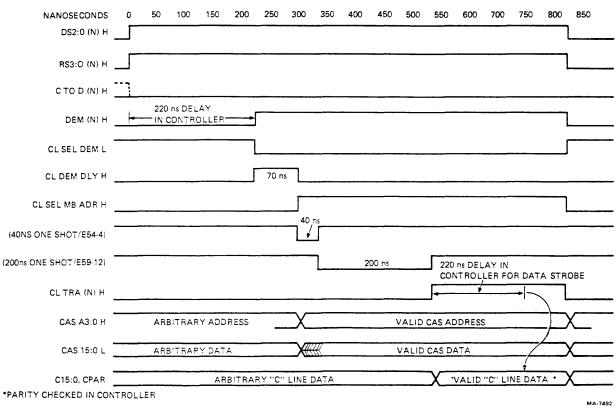

| 2-26 Timing for Massbus Read from CAS                         |                |

| -                                                             |                |

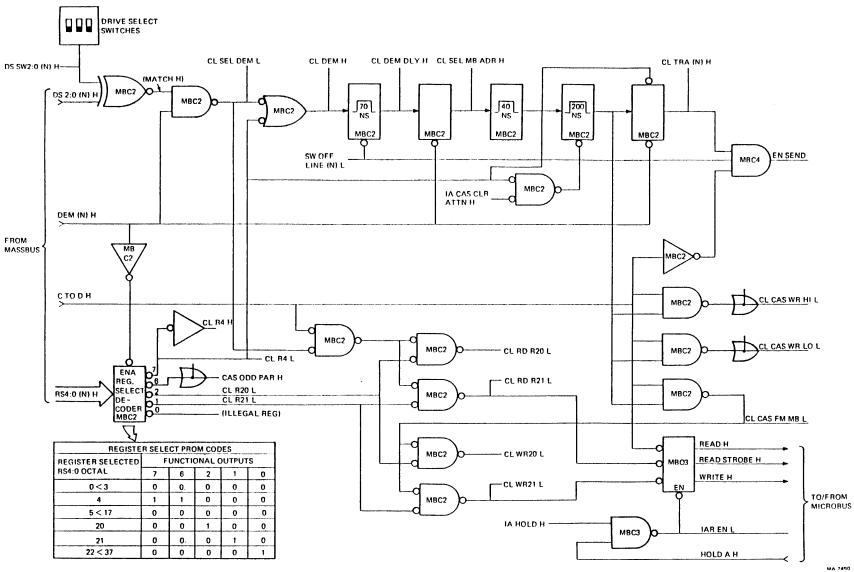

| 2-27 CAS Miscellaneous Control Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

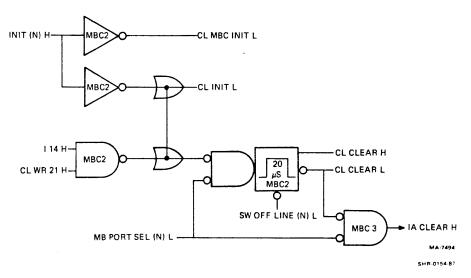

| 2-28 CAS Clear Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

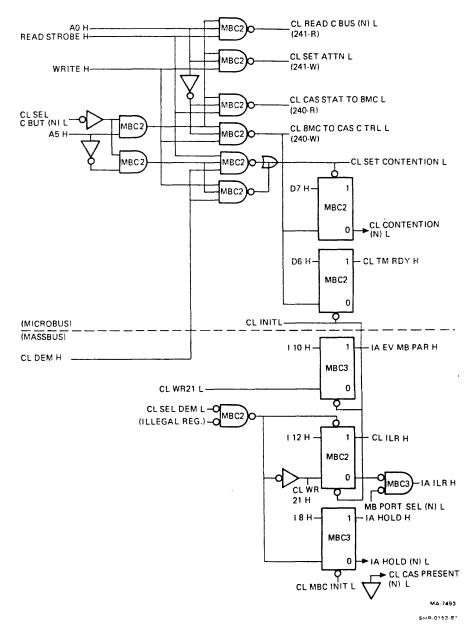

| 2-29 CAS Microbus Control Circuitry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2-30 Timing for Internal Write to CAS 2-85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2-31 Timing for Internal Read from CAS 2-86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

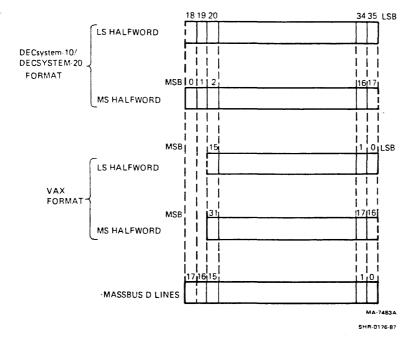

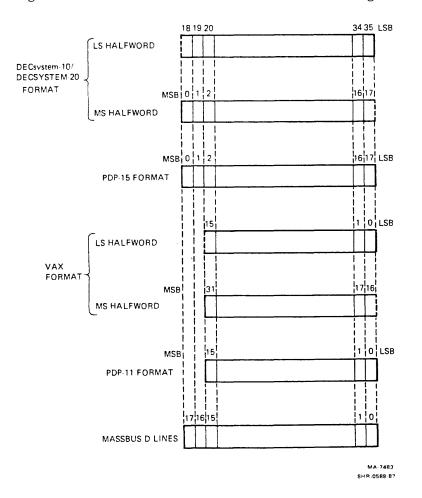

| 2-32 Processor Data Word Formats on Massbus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

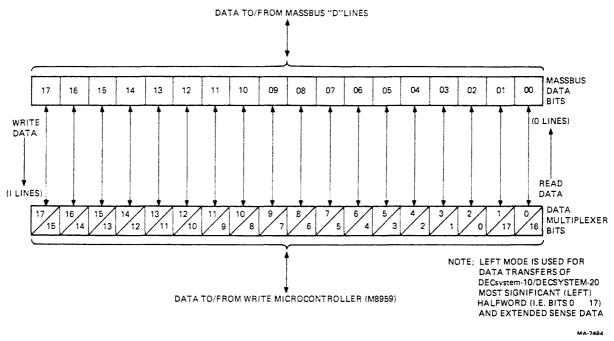

| 2-33 Data Multiplexer (Left Format)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

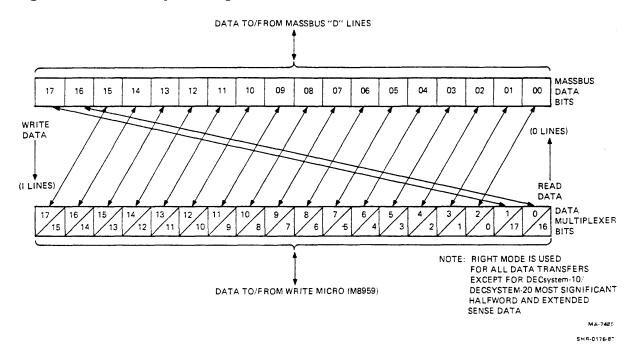

| 2-34 Data Multiplexer (Right Format)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

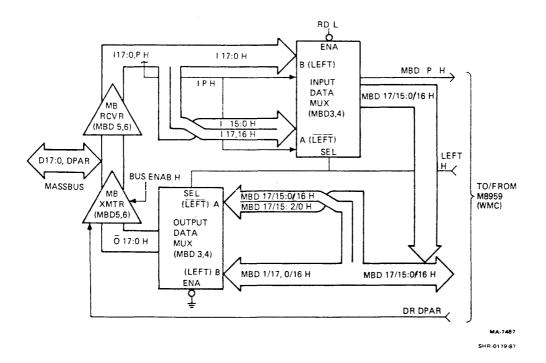

| 2-35 M8956 Massbus Data Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2-36 Massbus Data Multiplexers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

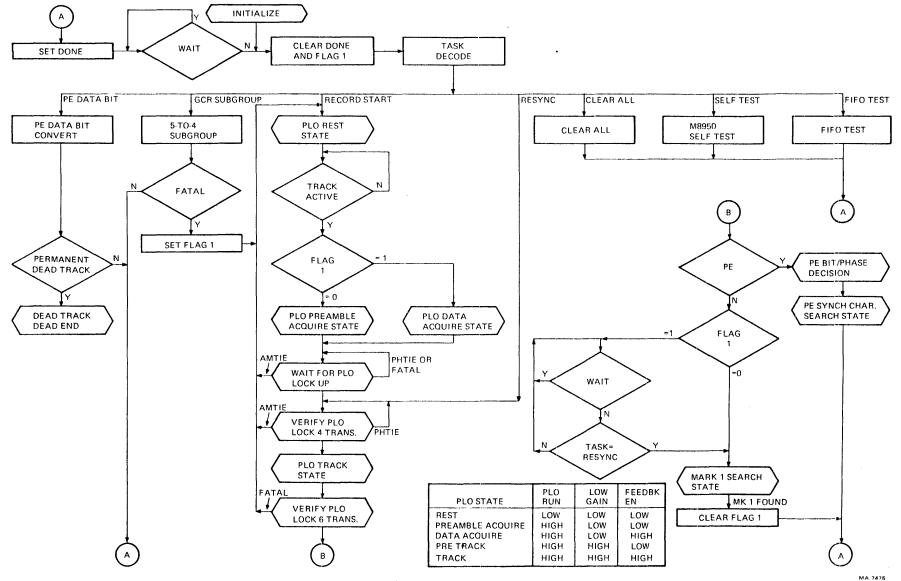

| 2-37 M8950 Read Channel Program Macro Flowchart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

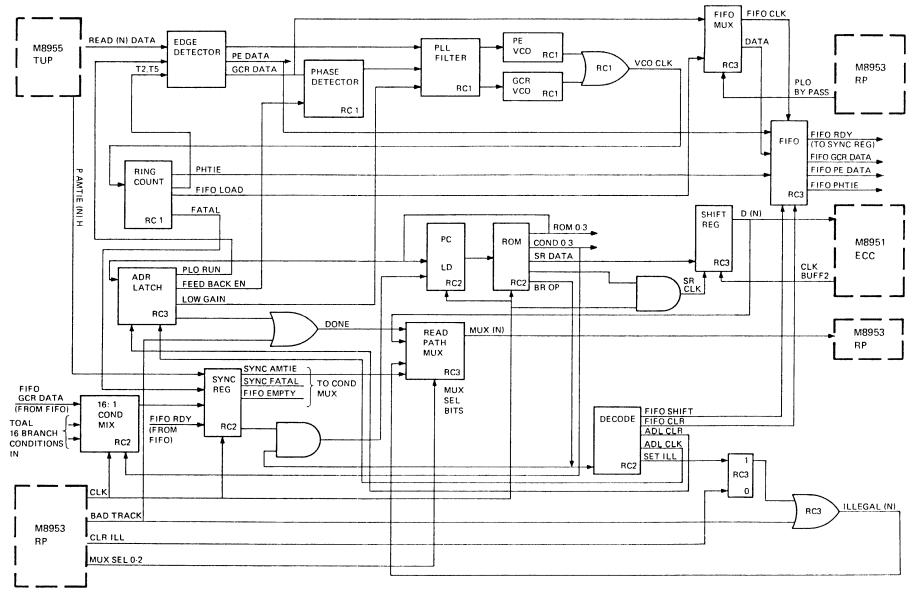

| 2-38 M8950 Read Channel Simplified Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

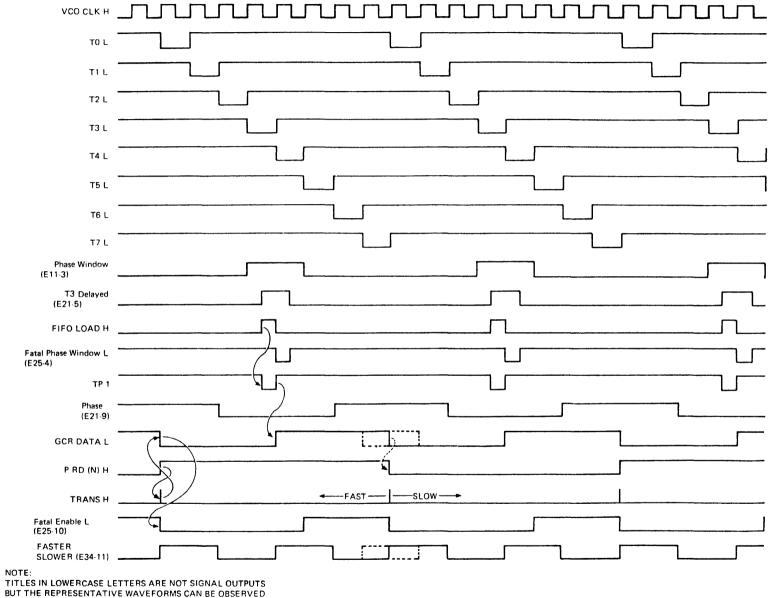

| 2-39 Read Channel PLL Timing Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

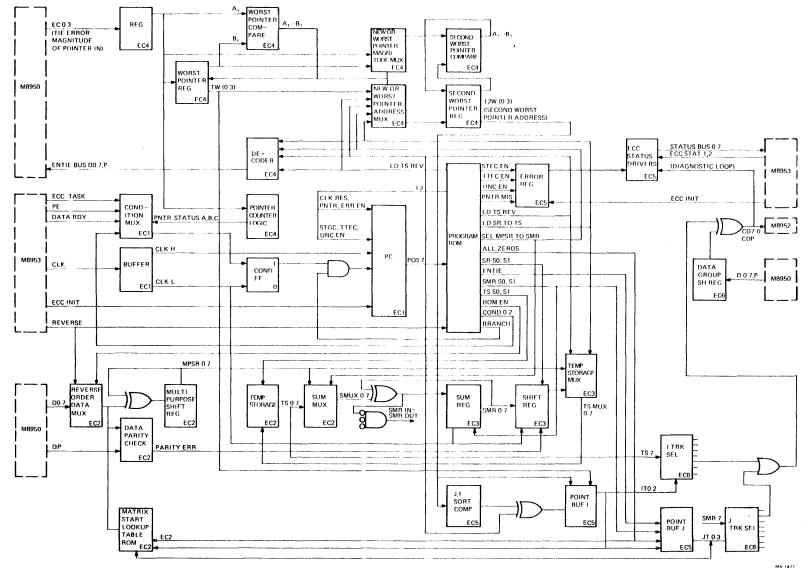

| 2-40 M8951 ECC Module Simplified Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2-41 M8952 CRC Module Simplified Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2-42 M8953 Read Path Controller Simplified Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

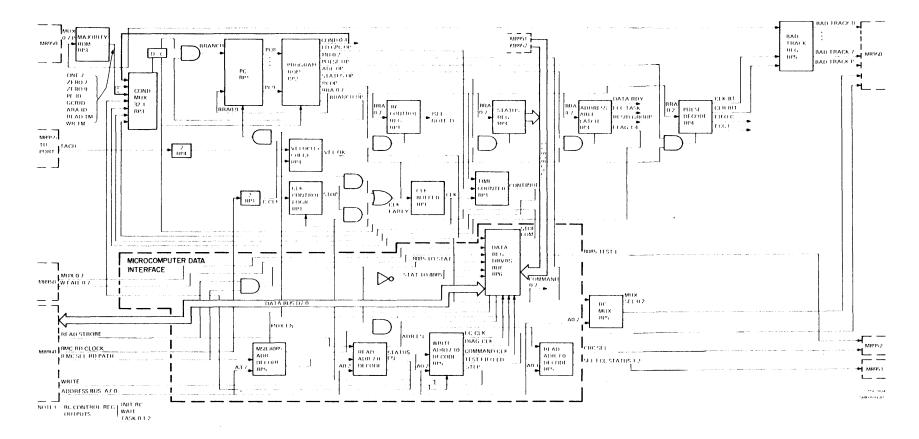

| 2-43 TU Port I/O Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2-44 M8955 TU Port Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

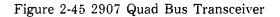

| 2-45 2907 Quad Bus Transceiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

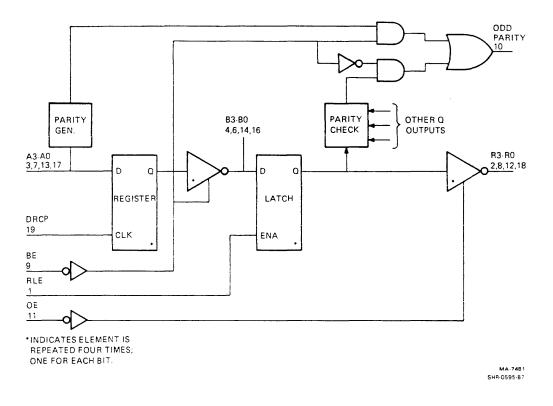

| 2-46 26S10 Quad Bus Transceiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

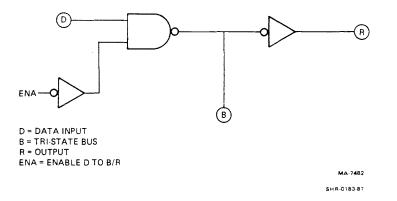

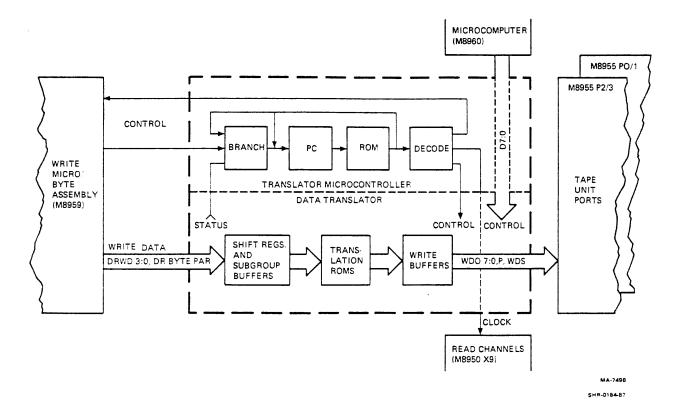

| 2-47 M8958 Translator Functional Area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

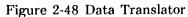

| 2-48 Data Translator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

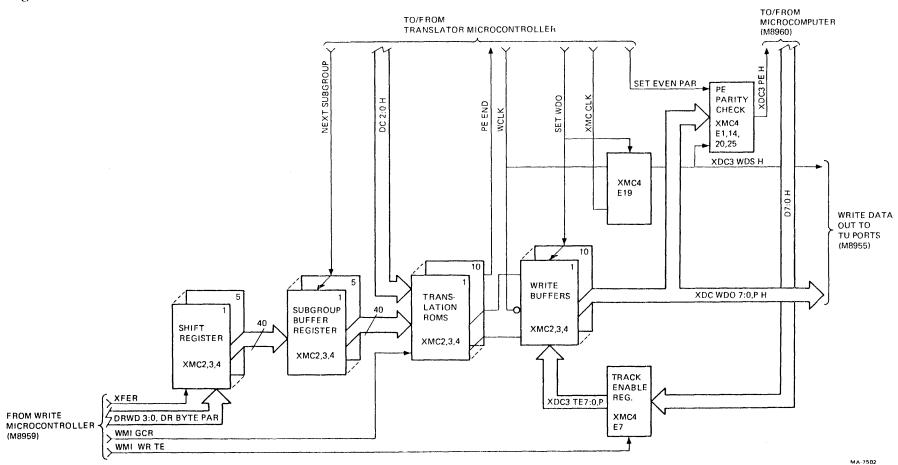

| 2-49 Translation ROM Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

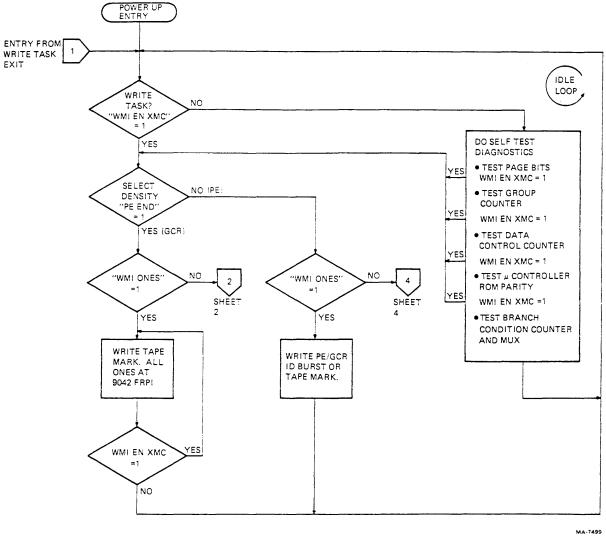

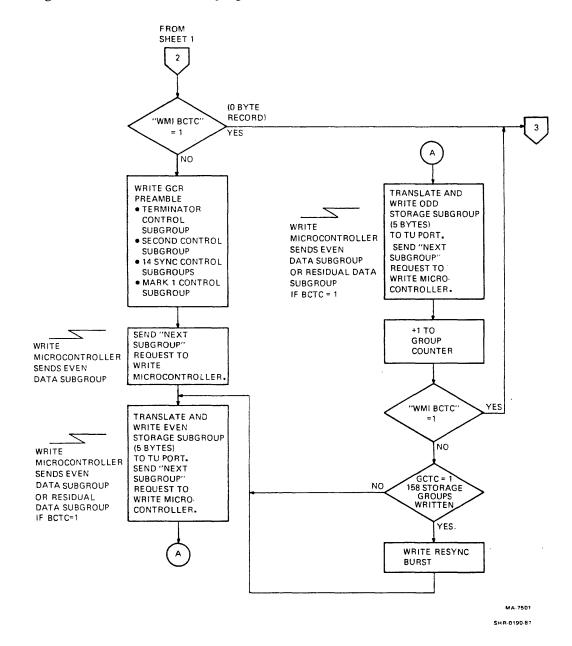

| 2-50 Translator Microprogram Flowchart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2-51 Translation Microcontroller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

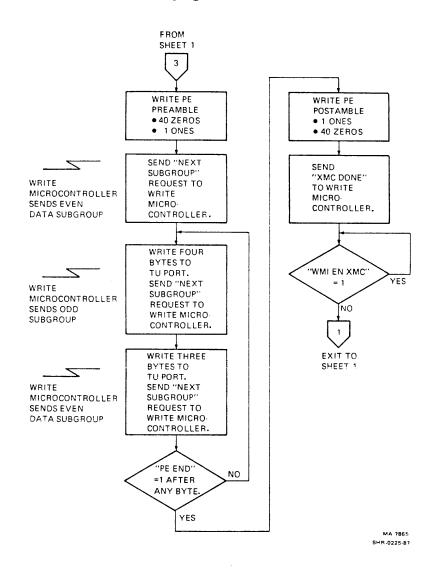

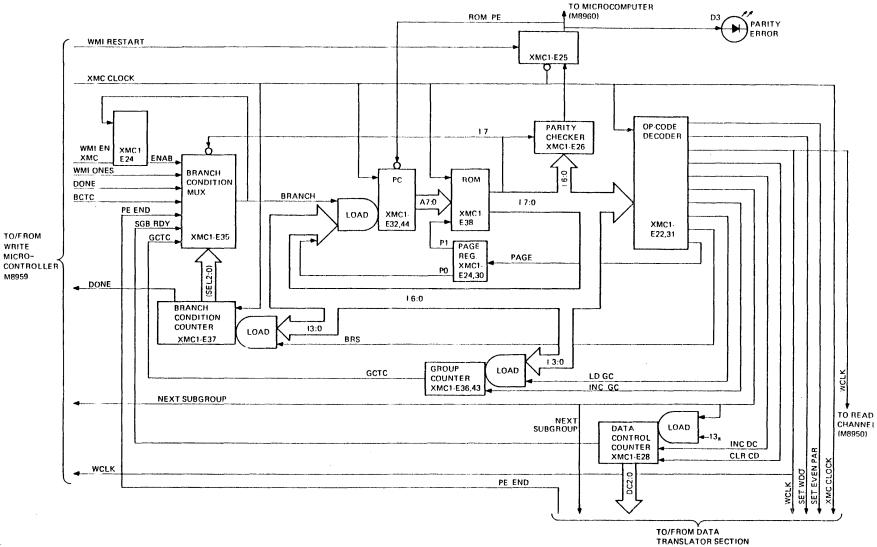

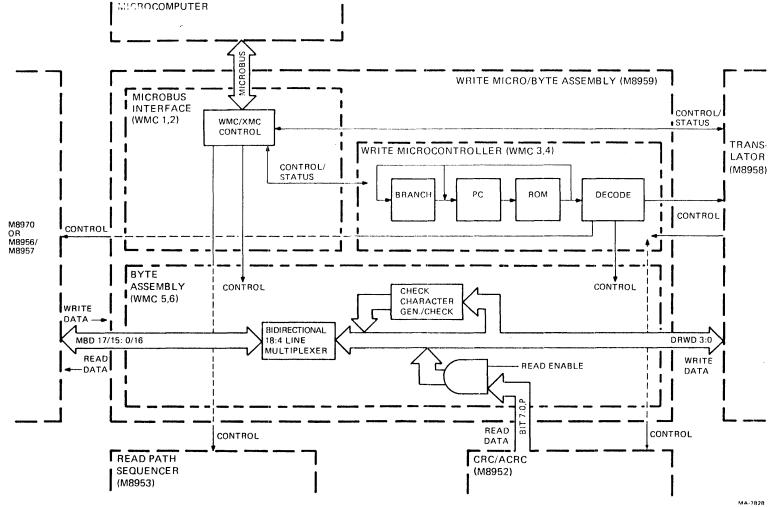

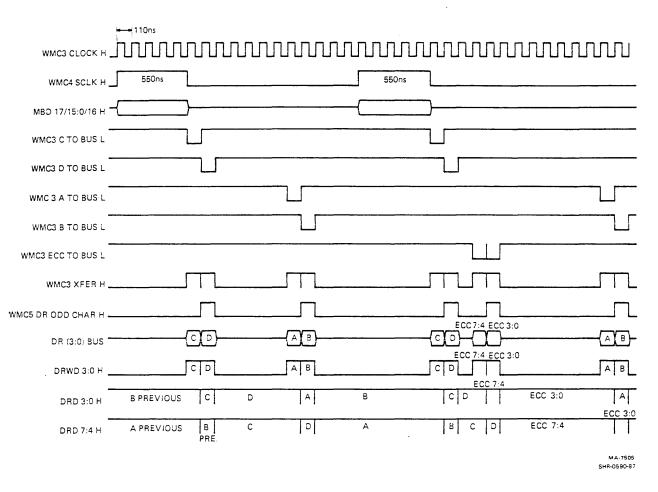

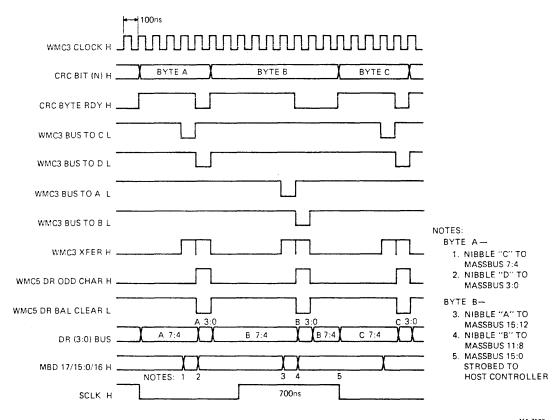

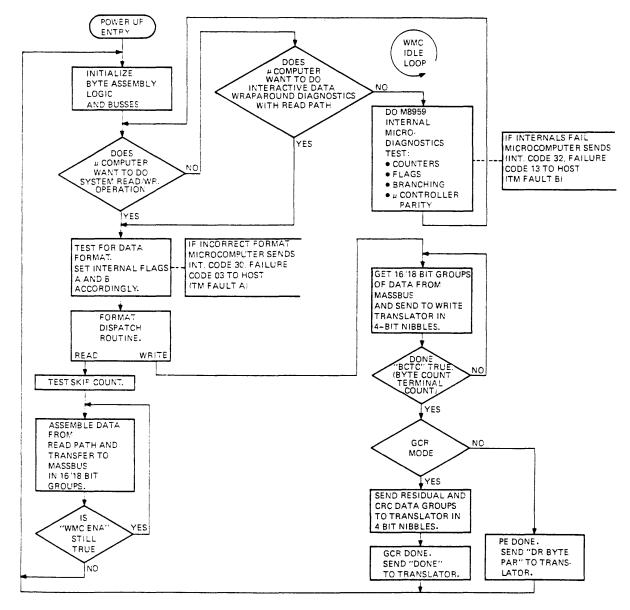

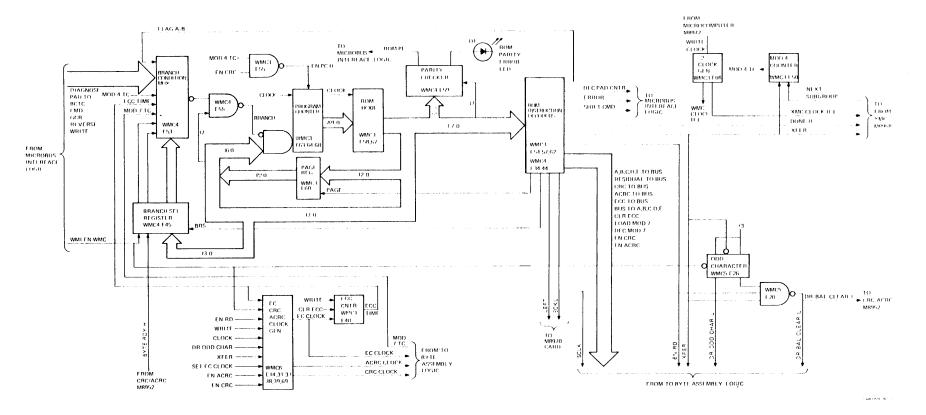

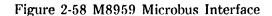

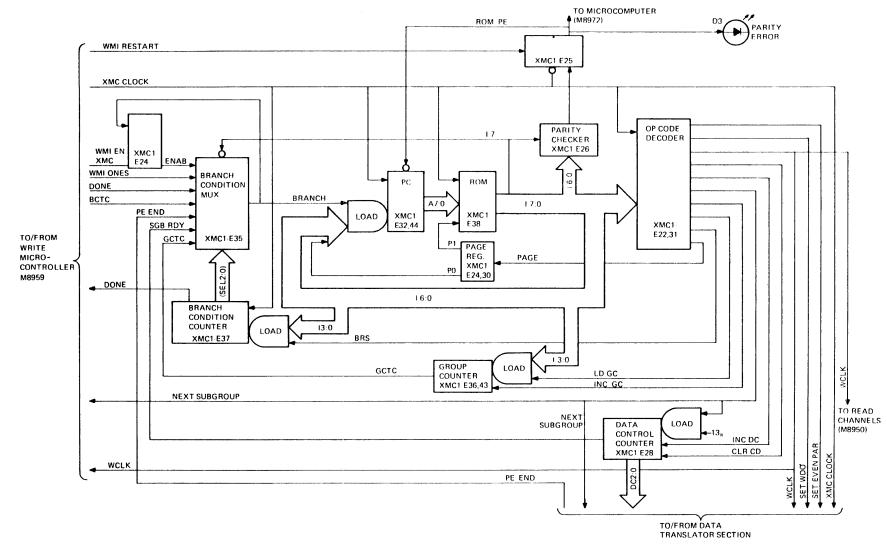

| 2-51 Translation Microcontroller.2-1382-52 M8959 Write Microcontroller Functional Areas2-1412-53 Write Microcontroller Byte Assembly Logic2-1432-54 Timing for Typical Write Data Flow through Byte Assembly Logic inPDP-11 Normal Mode.2-55 Timing for Typical Read Data Flow through Byte Assembly Logic in.2-143PDP-11 Normal Mode2-1432-56 Write Microcontroller Flow2-1432-57 Write Microcontroller Flow2-1532-58 M8959 Microbus Interface.2-1542-59 TS78 Power Supply2-156                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2-51 Translation Microcontroller.2-1382-52 M8959 Write Microcontroller Functional Areas2-1412-53 Write Microcontroller Byte Assembly Logic2-1432-54 Timing for Typical Write Data Flow through Byte Assembly Logic in.2-143PDP-11 Normal Mode2-1432-55 Timing for Typical Read Data Flow through Byte Assembly Logic in.2-143PDP-11 Normal Mode2-1432-56 Write Microcontroller Flow2-1432-57 Write Microcontroller Flow2-1532-58 M8959 Microbus Interface.2-1542-59 TS78 Power Supply2-1562-60 TS78 Power Distribution.2-156                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2-51 Translation Microcontroller.2-1382-52 M8959 Write Microcontroller Functional Areas2-1412-53 Write Microcontroller Byte Assembly Logic2-1432-54 Timing for Typical Write Data Flow through Byte Assembly Logic in.2-143PDP-11 Normal Mode2-1432-55 Timing for Typical Read Data Flow through Byte Assembly Logic in.2-143PDP-11 Normal Mode2-1432-56 Write Microcontroller Flow2-1532-57 Write Microcontroller Flow2-1532-58 M8959 Microbus Interface.2-1542-59 TS78 Power Supply2-1562-60 TS78 Power Distribution.2-1562-61 Backplane/Power Supply Interconnection.2-158                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

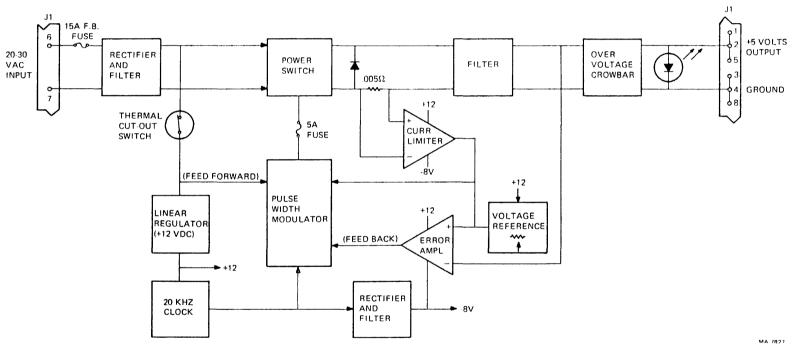

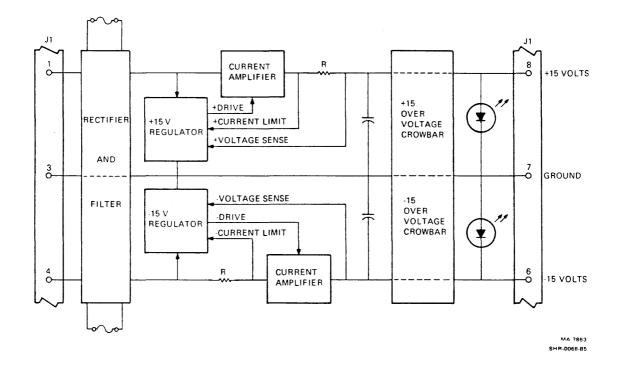

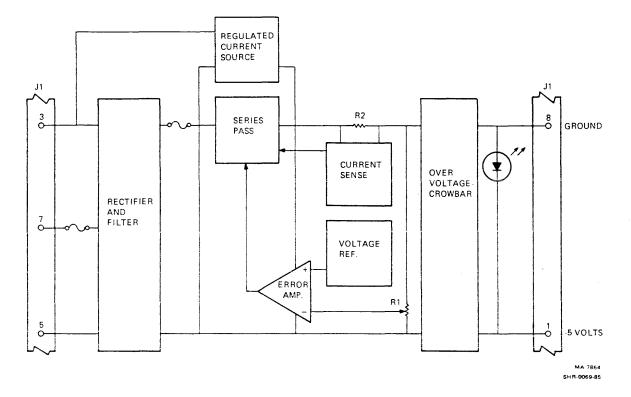

| 2-51 Translation Microcontroller.2-1382-52 M8959 Write Microcontroller Functional Areas2-1412-53 Write Microcontroller Byte Assembly Logic2-1432-54 Timing for Typical Write Data Flow through Byte Assembly Logic in.2-143PDP-11 Normal Mode2-1432-55 Timing for Typical Read Data Flow through Byte Assembly Logic in.2-143PDP-11 Normal Mode2-1432-56 Write Microcontroller Flow2-1432-57 Write Microcontroller Flow2-1532-58 M8959 Microbus Interface.2-1532-59 TS78 Power Supply.2-1562-60 TS78 Power Distribution.2-1562-61 Backplane/Power Supply Interconnection.2-1562-62 TS78 Power Supply Block Diagram2-161                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2-51 Translation Microcontroller.2-1382-52 M8959 Write Microcontroller Functional Areas2-1412-53 Write Microcontroller Byte Assembly Logic2-1432-54 Timing for Typical Write Data Flow through Byte Assembly Logic inPDP-11 Normal Mode.2-55 Timing for Typical Read Data Flow through Byte Assembly Logic in.2-143PDP-11 Normal Mode2-1432-56 Write Microcontroller Flow2-1432-57 Write Microcontroller Flow2-1532-58 M8959 Microbus Interface.2-1532-59 TS78 Power Supply.2-1532-60 TS78 Power Distribution.2-1532-61 Backplane/Power Supply Interconnection.2-1632-62 TS78 Power Supply Block Diagram2-1632-63 H7441 + 5 Volt Regulator Block Diagram2-163                                                                                                                                                                                                                                                                                                                                                                                               |

| 2-51 Translation Microcontroller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2-51 Translation Microcontroller.2-1332-52 M8959 Write Microcontroller Functional Areas2-1432-53 Write Microcontroller Byte Assembly Logic2-1432-54 Timing for Typical Write Data Flow through Byte Assembly Logic in.2-143PDP-11 Normal Mode2-1432-55 Timing for Typical Read Data Flow through Byte Assembly Logic in.2-143PDP-11 Normal Mode2-1432-55 Timing for Typical Read Data Flow through Byte Assembly Logic in.2-143PDP-11 Normal Mode2-1432-56 Write Microcontroller Flow2-1532-57 Write Microcontroller Flow2-1532-58 M8959 Microbus Interface.2-1532-59 TS78 Power Supply.2-1562-60 TS78 Power Supply.2-1562-61 Backplane/Power Supply Interconnection.2-1632-63 H7441 + 5 Volt Regulator Block Diagram2-1632-64 H7476 ± 15 Volt Regulator Block Diagram2-1642-65 H7490 — 5 Volt Regulator Block Diagram2-164                                                                                                                                                                                                                                 |

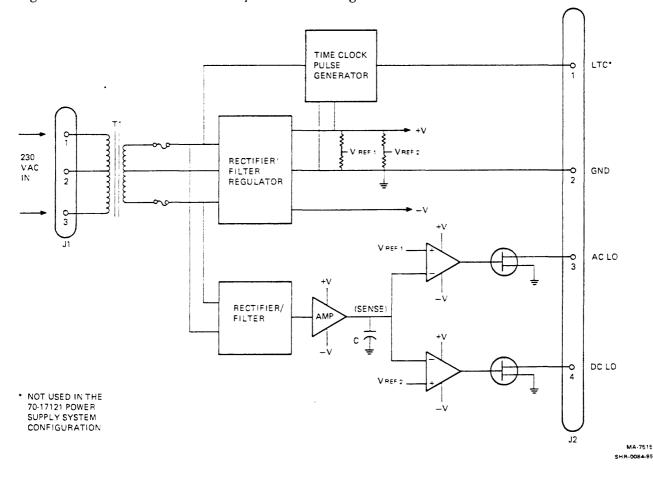

| 2-51 Translation Microcontroller.2-1332-52 M8959 Write Microcontroller Functional Areas2-1432-53 Write Microcontroller Byte Assembly Logic2-1432-54 Timing for Typical Write Data Flow through Byte Assembly Logic inPDP-11 Normal Mode.PDP-11 Normal Mode2-1432-55 Timing for Typical Read Data Flow through Byte Assembly Logic inPDP-11 Normal Mode.PDP-11 Normal Mode2-1432-55 Timing for Typical Read Data Flow through Byte Assembly Logic in2-143PDP-11 Normal Mode2-1432-56 Write Microcontroller Flow2-1562-57 Write Microcontroller Flow2-1562-58 M8959 Microbus Interface.2-1562-59 TS78 Power Supply.2-1562-60 TS78 Power Supply.2-1562-61 Backplane/Power Supply Interconnection.2-1662-62 TS78 Power Supply Block Diagram2-1662-64 H7476 ± 15 Volt Regulator Block Diagram2-1662-65 H7490 —5 Volt Regulator Block Diagram2-1662-66 AC/DC LO Module Simplified Block Diagram.2-166                                                                                                                                                             |

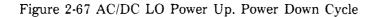

| 2-51 Translation Microcontroller2-1332-52 M8959 Write Microcontroller Functional Areas.2-1442-53 Write Microcontroller Byte Assembly Logic2-1442-53 Write Microcontroller Byte Assembly Logic2-1442-54 Timing for Typical Write Data Flow through Byte Assembly Logic inPDP-11 Normal Mode.PDP-11 Normal Mode.2-1442-55 Timing for Typical Read Data Flow through Byte Assembly Logic in2-144PDP-11 Normal Mode.2-1442-56 Write Microcontroller Flow.2-1452-57 Write Microcontroller Flow.2-1562-57 Write Microcontroller Supply2-1562-58 M8959 Microbus Interface2-1562-59 TS78 Power Supply2-1562-60 TS78 Power Supply2-1562-61 Backplane/Power Supply Interconnection2-1662-62 TS78 Power Supply Block Diagram2-1662-64 H7476 ± 15 Volt Regulator Block Diagram2-1662-65 H7490 —5 Volt Regulator Block Diagram2-1662-66 AC/DC LO Module Simplified Block Diagram2-1662-67 AC/DC LO Power Up, Power Down Cycle2-167                                                                                                                                       |

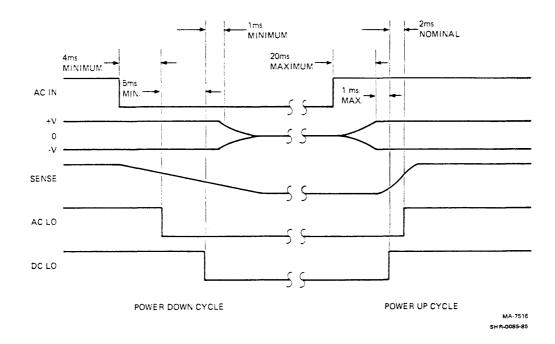

| 2-51 Translation Microcontroller2-1382-52 M8959 Write Microcontroller Functional Areas.2-1412-53 Write Microcontroller Byte Assembly Logic.2-1432-54 Timing for Typical Write Data Flow through Byte Assembly Logic in2-143PDP-11 Normal Mode.2-1432-55 Timing for Typical Read Data Flow through Byte Assembly Logic in2-143PDP-11 Normal Mode.2-1442-55 Timing for Typical Read Data Flow through Byte Assembly Logic inPDP-11 Normal Mode.2-1442-56 Write Microcontroller Flow.2-1542-57 Write Microcontroller Flow.2-1562-58 M8959 Microbus Interface2-1562-59 TS78 Power Supply2-1562-60 TS78 Power Supply2-1562-61 Backplane/Power Supply Interconnection2-1632-63 H7441 + 5 Volt Regulator Block Diagram2-1662-64 H7476 ± 15 Volt Regulator Block Diagram2-1662-65 H7490 —5 Volt Regulator Block Diagram2-1662-67 AC/DC LO Power Up, Power Down Cycle2-1662-68 TM78 Maintenance Panel Block Diagram2-1662-68 TM78 Maintenance Panel Block Diagram2-166                                                                                               |

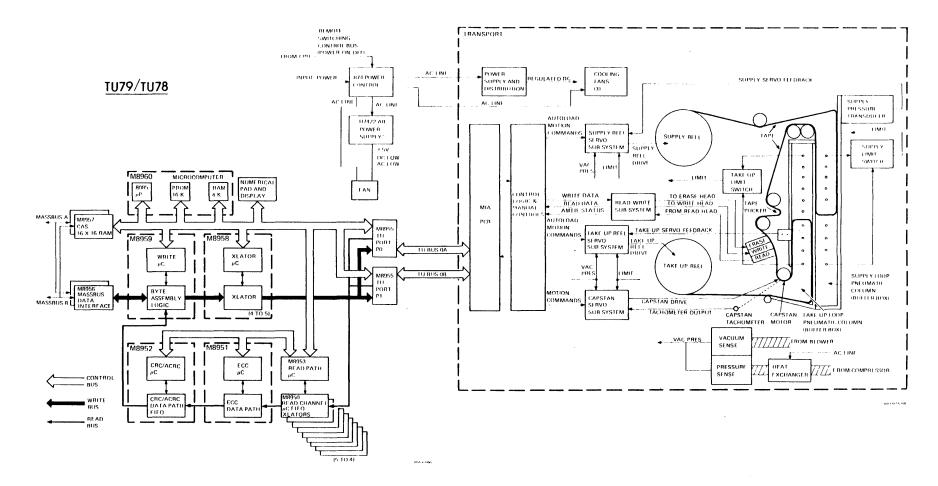

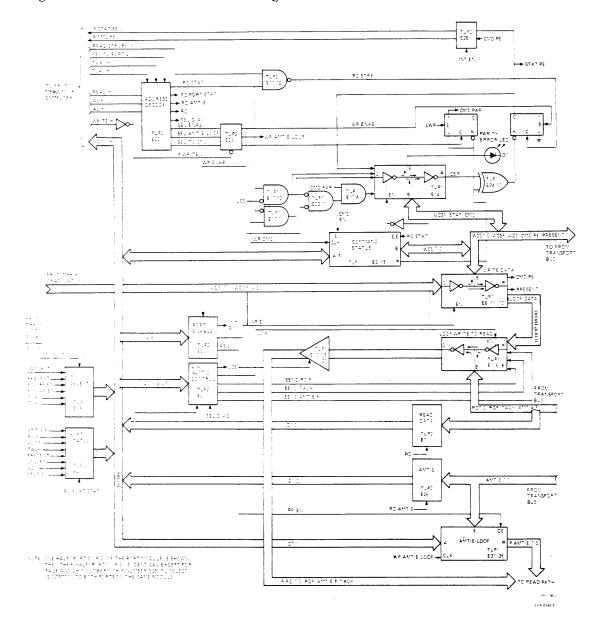

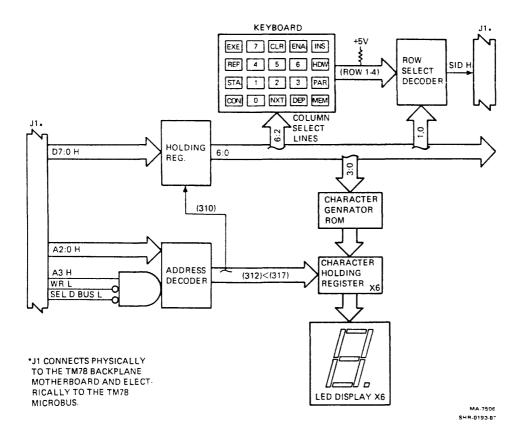

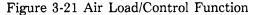

| 2-51 Translation Microcontroller2-1332-52 M8959 Write Microcontroller Functional Areas.2-1412-53 Write Microcontroller Byte Assembly Logic.2-1432-54 Timing for Typical Write Data Flow through Byte Assembly Logic in2-143PDP-11 Normal Mode.2-1432-55 Timing for Typical Read Data Flow through Byte Assembly Logic in2-143PDP-11 Normal Mode.2-1442-55 Timing for Typical Read Data Flow through Byte Assembly Logic inPDP-11 Normal Mode.2-1442-56 Write Microcontroller Flow.2-1542-57 Write Microcontroller Flow.2-1562-58 M8959 Microbus Interface2-1562-59 TS78 Power Supply2-1562-60 TS78 Power Supply2-1562-61 Backplane/Power Supply Interconnection2-1622-63 H7441 + 5 Volt Regulator Block Diagram2-1632-64 H7476 ± 15 Volt Regulator Block Diagram2-1662-65 H7490 — 5 Volt Regulator Block Diagram2-1662-66 AC/DC LO Module Simplified Block Diagram2-1662-67 AC/DC LO Power Up, Power Down Cycle2-1662-68 TM78 Maintenance Panel Block Diagram2-1663-1 Tape Drive Block Diagram2-1663-1 Tape Drive Block Diagram3-2                          |

| 2-51 Translation Microcontroller.2-1382-52 M8959 Write Microcontroller Functional Areas2-1412-53 Write Microcontroller Byte Assembly Logic2-1432-54 Timing for Typical Write Data Flow through Byte Assembly Logic inPDP-11 Normal Mode.PDP-11 Normal Mode2-1432-55 Timing for Typical Read Data Flow through Byte Assembly Logic inPDP-11 Normal Mode.PDP-11 Normal Mode2-1432-55 Write Microcontroller Flow2-1432-56 Write Microcontroller Flow2-1532-57 Write Microcontroller Flow2-1542-58 M8959 Microbus Interface.2-1542-59 TS78 Power Supply.2-1562-60 TS78 Power Supply.2-1562-61 Backplane/Power Supply Interconnection.2-1632-62 TS78 Power Supply Block Diagram2-1632-63 H7441 + 5 Volt Regulator Block Diagram2-1642-64 H7476 ± 15 Volt Regulator Block Diagram.2-1642-65 H7490 —5 Volt Regulator Block Diagram.2-1642-66 AC/DC LO Module Simplified Block Diagram.2-1642-67 AC/DC LO Power Up, Power Down Cycle.2-1642-68 TM78 Maintenance Panel Block Diagram.2-1643-1 Tape Drive Block Diagram.3-23-2 Functional Block Diagram Symbology.3-4 |

| 2-51 Translation Microcontroller2-1332-52 M8959 Write Microcontroller Functional Areas.2-1412-53 Write Microcontroller Byte Assembly Logic.2-1432-54 Timing for Typical Write Data Flow through Byte Assembly Logic in2-143PDP-11 Normal Mode.2-1432-55 Timing for Typical Read Data Flow through Byte Assembly Logic in2-143PDP-11 Normal Mode.2-1442-55 Timing for Typical Read Data Flow through Byte Assembly Logic inPDP-11 Normal Mode.2-1442-56 Write Microcontroller Flow.2-1542-57 Write Microcontroller Flow.2-1562-58 M8959 Microbus Interface2-1562-59 TS78 Power Supply2-1562-60 TS78 Power Supply2-1562-61 Backplane/Power Supply Interconnection2-1622-63 H7441 + 5 Volt Regulator Block Diagram2-1632-64 H7476 ± 15 Volt Regulator Block Diagram2-1662-65 H7490 — 5 Volt Regulator Block Diagram2-1662-66 AC/DC LO Module Simplified Block Diagram2-1662-67 AC/DC LO Power Up, Power Down Cycle2-1662-68 TM78 Maintenance Panel Block Diagram2-1663-1 Tape Drive Block Diagram2-1663-1 Tape Drive Block Diagram3-2                          |

|    | 3-5 Circuit Card Interconnections             |              |

|----|-----------------------------------------------|--------------|

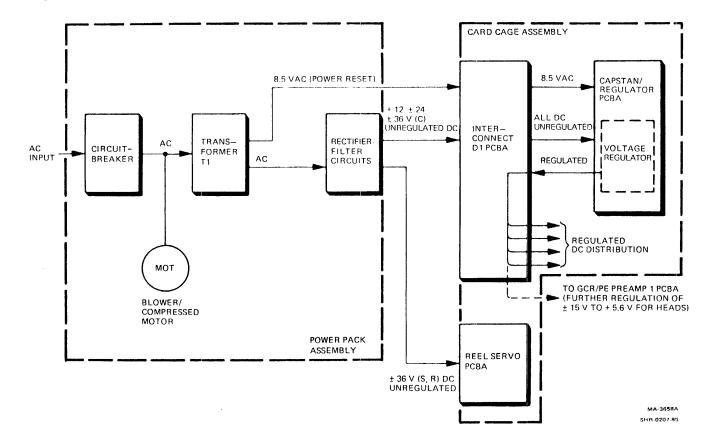

|    | 3-6 Power Supply Simplified Block Diagram     | 3-11         |

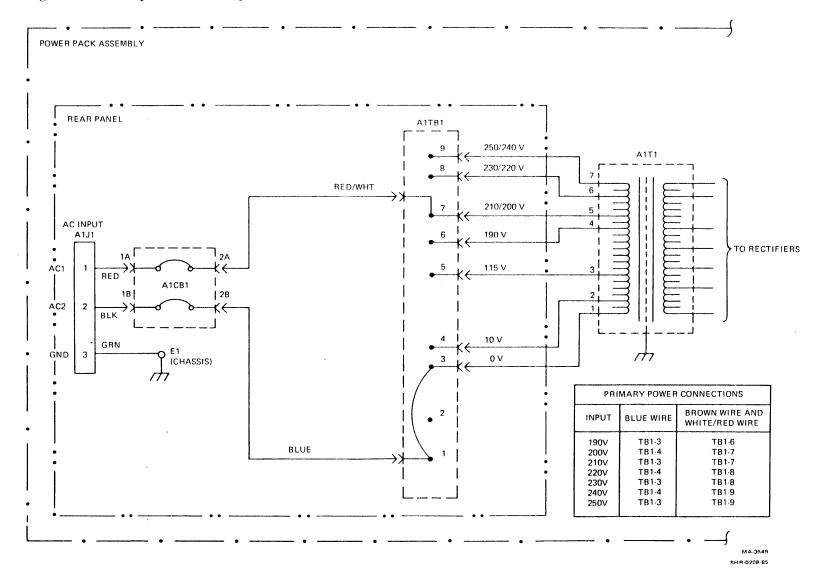

|    | 3-7 Primary Power Hookup and Control          | 3-13         |

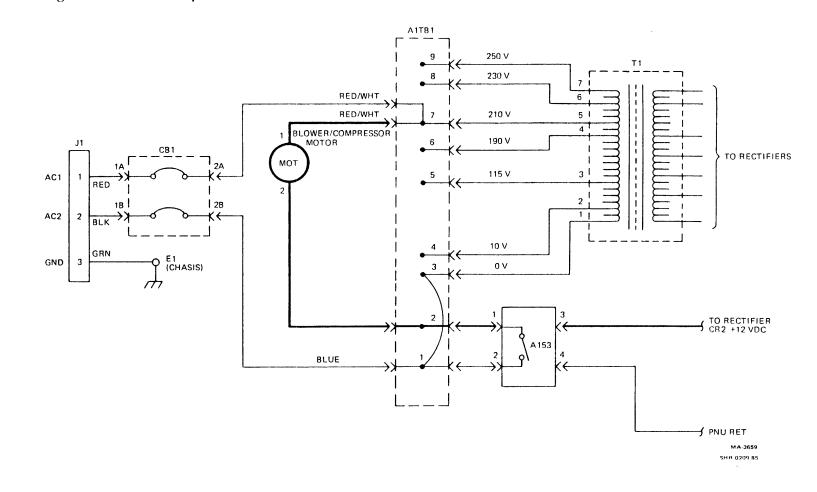

|    | 3-8 Blower/Compressor Motor Power and Control | 3-14         |

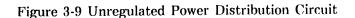

|    | 3-9 Unregulated Power Distribution Circuit    | 3-16         |

|    | 3-10 DC Power Regulation and Description      | 3-17         |

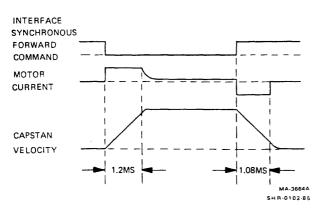

|    | 3-11 MIA Basic Block Diagram                  | 3-20         |

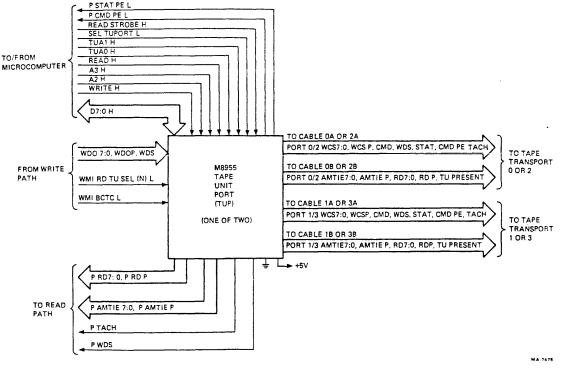

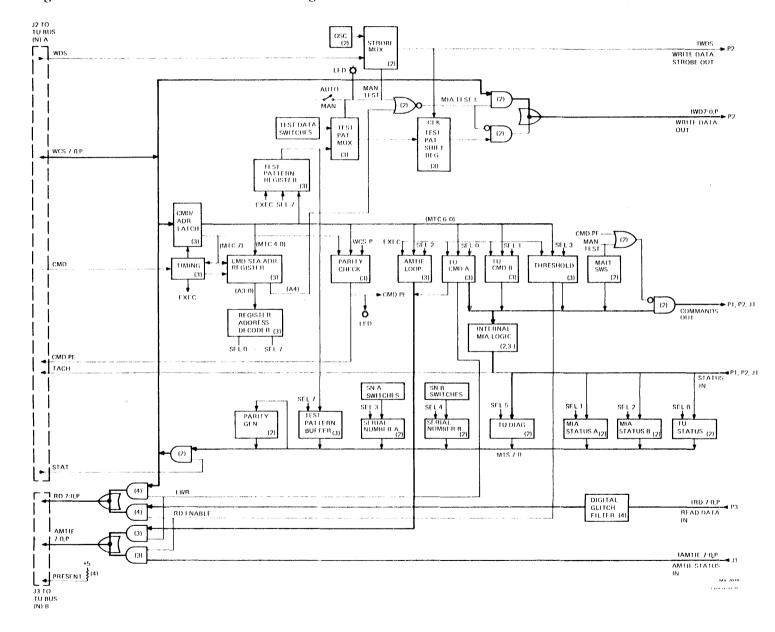

|    | 3-12 MIA PCBA Detailed Block Diagram          | 3-27         |

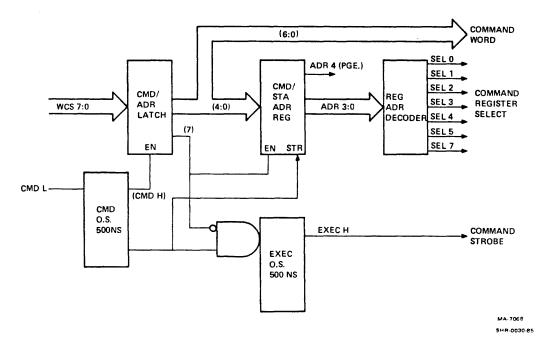

|    | 3-13 Command Timing Logic                     | 3-28         |

|    | 3-14 Command Timing                           |              |

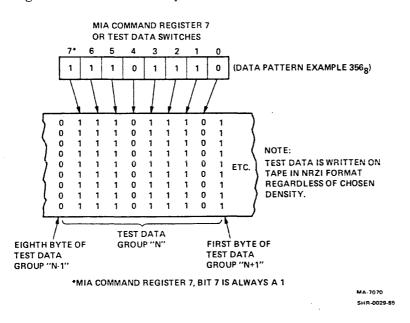

|    | 3-15 Test Data Tape Format                    |              |

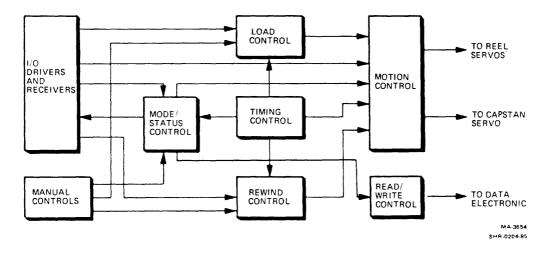

|    | 3-16 Control Logic Block Diagram              |              |

|    | 3-17 Control Signal General Routing           |              |

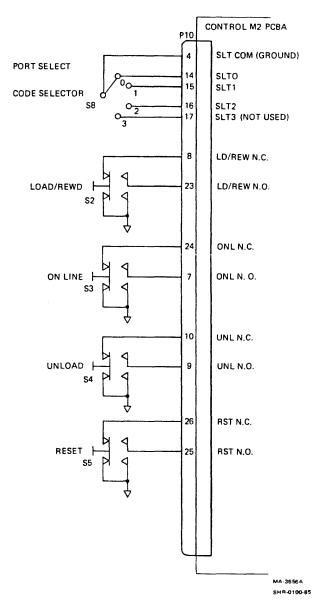

|    | 3-18 Manual Control Switch                    |              |

|    | 3-19 Front Panel Indicator Connections        |              |

|    | 3-20 Control M2 PCBA Inputs and Outputs.      |              |

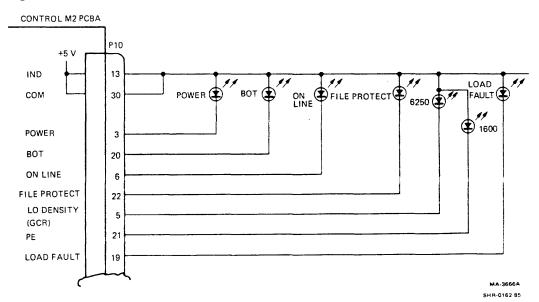

|    | 3-21 Air Load/Control Function                |              |

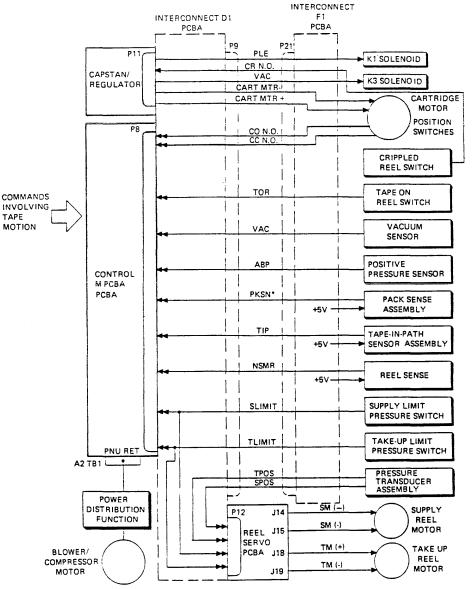

|    | 3-22 Tape Loop in Takeup Buffer Box           |              |

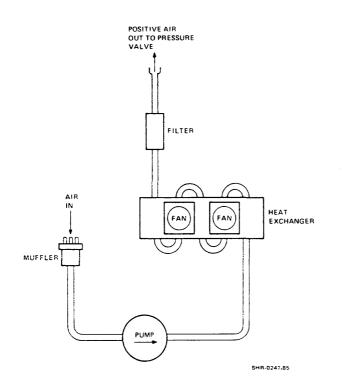

|    | 3-23 Positive Air Supply System               |              |

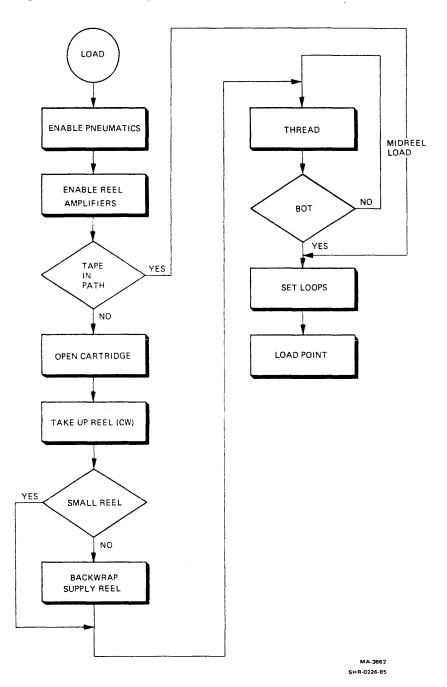

|    | 3-24 Load Sequence                            |              |

|    | -                                             |              |

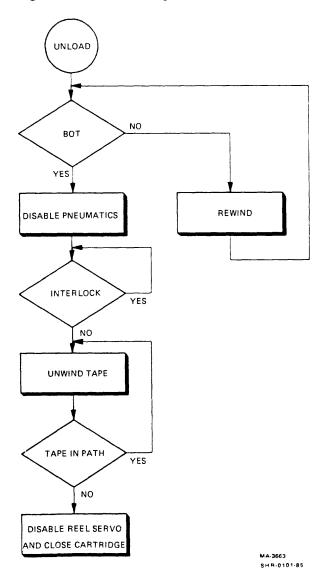

|    | 3-25 Unload Sequence.                         |              |

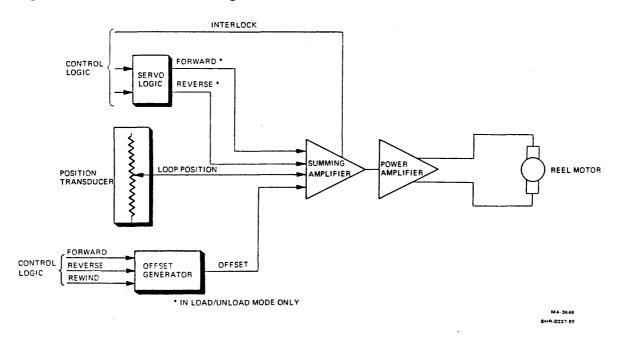

|    | 3-26 Reel Servo Block Diagram                 |              |

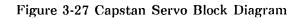

|    | 3-27 Capstan Servo Block Diagram.             |              |

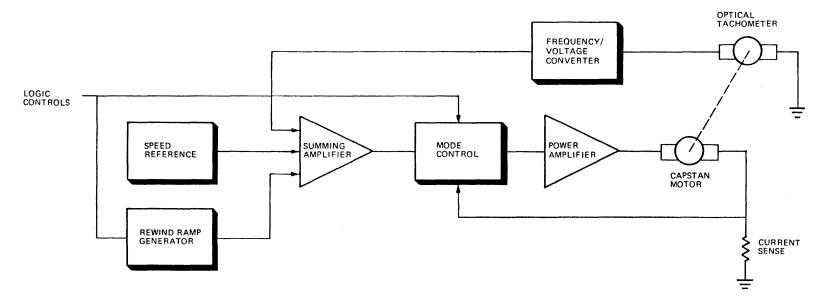

|    | 3-28 Capstan Servo Waveform.                  |              |

|    | 3-29 Data Paths                               |              |

|    | 3-30 Write Function Block Diagram             |              |

|    | 3-31 Read Function Block Diagram.             |              |

|    | 3-32 Write PCBA Block Diagram                 |              |

|    | 3-33 Write Amplifier Circuitry                |              |

|    | 3-34 AMTIE Generator                          |              |

|    | 3-35 Write PCBA Functional Block Diagram      |              |

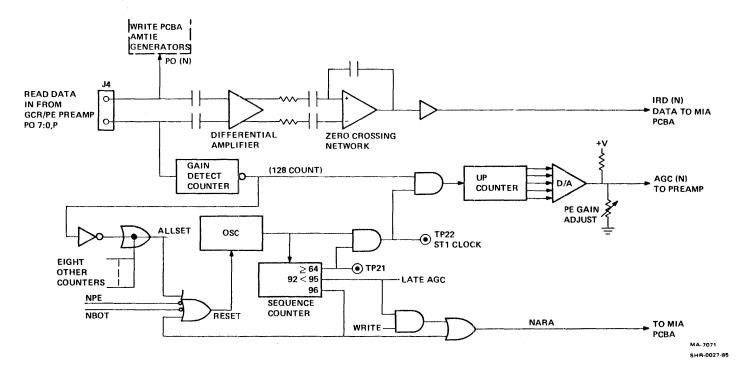

|    | 3-36 Read PCBA Functional Block Diagram       | 3-69         |

|    | B-1 Error Number Bytes                        | <b>B-</b> 58 |

|    | C-1 Tape Unit Command/Status Byte Format      | C-1          |

|    | C-2 TU Command/Status Summary                 | C-2          |

|    |                                               |              |

| Та | bles                                          |              |

|    | 1-1 Common Tape Term Definitions              | 1-5          |

|    | 1-2 Four-to-Five Translation Record Codes     | 1-14         |

|    | 1-3 TM78 Internal Interrupt Summary           | 1-25         |

|    | 1-4 TU Bus Signals                            | 1-50         |

|    | 2-1 Microcomputer Pins.                       |              |

|    | 2-2 Read/Write Path Clock Sources.            |              |

|    | 2-3 Microcomputer I/O Decoding                |              |

|    | 2-4 TS78 Interrupt Summary                    |              |

|    | 2-5 Data Path Operation Control               |              |

|    | 2-6 FIFO Clock Signal Sources                 |              |

|    | 2-7 STI Port Control.                         |              |

|    |                                               |              |

-----

| 2-9 M8973 I/O Decoding       2-58         2-10 Microcomputer Pins       2-62 |

|------------------------------------------------------------------------------|

| 2-10 Microcomputer Pins 2-69                                                 |

| 2-10 microcomputer 1 ms                                                      |

| 2-11 Read/Write Path Clock Sources                                           |

| 2-12 TU Port Registers                                                       |

| 2-13 Data Control Counter Description                                        |

| 2-14 TM78 Power Supply Output Power Characteristics                          |

| 2-15 Backplane/Power Supply Interconnections                                 |

| 3-1 TU Bus Signal Summary                                                    |

| 3-2 Transport to MIA Interface Signal Summary                                |

| 3-3 Basic Timing Frequencies                                                 |

| 3-4 Reel Servo PCBA Inputs                                                   |

| 3-5 Reel Servo PCBA Outputs                                                  |

| 3-6 Write PCBA Inputs                                                        |

| 3-7 Write PCBA Outputs                                                       |

| 3-8 Read PCBA Inputs                                                         |

| 3-9 Read PCBA Outputs                                                        |

| B-1 TS78 Control Panel Error Code B-1                                        |

| B-2 Register and Internal Address                                            |

| C-1 TU Command Register Descriptions                                         |

| C-2 TU Status Register Descriptions C-6                                      |

| F-1 Major Plug/Jack Reference Designations                                   |

| F-2 TU Bus Interface Signals                                                 |

| F-3 AMTIE Cable Signals F-3                                                  |

| F-4 MIA PCBA to Transport Interface                                          |

| F-5 Power Distribution on Interconnect D1 PCBA F-5                           |

| F-6 Deck Interface Ribbon to Interconnect D1 PCBA                            |

| F-7 Internal Control Signals on Interconnect D1 PCBA                         |

| F-8 Interface Control Signals on Interconnect D1 PCBA                        |

| F-9 Interface Read Signals on Interconnect D1 PCBA                           |

| F-10 Interface Write Signals on Interconnect D1 PCBA F-9                     |

# CHAPTER 1 GENERAL DESCRIPTION

## **1.1 INTRODUCTION**

This manual contains functional and detailed descriptions of the tape drive and formatter hardware. The subsystem is a high performance magnetic tape drive. The TA78/79 provides magnetic tape backup and data interchange for fixed-media disk drives controlled by the HSC, whereas the TU78/79 uses the Massbus directly from the system.

Both tape drives write and read data in 9-track phase-encoded (PE) or group code recording (GCR) format. Bit density is 1600 bits per inch (bits/in) for the PE format and 6250 bits/in in the GCR format. The tape drive can read or write data in the forward direction, or read data in the reverse direction. The read/write tape speed is 125 inches per second (in/s). They also offer the following features.

- Single-track error correction while reading PE or GCR data

- Two-track error correction while reading GCR data

- Resident in-line microdiagnostics

- Error repositioning for retries

# **1.2 SPECIFICATIONS**

The following list includes the mechanical, electrical, functional and environmental specifications of the tape subsystem.

| Tape (computer grade)    |                                                                                    |

|--------------------------|------------------------------------------------------------------------------------|

| Width                    | $12.6492 \text{ mm} \pm 0.0508 \text{ mm} (0.498 \text{ in} \pm 0.002 \text{ in})$ |

| Thickness                | 0.0381 mm (1.5 mil)                                                                |

| Tape tension             | 2.780 N (10.0 oz +0.0/ 1.0 oz) nominal                                             |

| Reel diameter (autoload) | 266.7 mm (10.5 in) maximum (note 1) and wraparound cartridge 1 and 2               |

| Recording modes          |                                                                                    |

| PE                       | 1600 bits/in (3200 FCI)                                                            |

| GCR                      | 6250 bits/in (9042 FCI)                                                            |

| Magnetic head            | Dual stack (with erase head)                                                       |

| Tape speed<br>Read/write<br>Rewind                                     | 3.2 m/s (125 in/s)<br>11.2 m/s (440 in/s)                                                                                |

|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| Instantaneous speed<br>variation                                       | $\pm$ 1 percent                                                                                                          |

| Long term speed<br>variation                                           | ± 1 percent (forward) ± 2 percent (reverse)                                                                              |

| Rewind time for 731.5 m<br>(2400 ft) tape                              | 65 seconds nominal (85 seconds<br>maximum)                                                                               |

| Tape cleaner                                                           | Dual blade type connected to vacuum supply                                                                               |

| Interchannel displacement error<br>Read<br>Read-after-write            | 3.81 m (150 in) maximum (note 2)<br>8.89 m (350 in) maximum (note 3)                                                     |

| Start/stop time<br>Start<br>Stop                                       | 1.3 ms $\pm$ 0.1 ms<br>1.1 ms $\pm$ 0.1 ms                                                                               |

| Start distance                                                         | 1.91 mm +0.25/ 0.38 mm<br>(0.075 in +0.010/ 0.015 in)                                                                    |

| Stop distance                                                          | 2.16 mm +0.25/ 0.38 mm<br>(0.85 in +0.010/ 0.015 in)                                                                     |

| Beginning of tape (BOT) and<br>end of tape (EOT) detectors<br>(note 4) | Photoelectric                                                                                                            |

| Tape creepage                                                          | None                                                                                                                     |

| Pneumatic interlock                                                    | Tape motion disabled when vacuum is lost in vacuum column                                                                |

| Load time                                                              | No greater than 10 seconds without a retry, and 20 seconds with a retry for 10.5-in reels                                |

| Unload time                                                            | Less than 7 seconds for 10.5-in reels                                                                                    |

| Write gap to read gap distance                                         | $0.381 \text{ cm} \pm 0.013 \text{ cm}$<br>(0.150 in $\pm 0.005$ in)                                                     |

| Error detection<br>PE                                                  | Single-track error correction                                                                                            |

| GCR                                                                    | Single-track error correction always: double-track error correction with pointers: CRC/ACRC check character verification |

| Maximum record length                                                  | 65,536 (64K) characters (PE and GCR)                                                                                     |

| Minimum record length                                                                          | 1 character (PE                  | and GCR)                                   |                                |  |

|------------------------------------------------------------------------------------------------|----------------------------------|--------------------------------------------|--------------------------------|--|

| Data reliability                                                                               | Established by o                 | error rate of transpor                     | e of transport as follows.     |  |

|                                                                                                | Recoverable                      | GCR<br>Read 1 in 10(9)<br>Write 1 in 10(7) | PE<br>1 in 10(9)<br>1 in 10(7) |  |

|                                                                                                | Nonrecoverable                   | Read 1 in 10(10)                           | 1 in 10(10)                    |  |

| Note:                                                                                          |                                  |                                            |                                |  |

| $\begin{array}{l} (10) = 10.000,000,000\\ (9) = 1.000,000,000\\ (7) = 10.000,000. \end{array}$ |                                  |                                            |                                |  |

| Operating temperature                                                                          | 150 to 320 C (59                 | 90 to 900 F) (note 5)                      |                                |  |

| Nonoperating temperature                                                                       | 400 to 660 C (40                 | )o to 1510 F)                              |                                |  |

| Humidity (operating)                                                                           |                                  | a maximum wet bulk<br>inimum dry bulb of t |                                |  |

| Operating altitude                                                                             | 0 m to 2438 m (                  | 0 ft to 8000 ft) (note                     | 6)                             |  |

| Nonoperating altitude                                                                          | 9100 m (30,000                   | ft) maximum                                |                                |  |

| Power<br>Volts ac                                                                              | 208 V to 240 V<br>208 V to 240 V |                                            |                                |  |

| Frequency                                                                                      | 50 Hz ± 1 Hz                     | or 60 Hz $\pm$ 1 Hz                        |                                |  |

| Kilovolt amp (kVA)<br>Standby (loaded)<br>Start/stop                                           | 1.74 kVA maxin<br>2.90 kVA maxin |                                            |                                |  |

#### Notes:

- 1. 177.8 mm (7 in) and 216.0 mm (8.5 in) reels may be used but cannot be autoloaded.

- 2. The maximum displacement between any two bits of a character when reading a master tape using the read section of the tape head.

- 3. The maximum displacement between any two bits of a character on a tape written with all ones using the write section of the tape head.

- 4. Approximate distance from detection area to write head gap is 35.6 mm (1.40 in).

- 5. For data transfer, the operating temperature is dictated by the nature of the tape media.

- 6. Operation above 610 m (2000 ft) requires installation of high altitude pulleys and belts in tape drive power pack.

# **1.3 RELATED DOCUMENTS**

The following list describes documents related to the TA78/TA79/TU79/TU78 magnetic tape drive.

| Title                                                  | <b>Document Number</b> |

|--------------------------------------------------------|------------------------|

| TA78 Magnetic Tape Drive User's Guide                  | EK-0TA78-UG            |

| TA78 Magnetic Tape Drive Service Manual                | EK-0TA78-SV            |

| TA78 Magnetic Tape Drive Maintenance Guide             | AA-P673A-TK            |

| TA78 Magnetic Tape Drive IPB                           | EK-0TA78-IP            |

| 874 Power Controller IPB                               | EK-00874-IP            |

| TA78 Field Maintenance Print Set                       | MP-01614-00            |

| TA79,TU79 Magnetic Tape Subsystem Service Manual       | EK-OTA79-SV            |

| TA78/79 System Error Logging/Error Handling Supplement | EK-OTA79-EL            |

| TA79,TU79 Magnetic Tape Subsystem Installation Manual  | EK-OTA79-IN            |

| TA79,TU79 Magnetic Tape Subsystem Owner's Manual       | EK-OTA79-OM            |

# **1.4 TAPE FORMATS**

The formatter used in the tape subsystem is industry compatible with 1600 bits/in PE and 6250 bits/in GCR tape formats. Both formats are described in the following paragraphs.